Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 2KB (2K x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

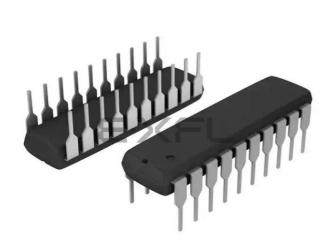

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89lp2052-20pu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7.7 I/O Ports

The I/O ports of the AT89LP2052/LP4052 may be configured in four different modes. On the AT89LP2052/LP4052, all the I/O ports revert to input-only (tri-stated) mode at power-up or reset. In the standard 8051, all ports are weakly pulled high during power-up or reset. To enable 8051-like ports, the ports must be put into quasi-bidirectional mode by clearing the P1M0 and P3M0 SFRs.

## 7.8 Reset

The RST pin in the AT89LP2052/LP4052 has different pulse width requirements than the standard 8051. The RST pin is sampled every clock cycle and must be held **high** for a minimum of two clock cycles, instead of 24 clock cycles, to be recognized as a valid reset pulse

# 8. Enhanced CPU

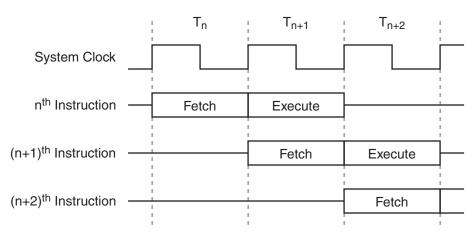

The AT89LP2052/LP4052 uses an enhanced 8051 CPU that runs at 6 to 12 times the speed of standard 8051 devices (or 3 to 6 times the speed of X2-mode 8051 devices). The increase in performance is due to two factors. First, the CPU fetches one instruction byte from the code memory every clock cycle. Second, the CPU uses a simple two-stage pipeline to fetch and execute instructions in parallel. This basic pipelining concept allows the CPU to obtain up to 1 MIPS per MHz. A simple example is shown in Figure 8-1.

The MCS-51 instruction set allows for instructions of variable length from 1 to 3 bytes. In a single-clock-per-byte-fetch system this means each instruction takes at least as many clocks as it has bytes to execute. A majority of the instructions in the AT89LP2052/LP4052 follow this rule: the instruction execution time in clock cycles equals the number of bytes per instruction with a few exceptions. Branches and Calls require an additional cycle to compute the target address and some other complex instructions require multiple cycles. See Section 22. "Instruction Set Summary" on page 52 for more detailed information on individual instructions. Figures 8-2 and 8-3 show examples of one- and two-byte instructions.

## Figure 8-1. Parallel Instruction Fetches and Executions

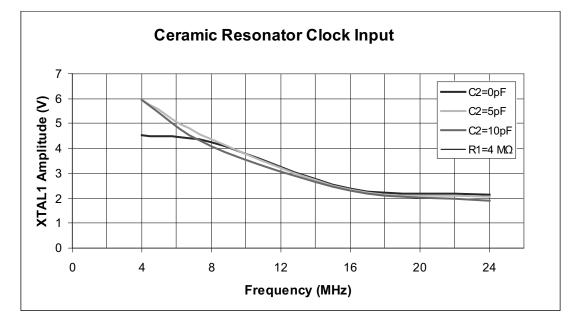

Figure 11-5. Ceramic Resonator Clock Source (B)

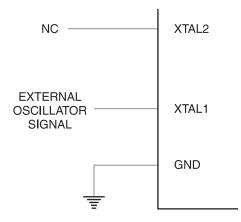

To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven, as shown in Figure 11-6.

Figure 11-6. External Clock Drive Configuration

| Table 14-4. | IPH – Interrupt Priority High Register |

|-------------|----------------------------------------|

|-------------|----------------------------------------|

| IPH =               | B7H Reset Value = X0X0 0000B |                                    |        |   |   |   |   |   |  |  |  |

|---------------------|------------------------------|------------------------------------|--------|---|---|---|---|---|--|--|--|

| Not Bit Addressable |                              |                                    |        |   |   |   |   |   |  |  |  |

|                     | -                            | – PCH – PSH PT1H PX1H PT0H PX0H    |        |   |   |   |   |   |  |  |  |

| Bit                 | 7                            | 6                                  | 5      | 4 | 3 | 2 | 1 | 0 |  |  |  |

| Symbol              | Function                     |                                    |        |   |   |   |   |   |  |  |  |

| PCH                 | Comparator                   | Interrupt Priority                 | / High |   |   |   |   |   |  |  |  |

| PSH                 | Serial Port I                | nterrupt Priority                  | High   |   |   |   |   |   |  |  |  |

| PT1H                | Timer 1 Inte                 | errupt Priority Hig                | Jh     |   |   |   |   |   |  |  |  |

| PX1H                | External Inte                | External Interrupt 1 Priority High |        |   |   |   |   |   |  |  |  |

| PT0H                | Timer 0 Inte                 | Timer 0 Interrupt Priority High    |        |   |   |   |   |   |  |  |  |

| PX0H                | External Inte                | errupt 0 Priority                  | High   |   |   |   |   |   |  |  |  |

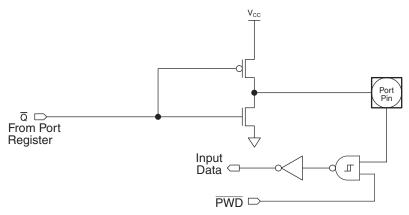

# 15. I/O Ports

All 15 port pins on the AT89LP2052/LP4052 may be configured to one of four modes: quasi-bidirectional (standard 8051 port outputs), push-pull output, open-drain output, or input-only. Port modes may be assigned in software on a pin-by-pin basis as shown in Table 15-1. All port pins default to input-only mode after reset. Each port pin also has a Schmitt-triggered input for improved input noise rejection. During Power-down all the Schmitt-triggered inputs are disabled with the exception of P3.2 and P3.3, which may be used to wake-up the device. Therefore P3.2 and P3.3 should not be left floating during Power-down.

| Table 15-1. | Configuration Modes for Port x, Bit y |  |

|-------------|---------------------------------------|--|

|-------------|---------------------------------------|--|

| PxM0.y | PxM1.y | Port Mode                   |

|--------|--------|-----------------------------|

| 0      | 0      | Quasi-bidirectional         |

| 0      | 1      | Push-pull Output            |

| 1      | 0      | Input Only (High Impedance) |

| 1      | 1      | Open-Drain Output           |

# 15.1 Quasi-bidirectional Output

Port pins in quasi-bidirectional output mode function similar to standard 8051 port pins. A Quasibidirectional port can be used both as an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is driven low, it is driven strongly and able to sink a large current. There are three pull-up transistors in the quasi-bidirectional output that serve different purposes.

One of these pull-ups, called the "very weak" pull-up, is turned on whenever the port register for the pin contains a logic "1". This very weak pull-up sources a very small current that will pull the pin high if it is left floating.

# 15.3 Open-drain Output

The open-drain output configuration turns off all pull-ups and only drives the pull-down transistor of the port pin when the port register contains a logic "0". To be used as a logic output, a port configured in this manner must have an external pull-up, typically a resistor tied to  $V_{CC}$ . The pull-down for this mode is the same as for the quasi-bidirectional mode. The open-drain port configuration is shown in Figure 15-4. The input circuitry of P3.2 and P3.3 is not disabled during Power-down (see Figure 15-3).

### Figure 15-4. Open-Drain Output

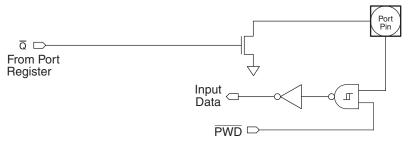

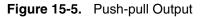

## 15.4 Push-pull Output

The push-pull output configuration has the same pull-down structure as both the open-drain and the quasi-bidirectional output modes, but provides a continuous strong pull-up when the port register contains a logic "1". The push-pull mode may be used when more source current is needed from a port output. The push-pull port configuration is shown in Figure 15-5. The input circuitry of P3.2 and P3.3 is not disabled during Power-down (see Figure 15-3).

## 15.5 Port 1 Analog Functions

The AT89LP2052/LP4052 incorporates an analog comparator. In order to give the best analog performance and minimize power consumption, pins that are being used for analog functions must have both the digital outputs and digital inputs disabled. Digital outputs are disabled by putting the port pins into the input-only mode as described in Section 15. "I/O Ports" on page 20.

Digital inputs on P1.0 and P1.1 are disabled whenever the Analog Comparator is enabled by setting the CEN bit in ACSR. CEN forces the PWD input on P1.0 and P1.1 low, thereby disabling the Schmitt trigger circuitry.

out an address byte that identifies the target slave. An address byte differs from a data byte in that the 9th bit is "1" in an address byte and "0" in a data byte. With SM2 = 1, no slave is interrupted by a data byte. An address byte, however, interrupts all slaves, so that each slave can examine the received byte and see if it is being addressed. The addressed slave clears its SM2 bit and prepares to receive the data bytes that follows. The slaves that are not addressed set their SM2 bits and ignore the data bytes.

The SM2 bit has no effect in Mode 0 but can be used to check the validity of the stop bit in Mode 1. In a Mode 1 reception, if SM2 = 1, the receive interrupt is not activated unless a valid stop bit is received.

| SCON Address = 98H Reset Value = 0000 0000B |            |     |     |     |     |     |    |    |  |

|---------------------------------------------|------------|-----|-----|-----|-----|-----|----|----|--|

| Bit A                                       | ddressable |     |     |     |     |     |    |    |  |

|                                             | SM0/FE     | SM1 | SM2 | REN | TB8 | RB8 | T1 | RI |  |

| Bit                                         | 7          | 6   | 5   | 4   | 3   | 2   | 1  | 0  |  |

| Table 18-1. S | CON – Serial Po | t Control | Register |

|---------------|-----------------|-----------|----------|

|---------------|-----------------|-----------|----------|

$(SMOD0 = 0/1)^{(1)}$

| Symbol | Function                                                                                                                                                                                                                                                                         |                                                           |                   |                       |                                                                                                                                                     |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| FE     | Framing error bit. This bit is set by the receiver when an invalid stop bit is detected. The FE bit is not cleared by valid frames but should be cleared by software. The SMOD0 bit must be set to enable access to the FE bit. FE will be set regardless of the state of SMOD0. |                                                           |                   |                       |                                                                                                                                                     |  |  |  |  |

| SM0    | Serial Port Mode Bit 0, (SMOD0 must = 0 to access bit SM0)                                                                                                                                                                                                                       |                                                           |                   |                       |                                                                                                                                                     |  |  |  |  |

|        | Serial Port Mode                                                                                                                                                                                                                                                                 | e Bit 1                                                   |                   |                       |                                                                                                                                                     |  |  |  |  |

|        | SM0                                                                                                                                                                                                                                                                              | SM1                                                       | Mode              | Description           | Baud Rate <sup>(2)</sup>                                                                                                                            |  |  |  |  |

|        | 0                                                                                                                                                                                                                                                                                | 0                                                         | 0                 | shift register        | f <sub>osc</sub> /2                                                                                                                                 |  |  |  |  |

| SM1    | 0                                                                                                                                                                                                                                                                                | 1                                                         | 1                 | 8-bit UART            | variable                                                                                                                                            |  |  |  |  |

|        | 1                                                                                                                                                                                                                                                                                | 0                                                         | 2                 | 9-bit UART            | $f_{\rm osc}/32$ or $f_{\rm osc}/16$                                                                                                                |  |  |  |  |

|        | 1                                                                                                                                                                                                                                                                                | 1                                                         | 3                 | 9-bit UART            | variable                                                                                                                                            |  |  |  |  |

| SM2    | 9th data bit (RB8                                                                                                                                                                                                                                                                | <ol> <li>is 1, indicating a be activated unles</li> </ol> | n address, and th | e received byte is a  | M2 = 1 then RI will not be set unless the receiv<br>Given or Broadcast Address. In Mode 1, if SM2<br>he received byte is a Given or Broadcast Addre |  |  |  |  |

| REN    | Enables serial re                                                                                                                                                                                                                                                                | eception. Set by so                                       | oftware to enable | reception. Clear by   | software to disable reception.                                                                                                                      |  |  |  |  |

| TB8    | The 9th data bit                                                                                                                                                                                                                                                                 | that will be transm                                       | itted in Modes 2  | and 3. Set or clear b | y software as desired.                                                                                                                              |  |  |  |  |

| RB8    | In Modes 2 and 3<br>0, RB8 is not use                                                                                                                                                                                                                                            |                                                           | hat was received  | . In Mode 1, if SM2 = | 0, RB8 is the stop bit that was received. In Mo                                                                                                     |  |  |  |  |

|        | Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission. Must be cleared by software.                                                                              |                                                           |                   |                       |                                                                                                                                                     |  |  |  |  |

| ті     |                                                                                                                                                                                                                                                                                  |                                                           |                   |                       |                                                                                                                                                     |  |  |  |  |

Notes: 1. SMOD0 is located at PCON.6.

2.  $f_{osc} = oscillator frequency.$

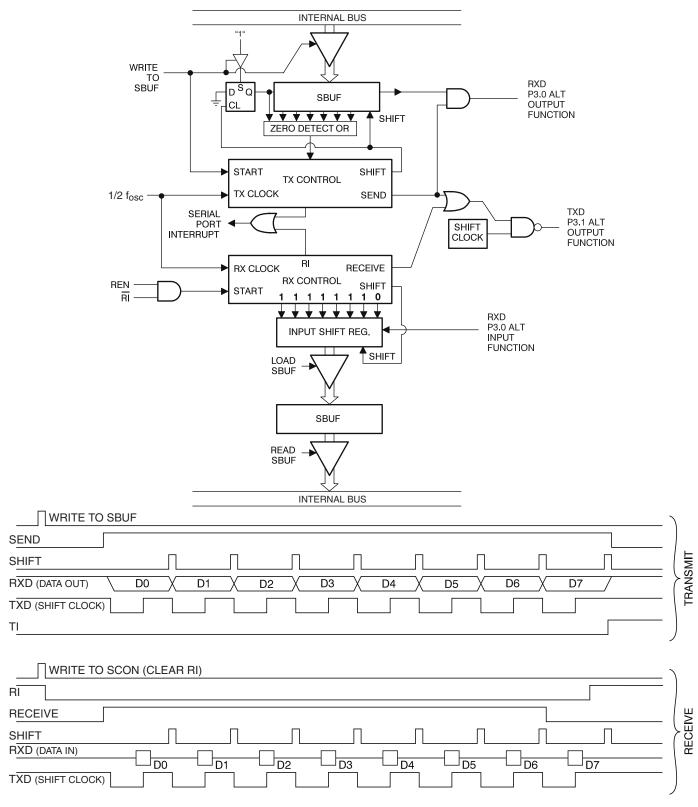

#### Figure 18-1. Serial Port Mode 0

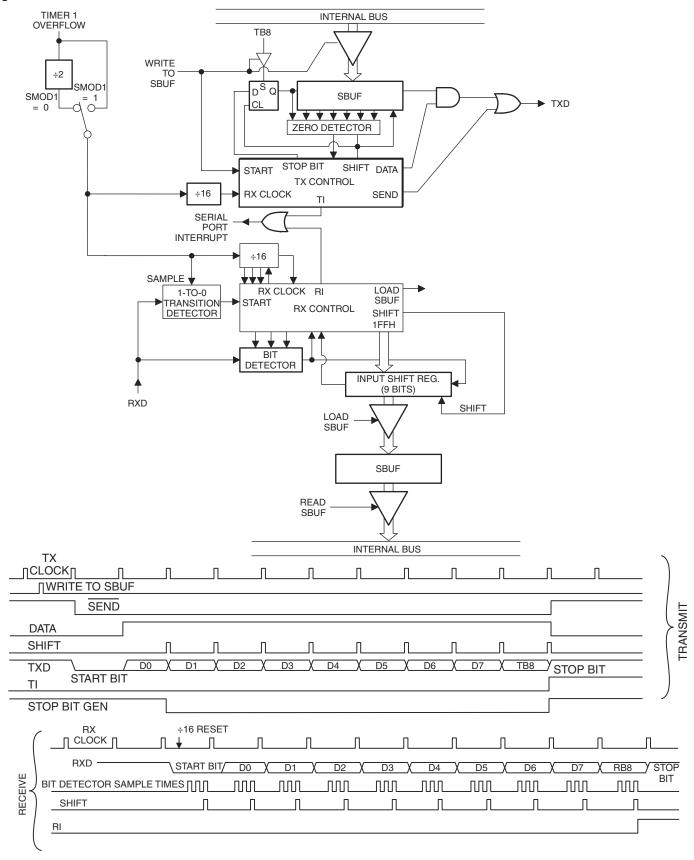

#### Figure 18-4. Serial Port Mode 3

• AT89LP2052/LP4052

40

Given = 1110 0X0X

In a more complex system the following could be used to select slaves 1 and 2 while excluding slave 0:

| Slave 0 | SADDR = 1100 0000        |

|---------|--------------------------|

|         | SADEN = <u>1111 1001</u> |

|         | Given = 1100 0XX0        |

|         |                          |

| Slave 1 | SADDR = 1110 0000        |

|         | SADEN = <u>1111 1010</u> |

Slave 2 SADDR = 1110 0000 SADEN = <u>1111 1100</u> Given = 1110 00XX

In the above example the differentiation among the 3 slaves is in the lower 3 address bits. Slave 0 requires that bit 0 = 0 and it can be uniquely addressed by 1110 0110. Slave 1 requires that bit 1 = 0 and it can be uniquely addressed by 1110 and 0101. Slave 2 requires that bit 2 = 0 and its unique address is 1110 0011. To select Slaves 0 and 1 and exclude Slave 2, use address 1110 0100, since it is necessary to make bit 2 = 1 to exclude slave 2.

The Broadcast Address for each slave is created by taking the logic OR of SADDR and SADEN. Zeros in this result are treated as don't cares. In most cases, interpreting the don't cares as ones, the broadcast address will be FF hexadecimal.

Upon reset SADDR (SFR address 0A9H) and SADEN (SFR address 0B9H) are loaded with "0"s. This produces a given address of all "don't cares" as well as a Broadcast address of all "don't cares". This effectively disables the Automatic Addressing mode and allows the microcontroller to use standard 80C51-type UART drivers which do not make use of this feature.

# **19. Serial Peripheral Interface**

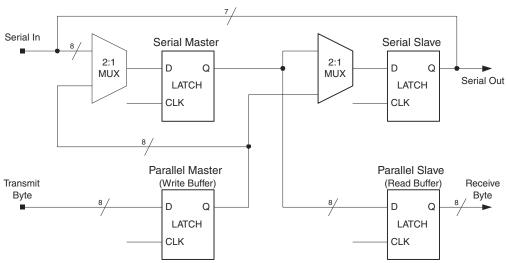

The serial peripheral interface (SPI) allows high-speed synchronous data transfer between the AT89LP2052/LP4052 and peripheral devices or between multiple AT89LP2052/LP4052 devices. The AT89LP2052/LP4052 SPI features include the following:

- Full-duplex, 3-wire Synchronous Data Transfer

- Master or Slave Operation

- Maximum Bit Frequency = f/4

- LSB First or MSB First Data Transfer

- Four Programmable Bit Rates in Master Mode

- End of Transmission Interrupt Flag

- Write Collision Flag Protection

- Double-buffered Receive

- Double-buffered Transmit (Enhanced Mode Only)

- Wake up from Idle Mode (Slave Mode Only)

# AT89LP2052/LP4052

Figure 19-3. SPI Shift Register Diagram

## 19.3 Serial Clock Generator

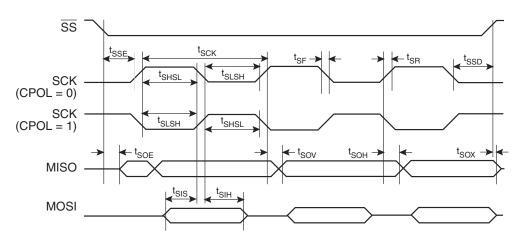

The CPHA (<u>Clock PHAse</u>), CPOL (<u>Clock POL</u>arity), and SPR (<u>Serial Peripheral clock Rate = baud rate</u>) bits in SPCR control the shape and rate of SCK. The two SPR bits provide four possible clock rates when the SPI is in master mode. In slave mode, the SPI will operate at the rate of the incoming SCK as long as it does not exceed the maximum bit rate. There are also four possible combinations of SCK phase and polarity with respect to the serial data. CPHA and CPOL determine which format is used for transmission. The SPI data transfer formats are shown in Figures 19-4 and and 19-5. To prevent glitches on SCK from disrupting the interface, CPHA, CPOL, and SPR should be set up before the interface is enabled, and the master device should be enabled before the slave device(s).

## Table 20-1. ACSR – Analog Comparator Control & Status Register

| ACSR =  | ACSR = 97H Reset Value = XXX0 0000B |   |      |    |     |     |     |     |  |  |  |

|---------|-------------------------------------|---|------|----|-----|-----|-----|-----|--|--|--|

| Not Bit | Not Bit Addressable                 |   |      |    |     |     |     |     |  |  |  |

|         | _                                   | - | CIDL | CF | CEN | CM2 | CM1 | CM0 |  |  |  |

| Bit     | 7                                   | 6 | 5    | 4  | 3   | 2   | 1   | 0   |  |  |  |

| Symbol   | Fund     | Function                                                                                                                                                                                                              |          |                                                                                                                                                                                                             |  |  |  |  |  |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CIDL     |          | Comparator Idle Enable. If CIDL = 1 the comparator will continue to operate during Idle mode. If CIDL = 0 the comparator is powered down during Idle mode. The comparator is always shut down during Power-down mode. |          |                                                                                                                                                                                                             |  |  |  |  |  |

| CF       |          | •                                                                                                                                                                                                                     |          | errupt Flag. Set when the comparator output meets the conditions specified by the CM [2:0] bits and CEN nust be cleared by software. The interrupt may be enabled/disabled by setting/clearing bit 6 of IE. |  |  |  |  |  |

| CEN      |          | Comparator Enable. Set this bit to enable the comparator. Clearing this bit will force the comparator output low and prevent further events from setting CF.                                                          |          |                                                                                                                                                                                                             |  |  |  |  |  |

| CM [2:0] | Com      | parato                                                                                                                                                                                                                | or Inte  | errupt Mode                                                                                                                                                                                                 |  |  |  |  |  |

|          | <u>2</u> | <u>1</u>                                                                                                                                                                                                              | <u>0</u> | Interrupt Mode                                                                                                                                                                                              |  |  |  |  |  |

|          | 0        | 0                                                                                                                                                                                                                     | 0        | Negative (Low) level                                                                                                                                                                                        |  |  |  |  |  |

|          | 0        | 0                                                                                                                                                                                                                     | 1        | Positive edge                                                                                                                                                                                               |  |  |  |  |  |

|          | 0        | 1                                                                                                                                                                                                                     | 0        | Toggle with debounce                                                                                                                                                                                        |  |  |  |  |  |

|          | 0        | 1                                                                                                                                                                                                                     | 1        | Positive edge with debounce                                                                                                                                                                                 |  |  |  |  |  |

|          | 1        | 0                                                                                                                                                                                                                     | 0        | Negative edge                                                                                                                                                                                               |  |  |  |  |  |

|          | 1        | 0                                                                                                                                                                                                                     | 1        | Toggle                                                                                                                                                                                                      |  |  |  |  |  |

|          | 1        | 1                                                                                                                                                                                                                     | 0        | Negative edge with debounce                                                                                                                                                                                 |  |  |  |  |  |

|          | 1        | 1                                                                                                                                                                                                                     | 1        | Positive (High) level                                                                                                                                                                                       |  |  |  |  |  |

# 21. Programmable Watchdog Timer

The programmable Watchdog Timer (WDT) protects the system from incorrect execution by triggering a system reset when it times out after the software has failed to feed the timer prior to the timer overflow. The WDT counts CPU clock cycles. The prescaler bits, PS0, PS1 and PS2 in SFR WDTCON are used to set the period of the Watchdog Timer from 16K to 2048K clock cycles. The WDT is disabled by Reset and during Power-down mode. When the WDT times out without being serviced, an internal RST pulse is generated to reset the CPU. See Table 21-1 for the available WDT period selections.

|     | WDT Prescaler Bits | Period* |                |

|-----|--------------------|---------|----------------|

| PS2 | PS1                | PS0     | (Clock Cycles) |

| 0   | 0                  | 0       | 16K            |

| 0   | 0                  | 1       | 32K            |

| 0   | 1                  | 0       | 64K            |

| 0   | 1                  | 1       | 128K           |

| 1   | 0                  | 0       | 256K           |

| 1   | 0                  | 1       | 512K           |

| 1   | 1                  | 0       | 1024K          |

| 1   | 1                  | 1       | 2048K          |

Table 21-1.

Watchdog Timer Time-out Period Selection

Note: \*The WDT time-out period is dependent on the system clock frequency.

The Watchdog Timer consists of a 14-bit timer with 7-bit programmable prescaler. Writing the sequence 1EH/E1H to the WDTRST register enables the timer. When the WDT is enabled, the WDTEN bit in WDTCON will be set to "1". To prevent the WDT from generating a reset when if overflows, the watchdog feed sequence must be written to WDTRST before the end of the timeout period. To feed the watchdog, two write instructions must be sequentially executed successfully. Between the two write instructions, SFR reads are allowed, but writes are not allowed. The instructions should move 1EH to the WDTRST register and then 1EH to the WDTRST register. An incorrect feed or enable sequence will cause an immediate watchdog reset. The program sequence to feed or enable the watchdog timer is as follows:

MOV WDTRST, #01Eh

MOV WDTRST, #0E1h

|                     |       | Clock | Clock Cycles |          |

|---------------------|-------|-------|--------------|----------|

| Logical Instruction | Bytes | 8051  | LP2052       | Hex Code |

| CLR A               | 1     | 12    | 1            | E4       |

| CPL A               | 1     | 12    | 1            | F4       |

| ANL A, Rn           | 1     | 12    | 1            | 58-5F    |

| ANL A, direct       | 2     | 12    | 2            | 55       |

| ANL A, @Ri          | 1     | 12    | 2            | 56-57    |

| ANL A, #data        | 2     | 12    | 2            | 54       |

| ANL direct, A       | 2     | 12    | 2            | 52       |

| ANL direct, #data   | 3     | 24    | 3            | 53       |

| ORL A, Rn           | 1     | 12    | 1            | 48-4F    |

| ORL A, direct       | 2     | 12    | 2            | 45       |

| ORL A, @Ri          | 1     | 12    | 2            | 46-47    |

| ORL A, #data        | 2     | 12    | 2            | 44       |

| ORL direct, A       | 2     | 12    | 2            | 42       |

| ORL direct, #data   | 3     | 24    | 3            | 43       |

| XRL A, Rn           | 1     | 12    | 1            | 68-6F    |

| XRL A, direct       | 2     | 12    | 2            | 65       |

| XRL A, @Ri          | 1     | 12    | 2            | 66-67    |

| XRL A, #data        | 2     | 12    | 2            | 64       |

| XRL direct, A       | 2     | 12    | 2            | 62       |

| XRL direct, #data   | 3     | 24    | 3            | 63       |

| RL A                | 1     | 12    | 1            | 23       |

| RLC A               | 1     | 12    | 1            | 33       |

| RR A                | 1     | 12    | 1            | 03       |

| RRC A               | 1     | 12    | 1            | 13       |

| SWAP A              | 1     | 12    | 1            | C4       |

## Table 22-3. Detailed Logical Instruction Summary

## **Table 22-5.**Detailed Bit Instruction Summary

|                 |       | Clock Cycles |        |          |

|-----------------|-------|--------------|--------|----------|

| Bit Instruction | Bytes | 8051         | LP2052 | Hex Code |

| SETB bit        | 2     | 12           | 2      | D2       |

| CPL C           | 1     | 12           | 1      | B3       |

| CPL bit         | 2     | 12           | 2      | B2       |

| ANL C, bit      | 2     | 24           | 2      | 82       |

| ANL C, /bit     | 2     | 24           | 2      | B0       |

| ORL C, bit      | 2     | 24           | 2      | 72       |

| ORL C, /bit     | 2     | 24           | 2      | A0       |

| MOV C, bit      | 2     | 12           | 2      | A2       |

| MOV bit, C      | 2     | 24           | 2      | 92       |

## Table 22-6. Detailed Branching Instruction Summary

|                       |       | Clock Cycles |        |                                 |

|-----------------------|-------|--------------|--------|---------------------------------|

| Branching Instruction | Bytes | 8051         | LP2052 | Hex Code                        |

| JC rel                | 2     | 24           | 3      | 40                              |

| JNC rel               | 2     | 24           | 3      | 50                              |

| JB bit, rel           | 3     | 24           | 4      | 20                              |

| JNB bit, rel          | 3     | 24           | 4      | 30                              |

| JBC bit, rel          | 3     | 24           | 4      | 10                              |

| JZ rel                | 2     | 24           | 3      | 60                              |

| JNZ rel               | 2     | 24           | 3      | 70                              |

| SJMP rel              | 2     | 24           | 3      | 80                              |

| ACALL addr11          | 2     | 24           | 3      | 11,31,51,7<br>1,91,B1,D1<br>,F1 |

| LCALL addr16          | 3     | 24           | 4      | 12                              |

| RET                   | 1     | 24           | 4      | 22                              |

| RETI                  | 1     | 24           | 4      | 32                              |

| AJMP addr11           | 2     | 24           | 3      | 01,21,41,6<br>1,81,A1,C1<br>,E1 |

| LJMP addr16           | 3     | 24           | 4      | 02                              |

| JMP @A+DPTR           | 1     | 24           | 2      | 73                              |

| CJNE A, direct, rel   | 3     | 24           | 4      | B5                              |

| CJNE A, #data, rel    | 3     | 24           | 4      | B4                              |

| CJNE Rn, #data, rel   | 3     | 24           | 4      | B8-BF                           |

| CJNE @Ri, #data, rel  | 3     | 24           | 4      | B6-B7                           |

| DJNZ Rn, rel          | 2     | 24           | 3      | D8-DF                           |

| DJNZ direct, rel      | 3     | 24           | 4      | D5                              |

| NOP                   | 1     | 12           | 1      | 00                              |

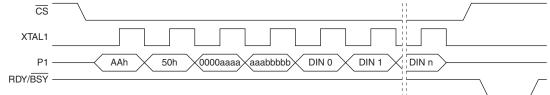

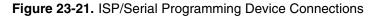

#### 23.4.6 Write Code Page

### Function:

- Programs 1 page (1 to 32 bytes) of data into the Code Memory array.

- Page address determined by bits [11:5] of loaded address.

- The byte address (offset in page) is initialized to bits [4:0] of the low address byte. One byte of data is loaded from P1 for the current address by the positive edge of a XTAL1 pulse. The internal address is incremented by one on the negative edge of the XTAL1 pulse. The address will wrap around to the 1st byte of the page when incremented past 31, however previously loaded bytes should not be re-loaded.

#### Usage:

- 1. Bring  $\overline{CS}$  (P3.2) low.

- 2. Drive P1 to AAh and pulse XTAL1 high.

- 3. Drive P1 to 50h and pulse XTAL1 high.

- 4. Drive P1 with bits [15:8] of address and pulse XTAL1 high.

- 5. Drive P1 with bits [7:0] of address and pulse XTAL1 high.

- 6. To write only previously loaded data, bring CS high before loading additional bytes. To load data bytes, drive data on P1 and pulse XTAL1 high to load one byte and increment to the next address. Repeat for additional bytes. Only 1-32 bytes may be programmed at one time, including any bytes loaded by a previous load page buffer command. Bytes should not be loaded more than once.

- 7. Bring  $\overline{\text{CS}}$  high.

- 8. Wait 2 ms, monitor P3.1, or poll data/status.

- Note: It is not possible to skip bytes while loading data during write. To load non-contiguous bytes in a page, use the Load Page Buffer command.

#### Figure 23-10. Write Code Page Sequence

Note: The waveform on this page is not to scale.

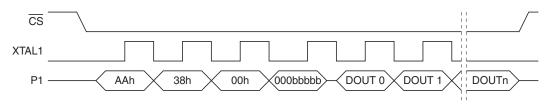

### 23.4.10 Read Atmel Signature Page

## Function:

- Read 1 to 32 bytes of data from the Atmel Signature Row.

- The byte address (offset in page) is initialized to bits [4:0] of the low address byte. The internal address is incremented by one on the negative edge of the XTAL1 pulse. The address will wrap around to the 1st byte of the page when incremented past 31.

- Read data will be output on P1 after the falling edge of fourth XTAL1 pulse (address low byte strobe). The programmer should tri-state P1 prior to this edge to avoid bus contention on P1.

#### Usage:

- 1. Bring  $\overline{CS}$  (P3.2) low.

- 2. Drive P1 to AAh and pulse XTAL1 high.

- 3. Drive P1 to 38h and pulse XTAL1 high.

- 4. Drive P1 to 00h and pulse XTAL1 high.

- 5. Drive P1 with bits [4:0] of address and bring XTAL1 high.

- 6. Tri-state P1.

- 7. Bring XTAL1 low.

- 8. Read data from P1.

- 9. To read additional data bytes in the page, pulse XTAL1 high to increment to the next address.

- 10. Drive CS high.

#### Figure 23-14. Read Atmel Signature Page Sequence

Note: The waveform on this page is not to scale.

Figure 23-20. Flash Programming and Verification Waveforms in Parallel Mode

Note: SCK frequency should be less than 5 MHz.

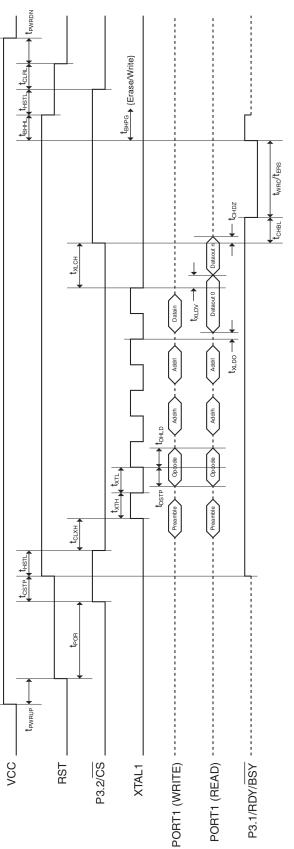

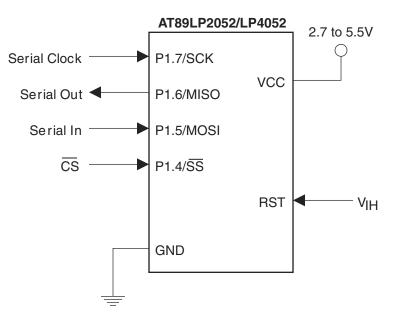

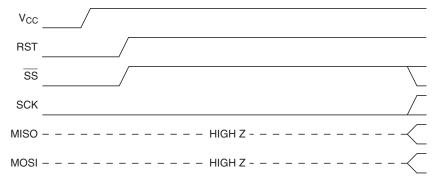

#### 23.5.1 Power-up Sequence

Execute this sequence to power-up the device before serial programming.

- 1. Apply power between VCC and GND pins.

- 2. Keep SCK (P1.7) and SS (P1.4) at "L".

- 3. Wait 10  $\mu$ s and bring RST and  $\overline{SS}$  to "H".

- 4. Wait at least 2 ms for internal Power-on Reset to time out.

#### Figure 23-22. Serial Programming Power-up Sequence

## Figure 24-4. SPI Slave Timing (CPHA = 1)

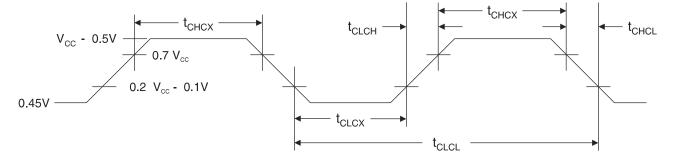

## 24.4 External Clock Drive

## Figure 24-5. External Clock Drive Waveform

#### Table 24-3. External Clock Drive Parameters

|                     |                      | V <sub>CC</sub> = 2.4V |     |       |

|---------------------|----------------------|------------------------|-----|-------|

| Symbol              | Parameter            | Min                    | Мах | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                      | 20  | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 50                     |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 12                     |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 12                     |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                        | 5   | ns    |

| t <sub>CHCL</sub>   | Fall Time            |                        | 5   | ns    |

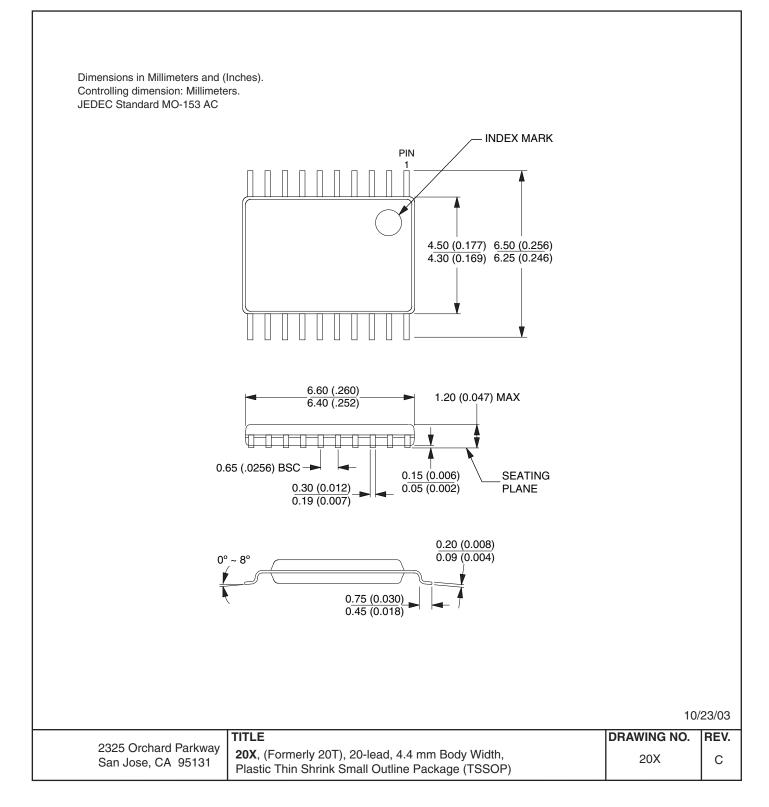

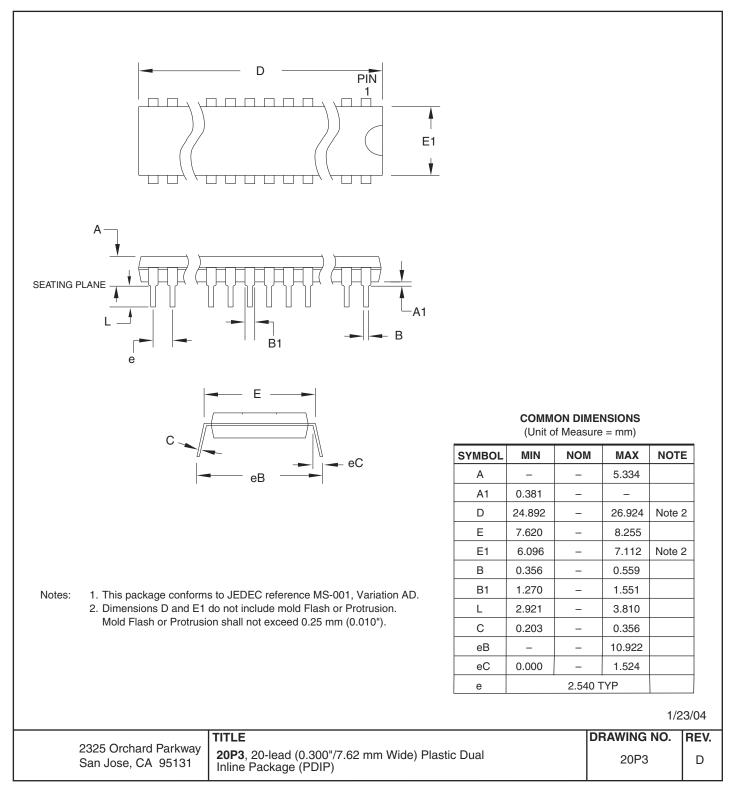

# 26. Packaging Information

# <sup>86</sup> AT89LP2052/LP4052

# 26.3 20X - TSSOP