Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, USB                               |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 33                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 8x12b                                                             |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | 44-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08jm60cld |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

|      | 10.3.2 Status and Control Register 2 (ADCSC2) | .141 |

|------|-----------------------------------------------|------|

|      | 10.3.3 Data Result High Register (ADCRH)      | .141 |

|      | 10.3.4 Data Result Low Register (ADCRL)       | .142 |

|      | 10.3.5 Compare Value High Register (ADCCVH)   | .142 |

|      | 10.3.6 Compare Value Low Register (ADCCVL)    | .143 |

|      | 10.3.7 Configuration Register (ADCCFG)        | .143 |

|      | 10.3.8 Pin Control 1 Register (APCTL1)        | .144 |

|      | 10.3.9 Pin Control 2 Register (APCTL2)        | .145 |

|      | 10.3.10Pin Control 3 Register (APCTL3)        | .146 |

| 10.4 | Functional Description                        | .147 |

|      | 10.4.1 Clock Select and Divide Control        |      |

|      | 10.4.2 Input Select and Pin Control           | .148 |

|      | 10.4.3 Hardware Trigger                       |      |

|      | 10.4.4 Conversion Control                     | .148 |

|      | 10.4.5 Automatic Compare Function             |      |

|      | 10.4.6 MCU Wait Mode Operation                | .151 |

|      | 10.4.7 MCU Stop3 Mode Operation               |      |

|      | 10.4.8 MCU Stop2 Mode Operation               |      |

| 10.5 | Initialization Information                    |      |

|      | 10.5.1 ADC Module Initialization Example      |      |

| 10.6 | Application Information                       | .154 |

|      | 10.6.1 External Pins and Routing              |      |

|      | 10.6.2 Sources of Error                       | .156 |

|      |                                               |      |

## Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 | Introduct | tion                                  | .159 |

|------|-----------|---------------------------------------|------|

|      | 11.1.1    | Features                              | .161 |

|      | 11.1.2    | Modes of Operation                    | .161 |

|      | 11.1.3    | Block Diagram                         | .161 |

| 11.2 | External  | Signal Description                    | .162 |

|      | 11.2.1    | SCL — Serial Clock Line               | .162 |

|      | 11.2.2    | SDA — Serial Data Line                | .162 |

| 11.3 | Register  | Definition                            | .162 |

|      | 11.3.1    | IIC Address Register (IICA)           | .163 |

|      | 11.3.2    | IIC Frequency Divider Register (IICF) | .163 |

|      | 11.3.3    | IIC Control Register (IICC1)          | .166 |

|      | 11.3.4    | IIC Status Register (IICS)            | .166 |

|      | 11.3.5    | IIC Data I/O Register (IICD)          | .167 |

|      | 11.3.6    | IIC Control Register 2 (IICC2)        | .168 |

| 11.4 | Function  | al Description                        | .169 |

|      | 11.4.1    | IIC Protocol                          | .169 |

|      | 11.4.2    | 10-bit Address                        | .172 |

|      | 11.4.3    | General Call Address                  | .173 |

| 11.5 | Resets    |                                       | .173 |

|      |           |                                       |      |

# Chapter 2 Pins and Connections

## 2.1 Introduction

This chapter describes signals that connect to package pins. It includes pinout diagrams, a table of signal properties, and detailed discussion of signals.

| Address<br>(High/Low) | Vector             | Vector Name |

|-----------------------|--------------------|-------------|

| 0xFFCA:FFCB           | ADC Conversion     | Vadc        |

| 0xFFCC:FFCD           | KBI                | Vkeyboard   |

| 0xFFCE:FFCF           | SCI2 Transmit      | Vsci2tx     |

| 0xFFD0:FFD1           | SCI2 Receive       | Vsci2rx     |

| 0xFFD2:FFD3           | SCI2 Error         | Vsci2err    |

| 0xFFD4:FFD5           | SCI1 Transmit      | Vsci1tx     |

| 0xFFD6:FFD7           | SCI1 Receive       | Vsci1rx     |

| 0xFFD8:FFD9           | SCI1 Error         | Vsci1err    |

| 0xFFDA:FFDB           | TPM2 Overflow      | Vtpm2ovf    |

| 0xFFDC:FFDD           | TPM2 Channel 1     | Vtpm2ch1    |

| 0xFFDE:FFDF           | TPM2 Channel 0     | Vtpm2ch0    |

| 0xFFE0:FFE1           | TPM1 Overflow      | Vtpm1ovf    |

| 0xFFE2:FFE3           | TPM1 Channel 5     | Vtpm1ch5    |

| 0xFFE4:FFE5           | TPM1 Channel 4     | Vtpm1ch4    |

| 0xFFE6:FFE7           | TPM1 Channel 3     | Vtpm1ch3    |

| 0xFFE8:FFE9           | TPM1 Channel 2     | Vtpm1ch2    |

| 0xFFEA:FFEB           | TPM1 Channel 1     | Vtpm1ch1    |

| 0xFFEC:FFED           | TPM1 Channel 0     | Vtpm1ch0    |

| 0xFFEE:FFEF           | Reserved           | —           |

| 0xFFF0:FFF1           | USB Status         | Vusb        |

| 0xFFF2:FFF3           | SPI2               | Vspi2       |

| 0xFFF4:FFF5           | SPI1               | Vspi1       |

| 0xFFF6:FFF7           | MCG Loss of Lock   | Vlol        |

| 0xFFF8:FFF9           | Low Voltage Detect | Vlvd        |

| 0xFFFA:FFFB           | IRQ                | Virq        |

| 0xFFFC:FFFD           | SWI                | Vswi        |

| 0xFFFE:FFFF           | Reset              | Vreset      |

## 4.2 Register Addresses and Bit Assignments

The registers in the MC9S08JM60 series are divided into these three groups:

- Direct-page registers are located in the first 176 locations in the memory map, so they are accessible with efficient direct addressing mode instructions.

- High-page registers are used much less often, so they are located above 0x1800 in the memory map. This leaves more room in the direct page for more frequently used registers and variables.

- The nonvolatile register area consists of a block of 16 locations in flash memory at 0xFFB0–0xFFBF.

Nonvolatile register locations include:

- Three values which are loaded into working registers at reset

# Chapter 5 Resets, Interrupts, and System Configuration

## 5.1 Introduction

This chapter discusses basic reset and interrupt mechanisms and the various sources of reset and interrupts in the MC9S08JM60 series. Some interrupt sources from peripheral modules are discussed in greater detail within other chapters of this data manual. This chapter gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog, are not part of on-chip peripheral systems with their own sections but are part of the system control logic.

## 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vectors for each module (reduces polling overhead) (see Table 5-1)

# 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pullup devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The MC9S08JM60 series has seven sources for reset:

- Power-on reset (POR)

- Low-voltage detect (LVD)

- Computer operating properly (COP) timer

- Illegal opcode detect (ILOP)

- Background debug forced reset

- External reset pin (RESET)

- Clock generator loss of lock and loss of clock reset (LOC)

| Field       | Description                                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>IRQACK | <b>IRQ Acknowledge</b> — This write-only bit is used to acknowledge interrupt request events (write 1 to clear IRQF). Writing 0 has no meaning or effect. Reads always return 0. If edge-and-level detection is selected (IRQMOD = 1), IRQF cannot be cleared while the IRQ pin remains at its asserted level.             |

| 1<br>IRQIE  | <ul> <li>IRQ Interrupt Enable — This read/write control bit determines whether IRQ events generate an interrupt request.</li> <li>0 Interrupt request when IRQF set is disabled (use polling).</li> <li>1 Interrupt requested whenever IRQF = 1.</li> </ul>                                                                |

| 0<br>IRQMOD | <ul> <li>IRQ Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. See Section 5.5.2.2, "Edge and Level Sensitivity," for more details.</li> <li>IRQ event on falling/rising edges only.</li> <li>IRQ event on falling/rising edges and low/high levels.</li> </ul> |

#### Table 5-2. IRQSC Register Field Descriptions (continued)

## 5.7.2 System Reset Status Register (SRS)

This register includes seven read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value except 0x55 and 0xAA in sequence to this register address causes the MCU reset with the source of COP. The reset state of these bits depends on what caused the MCU to reset.

|           | 7   | 6   | 5                | 4              | 3              | 2             | 1   | 0 |

|-----------|-----|-----|------------------|----------------|----------------|---------------|-----|---|

| R         | POR | PIN | COP              | ILOP           | 0              | LOC           | LVD | — |

| w         |     | W   | riting any value | e to SRS addre | ess clears COP | watchdog time | ər. |   |

| POR       | 1   | 0   | 0                | 0              | 0              | 0             | 1   | 0 |

| LVR:      | U   | 0   | 0                | 0              | 0              | 0             | 1   | 0 |

| Any other | 0   | (1) | (1)              | (1)            | 0              | (1)           | 0   | 0 |

reset:

U = Unaffected by reset

<sup>1</sup> Any of these reset sources that are active at the time of reset will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset will be cleared.

### Figure 5-3. System Reset Status (SRS)

### Table 5-3. SRS Register Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVR) status bit is also set to indicate that the reset occurred while the internal supply was below the LVR threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul> |

| 6<br>PIN | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                         |

must be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

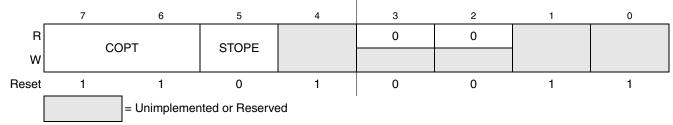

### Figure 5-5. System Options Register (SOPT1)

### Table 5-5. SOPT1 Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>COPT[1:0] | <b>COP Watchdog Timeout</b> — These write-once bits select the timeout period of the COP. COPT along with COPCLKS in SOPT2 defines the COP timeout period. See Table 5-6.                                                                                                                           |

| 5<br>STOPE       | <ul> <li>Stop Mode Enable — This write-once bit defaults to 0 after reset, which disables stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>0 Stop mode disabled.</li> <li>1 Stop mode enabled.</li> </ul> |

### Table 5-6. COP Configuration Options

| Control Bits |           | Clock Source COP Window <sup>1</sup> Opens |                | COP Overflow Count                             |  |  |

|--------------|-----------|--------------------------------------------|----------------|------------------------------------------------|--|--|

| COPCLKS      | COPT[1:0] | - Clock Source                             | (COPW = 1)     | COP Overnow Count                              |  |  |

| N/A          | 0:0       | N/A                                        | N/A            | COP is disabled                                |  |  |

| 0            | 0:1       | 1 kHz LPO<br>clock                         | N/A            | 2 <sup>5</sup> cycles (32 ms <sup>2</sup> )    |  |  |

| 0            | 1:0       | 1 kHz LPO<br>clock                         | N/A            | 2 <sup>8</sup> cycles (256 ms <sup>1</sup> )   |  |  |

| 0            | 1:1       | 1 kHz LPO<br>clock                         | N/A            | 2 <sup>10</sup> cycles (1.024 s <sup>1</sup> ) |  |  |

| 1            | 0:1       | BUSCLK                                     | 6144 cycles    | 2 <sup>13</sup> cycles                         |  |  |

| 1            | 1:0       | BUSCLK                                     | 49,152 cycles  | 2 <sup>16</sup> cycles                         |  |  |

| 1            | 1:1       | BUSCLK                                     | 196,608 cycles | 2 <sup>18</sup> cycles                         |  |  |

<sup>1</sup> Windowed COP operation requires the user to clear the COP timer in the last 25% of the selected timeout period. This column displays the minimum number of clock counts required before the COP timer can be reset when in windowed COP mode (COPW = 1).

<sup>2</sup> Values shown in milliseconds based on t<sub>LPO</sub> = 1 ms. See t<sub>LPO</sub> in the appendix Section A.12.1, "Control Timing," for the tolerance of this value.

#### **Chapter 6 Parallel Input/Output**

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFPE7 | PTFPE6 | PTFPE5 | PTFPE4 | PTFPE3 | PTFPE2 | PTFPE1 | PTFPE0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-29. Internal Pullup Enable for Port F (PTFPE)

### Table 6-28. PTFPE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFPE[7:0] | <ul> <li>Internal Pullup Enable for Port F Bits — Each of these control bits determines if the internal pullup device is enabled for the associated PTF pin. For port F pins that are configured as outputs, these bits have no effect and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled for port F bit n.</li> <li>1 Internal pullup device enabled for port F bit n.</li> </ul> |

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFSE7 | PTFSE6 | PTFSE5 | PTFSE4 | PTFSE3 | PTFSE2 | PTFSE1 | PTFSE0 |

| Reset  | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

### Figure 6-30. Output Slew Rate Control Enable for Port F (PTFSE)

### Table 6-29. PTFSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFSE[7:0] | <ul> <li>Output Slew Rate Control Enable for Port F Bits — Each of these control bits determine whether output slew rate control is enabled for the associated PTF pin. For port F pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port F bit n.</li> <li>Output slew rate control enabled for port F bit n.</li> </ul> |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFDS7 | PTFDS6 | PTFDS5 | PTFDS4 | PTFDS3 | PTFDS2 | PTFDS1 | PTFDS0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-31. Output Drive Strength Selection for Port F (PTFDS)

### Table 6-30. PTFDS Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                         |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTFDS[7:0] | <ul> <li>Output Drive Strength Selection for Port F Bits — Each of these control bits selects between low and high output drive for the associated PTF pin.</li> <li>0 Low output drive enabled for port F bit n.</li> <li>1 High output drive enabled for port F bit n.</li> </ul> |

### MC9S08JM60 Series Data Sheet, Rev. 5

### Chapter 7 Central Processor Unit (S08CPUV2)

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                   | Address<br>Mode                                     | Object Code                                                                      | ject Code                       |                                                  | Affect<br>on CCR |              |  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|------------------|--------------|--|

| Form                                                                                                            |                                                                                                                                                                                             | Ado                                                 |                                                                                  | S                               | Details                                          | VH               | INZC         |  |

| RSP                                                                                                             | Reset Stack Pointer (Low Byte)<br>SPL ← \$FF<br>(High Byte Not Affected)                                                                                                                    | INH                                                 | 9C                                                                               | 1                               | p                                                |                  |              |  |

| RTI                                                                                                             | Return from Interrupt<br>SP ← (SP) + \$0001; Pull (CCR)<br>SP ← (SP) + \$0001; Pull (A)<br>SP ← (SP) + \$0001; Pull (X)<br>SP ← (SP) + \$0001; Pull (PCH)<br>SP ← (SP) + \$0001; Pull (PCL) | INH                                                 | 80                                                                               | 9                               | uuuuufppp                                        | ¢                | \$\$\$<br>\$ |  |

| RTS                                                                                                             | Return from Subroutine<br>SP $\leftarrow$ SP + \$0001; Pull (PCH)<br>SP $\leftarrow$ SP + \$0001; Pull (PCL)                                                                                | INH                                                 | 81                                                                               | 5                               | ufppp                                            |                  |              |  |

| SBC #opr8i<br>SBC opr8a<br>SBC opr16a<br>SBC oprx16,X<br>SBC oprx8,X<br>SBC ,X<br>SBC oprx16,SP<br>SBC oprx8,SP | Subtract with Carry<br>A $\leftarrow$ (A) – (M) – (C)                                                                                                                                       | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A2 ii<br>B2 dd<br>C2 hh ll<br>D2 ee ff<br>E2 ff<br>F2<br>9E D2 ee ff<br>9E E2 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | \$-              | -\$\$\$      |  |

| SEC                                                                                                             | Set Carry Bit $(C \leftarrow 1)$                                                                                                                                                            | INH                                                 | 99                                                                               | 1                               | q                                                |                  | 1            |  |

| SEI                                                                                                             | Set Interrupt Mask Bit $(I \leftarrow 1)$                                                                                                                                                   | INH                                                 | 9в                                                                               | 1                               | р                                                |                  | 1 – – –      |  |

| STA opr8a<br>STA opr16a<br>STA oprx16,X<br>STA oprx8,X<br>STA ,X<br>STA oprx16,SP<br>STA oprx8,SP               | Store Accumulator in Memory $M \leftarrow (A)$                                                                                                                                              | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        | B7 dd<br>C7 hh 11<br>D7 ee ff<br>E7 ff<br>F7<br>9E D7 ee ff<br>9E E7 ff          | 3<br>4<br>4<br>3<br>2<br>5<br>4 | bmbb<br>bmbb<br>bmbb<br>bmbb                     | 0 —              | - ‡ ‡ -      |  |

| STHX <i>opr8a</i><br>STHX <i>opr16a</i><br>STHX <i>oprx8</i> ,SP                                                | Store H:X (Index Reg.)<br>(M:M + \$0001) ← (H:X)                                                                                                                                            | DIR<br>EXT<br>SP1                                   | 35 dd<br>96 hh 11<br>9E FF ff                                                    | 4<br>5<br>5                     | pwwpp<br>pwwpp                                   | 0 –              | - \$ \$ -    |  |

| STOP                                                                                                            | Enable Interrupts: Stop Processing<br>Refer to MCU Documentation<br>I bit ← 0; Stop Processing                                                                                              | INH                                                 | 8E                                                                               | 2                               | fp                                               |                  | 0            |  |

| STX opr8a<br>STX opr16a<br>STX oprx16,X<br>STX oprx8,X<br>STX ,X<br>STX oprx16,SP<br>STX oprx8,SP               | Store X (Low 8 Bits of Index Register)<br>in Memory<br>$M \leftarrow (X)$                                                                                                                   | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        | BF dd<br>CF hh ll<br>DF ee ff<br>EF ff<br>FF<br>9E DF ee ff<br>9E EF ff          | 3<br>4<br>3<br>2<br>5<br>4      | bmbb<br>bbmbb<br>mbb<br>bmbb<br>mbb<br>mbb       | 0 —              | -\$\$-       |  |

|                         |                        |                       |                       |                       |                       | e 7-3. U             | peoue                 |                        |              | 012)                 |                      |                      |                      |                      |                     |

|-------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|-----------------------|------------------------|--------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

|                         | ipulation              | Branch                |                       |                       | d-Modify-W            |                      |                       |                        | ntrol        |                      | -                    |                      | /Memory              |                      |                     |

| 00 5<br>BRSET0<br>3 DIR | 10 5<br>BSET0<br>2 DIR | 20 3<br>BRA<br>2 REL  | 30 5<br>NEG<br>2 DIR  | 40 1<br>NEGA<br>1 INH | 50 1<br>NEGX<br>1 INH | 60 5<br>NEG<br>2 IX1 | NEG<br>1 IX           | RTI<br>1 INH           | BGE<br>2 REL | SUB<br>2 IMM         | B0 3<br>SUB<br>2 DIR | C0 4<br>SUB<br>3 EXT | SUB<br>3 IX2         | SUB<br>2 IX1         | F0 3<br>SUB<br>1 IX |

| 01 5                    | 11 5                   | 21 3                  | 31 5                  | 41 4                  | 51 4                  | 61 5                 | 71 5                  | 81 6                   | BLT          | A1 2                 | B1 3                 | C1 4                 | D1 4                 | E1 3                 | F1 3                |

| BRCLR0                  | BCLR0                  | BRN                   | CBEQ                  | CBEQA                 | CBEQX                 | CBEQ                 | CBEQ                  | RTS                    |              | CMP                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 3 DIR                 | 3 IMM                 | 3 IMM                 | 3 IX1+               | 2 IX+                 | 1 INH                  |              | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 02 5                    | 12 5                   | 22 3                  | 32 5                  | 42 5                  | 52 6                  | 62 1                 | 72 1                  | 82 5+                  | 92 3         | A2 2                 | B2 3                 | C2 4                 | D2 4                 | E2 3                 | F2 3                |

| BRSET1                  | BSET1                  | BHI                   | LDHX                  | MUL                   | DIV                   | NSA                  | DAA                   | BGND                   | BGT          | SBC                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 3 EXT                 | 1 INH                 | 1 INH                 | 1 INH                | 1 INH                 | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 03 5                    | 13 5                   | 23 3                  | 33 5                  | 43 1                  | 53 1                  | 63 5                 | 73 4                  | 83 11                  | 93 3         | A3 2                 | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |

| BRCLR1                  | BCLR1                  | BLS                   | COM                   | COMA                  | COMX                  | COM                  | COM                   | SWI                    | BLE          | CPX                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 04 5                    | 14 5                   | 24 3                  | 34 5                  | 44 1                  | 54 1                  | 64 5                 | 74 4                  | 84 1                   | 94 2         | A4 2                 | B4 3                 | AND                  | D4 4                 | E4 3                 | F4 3                |

| BRSET2                  | BSET2                  | BCC                   | LSR                   | LSRA                  | LSRX                  | LSR                  | LSR                   | TAP                    | TXS          | AND                  | AND                  |                      | AND                  | AND                  | AND                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                |                      | 3 IX2                | 2 IX1                | 1 IX                |

| 05 5                    | 15 5                   | 25 3                  | 35 4                  | 45 3                  | 55 4                  | 65 3                 | 75 5                  | 85 1                   | 95 2         | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                  | BCLR2                  | BCS                   | STHX                  | LDHX                  | LDHX                  | CPHX                 | CPHX                  | TPA                    | TSX          | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 3 IMM                 | 2 DIR                 | 3 IMM                | 2 DIR                 | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                    | 16 5                   | 26 3                  | 36 5                  | 46 1                  | 56 1                  | 66 5                 | 76 4                  | 86 3                   | 96 5         | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                  | BSET3                  | BNE                   | ROR                   | RORA                  | RORX                  | ROR                  | ROR                   | PULA                   | STHX         | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 3 EXT        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                    | 17 5                   | 27 3                  | 37 5                  | 47 1                  | 57 1                  | 67 5                 | 77 4                  | 87 2                   | TAX          | A7 2                 | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                  | BCLR3                  | BEQ                   | ASR                   | ASRA                  | ASRX                  | ASR                  | ASR                   | PSHA                   |              | AIS                  | STA                  | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  |              | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                    | 18 5                   | 28 3                  | 38 5                  | 48 1                  | 58 1                  | 68 5                 | 78 4                  | 88 3                   | 98 1         | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                  | BSET4                  | BHCC                  | LSL                   | LSLA                  | LSLX                  | LSL                  | LSL                   | PULX                   | CLC          | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5<br>BRCLR4<br>3 DIR | 19 5<br>BCLR4<br>2 DIR | 29 3<br>BHCS<br>2 REL | 39 5<br>ROL<br>2 DIR  | 49 1<br>ROLA<br>1 INH | 59 1<br>ROLX<br>1 INH |                      | 79 4<br>ROL<br>1 IX   | 89 2<br>PSHX<br>1 INH  |              | A9 2<br>ADC<br>2 IMM | B9 3<br>ADC<br>2 DIR | C9 4<br>ADC<br>3 EXT | D9 4<br>ADC<br>3 IX2 | E9 3<br>ADC<br>2 IX1 | F9 3<br>ADC<br>1 IX |

| 0A 5                    | 1A 5                   | 2A 3                  | 3A 5                  | 4A 1                  | 5A 1                  | 6A 5                 | 7A 4                  | 8A 3                   | CLI          | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                  | BSET5                  | BPL                   | DEC                   | DECA                  | DECX                  | DEC                  | DEC                   | PULH                   |              | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  |              | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5                    | 1B 5                   | 2B 3                  | 3B 7                  | 4B 4                  | 5B 4                  | 6B 7                 | 7B 6                  | 8B 2                   | 9B 1         | AB 2                 | BB 3                 | ADD                  | DB 4                 | EB 3                 | FB 3                |

| BRCLR5                  | BCLR5                  | BMI                   | DBNZ                  | DBNZA                 | DBNZX                 | DBNZ                 | DBNZ                  | PSHH                   | SEI          | ADD                  | ADD                  |                      | ADD                  | ADD                  | ADD                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 3 DIR                 | 2 INH                 | 2 INH                 | 3 IX1                | 2 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                |                      | 3 IX2                | 2 IX1                | 1 IX                |

| 0C 5                    | 1C 5                   | 2C 3                  | 3C 5                  | 4C 1                  | 5C 1                  | 6C 5                 | 7C 4                  | 8C 1                   | 9C 1         |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                  | BSET6                  | BMC                   | INC                   | INCA                  | INCX                  | INC                  | INC                   | CLRH                   | RSP          |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5                    | 1D 5                   | 2D 3                  | 3D 4                  | 4D 1                  | 5D 1                  | 6D 4                 | <sup>7D</sup> 3       |                        | 9D 1         | AD 5                 | BD 5                 | CD 6                 | DD 6                 | ED 5                 | FD 5                |

| BRCLR6                  | BCLR6                  | BMS                   | TST                   | TSTA                  | TSTX                  | TST                  | TST                   |                        | NOP          | BSR                  | JSR                  | JSR                  | JSR                  | JSR                  | JSR                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  |                        | 1 INH        | 2 REL                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0E 5<br>BRSET7<br>3 DIR | 1E 5<br>BSET7<br>2 DIR | 2E 3<br>BIL<br>2 REL  | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+ | 6E 4<br>MOV<br>3 IMD | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2 | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5                    | 1F 5                   | 2F 3                  | 3F 5                  | 4F 1                  | 5F 1                  | 6F 5                 | 7F 4                  | 8F 2+                  | 9F 1         | AF 2                 | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |

| BRCLR7                  | BCLR7                  | BIH                   | CLR                   | CLRA                  | CLRX                  | CLR                  | CLR                   | WAIT                   | TXA          | AIX                  | STX                  | STX                  | STX                  | STX                  | STX                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

### Table 7-3. Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ REL IX IX1 IX2 IMD DIX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

MC9S08JM60 Series Data Sheet, Rev. 5

Opcode in Hexadecimal F0 3 SUB Instruction Mnemonic 1 IX Addressing Mode Number of Bytes 1

#### Chapter 8 5 V Analog Comparator (S08ACMPV2)

- 3. IRQ does not have a clamp diode to V<sub>DD</sub>. IRQ must not be driven above V<sub>DD</sub>.

- 4. Pin contains integrated pullup device.

- 5. When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pull-down device.

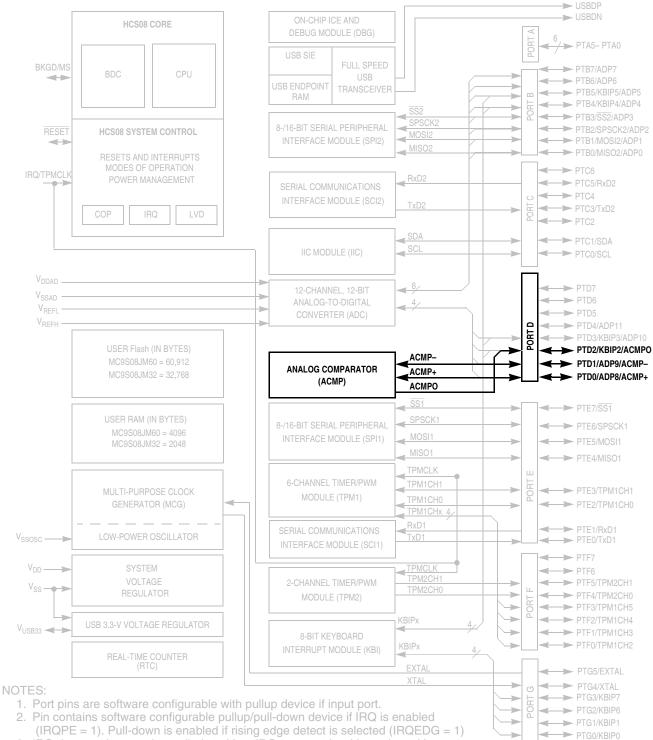

### Figure 8-1. MC9S08JM60 Series Block Diagram Highlighting ACMP Block and Pins

MC9S08JM60 Series Data Sheet, Rev. 5

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

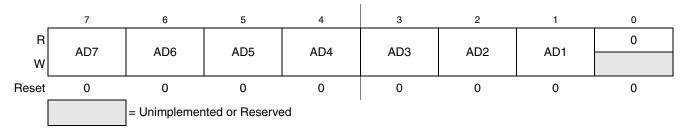

#### 11.3.1 **IIC Address Register (IICA)**

Figure 11-3. IIC Address Register (IICA)

Table 11-1. IICA Field Descriptions

| Field | Description                                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Slave Address.</b> The AD[7:1] field contains the slave address to be used by the IIC module. This field is used on the 7-bit address scheme and the lower seven bits of the 10-bit address scheme. |

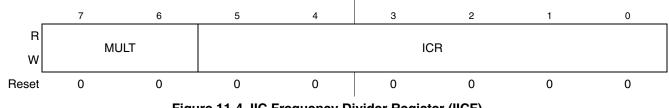

#### **IIC Frequency Divider Register (IICF)** 11.3.2

Figure 11-4. IIC Frequency Divider Register (IICF)

#### NOTES:

- 1. If general call is enabled, a check must be done to determine whether the received address was a general call address (0x00). If the received address was a general call address, then the general call must be handled by user software.

- 2. When 10-bit addressing is used to address a slave, the slave sees an interrupt following the first byte of the extended address.

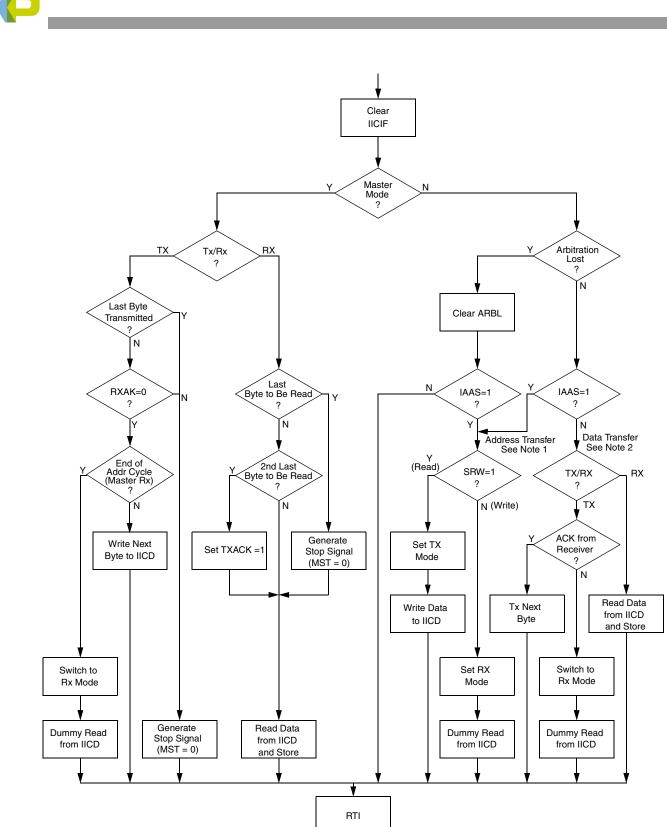

### Figure 11-12. Typical IIC Interrupt Routine

MC9S08JM60 Series Data Sheet, Rev. 5

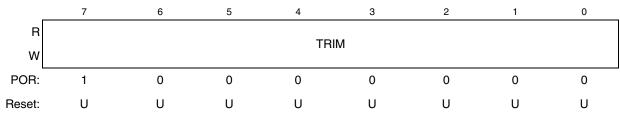

## 12.3.3 MCG Trim Register (MCGTRM)

## Figure 12-5. MCG Trim Register (MCGTRM)

| Table 12-3 | . MCG Trim | Register | Field D | Descriptions |

|------------|------------|----------|---------|--------------|

|------------|------------|----------|---------|--------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>TRIM | MCG <b>Trim Setting</b> — Controls the internal reference clock frequency by controlling the internal reference clock period. The TRIM bits are binary weighted (i.e., bit 1 will adjust twice as much as bit 0). Increasing the binary value in TRIM will increase the period, and decreasing the value will decrease the period. |

|             | An additional fine trim bit is available in MCGSC as the FTRIM bit.                                                                                                                                                                                                                                                                |

|             | If a TRIM[7:0] value stored in nonvolatile memory is to be used, it's the user's responsibility to copy that value from the nonvolatile memory location to this register.                                                                                                                                                          |

## 12.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL or PLL to be disabled and thus conserve power when these systems are not being used. However, in some applications it may be desirable to enable the FLL or PLL and allow it to lock for maximum accuracy before switching to an engaged mode. Do this by writing the LP bit to 0.

## 12.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as MCGIRCLK, which can be used as an additional clock source. The MCGIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the MCGTRM register. Writing a larger value will decrease the MCGIRCLK frequency, and writing a smaller value to the MCGTRM register will increase the MCGIRCLK frequency. The TRIM bits will effect the MCGOUT frequency if the MCG is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or bypassed low power internal (BLPI) mode. The TRIM and FTRIM value is initialized by POR but is not affected by other resets.

Until MCGIRCLK is trimmed, programming low reference divider (RDIV) factors may result in MCGOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN and IRCLKEN bits are both set, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

## 12.4.6 External Reference Clock

The MCG module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in FEE and FBE modes, 1 MHz to 16 MHz in PEE and PBE modes, and 0 to 40 MHz in BLPE mode. When ERCLKEN is set, the external reference clock signal will be presented as MCGERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL or PLL and will only be used as MCGERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

If EREFSTEN and ERCLKEN bits are both set or the MCG is in FEE, FBE, PEE, PBE or BLPE mode, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

If CME bit is written to 1, the clock monitor is enabled. If the external reference falls below a certain frequency ( $f_{loc\_high}$  or  $f_{loc\_low}$  depending on the RANGE bit in the MCGC2), the MCU will reset. The LOC bit in the System Reset Status (SRS) register will be set to indicate the error.

## 12.4.7 Fixed Frequency Clock

The MCG presents the divided reference clock as MCGFFCLK for use as an additional clock source. The MCGFFCLK frequency must be no more than 1/4 of the MCGOUT frequency to be valid. Because of this requirement, the MCGFFCLK is not valid in bypass modes for the following combinations of BDIV and RDIV values:

# 15.4 Functional Description

## 15.4.1 General

The SPI system is enabled by setting the SPI enable (SPE) bit in SPI Control Register 1. While the SPE bit is set, the four associated SPI port pins are dedicated to the SPI function as:

- Slave select  $(\overline{SS})$

- Serial clock (SPSCK)

- Master out/slave in (MOSI)

- Master in/slave out (MISO)

An SPI transfer is initiated in the master SPI device by reading the SPI status register (SPIxS) when SPTEF = 1 and then writing data to the transmit data buffer (write to SPIxDH:SPIxDL). When a transfer is complete, received data is moved into the receive data buffer. The SPIxDH:SPIxDL registers act as the SPI receive data buffer for reads and as the SPI transmit data buffer for writes.

The clock phase control bit (CPHA) and a clock polarity control bit (CPOL) in the SPI Control Register 1 (SPIxC1) select one of four possible clock formats to be used by the SPI system. The CPOL bit simply selects a non-inverted or inverted clock. The CPHA bit is used to accommodate two fundamentally different protocols by sampling data on odd numbered SPSCK edges or on even numbered SPSCK edges.

The SPI can be configured to operate as a master or as a slave. When the MSTR bit in SPI control register 1 is set, master mode is selected, when the MSTR bit is clear, slave mode is selected.

## 15.4.2 Master Mode

The SPI operates in master mode when the MSTR bit is set. Only a master SPI module can initiate transmissions. A transmission begins by reading the SPIxS register while SPTEF = 1 and writing to the master SPI data registers. If the shift register is empty, the byte immediately transfers to the shift register. The data begins shifting out on the MOSI pin under the control of the serial clock.

• SPSCK

The SPR2, SPR1, and SPR0 baud rate selection bits in conjunction with the SPPR2, SPPR1, and SPPR0 baud rate preselection bits in the SPI Baud Rate register control the baud rate generator and determine the speed of the transmission. The SPSCK pin is the SPI clock output. Through the SPSCK pin, the baud rate generator of the master controls the shift register of the slave peripheral.

• MOSI, MISO pin

In master mode, the function of the serial data output pin (MOSI) and the serial data input pin (MISO) is determined by the SPC0 and BIDIROE control bits.

• SS pin

If MODFEN and SSOE bit are set, the  $\overline{SS}$  pin is configured as slave select output. The  $\overline{SS}$  output becomes low during each transmission and is high when the SPI is in idle state.

If MODFEN is set and SSOE is cleared, the  $\overline{SS}$  pin is configured as input for detecting mode fault error. If the  $\overline{SS}$  input becomes low this indicates a mode fault error where another master tries to drive the MOSI

#### Timer/PWM Module (S08TPMV3)

When a channel is configured for edge-aligned PWM (CPWMS=0, MSnB=1 and ELSnB:ELSnA not = 0:0), the data direction is overridden, the TPMxCHn pin is forced to be an output controlled by the TPM, and ELSnA controls the polarity of the PWM output signal on the pin. When ELSnB:ELSnA=1:0, the TPMxCHn pin is forced high at the start of each new period (TPMxCNT=0x0000), and the pin is forced low when the channel value register matches the timer counter. When ELSnA=1, the TPMxCHn pin is forced high when the channel value register matches the timer counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

| TPMxCNTH:TPMxCNTL |   | 0 | 1 | 2 | 3 | 4 | 5      | 6 | 7 | 8 | 0 | 1 | 2 |  |

|-------------------|---|---|---|---|---|---|--------|---|---|---|---|---|---|--|

|                   | Ļ |   |   |   |   |   | Į –    |   |   |   |   |   |   |  |

| TPMxCHn —         |   |   |   |   |   |   |        |   |   |   |   |   |   |  |

| CHnF BIT          | 1 |   |   |   |   |   |        |   |   |   |   |   |   |  |

| TOF BIT           | i |   |   |   |   |   | 1<br>1 |   |   |   |   |   |   |  |

| IOF BIT           | 1 |   |   |   |   |   |        |   |   |   |   |   |   |  |

Figure 16-3. High-True Pulse of an Edge-Aligned PWM

| TPMxCNTH:TPMxCNTL |      | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 0 | 1 | 2 |   |

|-------------------|------|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TPMxCHn           |      |   |   |   |   |   |   |   |   |   |   |   |   |   |

| CHnF BIT          | <br> |   |   |   |   |   |   |   |   |   |   |   |   | _ |

| TOF BIT           | I    |   |   |   |   |   |   |   |   |   |   |   |   |   |

Figure 16-4. Low-True Pulse of an Edge-Aligned PWM

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

Timer/PWM Module (S08TPMV3)

## 16.6.2.2.3 PWM End-of-Duty-Cycle Events

For channels configured for PWM operation there are two possibilities. When the channel is configured for edge-aligned PWM, the channel flag gets set when the timer counter matches the channel value register which marks the end of the active duty cycle period. When the channel is configured for center-aligned PWM, the timer count matches the channel value register twice during each PWM cycle. In this CPWM case, the channel flag is set at the start and at the end of the active duty cycle period which are the times when the timer counter matches the channel value register. The flag is cleared by the two-step sequence described Section 16.6.2, "Description of Interrupt Operation."

| USB RAM<br>Offset | USB RAM Description of Contents        |                         |  |  |  |  |  |  |

|-------------------|----------------------------------------|-------------------------|--|--|--|--|--|--|

| 0x00              |                                        | Endpoint 0 IN           |  |  |  |  |  |  |

|                   |                                        | Endpoint 0, OUT         |  |  |  |  |  |  |

|                   |                                        | Endpoint 1              |  |  |  |  |  |  |

|                   |                                        | Endpoint 2              |  |  |  |  |  |  |

|                   | BDT                                    | Endpoint 3              |  |  |  |  |  |  |

|                   | 661                                    | Endpoint 4              |  |  |  |  |  |  |

|                   |                                        | Endpoint 5, Buffer EVEN |  |  |  |  |  |  |

|                   |                                        | Endpoint 5, Buffer ODD  |  |  |  |  |  |  |

|                   |                                        | Endpoint 6, Buffer EVEN |  |  |  |  |  |  |

| 0x1D              |                                        | Endpoint 6, Buffer ODD  |  |  |  |  |  |  |

| 0x1E              | RESERVED<br>RESERVED                   |                         |  |  |  |  |  |  |

| 0x1F              |                                        |                         |  |  |  |  |  |  |

| 0x20              | USB RAM available for endpoint buffers |                         |  |  |  |  |  |  |

| 0xFF              |                                        |                         |  |  |  |  |  |  |

### Table 17-21. USB RAM Organization

When the USB module receives a USB token on an enabled endpoint, it interrogates the BDT. The USB module reads the corresponding endpoint BD entry and determines if it owns the BD and corresponding data buffer.

## 17.4.2.3 Buffer Descriptor Formats

The buffer descriptors (BDs) are groups of registers that provide endpoint buffer control information for the USB module and the MCU. The BDs have different meanings based on who is reading the BD in memory.

The USB module uses the data stored in the BDs to determine:

- Who owns the buffer in system memory

- Data0 or Data1 PID

- Release Own upon packet completion

- Data toggle synchronization enable

- How much data to be transmitted or received

- Where the buffer resides in the buffer RAM.

The microcontroller uses the data stored in the BDs to determine:

- Who owns the buffer in system memory

- Data0 or Data1 PID

- The received TOKEN PID

appropriate course of action for future transactions — stalling the endpoint, canceling the transfer, disabling the endpoint, etc.

## 17.4.4 USB Packet Processing

Packet processing for a USB device consists of managing buffers for IN (to the USB Host) and OUT (to the USB device) transactions. Packet processing is further divided into request processing on Endpoint 0, and data packet processing on the data endpoints.

## 17.4.4.1 USB Data Pipe Processing

Data pipe processing is essentially a buffer management task. The firmware is responsible for managing the shared buffer RAM to ensure that a BD is always ready for the hardware to process (OWN bit = 1).

The device allocates buffers within the shared RAM, sets up the buffer descriptors, and waits for interrupts. On receipt of a TOKDNE interrupt, the firmware reads the STAT register to determine which endpoint is affected, then reads the corresponding BDT entry to determine what to do next.

When processing data packets, firmware is responsible for managing the size of the packet buffers to be in compliance with the USB specification, and the physical limitations of this module. Packet sizes up to 64 bytes are supported on all endpoints. Isochronous endpoints also can only specify packet sizes up to 64 bytes.

Firmware is also responsible for setting the appropriate bits in the BDT. For most applications using bulk packets (control, bulk, and interrupt-type transfers), the firmware will set the DTS, BC and EPADR fields for each BD. For isochronous packets, firmware will set BC and EPADR fields. In all cases, firmware will set the OWN bit to enable the endpoint for data transfers.

## 17.4.4.2 Request Processing on Endpoint 0

In most cases, commands to the USB device are directed to Endpoint 0. The host uses the "Standard Requests" described in Chapter 9 of the USB specification to enumerate and configure the device. Class drivers or product specific drivers running on the host send class (HID, Mass Storage, Imaging) and vendor specific commands to the device on endpoint 0.

USB requests always follow a specific format:

- Host sends a SETUP token, followed by an 8-byte setup packet, and the device hardware can send a handshake packet.

- If the setup packet specifies a data phase, the host and device may transfer up to 64 Kbytes of data (either IN or OUT, not both).

- The request is terminated by a status phase.

Device firmware monitors the INTSTAT and STAT registers, the endpoint 0 buffer descriptors (BD's), and the contents of the setup packet to correctly execute the host's request.

The flow for processing endpoint 0 requests is as follows:

1. Allocate 8-byte buffers for endpoint 0 OUT.

### Development Support

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

## 18.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.