#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | C166                                                                          |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 25MHz                                                                         |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 76                                                                            |

| Program Memory Size        | - ·                                                                           |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 3K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 4x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-BQFP                                                                      |

| Supplier Device Package    | PG-MQFP-100-2                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c161pil25mcabxuma1 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C161PI

### Introduction

The C161PI is a derivative of the Infineon C166 Family of 16-bit single-chip CMOS microcontrollers. It combines high CPU performance (up to 8 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. The C161PI derivative is especially suited for cost sensitive applications.

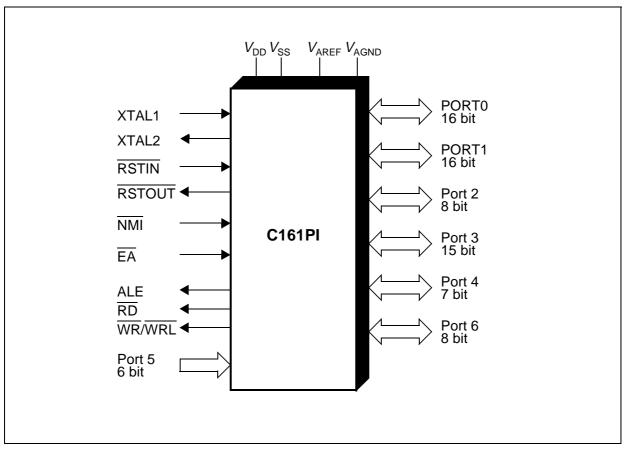

### Figure 1 Logic Symbol

| Table 1   | Pin Definitions and Functions (continued) |                     |                |                                                                                                                                                                                                                                                                                         |                  |                       |  |  |  |  |

|-----------|-------------------------------------------|---------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|--|--|--|--|

| Symbol    | Pin<br>Num.<br>TQFP                       | Pin<br>Num.<br>MQFP | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                |                  |                       |  |  |  |  |

| ĒĀ        | 35                                        | 37                  | I              | External Access Enable pin. A low level at this pin<br>during and after Reset forces the C161PI to begin<br>instruction execution out of external memory. A high<br>level forces execution out of the internal program<br>memory.<br>"ROMless" versions must have this pin tied to '0'. |                  |                       |  |  |  |  |

| PORT0     |                                           |                     | 10             | PORT0 consists of                                                                                                                                                                                                                                                                       | the two 8-bit bi | directional I/O ports |  |  |  |  |

| P0L.0-7   | 38-<br>45                                 | 40-<br>47           |                | P0L and P0H. It is b<br>output via direction                                                                                                                                                                                                                                            |                  | •                     |  |  |  |  |

| P0H.0-7   | 48-                                       | 50-                 |                | the output driver is p                                                                                                                                                                                                                                                                  | •                | <b>.</b>              |  |  |  |  |

|           | 55                                        | 57                  |                | In case of external b                                                                                                                                                                                                                                                                   | •                |                       |  |  |  |  |

|           |                                           |                     |                | as the address (A) a                                                                                                                                                                                                                                                                    |                  |                       |  |  |  |  |

|           |                                           |                     |                | multiplexed bus model<br>demultiplexed bus r                                                                                                                                                                                                                                            |                  | data (D) bus in       |  |  |  |  |

|           |                                           |                     |                | Demultiplexed bus                                                                                                                                                                                                                                                                       |                  |                       |  |  |  |  |

|           |                                           |                     |                | Data Path Width:                                                                                                                                                                                                                                                                        | 8-bit            | 16-bit                |  |  |  |  |

|           |                                           |                     |                | P0L.0 – P0L.7:                                                                                                                                                                                                                                                                          | D0 – D7          | D0 - D7               |  |  |  |  |

|           |                                           |                     |                | P0H.0 – P0H.7:<br>Multiplexed bus m                                                                                                                                                                                                                                                     | I/O<br>adas:     | D8 - D15              |  |  |  |  |

|           |                                           |                     |                | Data Path Width:                                                                                                                                                                                                                                                                        | 8-bit            | 16-bit                |  |  |  |  |

|           |                                           |                     |                | P0L.0 – P0L.7:                                                                                                                                                                                                                                                                          | AD0 – AD7        | AD0 - AD7             |  |  |  |  |

|           |                                           |                     |                | P0H.0 – P0H.7:                                                                                                                                                                                                                                                                          | A8 - A15         | AD8 - AD15            |  |  |  |  |

| PORT1     |                                           |                     | IO             | PORT1 consists of                                                                                                                                                                                                                                                                       | the two 8-bit bi | directional I/O ports |  |  |  |  |

| P1L.0-7   | 56-                                       | 58-                 |                | P1L and P1H. It is b                                                                                                                                                                                                                                                                    |                  | •                     |  |  |  |  |

| P1H.0-7   | 63<br>66-                                 | 65<br>68-           |                | output via direction<br>the output driver is p                                                                                                                                                                                                                                          | •                | <b>u</b>              |  |  |  |  |

| 1 111.0-7 | 73                                        | 75                  |                | PORT1 is used as t                                                                                                                                                                                                                                                                      | -                | •                     |  |  |  |  |

|           | -                                         |                     |                | demultiplexed bus m                                                                                                                                                                                                                                                                     |                  |                       |  |  |  |  |

|           |                                           |                     |                | a demultiplexed bus                                                                                                                                                                                                                                                                     | s mode to a mu   | Iltiplexed bus mode.  |  |  |  |  |

# **External Bus Controller**

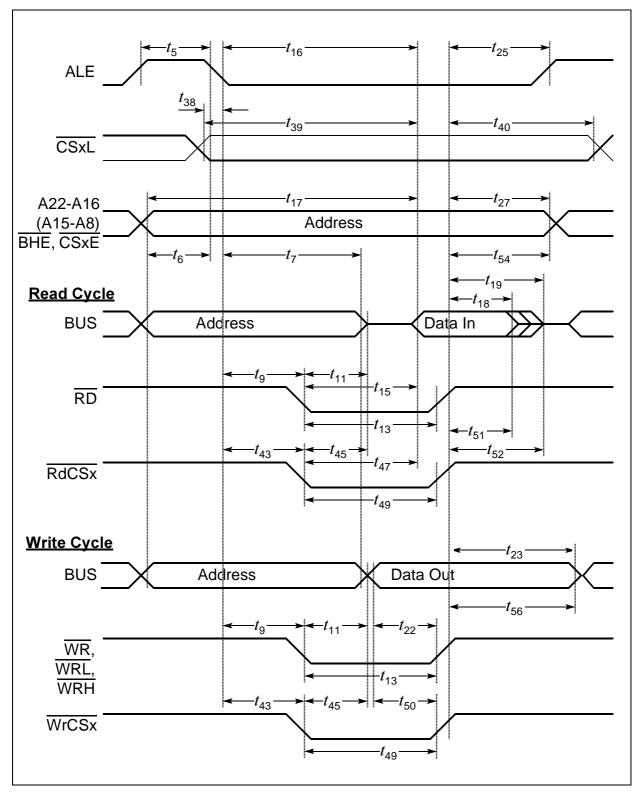

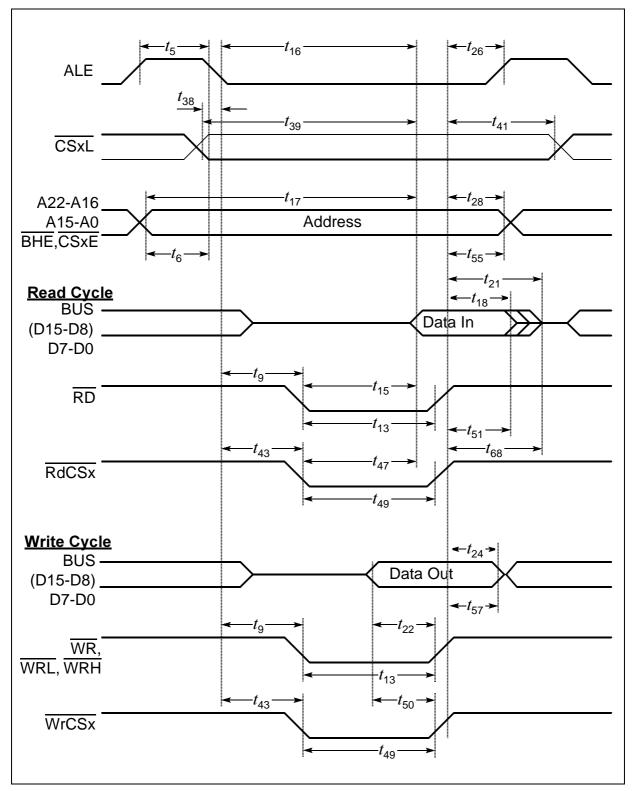

All of the external memory accesses are performed by a particular on-chip External Bus Controller (EBC). It can be programmed either to Single Chip Mode when no external memory is required, or to one of four different external memory access modes, which are as follows:

- 16-/18-/20-/23-bit Addresses, 16-bit Data, Demultiplexed

- 16-/18-/20-/23-bit Addresses, 16-bit Data, Multiplexed

- 16-/18-/20-/23-bit Addresses, 8-bit Data, Multiplexed

- 16-/18-/20-/23-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/ output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output.

Important timing characteristics of the external bus interface (Memory Cycle Time, Memory Tri-State Time, Length of ALE and Read Write Delay) have been made programmable to allow the user the adaption of a wide range of different types of memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via register pairs ADDRSELx / BUSCONx) which allow to access different resources with different bus characteristics. These address windows are arranged hierarchically where BUSCON4 overrides BUSCON3 and BUSCON2 overrides BUSCON1. All accesses to locations not covered by these 4 address windows are controlled by BUSCON0.

Up to 5 external  $\overline{CS}$  signals (4 windows plus default) can be generated in order to save external glue logic. The C161PI offers the possibility to switch the  $\overline{CS}$  outputs to an unlatched mode. In this mode the internal filter logic is switched off and the  $\overline{CS}$  signals are directly generated from the address. The unlatched  $\overline{CS}$  mode is enabled by setting CSCFG (SYSCON.6).

Access to very slow memories is supported via a particular 'Ready' function.

For applications which require less than 8 MBytes of external memory space, this address space can be restricted to 1 MByte, 256 KByte or to 64 KByte. In this case Port 4 outputs four, two or no address lines at all. It outputs all 7 address lines, if an address space of 8 MBytes is used.

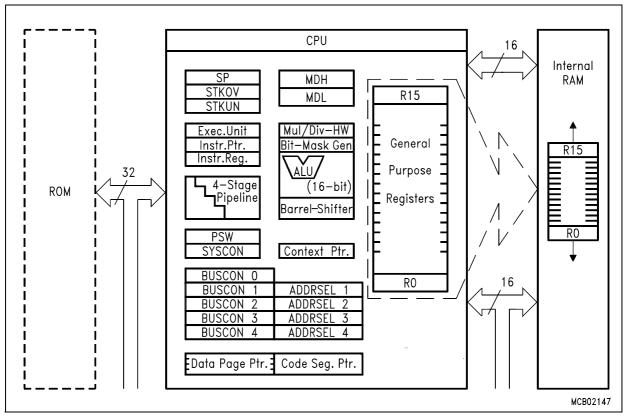

# **Central Processing Unit (CPU)**

The main core of the CPU consists of a 4-stage instruction pipeline, a 16-bit arithmetic and logic unit (ALU) and dedicated SFRs. Additional hardware has been spent for a separate multiply and divide unit, a bit-mask generator and a barrel shifter.

Based on these hardware provisions, most of the C161PI's instructions can be executed in just one machine cycle which requires 2 CPU clocks (4 TCL). For example, shift and rotate instructions are always processed during one machine cycle independent of the number of bits to be shifted. All multiple-cycle instructions have been optimized so that they can be executed very fast as well: branches in 2 cycles, a  $16 \times 16$  bit multiplication in 5 cycles and a 32-/16 bit division in 10 cycles. Another pipeline optimization, the so-called 'Jump Cache', reduces the execution time of repeatedly performed jumps in a loop from 2 cycles to 1 cycle.

Figure 5 CPU Block Diagram

# Table 2 C161PI Interrupt Nodes

| Source of Interrupt or PEC Service Request | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location   | Trap<br>Number  |

|--------------------------------------------|-----------------|----------------|---------------------|----------------------|-----------------|

| External Interrupt 0                       | CC8IR           | CC8IE          | CC8INT              | 00'0060 <sub>H</sub> | 18 <sub>H</sub> |

| External Interrupt 1                       | CC9IR           | CC9IE          | CC9INT              | 00'0064 <sub>H</sub> | 19 <sub>H</sub> |

| External Interrupt 2                       | CC10IR          | CC10IE         | CC10INT             | 00'0068 <sub>H</sub> | 1A <sub>H</sub> |

| External Interrupt 3                       | CC11IR          | CC11IE         | CC11INT             | 00'006C <sub>H</sub> | 1B <sub>H</sub> |

| External Interrupt 4                       | CC12IR          | CC12IE         | CC12INT             | 00'0070 <sub>H</sub> | 1C <sub>H</sub> |

| External Interrupt 5                       | CC13IR          | CC13IE         | CC13INT             | 00'0074 <sub>H</sub> | 1D <sub>H</sub> |

| External Interrupt 6                       | CC14IR          | CC14IE         | CC14INT             | 00'0078 <sub>H</sub> | 1E <sub>H</sub> |

| External Interrupt 7                       | CC15IR          | CC15IE         | CC15INT             | 00'007C <sub>H</sub> | 1F <sub>H</sub> |

| GPT1 Timer 2                               | T2IR            | T2IE           | T2INT               | 00'0088 <sub>H</sub> | 22 <sub>H</sub> |

| GPT1 Timer 3                               | T3IR            | T3IE           | T3INT               | 00'008C <sub>H</sub> | 23 <sub>H</sub> |

| GPT1 Timer 4                               | T4IR            | T4IE           | T4INT               | 00'0090 <sub>H</sub> | 24 <sub>H</sub> |

| GPT2 Timer 5                               | T5IR            | T5IE           | T5INT               | 00'0094 <sub>H</sub> | 25 <sub>H</sub> |

| GPT2 Timer 6                               | T6IR            | T6IE           | T6INT               | 00'0098 <sub>H</sub> | 26 <sub>H</sub> |

| GPT2 CAPREL<br>Register                    | CRIR            | CRIE           | CRINT               | 00'009C <sub>H</sub> | 27 <sub>H</sub> |

| A/D Conversion<br>Complete                 | ADCIR           | ADCIE          | ADCINT              | 00'00A0 <sub>H</sub> | 28 <sub>H</sub> |

| A/D Overrun Error                          | ADEIR           | ADEIE          | ADEINT              | 00'00A4 <sub>H</sub> | 29 <sub>H</sub> |

| ASC0 Transmit                              | SOTIR           | SOTIE          | SOTINT              | 00'00A8 <sub>H</sub> | 2A <sub>H</sub> |

| ASC0 Transmit Buffer                       | S0TBIR          | S0TBIE         | <b>S0TBINT</b>      | 00'011C <sub>H</sub> | 47 <sub>H</sub> |

| ASC0 Receive                               | SORIR           | SORIE          | SORINT              | 00'00AC <sub>H</sub> | 2B <sub>H</sub> |

| ASC0 Error                                 | S0EIR           | SOEIE          | SOEINT              | 00'00B0 <sub>H</sub> | 2C <sub>H</sub> |

| SSC Transmit                               | SCTIR           | SCTIE          | SCTINT              | 00'00B4 <sub>H</sub> | 2D <sub>H</sub> |

| SSC Receive                                | SCRIR           | SCRIE          | SCRINT              | 00'00B8 <sub>H</sub> | 2E <sub>H</sub> |

| SSC Error                                  | SCEIR           | SCEIE          | SCEINT              | 00'00BC <sub>H</sub> | 2F <sub>H</sub> |

| I <sup>2</sup> C Data Transfer<br>Event    | XP0IR           | XP0IE          | XP0INT              | 00'0100 <sub>H</sub> | 40 <sub>H</sub> |

| I <sup>2</sup> C Protocol Event            | XP1IR           | XP1IE          | XP1INT              | 00'0104 <sub>H</sub> | 41 <sub>H</sub> |

| X-Peripheral Node 2                        | XP2IR           | XP2IE          | XP2INT              | 00'0108 <sub>H</sub> | 42 <sub>H</sub> |

| PLL Unlock / RTC                           | XP3IR           | XP3IE          | XP3INT              | 00'010C <sub>H</sub> | 43 <sub>H</sub> |

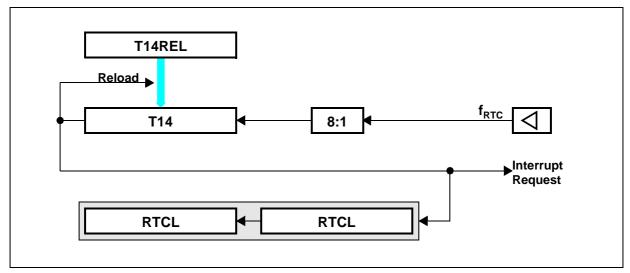

# **Real Time Clock**

The Real Time Clock (RTC) module of the C161PI consists of a chain of 3 divider blocks, a fixed 8:1 divider, the reloadable 16-bit timer T14, and the 32-bit RTC timer (accessible via registers RTCH and RTCL). The RTC module is directly clocked with the on-chip oscillator frequency divided by 32 via a separate clock driver ( $f_{\rm RTC} = f_{\rm OSC}$  / 32) and is therefore independent from the selected clock generation mode of the C161PI. All timers count up.

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time based interrupt

- 48-bit timer for long term measurements

Figure 8 RTC Block Diagram

Note: The registers associated with the RTC are not effected by a reset in order to maintain the correct system time even when intermediate resets are executed.

### A/D Converter

For analog signal measurement, a 10-bit A/D converter with 4 multiplexed input channels and a sample and hold circuit has been integrated on-chip. It uses the method of successive approximation. The sample time (for loading the capacitors) and the conversion time is programmable and can so be adjusted to the external circuitry.

Overrun error detection/protection is provided for the conversion result register (ADDAT): either an interrupt request will be generated when the result of a previous conversion has not been read from the result register at the time the next conversion is complete, or the next conversion is suspended in such a case until the previous result has been read.

For applications which require less than 4 analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converter of the C161PI supports four different conversion modes. In the standard Single Channel conversion mode, the analog level on a specified channel is sampled once and converted to a digital result. In the Single Channel Continuous mode, the analog level on a specified channel is repeatedly sampled and converted without software intervention. In the Auto Scan mode, the analog levels on a prespecified number of channels are sequentially sampled and converted. In the Auto Scan Continuous mode, the number of prespecified channels is repeatedly sampled and converted and converted and converted. In the Auto Scan Continuous mode, the number of a specific channels is repeatedly sampled and converted in a running sequence without disturbing this sequence. This is called Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the conversion results into a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer.

After each reset and also during normal operation the ADC automatically performs calibration cycles. This automatic self-calibration constantly adjusts the converter to changing operating conditions (e.g. temperature) and compensates process variations.

These calibration cycles are part of the conversion cycle, so they do not affect the normal operation of the A/D converter.

In order to decouple analog inputs from digital noise and to avoid input trigger noise those pins used for analog input can be disconnected from the digital IO or input stages under software control. This can be selected for each pin separately via registers P5DIDIS (Port 5 Digital Input Disable).

# I<sup>2</sup>C Module

The integrated  $I^2C$  Bus Module handles the transmission and reception of frames over the two-line  $I^2C$  bus in accordance with the  $I^2C$  Bus specification. The on-chip  $I^2C$  Module can receive and transmit data using 7-bit or 10-bit addressing and it can operate in slave mode, in master mode or in multi-master mode.

Several physical interfaces (port pins) can be established under software control. Data can be transferred at speeds up to 400 Kbit/sec.

Two interrupt nodes dedicated to the I<sup>2</sup>C module allow efficient interrupt service and also support operation via PEC transfers.

Note: The port pins associated with the  $l^2C$  interfaces feature open drain drivers only, as required by the  $l^2C$  specification.

# Watchdog Timer

The Watchdog Timer represents one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after a reset of the chip, and can only be disabled in the time interval until the EINIT (end of initialization) instruction has been executed. Thus, the chip's start-up procedure is always monitored. The software has to be designed to service the Watchdog Timer before it overflows. If, due to hardware or software related failures, the software fails to do so, the Watchdog Timer overflows and generates an internal hardware reset and pulls the RSTOUT pin low in order to allow external hardware components to be reset.

The Watchdog Timer is a 16-bit timer, clocked with the system clock divided either by 2 or by 128. The high byte of the Watchdog Timer register can be set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the high byte of the Watchdog Timer is reloaded. Thus, time intervals between 20 µs and 336 ms can be monitored (@ 25 MHz).

The default Watchdog Timer interval after reset is 5.24 ms (@ 25 MHz).

# **Parallel Ports**

The C161PI provides up to 76 IO lines which are organized into six input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of three IO ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. The other IO ports operate in push/pull mode, except for the I<sup>2</sup>C interface pins which are open drain pins only. During the internal reset, all port pins are configured as inputs.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

PORT0 and PORT1 may be used as address and data lines when accessing external memory, while Port 4 outputs the additional segment address bits A22/19/17...A16 in systems where segmentation is enabled to access more than 64 KBytes of memory.

Port 3 includes alternate functions of timers, serial interfaces, the optional bus control signal BHE and the system clock output CLKOUT (or the programmable frequency output FOUT).

Port 5 is used for the analog input channels to the A/D converter or timer control signals.

Port 6 provides the optional chip select signals and interface lines for the I<sup>2</sup>C module.

The edge characteristics (transition time) of the C161PI's port drivers can be selected via the Port Driver Control Register (PDCR).

### **Special Function Registers Overview**

The following table lists all SFRs which are implemented in the C161PI in alphabetical order.

**Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-Peripherals (I<sup>2</sup>C) are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

| Name     |    | Physical<br>Address | 8-Bit<br>Addr.  | Description                                                   | Reset<br>Value    |

|----------|----|---------------------|-----------------|---------------------------------------------------------------|-------------------|

| ADCIC    | b  | FF98 <sub>H</sub>   | CC <sub>H</sub> | A/D Converter End of Conversion<br>Interrupt Control Register | 0000 <sub>H</sub> |

| ADCON    | b  | FFA0 <sub>H</sub>   | D0 <sub>H</sub> | A/D Converter Control Register                                | 0000 <sub>H</sub> |

| ADDAT    |    | FEA0 <sub>H</sub>   | 50 <sub>H</sub> | A/D Converter Result Register                                 | 0000 <sub>H</sub> |

| ADDAT2   |    | F0A0 <sub>H</sub> E | 50 <sub>H</sub> | A/D Converter 2 Result Register                               | 0000 <sub>H</sub> |

| ADDRSEL1 |    | FE18 <sub>H</sub>   | 0C <sub>H</sub> | Address Select Register 1                                     | 0000 <sub>H</sub> |

| ADDRSEL2 | 2  | FE1A <sub>H</sub>   | 0D <sub>H</sub> | Address Select Register 2                                     | 0000 <sub>H</sub> |

| ADDRSEL3 | \$ | FE1C <sub>H</sub>   | 0E <sub>H</sub> | Address Select Register 3                                     | 0000 <sub>H</sub> |

| ADDRSEL4 | ŀ  | FE1E <sub>H</sub>   | 0F <sub>H</sub> | Address Select Register 4                                     | 0000 <sub>H</sub> |

| ADEIC    | b  | FF9A <sub>H</sub>   | CD <sub>H</sub> | A/D Converter Overrun Error Interrupt<br>Control Register     | 0000 <sub>H</sub> |

| BUSCON0  | b  | FF0C <sub>H</sub>   | 86 <sub>H</sub> | Bus Configuration Register 0                                  | 0000 <sub>H</sub> |

| BUSCON1  | b  | FF14 <sub>H</sub>   | 8A <sub>H</sub> | Bus Configuration Register 1                                  | 0000 <sub>H</sub> |

| BUSCON2  | b  | FF16 <sub>H</sub>   | 8B <sub>H</sub> | Bus Configuration Register 2                                  | 0000 <sub>H</sub> |

| BUSCON3  | b  | FF18 <sub>H</sub>   | 8C <sub>H</sub> | Bus Configuration Register 3                                  | 0000 <sub>H</sub> |

| BUSCON4  | b  | FF1A <sub>H</sub>   | 8D <sub>H</sub> | Bus Configuration Register 4                                  | 0000 <sub>H</sub> |

| CAPREL   |    | FE4A <sub>H</sub>   | 25 <sub>H</sub> | GPT2 Capture/Reload Register                                  | 0000 <sub>H</sub> |

| CC8IC    | b  | FF88 <sub>H</sub>   | C4 <sub>H</sub> | External Interrupt 0 Control Register                         | 0000 <sub>H</sub> |

| CC9IC    | b  | FF8A <sub>H</sub>   | C5 <sub>H</sub> | External Interrupt 1 Control Register                         | 0000 <sub>H</sub> |

| CC10IC   | b  | FF8C <sub>H</sub>   | C6 <sub>H</sub> | External Interrupt 2 Control Register                         | 0000 <sub>H</sub> |

| CC11IC   | b  | FF8E <sub>H</sub>   | C7 <sub>H</sub> | External Interrupt 3 Control Register                         | 0000 <sub>H</sub> |

### Table 5 C161PI Registers, Ordered by Name

| NamePhysical<br>Address8-Bit<br>Addr.DescriptionReset<br>ValueCC12ICbFF99 <sub>H</sub> C8 <sub>H</sub> External Interrupt 4 Control Register0000 <sub>H</sub> CC13ICbFF92 <sub>H</sub> C9 <sub>H</sub> External Interrupt 5 Control Register0000 <sub>H</sub> CC14ICbFF94 <sub>H</sub> CA <sub>H</sub> External Interrupt 6 Control Register0000 <sub>H</sub> CC15ICbFF96 <sub>H</sub> CB <sub>H</sub> External Interrupt 7 Control Register0000 <sub>H</sub> CC15ICbFF96 <sub>H</sub> CB <sub>H</sub> External Interrupt 7 Control Register0000 <sub>H</sub> CRIbFF6A <sub>H</sub> B5 <sub>H</sub> GPT2 CAPREL Interrupt Ctrl. Register0000 <sub>H</sub> CSPFE08 <sub>H</sub> 04 <sub>H</sub> CPU Code Segment Pointer Register000 <sub>H</sub> DP0LbF100 <sub>H</sub> E80 <sub>H</sub> POL Direction Control Register000 <sub>H</sub> DP1LbF104 <sub>H</sub> E82 <sub>H</sub> P1L Direction Control Register000 <sub>H</sub> DP1LbF104 <sub>H</sub> E83 <sub>H</sub> P1H Direction Control Register000 <sub>H</sub> DP1LbF104 <sub>H</sub> E83 <sub>H</sub> P1H Direction Control Register000 <sub>H</sub> DP1LbF104 <sub>H</sub> E83 <sub>H</sub> P1H Direction Control Register000 <sub>H</sub> DP1LbF104 <sub>H</sub> E83 <sub>H</sub> P1H Direction Control Register000 <sub>H</sub> DP1bF104 <sub>H</sub> E83 <sub>H</sub> P1H Direction Control Register000 <sub>H</sub> DP2bFFC2 <sub>H</sub> E1 <sub>H</sub> Port 2 Direction Control Register000 <sub>H</sub> DP3bFFC6 <sub>H</sub> E3 <sub>H</sub> <td< th=""><th>Table 5</th><th>(</th><th>C161PI R</th><th>egi</th><th>sters, C</th><th>Ordered by Name (continued)</th><th></th></td<> | Table 5 | ( | C161PI R          | egi | sters, C        | Ordered by Name (continued)              |                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---|-------------------|-----|-----------------|------------------------------------------|-------------------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Name    |   | -                 |     |                 | Description                              |                   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CC12IC  | b | FF90 <sub>H</sub> |     | C8 <sub>H</sub> | External Interrupt 4 Control Register    | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CC13IC  | b | FF92 <sub>H</sub> |     | C9 <sub>H</sub> | External Interrupt 5 Control Register    | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CC14IC  | b | FF94 <sub>H</sub> |     | $CA_{H}$        | External Interrupt 6 Control Register    | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CC15IC  | b | FF96 <sub>H</sub> |     | $CB_H$          | External Interrupt 7 Control Register    | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | СР      |   | FE10 <sub>H</sub> |     | 08 <sub>H</sub> | CPU Context Pointer Register             | FC00 <sub>H</sub> |

| DPOLbF100 <sub>H</sub> E $80_H$ POL Direction Control Register $00_H$ DPOHbF102 <sub>H</sub> E $81_H$ POH Direction Control Register $00_H$ DP1LbF104 <sub>H</sub> E $82_H$ P1L Direction Control Register $00_H$ DP1HbF106_HE $83_H$ P1H Direction Control Register $00_H$ DP2bFFC2_HE1_HPort 2 Direction Control Register $000_H$ DP3bFFC6_HE3_HPort 3 Direction Control Register $0000_H$ DP4bFFC6_HE5_HPort 4 Direction Control Register $000_H$ DP6bFFCE_HE7_HPort 6 Direction Control Register $000_H$ DP6bFFCE_HE7_HPort 6 Direction Control Register $000_H$ DP7FE00_H $00_H$ CPU Data Page Pointer 0 Register (10) $0000_H$ DP90FE02_H01_HCPU Data Page Pointer 2 Reg. (10 bits) $0001_H$ DP91FE02_H $01_H$ CPU Data Page Pointer 3 Reg. (10 bits) $0002_H$ DP93FE06_H $03_H$ CPU Data Page Pointer 3 Reg. (10 bits) $0003_H$ EXICONbF1C0_HEE0_HExternal Interrupt Control Register $0000_H$ ICADRED06_HXI²C Address Register $0XXX_H$ ICCFGED08_HXI²C Control Register $0000_H$ ICADRED08_HXI²C Receive/Transmit Buffer $XX_H$ ICCNED08_H<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CRIC    | b | FF6A <sub>H</sub> |     | B5 <sub>H</sub> | GPT2 CAPREL Interrupt Ctrl. Register     | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CSP     |   | FE08 <sub>H</sub> |     | 04 <sub>H</sub> | 5 5                                      | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DP0L    | b | F100 <sub>H</sub> | Ε   | 80 <sub>H</sub> | P0L Direction Control Register           | 00 <sub>H</sub>   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DP0H    | b | F102 <sub>H</sub> | Ε   | 81 <sub>H</sub> | P0H Direction Control Register           | 00 <sub>H</sub>   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DP1L    | b | F104 <sub>H</sub> | Ε   | 82 <sub>H</sub> | P1L Direction Control Register           | 00 <sub>H</sub>   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DP1H    | b | F106 <sub>H</sub> | Ε   | 83 <sub>H</sub> | P1H Direction Control Register           | 00 <sub>H</sub>   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DP2     | b | FFC2 <sub>H</sub> |     | E1 <sub>H</sub> | Port 2 Direction Control Register        | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DP3     | b | $FFC6_{H}$        |     | E3 <sub>H</sub> | Port 3 Direction Control Register        | 0000 <sub>H</sub> |

| DPP0 $FE00_H$ $00_H$ $CPU$ Data Page Pointer 0 Register (10<br>bits) $0000_H$ DPP1 $FE02_H$ $01_H$ $CPU$ Data Page Pointer 1 Reg. (10 bits) $0001_H$ DPP2 $FE04_H$ $02_H$ $CPU$ Data Page Pointer 2 Reg. (10 bits) $0002_H$ DPP3 $FE06_H$ $03_H$ $CPU$ Data Page Pointer 3 Reg. (10 bits) $0003_H$ EXICONb $F1C0_H$ E $E0_H$ External Interrupt Control Register $0000_H$ ICADR $ED06_H$ X $I^2C$ Address Register $0XXX_H$ ICCFG $ED00_H$ X $I^2C$ Configuration Register $0000_H$ ICCN $ED02_H$ X $I^2C$ Control Register $0000_H$ ICRTB $ED08_H$ X $I^2C$ Receive/Transmit Buffer $XX_H$ IDCHIP $F07C_H$ E $3E_H$ Identifier $09XX_H$ IDMANUF $F07E_H$ E $3F_H$ Identifier $1820_H$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DP4     | b | $FFCA_{H}$        |     | E5 <sub>H</sub> | Port 4 Direction Control Register        | 00 <sub>H</sub>   |

| DPP1FE02 <sub>H</sub> 01 <sub>H</sub> CPU Data Page Pointer 1 Reg. (10 bits)0001 <sub>H</sub> DPP2FE04 <sub>H</sub> 02 <sub>H</sub> CPU Data Page Pointer 2 Reg. (10 bits)0002 <sub>H</sub> DPP3FE06 <sub>H</sub> 03 <sub>H</sub> CPU Data Page Pointer 3 Reg. (10 bits)0003 <sub>H</sub> EXICONbF1C0 <sub>H</sub> EE0 <sub>H</sub> External Interrupt Control Register0000 <sub>H</sub> ICADRED06 <sub>H</sub> XI²C Address Register0XXX <sub>H</sub> ICCFGED00 <sub>H</sub> XI²C Configuration Register0000 <sub>H</sub> ICCONED02 <sub>H</sub> XI²C Control Register0000 <sub>H</sub> ICRTBED08 <sub>H</sub> XI²C Receive/Transmit BufferXX <sub>H</sub> ICSTED04 <sub>H</sub> XI²C Status Register0000 <sub>H</sub> IDCHIPF07C <sub>H</sub> E3E <sub>H</sub> Identifier09XX <sub>H</sub> IDMANUFF07E <sub>H</sub> E3F <sub>H</sub> Identifier1820 <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DP6     | b | $FFCE_H$          |     | E7 <sub>H</sub> | Port 6 Direction Control Register        | 00 <sub>H</sub>   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DPP0    |   | FE00 <sub>H</sub> |     | 00 <sub>H</sub> | <b>č č</b> ,                             | 0000 <sub>H</sub> |

| DPP3FE06 <sub>H</sub> 03 <sub>H</sub> CPU Data Page Pointer 3 Reg. (10 bits)0003 <sub>H</sub> EXICONbF1C0 <sub>H</sub> EE0 <sub>H</sub> External Interrupt Control Register0000 <sub>H</sub> ICADRED06 <sub>H</sub> XI²C Address Register0XXX <sub>H</sub> ICCFGED00 <sub>H</sub> XI²C Configuration RegisterXX00 <sub>H</sub> ICCONED02 <sub>H</sub> XI²C Control Register0000 <sub>H</sub> ICRTBED08 <sub>H</sub> XI²C Receive/Transmit BufferXX <sub>H</sub> ICSTED04 <sub>H</sub> XI²C Status Register0000 <sub>H</sub> IDCHIPF07C <sub>H</sub> E3E <sub>H</sub> Identifier09XX <sub>H</sub> IDMANUFF07E <sub>H</sub> E3F <sub>H</sub> Identifier1820 <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DPP1    |   | FE02 <sub>H</sub> |     | 01 <sub>H</sub> | CPU Data Page Pointer 1 Reg. (10 bits)   | 0001 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DPP2    |   | FE04 <sub>H</sub> |     | 02 <sub>H</sub> | CPU Data Page Pointer 2 Reg. (10 bits)   | 0002 <sub>H</sub> |

| ICADRED06 <sub>H</sub> XI²C Address Register $0XXX_H$ ICCFGED00 <sub>H</sub> XI²C Configuration Register $XX00_H$ ICCONED02 <sub>H</sub> XI²C Control Register $0000_H$ ICRTBED08 <sub>H</sub> XI²C Receive/Transmit Buffer $XX_H$ ICSTED04 <sub>H</sub> XI²C Status Register $0000_H$ IDCHIPF07C <sub>H</sub> E $3E_H$ Identifier $09XX_H$ IDMANUFF07E_HE $3F_H$ Identifier $1820_H$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DPP3    |   | FE06 <sub>H</sub> |     | 03 <sub>H</sub> | CPU Data Page Pointer 3 Reg. (10 bits)   | 0003 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EXICON  | b | F1C0 <sub>H</sub> | Ε   | E0 <sub>H</sub> | External Interrupt Control Register      | 0000 <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ICADR   |   | ED06 <sub>H</sub> | Χ   |                 | I <sup>2</sup> C Address Register        | 0XXX <sub>H</sub> |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ICCFG   |   | ED00 <sub>H</sub> | Χ   |                 | I <sup>2</sup> C Configuration Register  | XX00 <sub>H</sub> |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ICCON   |   | ED02 <sub>H</sub> | Χ   |                 | I <sup>2</sup> C Control Register        | 0000 <sub>H</sub> |

| IDCHIP $F07C_H$ E $3E_H$ Identifier $09XX_H$ IDMANUF $F07E_H$ E $3F_H$ Identifier $1820_H$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ICRTB   |   | ED08 <sub>H</sub> | Χ   |                 | I <sup>2</sup> C Receive/Transmit Buffer | XX <sub>H</sub>   |