#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | C166                                                                          |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20MHz                                                                         |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 76                                                                            |

| Program Memory Size        | -                                                                             |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 3K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 4x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-LQFP                                                                      |

| Supplier Device Package    | PG-TQFP-100-1                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c161pilf3vcafxuma1 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C166 Family of High-Performance CMOS 16-Bit Microcontrollers

# Preliminary C161PI 16-Bit Microcontroller

- High Performance 16-bit CPU with 4-Stage Pipeline

- 80 ns Instruction Cycle Time at 25 MHz CPU Clock

- 400 ns Multiplication (16  $\times$  16 bit), 800 ns Division (32 / 16 bit)

- Enhanced Boolean Bit Manipulation Facilities

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Single-Cycle Context Switching Support

- 16 MBytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area

- 16-Priority-Level Interrupt System with 27 Sources, Sample-Rate down to 40 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC)

- Clk. Generation via on-chip PLL (1:1.5/2/2.5/3/4/5), via prescaler or via direct clk. inp.

- On-Chip Memory Modules

- 1 KByte On-Chip Internal RAM (IRAM)

- 2 KBytes On-Chip Extension RAM (XRAM)

- On-Chip Peripheral Modules

- 4-Channel 10-bit A/D Converter with Programm. Conversion Time down to 7.8 μs

- Two Multi-Functional General Purpose Timer Units with 5 Timers

- Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

- I<sup>2</sup>C Bus Interface (10-bit Addressing, 400 KHz) with 2 Channels (multiplexed)

- Up to 8 MBytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses with 8-Bit or 16-Bit Data Bus Width

- Five Programmable Chip-Select Signals

- Idle and Power Down Modes with Flexible Power Management

- Programmable Watchdog Timer and Oscillator Watchdog

- On-Chip Real Time Clock

- Up to 76 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

- 100-Pin MQFP / TQFP Package

| Table 1    | Pin Definitions and Functions (continued) |                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|------------|-------------------------------------------|---------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol     | Pin<br>Num.<br>TQFP                       | Pin<br>Num.<br>MQFP | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| RSTIN      | 76                                        | 78                  | I/O            | Reset Input with Schmitt-Trigger characteristics. A low<br>level at this pin while the oscillator is running resets the<br>C161PI. An internal pullup resistor permits power-on<br>reset using only a capacitor connected to $V_{SS}$ .<br>A spike filter suppresses input pulses <10 ns. Input<br>pulses >100 ns safely pass the filter.<br>The minimum duration for a safe recognition should be<br>100 ns + 2 CPU clock cycles.<br>In bidirectional reset mode (enabled <u>by setting bit</u><br>BDRSTEN in register SYSCON) the RSTIN line is<br>internally pulled low for the duration of the internal<br>reset sequence upon any reset (HW, SW, WDT).<br>See note below this table. |  |  |  |  |  |

|            |                                           |                     |                | Note: To let the reset configuration of PORT0 settle<br>and to let the PLL lock a reset duration of ca.<br>1 ms is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| RST<br>OUT | 77                                        | 79                  | 0              | Internal Reset Indication Output. This pin is set to a low<br>level when the part is executing either a hardware-, a<br>software- or a watchdog timer reset. RSTOUT remains<br>low until the EINIT (end of initialization) instruction is<br>executed.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| NMI        | 78                                        | 80                  | 1              | Non-Maskable Interrupt Input. A high to low transition<br>at this pin causes the CPU to vector to the NMI trap<br>routine. When the PWRDN (power down) instruction is<br>executed, the NMI pin must be low in order to force the<br>C161PI to go into power down mode. If NMI is high,<br>when PWRDN is executed, the part will continue to run<br>in normal mode.<br>If not used, pin NMI should be pulled high externally.                                                                                                                                                                                                                                                              |  |  |  |  |  |

### **External Bus Controller**

All of the external memory accesses are performed by a particular on-chip External Bus Controller (EBC). It can be programmed either to Single Chip Mode when no external memory is required, or to one of four different external memory access modes, which are as follows:

- 16-/18-/20-/23-bit Addresses, 16-bit Data, Demultiplexed

- 16-/18-/20-/23-bit Addresses, 16-bit Data, Multiplexed

- 16-/18-/20-/23-bit Addresses, 8-bit Data, Multiplexed

- 16-/18-/20-/23-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/ output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output.

Important timing characteristics of the external bus interface (Memory Cycle Time, Memory Tri-State Time, Length of ALE and Read Write Delay) have been made programmable to allow the user the adaption of a wide range of different types of memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via register pairs ADDRSELx / BUSCONx) which allow to access different resources with different bus characteristics. These address windows are arranged hierarchically where BUSCON4 overrides BUSCON3 and BUSCON2 overrides BUSCON1. All accesses to locations not covered by these 4 address windows are controlled by BUSCON0.

Up to 5 external  $\overline{CS}$  signals (4 windows plus default) can be generated in order to save external glue logic. The C161PI offers the possibility to switch the  $\overline{CS}$  outputs to an unlatched mode. In this mode the internal filter logic is switched off and the  $\overline{CS}$  signals are directly generated from the address. The unlatched  $\overline{CS}$  mode is enabled by setting CSCFG (SYSCON.6).

Access to very slow memories is supported via a particular 'Ready' function.

For applications which require less than 8 MBytes of external memory space, this address space can be restricted to 1 MByte, 256 KByte or to 64 KByte. In this case Port 4 outputs four, two or no address lines at all. It outputs all 7 address lines, if an address space of 8 MBytes is used.

#### Serial Channels

Serial communication with other microcontrollers, processors, terminals or external peripheral components is provided by two serial interfaces with different functionality, an Asynchronous/Synchronous Serial Channel (**ASC0**) and a High-Speed Synchronous Serial Channel (**SSC**).

**The ASC0** is upward compatible with the serial ports of the Infineon 8-bit microcontroller families and supports full-duplex asynchronous communication at up to 780 KBaud and half-duplex synchronous communication at up to 3.1 MBaud @ 25 MHz CPU clock.

A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling 4 separate interrupt vectors are provided. In asynchronous mode, 8- or 9-bit data frames are transmitted or received, preceded by a start bit and terminated by one or two stop bits. For multiprocessor communication, a mechanism to distinguish address from data bytes has been included (8-bit data plus wake up bit mode).

In synchronous mode, the ASC0 transmits or receives bytes (8 bits) synchronously to a shift clock which is generated by the ASC0. The ASC0 always shifts the LSB first. A loop back option is available for testing purposes.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. A parity bit can automatically be generated on transmission or be checked on reception. Framing error detection allows to recognize data frames with missing stop bits. An overrun error will be generated, if the last character received has not been read out of the receive buffer register at the time the reception of a new character is complete.

**The SSC** supports full-duplex synchronous communication at up to 6.25 Mbaud @ 25 MHz CPU clock. It may be configured so it interfaces with serially linked peripheral components. A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling 3 separate interrupt vectors are provided.

The SSC transmits or receives characters of 2...16 bits length synchronously to a shift clock which can be generated by the SSC (master mode) or by an external master (slave mode). The SSC can start shifting with the LSB or with the MSB and allows the selection of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. Transmit and receive error supervise the correct handling of the data buffer. Phase and baudrate error detect incorrect serial data.

| Table 4              | Instruction Set Summary (continued)                                                 |       |

|----------------------|-------------------------------------------------------------------------------------|-------|

| Mnemonic             | Description                                                                         | Bytes |

| MOV(B)               | Move word (byte) data                                                               | 2/4   |

| MOVBS                | Move byte operand to word operand with sign extension                               | 2/4   |

| MOVBZ                | Move byte operand to word operand. with zero extension                              | 2/4   |

| JMPA, JMPI,<br>JMPR  | Jump absolute/indirect/relative if condition is met                                 | 4     |

| JMPS                 | Jump absolute to a code segment                                                     | 4     |

| J(N)B                | Jump relative if direct bit is (not) set                                            | 4     |

| JBC                  | Jump relative and clear bit if direct bit is set                                    | 4     |

| JNBS                 | Jump relative and set bit if direct bit is not set                                  | 4     |

| CALLA, CALL<br>CALLR | I, Call absolute/indirect/relative subroutine if condition is met                   | 4     |

| CALLS                | Call absolute subroutine in any code segment                                        | 4     |

| PCALL                | Push direct word register onto system stack and call absolute subroutine            | 4     |

| TRAP                 | Call interrupt service routine via immediate trap number                            | 2     |

| PUSH, POP            | Push/pop direct word register onto/from system stack                                | 2     |

| SCXT                 | Push direct word register onto system stack und update register with word operand   | 4     |

| RET                  | Return from intra-segment subroutine                                                | 2     |

| RETS                 | Return from inter-segment subroutine                                                | 2     |

| RETP                 | Return from intra-segment subroutine and pop direct word register from system stack | 2     |

| RETI                 | Return from interrupt service subroutine                                            | 2     |

| SRST                 | Software Reset                                                                      | 4     |

| IDLE                 | Enter Idle Mode                                                                     | 4     |

| PWRDN                | Enter Power Down Mode (supposes NMI-pin being low)                                  | 4     |

| SRVWDT               | Service Watchdog Timer                                                              | 4     |

| DISWDT               | Disable Watchdog Timer                                                              | 4     |

| EINIT                | Signify End-of-Initialization on RSTOUT-pin                                         | 4     |

| ATOMIC               | Begin ATOMIC sequence                                                               | 2     |

| EXTR                 | Begin EXTended Register sequence                                                    | 2     |

| EXTP(R)              | Begin EXTended Page (and Register) sequence                                         | 2/4   |

| EXTS(R)              | Begin EXTended Segment (and Register) sequence                                      | 2/4   |

| NOP                  | Null operation                                                                      | 2     |

#### **Parameter Interpretation**

The parameters listed in the following partly represent the characteristics of the C161PI and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C161PI will provide signals with the respective timing characteristics.

#### SR (System Requirement):

The external system must provide signals with the respective timing characteristics to the C161PI.

## DC Characteristics (Standard Supply Voltage Range)

(Operating Conditions apply)

| Parameter                                                                            | Symbol              | Limit                        | Values                       | Unit | Test Condition                 |

|--------------------------------------------------------------------------------------|---------------------|------------------------------|------------------------------|------|--------------------------------|

|                                                                                      |                     | min.                         | max.                         |      |                                |

| Input low voltage XTAL1,<br>P3.0, P3.1, P6.5, P6.6, P6.7                             | V <sub>IL1</sub> SR | - 0.5                        | 0.3 V <sub>DD</sub>          | V    | -                              |

| Input low voltage<br>(TTL)                                                           | V <sub>IL</sub> SR  | - 0.5                        | 0.2 V <sub>DD</sub><br>- 0.1 | V    | -                              |

| Input low voltage<br>(Special Threshold)                                             | $V_{\rm ILS}$ SR    | - 0.5                        | 2.0                          | V    | -                              |

| Input high voltage RSTIN                                                             | V <sub>IH1</sub> SR | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input high voltage XTAL1,<br>P3.0, P3.1, P6.5, P6.6, P6.7                            | V <sub>IH2</sub> SR | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input high voltage<br>(TTL)                                                          | V <sub>IH</sub> SR  | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input high voltage<br>(Special Threshold)                                            | V <sub>IHS</sub> SR | 0.8 V <sub>DD</sub><br>- 0.2 | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input Hysteresis<br>(Special Threshold)                                              | HYS                 | 400                          | -                            | mV   | -                              |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, CLKOUT,<br>RSTOUT) | V <sub>OL</sub> CC  | -                            | 0.45                         | V    | I <sub>OL</sub> = 2.4 mA       |

| Output low voltage<br>(P3.0, P3.1, P6.5, P6.6, P6.7)                                 | V <sub>OL2</sub> CC | -                            | 0.4                          | V    | <i>I</i> <sub>OL2</sub> = 3 mA |

# DC Characteristics (Reduced Supply Voltage Range)

(Operating Conditions apply)

| Parameter                                                                                           | Symbol                          | Limit '                      | Values                | Unit | Test Condition                   |  |

|-----------------------------------------------------------------------------------------------------|---------------------------------|------------------------------|-----------------------|------|----------------------------------|--|

|                                                                                                     |                                 | min.                         | max.                  |      |                                  |  |

| Input low voltage XTAL1,<br>P3.0, P3.1, P6.5, P6.6, P6.7                                            | V <sub>IL1</sub> SR             | - 0.5                        | 0.3 V <sub>DD</sub>   | V    | -                                |  |

| Input low voltage<br>(TTL)                                                                          | V <sub>IL</sub> SR              | - 0.5                        | 0.8                   | V    | -                                |  |

| Input low voltage<br>(Special Threshold)                                                            | V <sub>ILS</sub> SR             | - 0.5                        | 1.3                   | V    | -                                |  |

| Input high voltage RSTIN                                                                            | V <sub>IH1</sub> SR             | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5 | V    | -                                |  |

| Input high voltage XTAL1,<br>P3.0, P3.1, P6.5, P6.6, P6.7                                           | V <sub>IH2</sub> SR             | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5 | V    | -                                |  |

| Input high voltage<br>(TTL)                                                                         | V <sub>IH</sub> SR              | 1.8                          | V <sub>DD</sub> + 0.5 | V    | -                                |  |

| Input high voltage<br>(Special Threshold)                                                           | V <sub>IHS</sub> SR             | 0.8 V <sub>DD</sub><br>- 0.2 | V <sub>DD</sub> + 0.5 | V    | -                                |  |

| Input Hysteresis<br>(Special Threshold)                                                             | HYS                             | 250                          | _                     | mV   | -                                |  |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, CLKOUT,<br>RSTOUT)                | V <sub>OL</sub> CC              | _                            | 0.45                  | V    | I <sub>OL</sub> = 1.6 mA         |  |

| Output low voltage<br>P3.0, P3.1, P6.5, P6.6, P6.7                                                  | V <sub>OL2</sub> CC             | -                            | 0.4                   | V    | <i>I</i> <sub>OL2</sub> = 1.6 mA |  |

| Output low voltage<br>(all other outputs)                                                           | V <sub>OL1</sub> CC             | -                            | 0.45                  | V    | <i>I</i> <sub>OL</sub> = 1.0 mA  |  |

| Output high voltage <sup>1)</sup><br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, CLKOUT,<br>RSTOUT) | V <sub>OH</sub> CC              | 0.9 V <sub>DD</sub>          | -                     | V    | I <sub>OH</sub> = -0.5 mA        |  |

| Output high voltage <sup>1)</sup><br>(all other outputs)                                            | V <sub>OH1</sub> CC             | 0.9 V <sub>DD</sub>          | -                     | V    | I <sub>OH</sub> = -0.25 mA       |  |

| Input leakage current (Port 5)                                                                      | I <sub>OZ1</sub> CC             | -                            | ±200                  | nA   | $0.45V < V_{IN} < V_{DD}$        |  |

| Input leakage current (all other)                                                                   | I <sub>OZ2</sub> CC             | _                            | ±500                  | nA   | $0.45V < V_{IN} < V_{DD}$        |  |

| RSTIN inactive current <sup>2)</sup>                                                                | I <sub>RSTH</sub> <sup>3)</sup> | _                            | -10                   | μA   | $V_{\rm IN} = V_{\rm IH1}$       |  |

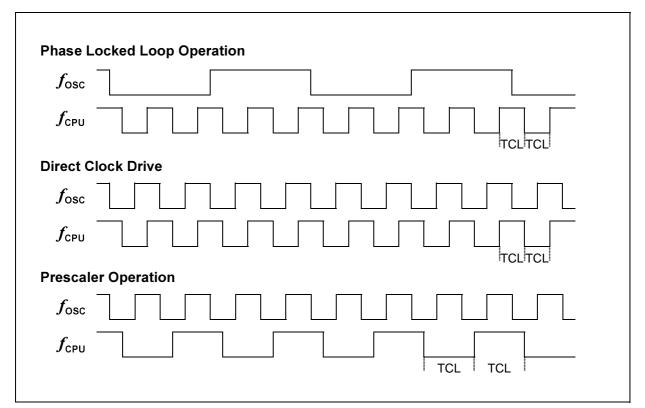

#### AC Characteristics Definition of Internal Timing

The internal operation of the C161PI is controlled by the internal CPU clock  $f_{CPU}$ . Both edges of the CPU clock can trigger internal (e.g. pipeline) or external (e.g. bus cycles) operations.

The specification of the external timing (AC Characteristics) therefore depends on the time between two consecutive edges of the CPU clock, called "TCL" (see figure below).

Figure 11 Generation Mechanisms for the CPU Clock

The CPU clock signal  $f_{CPU}$  can be generated from the oscillator clock signal  $f_{OSC}$  via different mechanisms. The duration of TCLs and their variation (and also the derived external timing) depends on the used mechanism to generate  $f_{CPU}$ . This influence must be regarded when calculating the timings for the C161PI.

Note: The example for PLL operation shown in the fig. above refers to a PLL factor of 4.

The used mechanism to generate the CPU clock is selected during reset via the logic levels on pins P0.15-13 (P0H.7-5).

The table below associates the combinations of these three bits with the respective clock generation mode.

The timings listed in the AC Characteristics that refer to TCLs therefore must be calculated using the minimum TCL that is possible under the respective circumstances.

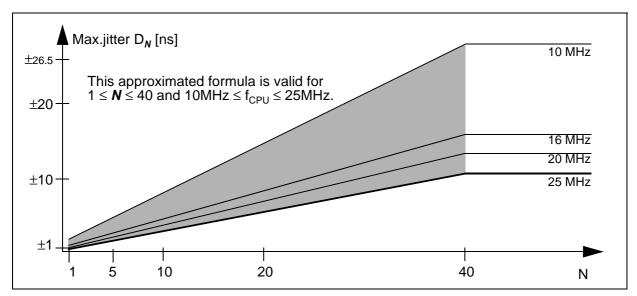

The actual minimum value for TCL depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency (crystal or oscillator) the relative deviation for periods of more than one TCL is lower than for one single TCL (see formula and figure below).

For a period of N \* TCL the minimum value is computed using the corresponding deviation  $D_N$ :

$(N * TCL)_{min} = N * TCL_{NOM} - D_N$   $D_N [ns] = \pm(13.3 + N*6.3) / f_{CPU} [MHz],$ where N = number of consecutive TCLs and  $1 \le N \le 40$ .

So for a period of 3 TCLs @ 25 MHz (i.e. N = 3): D<sub>3</sub> = (13.3 +  $3 \times 6.3$ ) / 25 = 1.288 ns, and (3TCL)<sub>min</sub> = 3TCL<sub>NOM</sub> - 1.288 ns = 58.7 ns (@  $f_{CPU} = 25$  MHz).

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is neglectible.

Note: For all periods longer than 40 TCL the N=40 value can be used (see figure below).

Figure 12 Approximated Maximum Accumulated PLL Jitter

### **A/D Converter Characteristics**

(Operating Conditions apply)

4.0V (2.6V)  $\leq V_{\rm AREF} \leq V_{\rm DD}$  + 0.1V (Note the influence on TUE.)

$V_{\rm SS}$  - 0.1V  $\leq V_{\rm AGND} \leq V_{\rm SS}$  + 0.2V

| Parameter                                       | Symbol              | Limit             | Values                             | Unit | <b>Test Condition</b>                            |  |

|-------------------------------------------------|---------------------|-------------------|------------------------------------|------|--------------------------------------------------|--|

|                                                 |                     | min.              | max.                               |      |                                                  |  |

| Analog input voltage range                      | V <sub>AIN</sub> SR | V <sub>AGND</sub> | $V_{AREF}$                         | V    | 1)                                               |  |

| Basic clock frequency                           | $f_{\rm BC}$        | 0.5               | 6.25                               | MHz  | 2)                                               |  |

| Conversion time                                 | t <sub>C</sub> CC   | _                 | 40 $t_{BC}$ + $t_{S}$ +2 $t_{CPU}$ |      | <sup>3)</sup><br>$t_{\rm CPU} = 1 / f_{\rm CPU}$ |  |

| Total unadjusted error                          | TUE CC              | -                 | ± 2                                | LSB  | $V_{\text{AREF}} \ge 4.0 \text{ V}^{-5}$         |  |

|                                                 | 4)                  | -                 | ± 4                                | LSB  | $V_{AREF} \ge 2.6 \text{ V}$                     |  |

| Internal resistance of reference voltage source | $R_{AREF} SR$       | _                 | t <sub>BC</sub> / 60<br>- 0.25     | kΩ   | <i>t</i> <sub>BC</sub> in [ns] <sup>6) 7)</sup>  |  |

| Internal resistance of analog source            | $R_{\rm ASRC}$ SR   | -                 | t <sub>S</sub> / 450<br>- 0.25     | kΩ   | <i>t</i> <sub>S</sub> in [ns] <sup>7) 8)</sup>   |  |

| ADC input capacitance                           | $C_{AIN}$ CC        | -                 | 33                                 | pF   | 7)                                               |  |

V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 2) The limit values for  $f_{BC}$  must not be exceeded when selecting the CPU frequency and the ADCTC setting.

- 3) This parameter includes the sample time  $t_s$ , the time for determining the digital result and the time to load the result register with the conversion result.

Values for the basic clock  $t_{\rm BC}$  depend on the conversion time programming.

This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

TUE is tested at V<sub>AREF</sub>=5.0V (3.3V), V<sub>AGND</sub>=0V, V<sub>DD</sub>=4.9V (3.2V). It is guaranteed by design for all other voltages within the defined voltage range.

The specified TUE is guaranteed only if an overload condition (see  $I_{OV}$  specification) occurs on maximum 2 not selected analog input pins and the absolute sum of input overload currents on all analog input pins does not exceed 10 mA.

During the reset calibration sequence the maximum TUE may be  $\pm4$  LSB ( $\pm8$  LSB @ 3V).

- 5) This case is not applicable for the reduced supply voltage range.

- 6) During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference voltage source must allow the capacitance to reach its respective voltage level within each conversion step. The maximum internal resistance results from the programmed conversion timing.

- 7) Not 100% tested, guaranteed by design.

- 8) During the sample time the input capacitance  $C_1$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_s$ . After the end of the sample time  $t_s$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample time  $t_s$  depend on programming and can be taken from the table below.

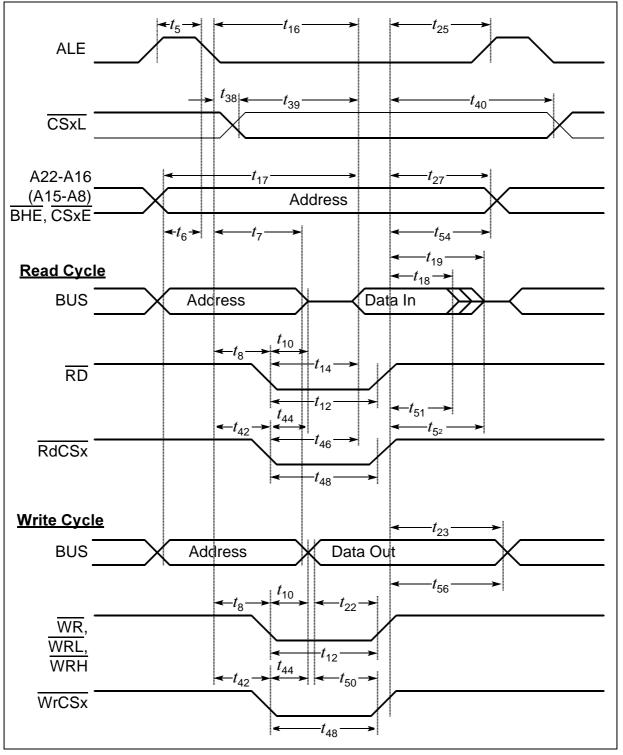

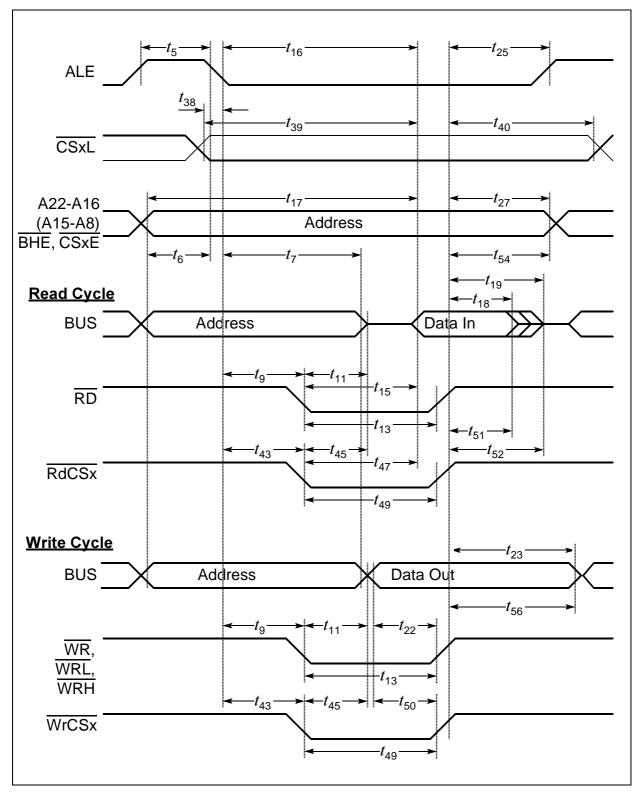

Figure 16 External Memory Cycle: Multiplexed Bus, With Read/Write Delay, Normal ALE

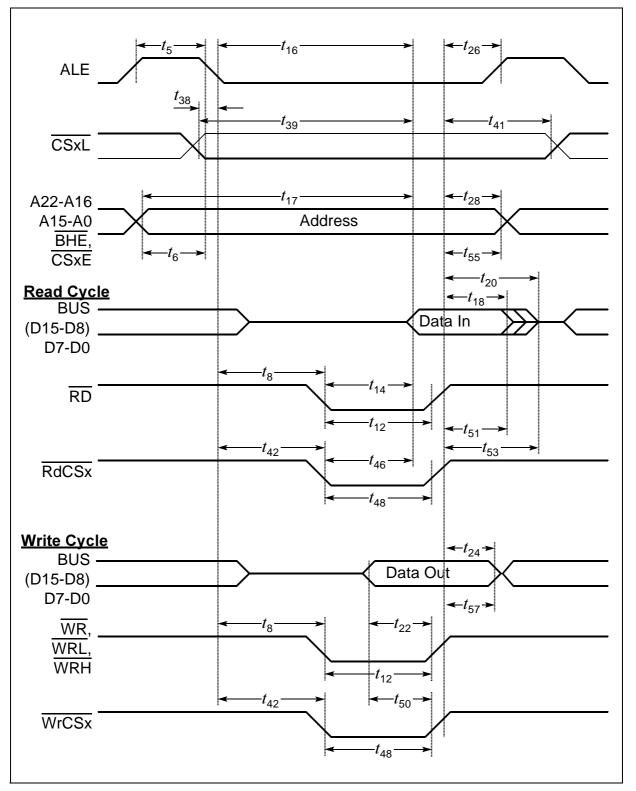

Figure 17 External Memory Cycle: Multiplexed Bus, With Read/Write Delay, Extended ALE

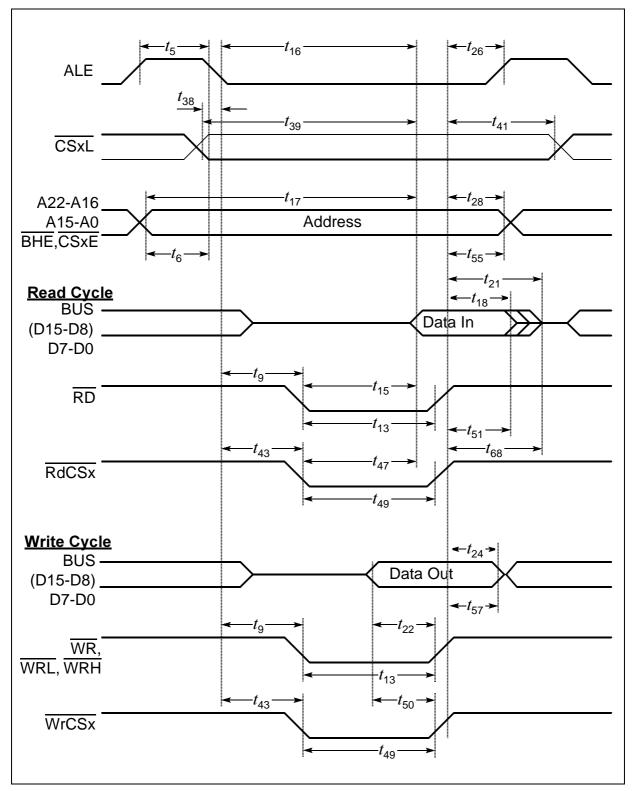

Figure 19 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Extended ALE

#### **AC Characteristics**

#### Demultiplexed Bus (Standard Supply Voltage Range)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                      | Symbol                 |    | Max. CPU Clock<br>= 25 MHz |                             | Variable (<br>1 / 2TCL =             | Unit                                               |    |

|----------------------------------------------------------------|------------------------|----|----------------------------|-----------------------------|--------------------------------------|----------------------------------------------------|----|

|                                                                |                        |    | min.                       | max.                        | min.                                 | max.                                               | -  |

| ALE high time                                                  | <i>t</i> <sub>5</sub>  | CC | $10 + t_{A}$               | -                           | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                  | ns |

| Address setup to ALE                                           | <i>t</i> <sub>6</sub>  | CC | $4 + t_A$                  | -                           | TCL - 16<br>+ <i>t</i> <sub>A</sub>  | -                                                  | ns |

| ALE falling edge to $\overline{RD}$ , WR (with RW-delay)       | <i>t</i> <sub>8</sub>  | CC | $10 + t_{A}$               | -                           | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                  | ns |

| ALE falling edge to RD,<br>WR (no RW-delay)                    | <i>t</i> 9             | CC | $-10 + t_{A}$              | -                           | -10<br>+ <i>t</i> <sub>A</sub>       | -                                                  | ns |

| RD, WR low time<br>(with RW-delay)                             | <i>t</i> <sub>12</sub> | CC | $30 + t_{\rm C}$           | -                           | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| RD, WR low time<br>(no RW-delay)                               | <i>t</i> <sub>13</sub> | CC | $50 + t_{\rm C}$           | -                           | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| RD to valid data in (with RW-delay)                            | <i>t</i> <sub>14</sub> | SR | -                          | $20 + t_{\rm C}$            | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>               | ns |

| RD to valid data in (no RW-delay)                              | t <sub>15</sub>        | SR | _                          | $40 + t_{\rm C}$            | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>               | ns |

| ALE low to valid data in                                       | t <sub>16</sub>        | SR | -                          | $40 + t_A + t_C$            | -                                    | $3TCL - 20 + t_A + t_C$                            | ns |

| Address to valid data in                                       | <i>t</i> <sub>17</sub> | SR | _                          | $50 + 2t_A + t_C$           | _                                    | $4TCL - 30 + 2t_A + t_C$                           | ns |

| Data hold after RD rising edge                                 | t <sub>18</sub>        | SR | 0                          | -                           | 0                                    | -                                                  | ns |

| Data float after RD rising edge (with RW-delay <sup>1)</sup> ) | <i>t</i> <sub>20</sub> | SR | _                          | $26 + 2t_A + t_F$           | -                                    | 2TCL - 14<br>+ $22t_A$<br>+ $t_F^{(1)}$            | ns |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )   | <i>t</i> <sub>21</sub> | SR | _                          | $10 + 2t_{A} + t_{F}^{(1)}$ | _                                    | TCL - 10<br>+ $22t_{\rm A}$<br>+ $t_{\rm F}^{-1)}$ | ns |

| Data valid to $\overline{WR}$                                  | <i>t</i> <sub>22</sub> | CC | 20 + $t_{\rm C}$           | -                           | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

# Demultiplexed Bus (Standard Supply Voltage Range) (continued)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                             | Symbol                 |    | Max. CPU Clock<br>= 25 MHz  |                            | Variable (<br>1 / 2TCL =             | Unit                                               |    |

|-------------------------------------------------------|------------------------|----|-----------------------------|----------------------------|--------------------------------------|----------------------------------------------------|----|

|                                                       |                        |    | min.                        | max.                       | min.                                 | max.                                               |    |

| Data hold after WR                                    | <i>t</i> <sub>24</sub> | CC | 10 + <i>t</i> <sub>F</sub>  | -                          | TCL - 10<br>+ <i>t</i> <sub>F</sub>  | -                                                  | ns |

| $\frac{ALE}{WR}$ rising edge after $\overline{RD}$ ,  | t <sub>26</sub>        | CC | -10 + <i>t</i> <sub>F</sub> | -                          | -10 + <i>t</i> <sub>F</sub>          | -                                                  | ns |

| Address hold after WR 2)                              | t <sub>28</sub>        | CC | $0 + t_{F}$                 | -                          | $0 + t_{F}$                          | -                                                  | ns |

| ALE falling edge to CS 3)                             | <i>t</i> <sub>38</sub> | CC | -4 - <i>t</i> <sub>A</sub>  | 10 - <i>t</i> <sub>A</sub> | -4 - <i>t</i> <sub>A</sub>           | 10 - <i>t</i> <sub>A</sub>                         | ns |

| CS low to Valid Data In <sup>3)</sup>                 | <i>t</i> <sub>39</sub> | SR | -                           | $40 + t_{C} + 2t_{A}$      | -                                    | $3TCL - 20 + t_{C} + 2t_{A}$                       | ns |

| CS hold after RD, WR 3)                               | <i>t</i> <sub>41</sub> | CC | $6 + t_{F}$                 | -                          | TCL - 14<br>+ <i>t</i> <sub>F</sub>  | -                                                  | ns |

| ALE falling edge to<br>RdCS, WrCS (with RW-<br>delay) | t <sub>42</sub>        | CC | $16 + t_{A}$                | -                          | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | -                                                  | ns |

| ALE falling edge to<br>RdCS, WrCS (no RW-<br>delay)   | t <sub>43</sub>        | CC | $-4 + t_{A}$                | _                          | -4<br>+ <i>t</i> <sub>A</sub>        | -                                                  | ns |

| RdCS to Valid Data In<br>(with RW-delay)              | <i>t</i> <sub>46</sub> | SR | -                           | 16 + <i>t</i> <sub>C</sub> | -                                    | 2TCL - 24<br>+ <i>t</i> <sub>C</sub>               | ns |

| RdCS to Valid Data In<br>(no RW-delay)                | <i>t</i> <sub>47</sub> | SR | _                           | $36 + t_{\rm C}$           | -                                    | 3TCL - 24<br>+ <i>t</i> <sub>C</sub>               | ns |

| RdCS, WrCS Low Time<br>(with RW-delay)                | <i>t</i> <sub>48</sub> | CC | $30 + t_{\rm C}$            | -                          | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| RdCS, WrCS Low Time<br>(no RW-delay)                  | <i>t</i> <sub>49</sub> | CC | $50 + t_{\rm C}$            | -                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| Data valid to WrCS                                    | <i>t</i> <sub>50</sub> | CC | 26 + $t_{\rm C}$            | -                          | 2TCL - 14<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| Data hold after RdCS                                  | <i>t</i> <sub>51</sub> | SR | 0                           | _                          | 0                                    | _                                                  | ns |

| Data float after RdCS (with RW-delay) <sup>1)</sup>   | <i>t</i> <sub>53</sub> | SR | -                           | $20 + t_{\rm F}$           | -                                    | 2TCL - 20<br>+ $2t_{\text{A}} + t_{\text{F}}^{-1}$ | ns |

| Data float after RdCS (no RW-delay) 1)                | t <sub>68</sub>        | SR | -                           | $0 + t_{\rm F}$            | -                                    | TCL - 20<br>+ $2t_{A} + t_{F}^{(1)}$               | ns |

# Demultiplexed Bus (Standard Supply Voltage Range) (continued)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                        | Symbol                    |                  | PU Clock<br>5 MHz | Variable (<br>1 / 2TCL =            | Unit |    |

|----------------------------------|---------------------------|------------------|-------------------|-------------------------------------|------|----|

|                                  |                           | min.             | max.              | min.                                | max. | -  |

| Address hold after<br>RdCS, WrCS | <i>t</i> <sub>55</sub> CC | $-6 + t_{\rm F}$ | -                 | $-6 + t_{\rm F}$                    | -    | ns |

| Data hold after WrCS             | <i>t</i> <sub>57</sub> CC | $6 + t_{\rm F}$  | -                 | TCL - 14 +<br><i>t</i> <sub>F</sub> | -    | ns |

1) RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

2) Read data are latched with the same clock edge that triggers the address change and the rising  $\overline{\text{RD}}$  edge. Therefore address changes before the end of  $\overline{\text{RD}}$  have no impact on read cycles.

3) These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

# Demultiplexed Bus (Reduced Supply Voltage Range) (continued)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (100 ns at 20 MHz CPU clock without waitstates)

| Parameter                                                               |                        | nbol | Max. CPU Clock<br>= 20 MHz  |                               | Variable (<br>1 / 2TCL =             | Unit                                               |    |

|-------------------------------------------------------------------------|------------------------|------|-----------------------------|-------------------------------|--------------------------------------|----------------------------------------------------|----|

|                                                                         |                        |      | min.                        | max.                          | min.                                 | max.                                               |    |

| Data hold after WR                                                      | <i>t</i> <sub>24</sub> | CC   | 15 + <i>t</i> <sub>F</sub>  | -                             | TCL - 10<br>+ <i>t</i> <sub>F</sub>  | -                                                  | ns |

| $\frac{\text{ALE rising edge after } \overline{\text{RD}},}{\text{WR}}$ | t <sub>26</sub>        | CC   | -12 + <i>t</i> <sub>F</sub> | -                             | -12 + <i>t</i> <sub>F</sub>          | -                                                  | ns |

| Address hold after WR 2)                                                | <i>t</i> <sub>28</sub> | CC   | $0 + t_{F}$                 | _                             | $0 + t_{F}$                          | -                                                  | ns |

| ALE falling edge to $\overline{\text{CS}}^{3)}$                         | <i>t</i> <sub>38</sub> | CC   | -8 - <i>t</i> <sub>A</sub>  | 10 - <i>t</i> <sub>A</sub>    | -8 - <i>t</i> <sub>A</sub>           | 10 - <i>t</i> <sub>A</sub>                         | ns |

| CS low to Valid Data In <sup>3)</sup>                                   | t <sub>39</sub>        | SR   | _                           | $47 + t_{\rm C} + 2t_{\rm A}$ | -                                    | $3TCL - 28 + t_{C} + 2t_{A}$                       | ns |

| CS hold after RD, WR 3)                                                 | <i>t</i> <sub>41</sub> | CC   | 9 + $t_{\rm F}$             | -                             | TCL - 16<br>+ <i>t</i> <sub>F</sub>  | -                                                  | ns |

| ALE falling edge to<br>RdCS, WrCS (with RW-<br>delay)                   | t <sub>42</sub>        | CC   | 19 + <i>t</i> <sub>A</sub>  | _                             | TCL - 6<br>+ <i>t</i> <sub>A</sub>   | -                                                  | ns |

| ALE falling edge to<br>RdCS, WrCS (no RW-<br>delay)                     | t <sub>43</sub>        | CC   | $-6 + t_{A}$                | _                             | -6<br>+ <i>t</i> <sub>A</sub>        | -                                                  | ns |

| RdCS to Valid Data In<br>(with RW-delay)                                | t <sub>46</sub>        | SR   | _                           | $20 + t_{\rm C}$              | -                                    | 2TCL - 30<br>+ <i>t</i> <sub>C</sub>               | ns |

| RdCS to Valid Data In<br>(no RW-delay)                                  | t <sub>47</sub>        | SR   | _                           | $45 + t_{\rm C}$              | -                                    | 3TCL - 30<br>+ <i>t</i> <sub>C</sub>               | ns |

| RdCS, WrCS Low Time<br>(with RW-delay)                                  | t <sub>48</sub>        | CC   | $38 + t_{\rm C}$            | -                             | 2TCL - 12<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| RdCS, WrCS Low Time<br>(no RW-delay)                                    | t <sub>49</sub>        | CC   | $63 + t_{\rm C}$            | -                             | 3TCL - 12<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| Data valid to WrCS                                                      | <i>t</i> <sub>50</sub> | CC   | $28 + t_{\rm C}$            | -                             | 2TCL - 22<br>+ <i>t</i> <sub>C</sub> | -                                                  | ns |

| Data hold after RdCS                                                    | <i>t</i> <sub>51</sub> | SR   | 0                           | -                             | 0                                    | -                                                  | ns |

| Data float after RdCS (with RW-delay) <sup>1)</sup>                     | <i>t</i> <sub>53</sub> | SR   | _                           | $30 + t_{\rm F}$              | -                                    | 2TCL - 20<br>+ $2t_{\text{A}} + t_{\text{F}}^{-1}$ | ns |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup>                    | t <sub>68</sub>        | SR   | -                           | $5 + t_{\rm F}$               | -                                    | TCL - 20<br>+ $2t_{A}$ + $t_{F}$ <sup>1)</sup>     | ns |

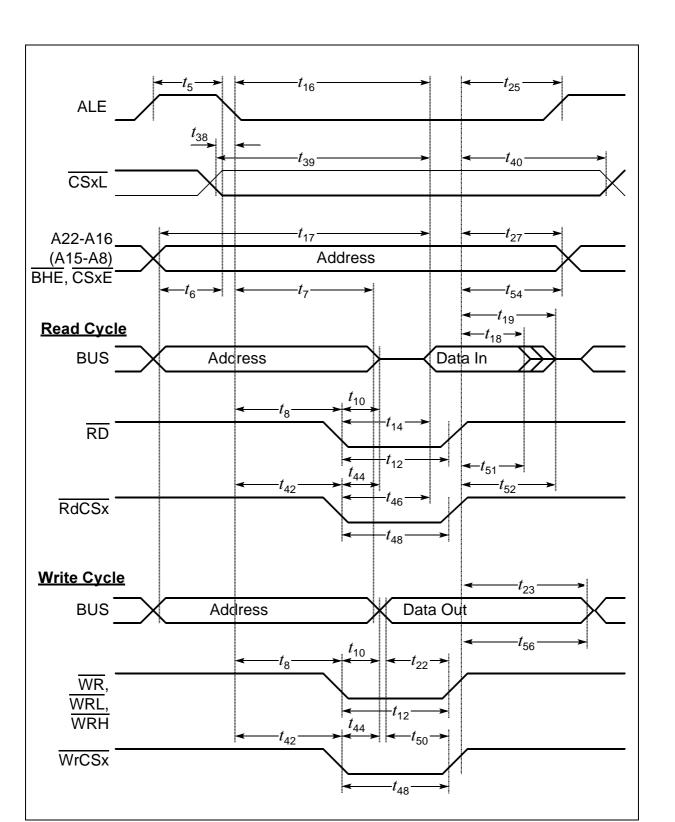

#### Figure 21 External Memory Cycle: Demultiplexed Bus, With Read/Write Delay, Extended ALE

#### Figure 23 External Memory Cycle: Demultiplexed Bus, No Read/Write Delay, Extended ALE

### **AC Characteristics**

# CLKOUT and READY (Reduced Supply Voltage Range)

(Operating Conditions apply)

| Parameter                                                                        | Symbol                 |    |           | PU Clock<br>) MHz                                                    | Variable (<br>1 / 2TCL =      | Unit                                             |    |

|----------------------------------------------------------------------------------|------------------------|----|-----------|----------------------------------------------------------------------|-------------------------------|--------------------------------------------------|----|

|                                                                                  |                        |    | min.      | max.                                                                 | min.                          | max.                                             |    |

| CLKOUT cycle time                                                                | <i>t</i> <sub>29</sub> | CC | 40        | 40                                                                   | 2TCL                          | 2TCL                                             | ns |

| CLKOUT high time                                                                 | <i>t</i> <sub>30</sub> | CC | 15        | -                                                                    | TCL – 10                      | -                                                | ns |

| CLKOUT low time                                                                  | <i>t</i> <sub>31</sub> | CC | 13        | -                                                                    | TCL – 12                      | -                                                | ns |

| CLKOUT rise time                                                                 | <i>t</i> <sub>32</sub> | CC | -         | 12                                                                   | -                             | 12                                               | ns |

| CLKOUT fall time                                                                 | <i>t</i> <sub>33</sub> | CC | -         | 8                                                                    | -                             | 8                                                | ns |

| CLKOUT rising edge to<br>ALE falling edge                                        | <i>t</i> <sub>34</sub> | CC | $0 + t_A$ | $8 + t_A$                                                            | $0 + t_A$                     | $8 + t_A$                                        | ns |

| Synchronous READY setup time to CLKOUT                                           | <i>t</i> <sub>35</sub> | SR | 18        | -                                                                    | 18                            | -                                                | ns |

| Synchronous READY<br>hold time after CLKOUT                                      | <i>t</i> <sub>36</sub> | SR | 4         | -                                                                    | 4                             | -                                                | ns |

| Asynchronous READY low time                                                      | <i>t</i> <sub>37</sub> | SR | 68        | -                                                                    | 2TCL + <i>t</i> <sub>58</sub> | -                                                | ns |

| Asynchronous READY setup time <sup>1)</sup>                                      | <i>t</i> <sub>58</sub> | SR | 18        | -                                                                    | 18                            | -                                                | ns |

| Asynchronous READY hold time <sup>1)</sup>                                       | <i>t</i> <sub>59</sub> | SR | 4         | -                                                                    | 4                             | -                                                | ns |

| Async. READY hold time<br>after RD, WR high<br>(Demultiplexed Bus) <sup>2)</sup> | <i>t</i> <sub>60</sub> | SR | 0         | $ \begin{array}{c} 0 \\ + 2t_{A} + \\ t_{C} + t_{F} \\ \end{array} $ | 0                             | TCL - 25<br>+ $2t_{A} + t_{C}$<br>+ $t_{F}^{2)}$ | ns |

1) These timings are given for test purposes only, in order to assure recognition at a specific clock edge.

Demultiplexed bus is the worst case. For multiplexed bus 2TCL are to be added to the maximum values. This

adds even more time for deactivating READY.

The  $2t_A$  and  $t_C$  refer to the next following bus cycle,  $t_F$  refers to the current <u>bus cycle</u>.

The maximum limit for  $t_{60}$  must be fulfilled if the next following bus cycle is **READY** controlled.