Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

#### Details

| 2 0 0 0 0 0                     |                                                                              |

|---------------------------------|------------------------------------------------------------------------------|

| Product Status                  | Not For New Designs                                                          |

| Programmable Type               | In System Programmable                                                       |

| Delay Time tpd(1) Max           | 10 ns                                                                        |

| Voltage Supply - Internal       | 4.5V ~ 5.5V                                                                  |

| Number of Logic Elements/Blocks | -                                                                            |

| Number of Macrocells            | 128                                                                          |

| Number of Gates                 | -                                                                            |

| Number of I/O                   | 64                                                                           |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                            |

| Mounting Type                   | Surface Mount                                                                |

| Package / Case                  | 100-BQFP                                                                     |

| Supplier Device Package         | 100-PQFP (14x20)                                                             |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/m4a5-128-64-10yni |

|                                 |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.3 V Devices          |         |         |         |          |          |             |          |             |

|------------------------|---------|---------|---------|----------|----------|-------------|----------|-------------|

| Feature                | M4A3-32 | M4A3-64 | M4A3-96 | M4A3-128 | M4A3-192 | M4A3-256    | M4A3-384 | M4A3-512    |

| Macrocells             | 32      | 64      | 96      | 128      | 192      | 256         | 384      | 512         |

| User I/O options       | 32      | 32/64   | 48      | 64       | 96       | 128/160/192 | 160/192  | 160/192/256 |

| t <sub>PD</sub> (ns)   | 5.0     | 5.5     | 5.5     | 5.5      | 6.0      | 5.5         | 6.5      | 7.5         |

| f <sub>CNT</sub> (MHz) | 182     | 167     | 167     | 167      | 160      | 167         | 154      | 125         |

| t <sub>COS</sub> (ns)  | 4.0     | 4.0     | 4.0     | 4.0      | 4.5      | 4.0         | 4.5      | 5.5         |

| t <sub>SS</sub> (ns)   | 3.0     | 3.5     | 3.5     | 3.5      | 3.5      | 3.5         | 3.5      | 5.0         |

| Static Power (mA)      | 20      | 25/52   | 40      | 55       | 85       | 110/150     | 149/155  | 179         |

| JTAG Compliant         | Yes     | Yes     | Yes     | Yes      | Yes      | Yes         | Yes      | Yes         |

| PCI Compliant          | Yes     | Yes     | Yes     | Yes      | Yes      | Yes         | Yes      | Yes         |

### Table 1. ispMACH 4A Device Features

| 5 V Devices            |         |         |         |          |          |          |

|------------------------|---------|---------|---------|----------|----------|----------|

| Feature                | M4A5-32 | M4A5-64 | M4A5-96 | M4A5-128 | M4A5-192 | M4A5-256 |

| Macrocells             | 32      | 64      | 96      | 128      | 192      | 256      |

| User I/O options       | 32      | 32      | 48      | 64       | 96       | 128      |

| t <sub>PD</sub> (ns)   | 5.0     | 5.5     | 5.5     | 5.5      | 6.0      | 6.5      |

| f <sub>CNT</sub> (MHz) | 182     | 167     | 167     | 167      | 160      | 154      |

| t <sub>COS</sub> (ns)  | 4.0     | 4.0     | 4.0     | 4.0      | 4.5      | 5.0      |

| t <sub>SS</sub> (ns)   | 3.0     | 3.5     | 3.5     | 3.5      | 3.5      | 3.5      |

| Static Power (mA)      | 20      | 25      | 40      | 55       | 74       | 110      |

| JTAG Compliant         | Yes     | Yes     | Yes     | Yes      | Yes      | Yes      |

| PCI Compliant          | Yes     | Yes     | Yes     | Yes      | Yes      | Yes      |

|                          | ispMACH                    | 4A Devices       |

|--------------------------|----------------------------|------------------|

|                          | M4A3-64/32, M4A5-64/32     |                  |

|                          | M4A3-96/48, M4A5-96/48     | M4A3-32/32       |

|                          | M4A3-128/64, M4A5-128/64   | M4A5-32/32       |

|                          | M4A3-192/96, M4A5-192/96   | M4A3-64/64       |

|                          | M4A3-256/128, M4A5-256/128 | M4A3-256/160     |

|                          | M4A3-384                   | M4A3-256/192     |

|                          | M4A3-512                   |                  |

| Macrocell-I/O Cell Ratio | 2:1                        | 1:1              |

| Input Switch Matrix      | Yes                        | Yes <sup>1</sup> |

| Input Registers          | Yes                        | No               |

| Central Switch Matrix    | Yes                        | Yes              |

| Output Switch Matrix     | Yes                        | Yes              |

The Macrocell-I/O cell ratio is defined as the number of macrocells versus the number of I/O cells internally in a PAL block (Table 4).

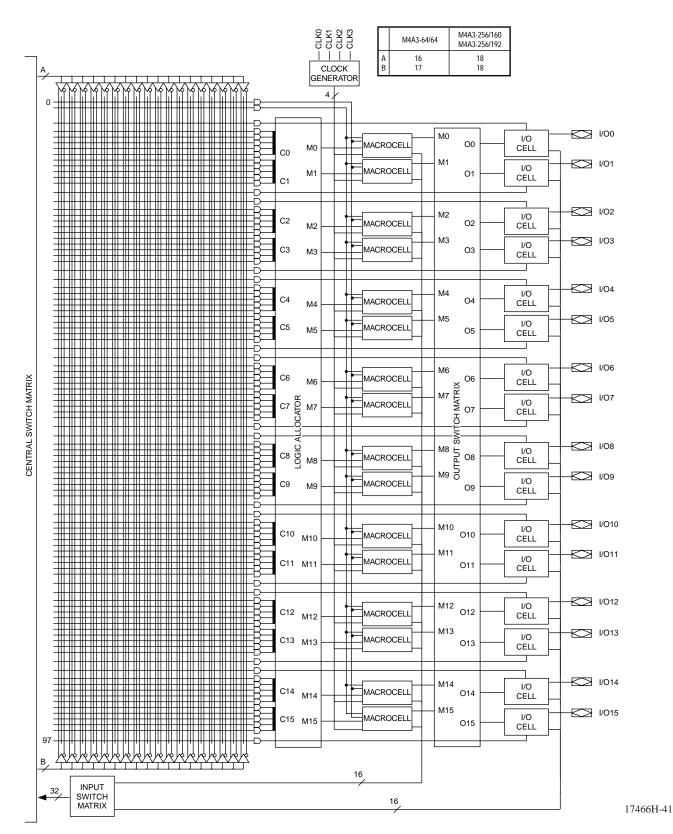

The central switch matrix takes all dedicated inputs and signals from the input switch matrices and routes them as needed to the PAL blocks. Feedback signals that return to the same PAL block still must go through the central switch matrix. This mechanism ensures that PAL blocks in ispMACH 4A devices communicate with each other with consistent, predictable delays.

The central switch matrix makes a ispMACH 4A device more advanced than simply several PAL devices on a single chip. It allows the designer to think of the device not as a collection of blocks, but as a single programmable device; the software partitions the design into PAL blocks through the central switch matrix so that the designer does not have to be concerned with the internal architecture of the device.

Each PAL block consists of:

- Product-term array

- Logic allocator

- Macrocells

- Output switch matrix

- ◆ I/O cells

- Input switch matrix

- Clock generator

### Notes:

1. M4A3-64/64 internal switch matrix functionality embedded in central switch matrix.

## **Product-Term Array**

The product-term array consists of a number of product terms that form the basis of the logic being implemented. The inputs to the AND gates come from the central switch matrix (Table 5), and are provided in both true and complement forms for efficient logic implementation.

| Device                        | Number of Inputs to PAL Block |

|-------------------------------|-------------------------------|

| M4A3-32/32 and M4A5-32/32     | 33                            |

| M4A3-64/32 and M4A5-64/32     | 33                            |

| M4A3-64/64                    | 33                            |

| M4A3-96/48 and M4A5-96/48     | 33                            |

| M4A3-128/64 and M4A5-128/64   | 33                            |

| M4A3-192/96 and M4A5-192/96   | 34                            |

| M4A3-256/128 and M4A5-256/128 | 34                            |

| M4A3-256/160 and M4A3-256/192 | 36                            |

| M4A3-384                      | 36                            |

| M4A3-512                      | 36                            |

**Table 5. PAL Block Inputs**

## **Logic Allocator**

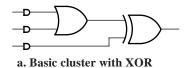

Within the logic allocator, product terms are allocated to macrocells in "product term clusters." The availability and distribution of product term clusters are automatically considered by the software as it fits functions within a PAL block. The size of a product term cluster has been optimized to provide high utilization of product terms, making complex functions using many product terms possible. Yet when few product terms are used, there will be a minimal number of unused—or wasted—product terms left over. The product term clusters available to each macrocell within a PAL block are shown in Tables 6 and 7.

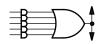

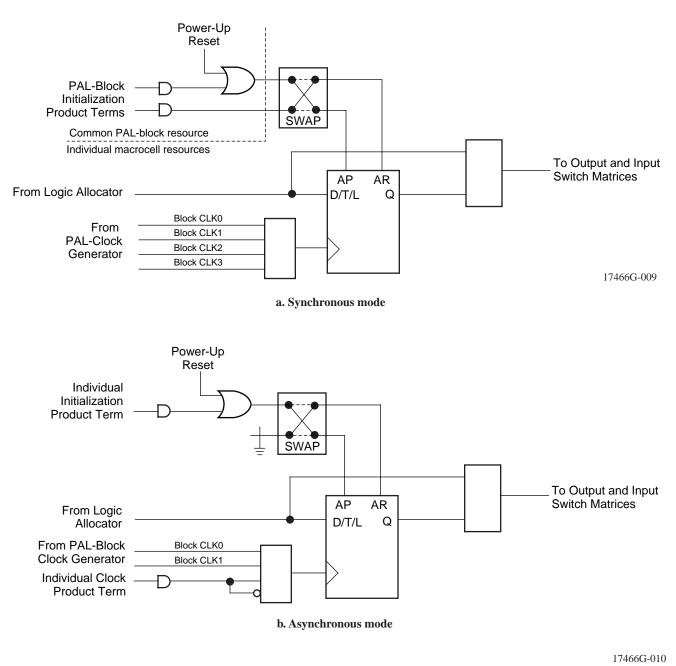

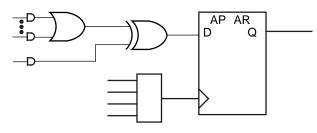

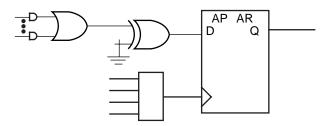

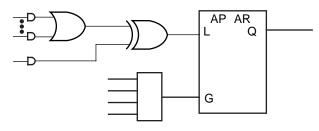

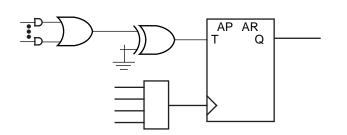

Each product term cluster is associated with a macrocell. The size of a cluster depends on the configuration of the associated macrocell. When the macrocell is used in synchronous mode

(Figure 2a), the basic cluster has 4 product terms. When the associated macrocell is used in asynchronous mode (Figure 2b), the cluster has 2 product terms. Note that if the product term cluster is routed to a different macrocell, the allocator configuration is not determined by the mode of the macrocell actually being driven. The configuration is always set by the mode of the macrocell that the cluster will drive if not routed away, regardless of the actual routing.

In addition, there is an extra product term that can either join the basic cluster to give an extended cluster, or drive the second input of an exclusive-OR gate in the signal path. If included with the basic cluster, this provides for up to 20 product terms on a synchronous function that uses four extended 5-product-term clusters. A similar asynchronous function can have up to 18 product terms.

When the extra product term is used to extend the cluster, the value of the second XOR input can be programmed as a 0 or a 1, giving polarity control. The possible configurations of the logic allocator are shown in Figures 3 and 4.

a. Basic cluster with XOR

b. Extended cluster, active high

c. Extended cluster, active low

d. Basic cluster routed away; single-product-term, active high

e. Extended cluster routed away

17466G-007

Figure 3. Logic Allocator Configurations: Synchronous Mode

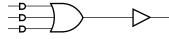

b. Extended cluster, active high

c. Extended cluster, active low

d. Basic cluster routed away; single-product-term, active high

e. Extended cluster routed away

17466G-008

Figure 4. Logic Allocator Configurations: Asynchronous Mode

Note that the configuration of the logic allocator has absolutely no impact on the speed of the signal. All configurations have the same delay. This means that designers do not have to decide between optimizing resources or speed; both can be optimized.

If not used in the cluster, the extra product term can act in conjunction with the basic cluster to provide XOR logic for such functions as data comparison, or it can work with the D-,T-type flip-flop to provide for J-K, and S-R register operation. In addition, if the basic cluster is routed to another macrocell, the extra product term is still available for logic. In this case, the first XOR input will be a logic 0. This circuit has the flexibility to route product terms elsewhere without giving up the use of the macrocell.

Product term clusters do not "wrap" around a PAL block. This means that the macrocells at the ends of the block have fewer product terms available.

## Macrocell

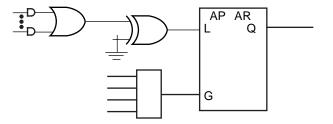

The macrocell consists of a storage element, routing resources, a clock multiplexer, and initialization control. The macrocell has two fundamental modes: synchronous and asynchronous (Figure 5). The mode chosen only affects clocking and initialization in the macrocell.

Figure 5. Macrocell

In either mode, a combinatorial path can be used. For combinatorial logic, the synchronous mode will generally be used, since it provides more product terms in the allocator.

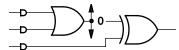

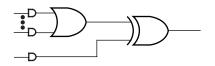

The flip-flop can be configured as a D-type or T-type latch. J-K or S-R registers can be synthesized. The primary flip-flop configurations are shown in Figure 6, although others are possible. Flip-flop functionality is defined in Table 8. Note that a J-K latch is inadvisable as it will cause oscillation if both J and K inputs are HIGH.

a. D-type with XOR

b. D-type with programmable D polarity

c. Latch with XOR

e. T-type with programmable T polarity

d. Latch with programmable D polarity

f. Combinatorial with XOR

g. Combinatorial with programmable polarity

17466G-011

**Figure 6. Primary Macrocell Configurations**

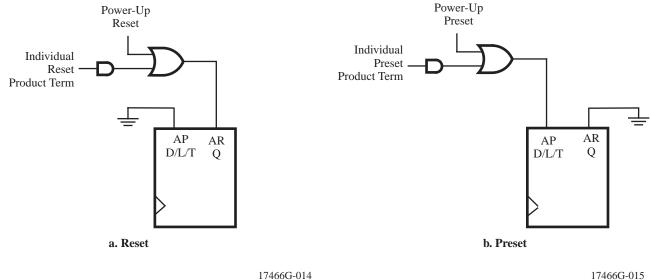

A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing flexibility. In asynchronous mode (Figure 8), a single individual product term is provided for initialization. It can be selected to control reset or preset.

Figure 8. Asynchronous Mode Initialization Configurations

17466G-015

Note that the reset/preset swapping selection feature effects power-up reset as well. The initialization functionality of the flip-flops is illustrated in Table 9. The macrocell sends its data to the output switch matrix and the input switch matrix. The output switch matrix can route this data to an output if so desired.

The input switch matrix can send the signal back to the central switch matrix as feedback.

| Table 5. Asynchronous Researcesco Operation |    |                     |             |  |  |

|---------------------------------------------|----|---------------------|-------------|--|--|

| AR                                          | AP | CLK/LE <sup>1</sup> | Q+          |  |  |

| 0                                           | 0  | Х                   | See Table 8 |  |  |

| 0                                           | 1  | Х                   | 1           |  |  |

| 1                                           | 0  | Х                   | 0           |  |  |

| 1                                           | 1  | Х                   | 0           |  |  |

Table 9. Asynchronous Reset/Preset Operation

#### Note:

1. Transparent latch is unaffected by AR, AP

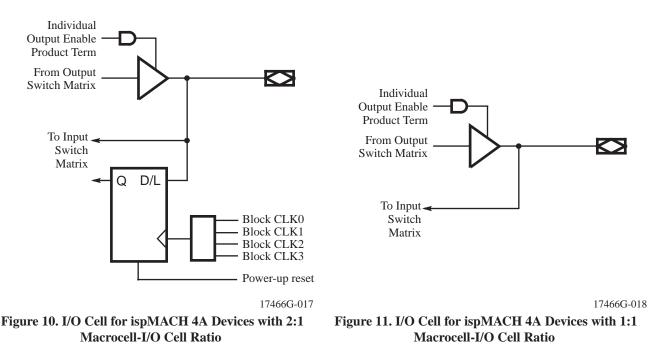

## I/O Cell

The I/O cell (Figures 10 and 11) simply consists of a programmable output enable, a feedback path, and flip-flop (except ispMACH 4A devices with 1:1 macrocell-I/O cell ratio). An individual output enable product term is provided for each I/O cell. The feedback signal drives the input switch matrix.

The I/O cell (Figure 10) contains a flip-flop, which provides the capability for storing the input in a D-type register or latch. The clock can be any of the PAL block clocks. Both the direct and registered versions of the input are sent to the input switch matrix. This allows for such functions as "time-domain-multiplexed" data comparison, where the first data value is stored, and then the second data value is put on the I/O pin and compared with the previous stored value.

Note that the flip-flop used in the ispMACH 4A I/O cell is independent of the flip-flops in the macrocells. It powers up to a logic low.

## Zero-Hold-Time Input Register

The ispMACH 4A devices have a zero-hold-time (ZHT) fuse which controls the time delay associated with loading data into all I/O cell registers and latches. When programmed, the ZHT fuse increases the data path setup delays to input storage elements, matching equivalent delays in the clock path. When the fuse is erased, the setup time to the input storage element is minimized. This feature facilitates doing worst-case designs for which data is loaded from sources which have low (or zero) minimum output propagation delays from clock edges.

weakly pulled up. For the circuit diagram, please refer to the document entitled *MACH Endurance Characteristics* on the Lattice Data Book CD-ROM or Lattice web site.

# **POWER MANAGEMENT**

Each individual PAL block in ispMACH 4A devices features a programmable low-power mode, which results in power savings of up to 50%. The signal speed paths in the low-power PAL block will be slower than those in the non-low-power PAL block. This feature allows speed critical paths to run at maximum frequency while the rest of the signal paths operate in the low-power mode.

# PROGRAMMABLE SLEW RATE

Each ispMACH 4A device I/O has an individually programmable output slew rate control bit. Each output can be individually configured for the higher speed transition (3 V/ns) or for the lower noise transition (1 V/ns). For high-speed designs with long, unterminated traces, the slow-slew rate will introduce fewer reflections, less noise, and keep ground bounce to a minimum. For designs with short traces or well terminated lines, the fast slew rate can be used to achieve the highest speed. The slew rate is adjusted independent of power.

## **POWER-UP RESET/SET**

All flip-flops power up to a known state for predictable system initialization. If a macrocell is configured to SET on a signal from the control generator, then that macrocell will be SET during device power-up. If a macrocell is configured to RESET on a signal from the control generator or is not configured for set/reset, then that macrocell will RESET on power-up. To guarantee initialization values, the  $V_{CC}$  rise must be monotonic, and the clock must be inactive until the reset delay time has elapsed.

## **SECURITY BIT**

A programmable security bit is provided on the ispMACH 4A devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. Programming and verification are also defeated by the security bit. The bit can only be reset by erasing the entire device.

# HOT SOCKETING

ispMACH 4A devices are well-suited for those applications that require hot socketing capability. Hot socketing a device requires that the device, when powered down, can tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of the powered-down MACH devices be minimal on active signals.

Figure 17. PAL Block for ispMACH 4A Devices with 1:1 Macrocell-I/O Cell Ratio (except M4A (3,5)-32/32)

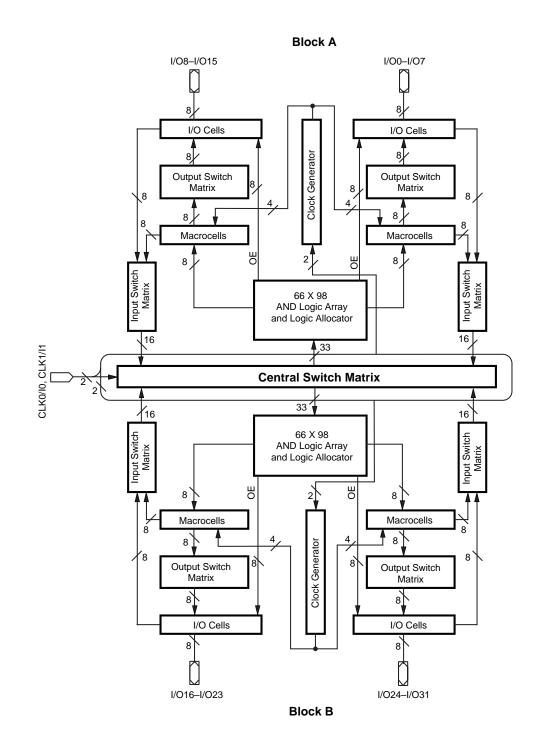

# BLOCK DIAGRAM – M4A(3,5)-32/32

17466H-019

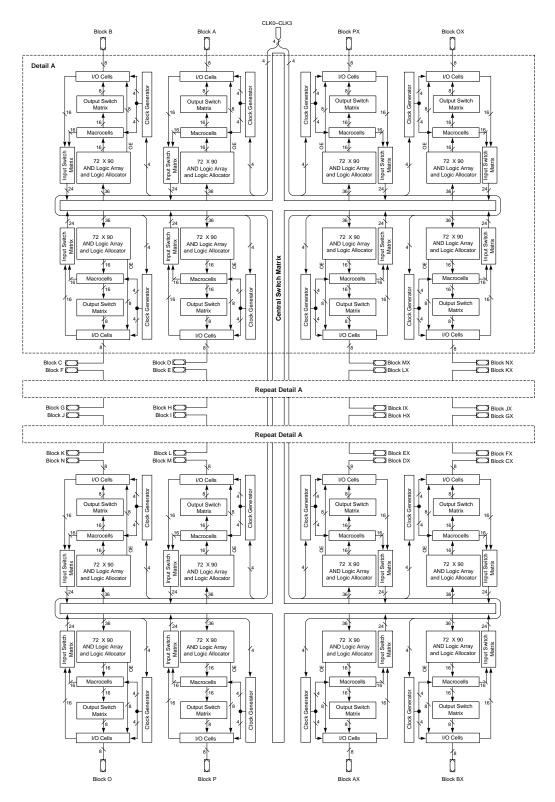

## BLOCK DIAGRAM - M4A3-512/160, M4A3-512/192, M4A3-512/256

17466G-068

# **ABSOLUTE MAXIMUM RATINGS**

## M4A5

| Storage Temperature65°C to +150°C                                        |

|--------------------------------------------------------------------------|

| Ambient Temperature<br>with Power Applied55°C to +100°C                  |

| Device Junction Temperature+130°C                                        |

| Supply Voltage with Respect to Ground                                    |

| DC Input Voltage                                                         |

| Static Discharge Voltage 2000 V                                          |

| Latchup Current (T <sub>A</sub> = -40°C to +85°C)200 mA                  |

| Straccas above these listed under Absolute Maximum Patings may cause per |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

### **Commercial (C) Devices**

| $ \begin{array}{l} \mbox{Ambient Temperature (T_A)} \\ \mbox{Operating in Free Air} \dots & 0^{\circ}\mbox{C to } +70^{\circ}\mbox{C} \end{array} $ |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Supply Voltage (V_CC) with Respect to Ground                                                                                                        |  |

## Industrial (I) Devices

| Ambient Temperature (T <sub>A</sub> ) |

|---------------------------------------|

| Operating in Free Air40°C to +85°C    |

| Supply Voltage (V <sub>CC</sub> )     |

| with Respect to Ground                |

|                                       |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# **5-V DC CHARACTERISTICS OVER OPERATING RANGES**

| Parameter<br>Symbol | Parameter Description                 | Test Conditions                                                                | Min | Тур | Max  | Unit |

|---------------------|---------------------------------------|--------------------------------------------------------------------------------|-----|-----|------|------|

| V                   | Output HIGH Voltage                   | $I_{OH}=-3.2$ mA, $V_{CC}=$ Min, $V_{IN}=V_{IH} or  V_{IL}$                    | 2.4 |     |      | V    |

| V <sub>OH</sub>     | ouput mon vonage                      | $I_{OH}$ = -100 $\mu\text{A},V_{CC}$ = Max, $V_{IN}$ = $V_{IH}\text{or}V_{IL}$ |     | 3.3 | 3.6  | V    |

| V <sub>OL</sub>     | Output LOW Voltage                    | $I_{OL} = 24$ mA, $V_{CC} = Min,  V_{IN} = V_{IH} \text{ or } V_{IL}$ (Note 1) |     |     | 0.5  | V    |

| V <sub>IH</sub>     | Input HIGH Voltage                    | Guaranteed Input Logical HIGH Voltage for all Inputs (Note 2)                  | 2.0 |     |      | V    |

| V <sub>IL</sub>     | Input LOW Voltage                     | Guaranteed Input Logical LOW Voltage for all Inputs<br>(Note 2)                |     |     | 0.8  | V    |

| I <sub>IH</sub>     | Input HIGH Leakage Current            | $V_{IN} = 5.25$ V, $V_{CC} = Max$ (Note 3)                                     |     |     | 10   | μA   |

| I <sub>IL</sub>     | Input LOW Leakage Current             | $V_{IN} = 0$ V, $V_{CC} = Max$ (Note 3)                                        |     |     | -10  | μA   |

| I <sub>OZH</sub>    | Off-State Output Leakage Current HIGH | $V_{OUT} = 5.25$ V, $V_{CC} = Max,  V_{IN} = V_{IH}  or  V_{IL}$ (Note 3)      |     |     | 10   | μA   |

| I <sub>OZL</sub>    | Off-State Output Leakage Current LOW  | $V_{OUT}=0$ V, $V_{CC}=Max$ , $V_{IN}=V_{IH} \mbox{ or } V_{IL}$ (Note 3)      |     |     | -10  | μΑ   |

| I <sub>SC</sub>     | Output Short-Circuit Current          | $V_{OUT} = 0.5$ V, $V_{CC} = Max$ (Note 4)                                     | -30 |     | -160 | mA   |

### Notes:

1. Total I<sub>OL</sub> for one PAL block should not exceed 64 mA.

2. These are absolute values with respect to device ground, and all overshoots due to system or tester noise are included.

3. I/O pin leakage is the worst case of  $I_{IL}$  and  $I_{OZL}$  (or  $I_{IH}$  and  $I_{OZH}$ ).

4. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.  $V_{OUT} = 0.5 V$  has been chosen to avoid test problems caused by tester ground degradation.

# **ABSOLUTE MAXIMUM RATINGS**

### M4A3

| Storage Temperature65°C to +150°C                                         |

|---------------------------------------------------------------------------|

| Ambient Temperature<br>with Power Applied55°C to +100°C                   |

| Device Junction Temperature+130°C                                         |

| Supply Voltage with Respect to Ground                                     |

| DC Input Voltage                                                          |

| Static Discharge Voltage 2000 V                                           |

| Latchup Current (T <sub>A</sub> = -40°C to +85°C)200 mA                   |

| Stresses above those listed under Absolute Maximum Ratings may cause per- |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

### **Commercial (C) Devices**

| $\begin{array}{l} \mbox{Ambient Temperature (T_A)} \\ \mbox{Operating in Free Air} &  & \mbox{0°C to } +70^{\circ}\mbox{C} \end{array}$ |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage (V $_{CC}$ ) with Respect to Ground                                                                                      |

## Industrial (I) Devices

| Ambient Temperature (T <sub>A</sub> )   |

|-----------------------------------------|

| Operating in Free Air40°C to +85°C      |

| Supply Voltage (V <sub>CC</sub> )       |

| with Respect to Ground +3.0 V to +3.6 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# **3.3-V DC CHARACTERISTICS OVER OPERATING RANGES**

| Parameter<br>Symbol | Parameter Description                 | Test Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ditions                    | Min            | Тур | Max  | Unit |

|---------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------|-----|------|------|

| V                   | Output HIGH Voltage                   | V <sub>CC</sub> = Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OH}=-100\;\mu\text{A}$ | $V_{CC} - 0.2$ |     |      | V    |

| V <sub>OH</sub>     | ouput mon vonage                      | $V_{IN} = V_{IH} \text{ or } V_{IL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $I_{OH} = -3.2 \text{ mA}$ | 2.4            |     |      | V    |

| V <sub>OL</sub>     | Output LOW Voltage                    | $\label{eq:constraint} \begin{array}{ c c c c c } \hline V_{IN} = V_{IH} \mbox{ or } V_{IL} & \hline I_{OH} = -3.2 \mbox{ mA} \\ \hline V_{CC} = Min \\ V_{IN} = V_{IH} \mbox{ or } V_{IL} \\ \hline (Note 1) & \hline I_{OL} = 100 \mbox{ $\mu$A} \\ \hline I_{OL} = 24 \mbox{ mA} \\ \hline I_{OL} = 20 \mbox{ mA} \\ \hline I_{O$ |                            |                |     | 0.2  | V    |

| 0L                  |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $I_{OL} = 24 \text{ mA}$   |                |     | 0.5  | V    |

| V <sub>IH</sub>     | Input HIGH Voltage                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l HIGH Voltage for all     | 2.0            |     | 5.5  | V    |

| V <sub>IL</sub>     | Input LOW Voltage                     | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | l LOW Voltage for all      | -0.3           |     | 0.8  | V    |

| I <sub>IH</sub>     | Input HIGH Leakage Current            | $V_{\rm IN}=3.6$ V, $V_{\rm CC}={ m Max}$ (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Note 2)                    |                |     | 5    | μA   |

| IIL                 | Input LOW Leakage Current             | $V_{\rm IN} = 0$ V, $V_{\rm CC} = {\rm Max}$ (No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ote 2)                     |                |     | -5   | μA   |

| I <sub>OZH</sub>    | Off-State Output Leakage Current HIGH | $V_{OUT} = 3.6 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                |     | 5    | μA   |

| I <sub>OZL</sub>    | Off-State Output Leakage Current LOW  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |     | -5   | μA   |

| I <sub>SC</sub>     | Output Short-Circuit Current          | $V_{OUT} = 0.5$ V, $V_{CC} = Max$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (Note 3)                   | -15            |     | -160 | mA   |

#### Notes:

- 1. Total I<sub>OL</sub> for one PAL block should not exceed 64 mA.

- 2. I/O pin leakage is the worst case of  $I_{IL}$  and  $I_{OZL}$  (or  $I_{IH}$  and  $I_{OZH}$ ).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

### Notes:

- 1. See "MACH Switching Test Circuit" document on the Literature Download page of the Lattice web site.

- 2. This parameter does not apply to flip-flops in the emulated mode since the feedback path is required for emulation.

#### is pMACH 4A TIMING PARAMETERS OVER OPERATING RANGES $^{\rm 1}$

|                   |                                                                                                                                                 | -   | 5   | -5  | 55  | -   | 6   | -(   | 35  | -    | 7   | -1   | 10  | -1   | 12  | -1   | 14  |      |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|

|                   |                                                                                                                                                 | Min | Max | Min | Max | Min | Max | Min  | Max | Min  | Max | Min  | Max | Min  | Max | Min  | Max | Unit |

| Frequ             | iency:                                                                                                                                          |     |     |     |     |     |     |      |     |      |     |      |     |      |     |      |     |      |

|                   | External feedback, D-type, Min of $1/(t_{WLS} + t_{WHS})$ or $1/(t_{SS} + t_{COS})$                                                             | 143 |     | 133 |     | 125 |     | 118  |     | 95.2 |     | 87.0 |     | 74.1 |     | 60.6 |     | MHz  |

|                   | External feedback, T-type, Min of $1/(t_{WLS} + t_{WHS})$ or $1/(t_{SST} + t_{COS})$                                                            | 125 |     | 125 |     | 118 |     | 111  |     | 87.0 |     | 80.0 |     | 69.0 |     | 57.1 |     | MHz  |

| f <sub>MAXS</sub> | Internal feedback ( $f_{CNT}$ ), D-type, Min of $1/(t_{WLS} + t_{WHS})$ or $1/(t_{SS} + t_{COSi})$                                              | 182 |     | 167 |     | 160 |     | 154  |     | 125  |     | 118  |     | 95.0 |     | 74.1 |     | MHz  |

|                   | Internal feedback ( $f_{CNT}$ ), T-type, Min of $1/(t_{WLS} + t_{WHS})$ or $1/(t_{SST} + t_{COSi})$                                             | 154 |     | 154 |     | 148 |     | 143  |     | 111  |     | 105  |     | 87.0 |     | 69.0 |     | MHz  |

|                   | No feedback <sup>2</sup> , Min of $1/(t_{WLS} + t_{WHS})$ ,<br>$1/(t_{SS} + t_{HS})$ or $1/(t_{SST} + t_{HS})$                                  | 250 |     | 250 |     | 200 |     | 200  |     | 154  |     | 125  |     | 100  |     | 83.3 |     | MHz  |

|                   | External feedback, D-type, Min of 1/ $(t_{WLA} + t_{WHA})$ or 1/ $(t_{SA} + t_{COA})$                                                           | 111 |     | 111 |     | 108 |     | 100  |     | 83.3 |     | 66.7 |     | 55.6 |     | 43.5 |     | MHz  |

|                   | External feedback, T-type, Min of $1/(t_{WLA} + t_{WHA})$ or $1/(t_{SAT} + t_{COA})$                                                            | 105 |     | 105 |     | 102 |     | 95.2 |     | 76.9 |     | 62.5 |     | 52.6 |     | 41.7 |     | MHz  |

| f <sub>MAXA</sub> | $ \begin{array}{l} \mbox{Internal feedback (f_{CNTA}), D-type, Min of} \\ 1/(t_{WLA} + t_{WHA}) \mbox{ or } 1/(t_{SA} + t_{COAi}) \end{array} $ | 133 |     | 133 |     | 125 |     | 125  |     | 105  |     | 83.3 |     | 66.7 |     | 50.0 |     | MHz  |

|                   | Internal feedback ( $f_{CNTA}$ ), T-type, Min of $1/(t_{WLA} + t_{WHA})$ or $1/(t_{SAT} + t_{COAi})$                                            | 125 |     | 125 |     | 125 |     | 118  |     | 95.2 |     | 76.9 |     | 62.5 |     | 47.6 |     | MHz  |

|                   | No feedback <sup>2</sup> , Min of $1/(t_{WLA} + t_{WHA})$ , $1/(t_{SA} + t_{HA})$ or $1/(t_{SAT} + t_{HA})$                                     | 167 |     | 167 |     | 143 |     | 143  |     | 125  |     | 100  |     | 62.5 |     | 55.6 |     | MHz  |

| f <sub>MAXI</sub> | Maximum input register frequency, Min of $1/(t_{WIRH} + t_{WIRL})$ or $1/(t_{SIRS} + t_{HIRS})$                                                 | 167 |     | 167 |     | 143 |     | 143  |     | 125  |     | 100  |     | 83.3 |     | 83.3 |     | MHz  |

### Notes:

1. See "Switching Test Circuit" document on the Literature Download page of the Lattice web site.

2. This parameter does not apply to flip-flops in the emulated mode since the feedback path is required for emulation.

# CAPACITANCE<sup>1</sup>

| Parameter Symbol | Parameter Description | Test Co                | nditions                  | Тур | Unit |

|------------------|-----------------------|------------------------|---------------------------|-----|------|

| C <sub>IN</sub>  | Input capacitance     | V <sub>IN</sub> =2.0 V | 3.3 V or 5 V, 25°C, 1 MHz | 6   | pF   |

| C <sub>I/O</sub> | Output capacitance    | V <sub>OUT</sub> =2.0V | 3.3 V or 5 V, 25°C, 1 MHz | 8   | pF   |

### Note:

1. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where this parameter may be affected.

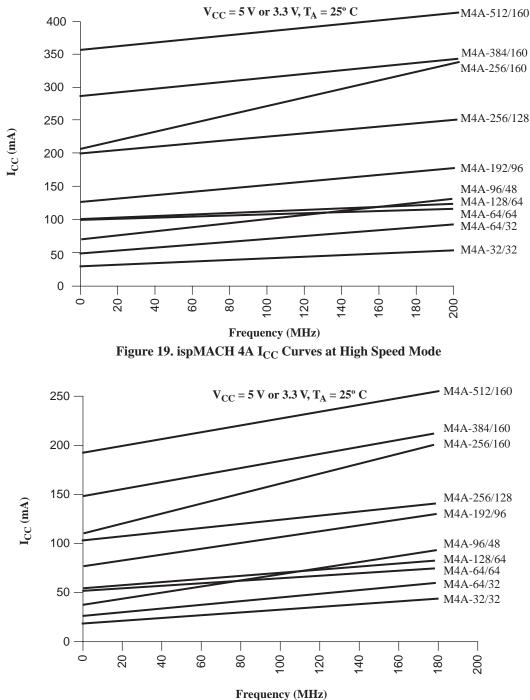

# I<sub>CC</sub> vs. FREQUENCY

These curves represent the typical power consumption for a particular device at system frequency. The selected "typical" pattern is a 16-bit up-down counter. This pattern fills the device and exercises every macrocell. Maximum frequency shown uses internal feedback and a D-type register. Power/Speed are optimized to obtain the highest counter frequency and the lowest power. The highest frequency (LSBs) is placed in common PAL blocks, which are set to high power. The lowest frequency signals (MSBs) are placed in a common PAL block and set to lowest power.

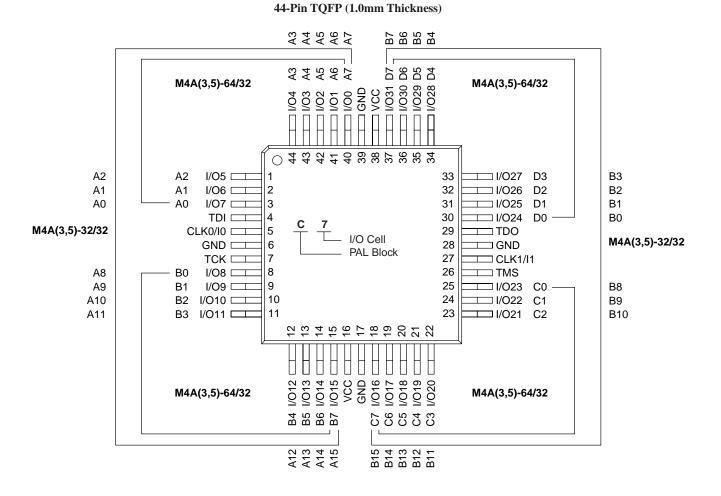

# 44-PIN TQFP CONNECTION DIAGRAM (M4A(3,5)-32/32 AND M4A(3,5)-64/32)

### **Top View**

## **PIN DESIGNATIONS**

- CLK/I = Clock or Input

- GND = Ground

- I/O = Input/Output

- $V_{CC}$  = Supply Voltage

- TDI = Test Data In

- TCK = Test Clock

- TMS = Test Mode Select

- TDO = Test Data Out

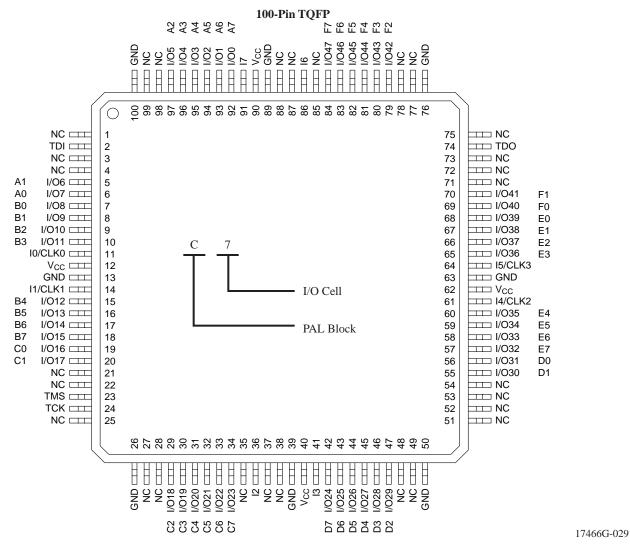

## 100-PIN TQFP CONNECTION DIAGRAM (M4A(3,5)-96/48)

### **Top View**

## **PIN DESIGNATIONS**

- CLK/I = Clock or Input

- GND = Ground

- I = Input

- I/O = Input/Output

- V<sub>CC</sub> = Supply Voltage

- NC = No Connect

- TDI = Test Data In

- TCK = Test Clock

- TMS = Test Mode Select

- TDO = Test Data Out

# 100-PIN TQFP CONNECTION DIAGRAM (M4A3-64/64 AND M4A(3,5)-128/64)

### **Top View**

100-Pin TQFP M4A3-128/64 M4A5-128/64 A12 A12 A2 A2 A2 A2 A2 A2 A2 A2 M4A3-64/64 B F Ó 1 75 74 2 3 4 I/O8 \_\_\_\_ B7 73 A1 B6 A3 I/O9 \_\_\_\_ 72 1/O55 D1 G7 B5 A5 I/O10 \_\_\_\_ 5 71 1/O54 D3 G6 B4 B3 70 69 1/053 1/052 D5 D7 G5 G4 A7 I/011 \_\_\_\_ 6 7 A9 I/012 \_\_\_\_ B2 1/051 D9 G3 A11 I/O13 \_\_\_\_ 68 8 B1 I/014 💷 HTT 1/050 D11 G2 A13 9 67 I/O49 III I/O48 III I4/CLK3 B0 A15 I/O15 💷 10 66 D13 G1 I0/CLK0 11 65 D15 G0 12 64 13 63 I/O Cell I1/CLK1 14 62 C0 B15 I/O16 🗆 🗆 15 61 60 59 F0 C1 C2 C3 C4 C5 C6 C7 B13 1/017 16 17 C15 PAL Block 1/046 C13 C11 I/O18 \_\_\_\_ F1 B11 I/O19 💷 18 58 1/045 F2 В9 B7 I/O20 \_\_\_\_ 19 57 └── I/O44 C9 F3 1/043 1/042 C7 C5 C3 B5 I/O21 \_\_\_\_ 20 56 F4 1/022 21 22 55 54 F5 B3 B1 1/023 -----I/041 F6 TMS CTT 23 53 1/O40 C1 F7 24 25 тск 💷 52 51 HHHH GND GND (0224) (0224) (0226) (0230) (0231) (0231) (0231) (0231) (0231) (0232) (0232) (0232) (0232) (0232) (0232) (0232) (0232) (0232) (0232) (0232) (0232) (0232) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (0222) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (022) (0 17466G-032a E0 E1 E2 E3 E5 E7 E7

## **PIN DESIGNATIONS**

- CLK/I = Clock or Input

- GND = Ground

- I = Input

- I/O = Input/Output

- $V_{CC}$  = Supply Voltage

- TDI = Test Data In

- TCK = Test Clock

- TMS = Test Mode Select

- TDO = Test Data Out

- $\overline{\text{TRST}}$  = Test Reset

- $\overline{\text{ENABLE}} = \text{Program}$

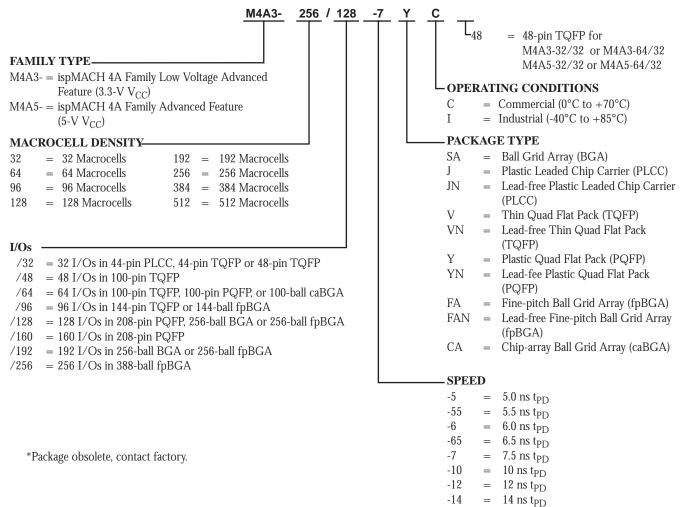

# ispMACH 4A PRODUCT ORDERING INFORMATION

### ispMACH 4A Devices Commercial and Industrial - 3.3V and 5V

Lattice programmable logic products are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

### **Conventional Packaging**

| 3.3          | <b>W Commercial Combin</b>      | nations      |

|--------------|---------------------------------|--------------|

| M4A3-32/32   | -5, -7, -10                     | JC, VC, VC48 |

| M4A3-64/32   |                                 | JC, VC, VC48 |

| M4A3-64/64   | -55, -7, -10                    | VC           |

| M4A3-96/48   | -33, -7, -10                    | VC           |

| M4A3-128/64  |                                 | YC, VC, CAC  |

| M4A3-192/96  | -6, -7, -10                     | VC, FAC      |

| M4A3-256/128 | -55, -65 <sup>1</sup> , -7, -10 | YC, FAC, SAC |

| M4A3-256/160 | -710                            | YC           |

| M4A3-256/192 | -7, -10                         | FAC          |

| M4A3-384/160 | -65, -10, -12                   | YC           |

| M4A3-384/192 | -03, -10, -12                   | SAC, FAC     |

| M4A3-512/160 |                                 | YC           |

| M4A3-512/192 | -7, -10, -12                    | FAC          |

| M4A3-512/256 |                                 | FAC          |

1. Use 5.5ns for new designs.