#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                       |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 266MHz                                                       |

| Co-Processors/DSP               | Security; SEC                                                |

| RAM Controllers                 | DDR                                                          |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (2)                                          |

| SATA                            | -                                                            |

| USB                             | USB 2.0 + PHY (2)                                            |

| Voltage - I/O                   | 2.5V, 3.3V                                                   |

| Operating Temperature           | -40°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                        |

| Package / Case                  | 620-BBGA Exposed Pad                                         |

| Supplier Device Package         | 620-HBGA (29x29)                                             |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8347ecvraddb |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter                                                                          | Symbol <sup>1</sup>                         | Min                          | Мах                          | Unit | Notes |

|------------------------------------------------------------------------------------|---------------------------------------------|------------------------------|------------------------------|------|-------|

| MCK[n] cycle time, (MCK[n]/MCK[n] crossing)                                        | t <sub>MCK</sub>                            | 6                            | 10                           | ns   | 2     |

| Skew between any MCK to ADDR/CMD<br>333 MHz<br>266 MHz<br>200 MHz                  | t <sub>aoskew</sub>                         | -1000<br>-1100<br>-1200      | 200<br>300<br>400            | ps   | 3     |

| ADDR/CMD output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz         | <sup>t</sup> DDKHAS                         | 2.8<br>3.45<br>4.6           | _                            | ns   | 4     |

| ADDR/CMD output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz          | t <sub>DDKHAX</sub>                         | 2.0<br>2.65<br>3.8           | _                            | ns   | 4     |

| MCS(n) output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz           | t <sub>DDKHCS</sub>                         | 2.8<br>3.45<br>4.6           | —                            | ns   | 4     |

| MCS(n) output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz            | <sup>t</sup> DDKHCX                         | 2.0<br>2.65<br>3.8           | _                            | ns   | 4     |

| MCK to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                                       | <sup>t</sup> DDKHMH                         | -0.9<br>-1.1<br>-1.2         | 0.3<br>0.5<br>0.6            | ns   | 5     |

| MDQ/MECC/MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 900<br>900<br>1200           | _                            | ps   | 6     |

| MDQ/MECC/MDM output hold with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz  | <sup>t</sup> ddkhdx,<br><sup>t</sup> ddkldx | 900<br>900<br>1200           | _                            | ps   | 6     |

| MDQS preamble start                                                                | t <sub>DDKHMP</sub>                         | $-0.25 \times t_{MCK} - 0.9$ | $-0.25 \times t_{MCK}$ + 0.3 | ns   | 7     |

#### DDR SDRAM

### Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter         | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|-------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end | t <sub>DDKLME</sub> | -0.9 | 0.3 | ns   | 7     |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. In the source synchronous mode, MCK/MCK can be shifted in 1/4 applied cycle increments through the clock control register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8349E PowerQUICC<sup>™</sup> II Pro Integrated Host Processor Family Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8347E.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the MPC8347E. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

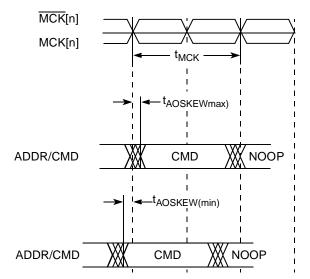

Figure 5 shows the DDR SDRAM output timing for address skew with respect to any MCK.

Figure 5. Timing Diagram for t<sub>AOSKEW</sub> Measurement

Figure 6 provides the AC test load for the DDR bus.

# 8 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speeds (10/100/1000 Mbps) and MII management.

# 8.1 Three-Speed Ethernet Controller (TSEC)— GMII/MII/TBI/RGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to the gigabit media independent interface (GMII), the media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), and reduced ten-bit interface (RTBI) signals except management data input/output (MDIO) and management data clock (MDC). The MII, GMII, and TBI interfaces are defined for 3.3 V, and the RGMII and RTBI interfaces are defined for 2.5 V. The RGMII and RTBI interfaces follow the Hewlett-Packard *Reduced Pin-Count Interface for Gigabit Ethernet Physical Layer Device Specification*, Version 1.2a (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

# 8.1.1 **TSEC DC Electrical Characteristics**

GMII, MII, TBI, RGMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 19 and Table 20. The RGMII and RTBI signals in Table 20 are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter            | Symbol                        | Conditions                                |                                    | Min  | Мах                    | Unit |

|----------------------|-------------------------------|-------------------------------------------|------------------------------------|------|------------------------|------|

| Supply voltage 3.3 V | LV <sub>DD</sub> <sup>2</sup> | —                                         |                                    | 2.97 | 3.63                   | V    |

| Output high voltage  | V <sub>OH</sub>               | I <sub>OH</sub> = -4.0 mA                 | LV <sub>DD</sub> = Min             | 2.40 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>               | $I_{OL} = 4.0 \text{ mA}$ $LV_{DD} = Min$ |                                    | GND  | 0.50                   | V    |

| Input high voltage   | V <sub>IH</sub>               |                                           |                                    | 2.0  | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>               | —                                         |                                    |      | 0.90                   | V    |

| Input high current   | IIH                           | $V_{IN}^{1} = LV_{DD}$                    |                                    | —    | 40                     | μΑ   |

| Input low current    | ۱ <sub>IL</sub>               | V <sub>IN</sub> <sup>1</sup> =            | V <sub>IN</sub> <sup>1</sup> = GND |      | —                      | μΑ   |

Table 19. GMII/TBI and MII DC Electrical Characteristics

#### Notes:

1. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

2. GMII/MII pins not needed for RGMII or RTBI operation are powered by the  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  supply.

9 USB

This section provides the AC and DC electrical specifications for the USB interface of the MPC8347E.

### 9.1 USB DC Electrical Characteristics

Table 31 provides the DC electrical characteristics for the USB interface.

| Parameter                                            | Symbol          | Min                    | Мах                    | Unit |

|------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current                                        | I <sub>IN</sub> | —                      | ±5                     | μA   |

| High-level output voltage, I <sub>OH</sub> = −100 μA | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$     | V <sub>OL</sub> | _                      | 0.2                    | V    |

### Table 31. USB DC Electrical Characteristics

# 9.2 USB AC Electrical Specifications

Table 32 describes the general timing parameters of the USB interface of the MPC8347E.

| Table 32. USB General Timing | Parameters ( | ULPI Mode Only) |

|------------------------------|--------------|-----------------|

|------------------------------|--------------|-----------------|

| Parameter                              | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|----------------------------------------|---------------------|-----|-----|------|-------|

| USB clock cycle time                   | t <sub>USCK</sub>   | 15  | _   | ns   | 2–5   |

| Input setup to USB clock—all inputs    | t <sub>USIVKH</sub> | 4   | —   | ns   | 2–5   |

| Input hold to USB clock—all inputs     | t <sub>USIXKH</sub> | 1   | —   | ns   | 2–5   |

| USB clock to output valid—all outputs  | t <sub>USKHOV</sub> | —   | 7   | ns   | 2–5   |

| Output hold from USB clock—all outputs | t <sub>USKHOX</sub> | 2   | _   | ns   | 2–5   |

Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>USIXKH</sub> symbolizes USB timing (US) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes USB timing (US) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to USB clock.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of the USB clock to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

# 10 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8347E.

# **10.1** Local Bus DC Electrical Characteristics

Table 33 provides the DC electrical characteristics for the local bus interface.

### Table 33. Local Bus DC Electrical Characteristics

| Parameter                                          | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                           | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current                                      | I <sub>IN</sub> | —                      | ±5                     | μΑ   |

| High-level output voltage, $I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | —                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$   | V <sub>OL</sub> | —                      | 0.2                    | V    |

### **10.2 Local Bus AC Electrical Specification**

Table 34 and Table 35 describe the general timing parameters of the local bus interface of the MPC8347E.

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 7.5 |     | ns   | 2     |

| Input setup to local bus clock (except LUPWAIT)             | t <sub>LBIVKH1</sub> | 1.5 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                      | t <sub>LBIVKH2</sub> | 2.2 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)            | t <sub>LBIXKH1</sub> | 1.0 | —   | ns   | 3, 4  |

| LUPWAIT Input hold from local bus clock                     | t <sub>LBIXKH2</sub> | 1.0 | —   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3   | —   | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 | —   | ns   | 7     |

| Local bus clock to LALE rise                                | t <sub>LBKHLR</sub>  | —   | 4.5 | ns   |       |

| Local bus clock to output valid (except LAD/LDP and LALE)   | t <sub>LBKHOV1</sub> | —   | 4.5 | ns   |       |

| Local bus clock to data valid for LAD/LDP                   | t <sub>LBKHOV2</sub> | —   | 4.5 | ns   | 3     |

| Local bus clock to address valid for LAD                    | t <sub>LBKHOV3</sub> | —   | 4.5 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)  | t <sub>LBKHOX1</sub> | 1   | —   | ns   | 3     |

Table 34. Local Bus General Timing Parameters—DLL On

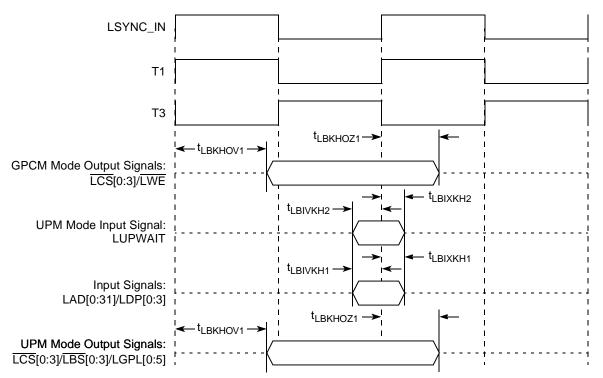

Figure 22. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Enabled)

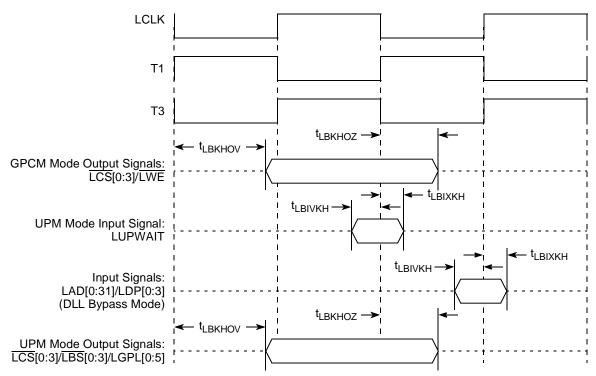

Figure 23. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Bypass Mode)

13 PCI

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8347E.

## **13.1 PCI DC Electrical Characteristics**

Table 40 provides the DC electrical characteristics for the PCI interface of the MPC8347E.

| Parameter                 | Symbol          | Test Condition                                       | Min                    | Мах                    | Unit |

|---------------------------|-----------------|------------------------------------------------------|------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                        | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)                           | -0.3                   | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}^{1} = 0 V \text{ or } V_{IN} = OV_{DD}$      | _                      | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | OV <sub>DD</sub> = min,<br>I <sub>OH</sub> = -100 μA | OV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | OV <sub>DD</sub> = min,<br>I <sub>OL</sub> = 100 μA  | _                      | 0.2                    | V    |

Table 40. PCI DC Electrical Characteristics

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1.

# 13.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus of the MPC8347E. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the MPC8347E is configured as a host or agent device. Table 41 provides the PCI AC timing specifications at 66 MHz.

| Table 41. PCI A | C Timing | <b>Specifications</b> | at 66 MHz <sup>1</sup> |

|-----------------|----------|-----------------------|------------------------|

|-----------------|----------|-----------------------|------------------------|

| Parameter                      | Symbol <sup>2</sup> | Min | Мах | Unit | Notes |

|--------------------------------|---------------------|-----|-----|------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | _   | 6.0 | ns   | 3     |

| Output hold from clock         | t <sub>PCKHOX</sub> | 1   | —   | ns   | 3     |

| Clock to output high impedance | t <sub>PCKHOZ</sub> |     | 14  | ns   | 3, 4  |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 |     | ns   | 3, 5  |

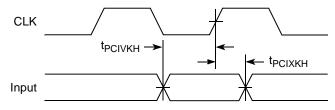

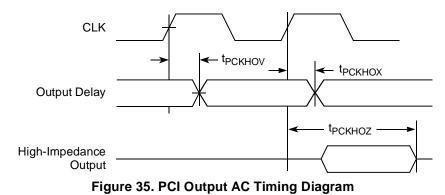

Figure 34 shows the PCI input AC timing diagram.

Figure 34. PCI Input AC Timing Diagram

Figure 35 shows the PCI output AC timing diagram.

MPC8347E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 11

Timers

# 14 Timers

This section describes the DC and AC electrical specifications for the timers.

# 14.1 Timer DC Electrical Characteristics

Table 43 provides the DC electrical characteristics for the MPC8347E timer pins, including TIN,  $\overline{\text{TOUT}}$ ,  $\overline{\text{TGATE}}$ , and RTC\_CLK.

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                           | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                           | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                           |      | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

Table 43. Timer DC Electrical Characteristics

# 14.2 Timer AC Timing Specifications

Table 44 provides the timer input and output AC timing specifications.

### Table 44. Timers Input AC Timing Specifications<sup>1</sup>

| Characteristic                    | Symbol <sup>2</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

#### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by external synchronous logic. Timer inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation.

#### IPIC

# 16 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins.

# **16.1 IPIC DC Electrical Characteristics**

Table 47 provides the DC electrical characteristics for the external interrupt pins.

| Table 47. IPIC DC Electrical Char | acteristics <sup>1</sup> |

|-----------------------------------|--------------------------|

|-----------------------------------|--------------------------|

| Characteristic     | Symbol          | Condition                | Min  | Max                    | Unit | Notes |

|--------------------|-----------------|--------------------------|------|------------------------|------|-------|

| Input high voltage | V <sub>IH</sub> |                          | 2.0  | OV <sub>DD</sub> + 0.3 | V    |       |

| Input low voltage  | V <sub>IL</sub> |                          | -0.3 | 0.8                    | V    |       |

| Input current      | I <sub>IN</sub> |                          |      | ±5                     | μA   |       |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | _    | 0.5                    | V    | 2     |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | _    | 0.4                    | V    | 2     |

#### Notes:

1. This table applies for pins IRQ[0:7], IRQ\_OUT, and MCP\_OUT.

2.  $\overline{\text{IRQ}_\text{OUT}}$  and  $\overline{\text{MCP}_\text{OUT}}$  are open-drain pins; thus  $\text{V}_\text{OH}$  is not relevant for those pins.

# 16.2 IPIC AC Timing Specifications

Table 48 provides the IPIC input and output AC timing specifications.

### Table 48. IPIC Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PICWID</sub> | 20  | ns   |

#### Notes:

1. Input specifications are measured at the 50 percent level of the IPIC input signals. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by external synchronous logic. IPIC inputs must be valid for at least t<sub>PICWID</sub> ns to ensure proper operation in edge triggered mode. SPI

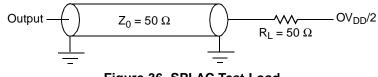

Figure 36 provides the AC test load for the SPI.

Figure 36. SPI AC Test Load

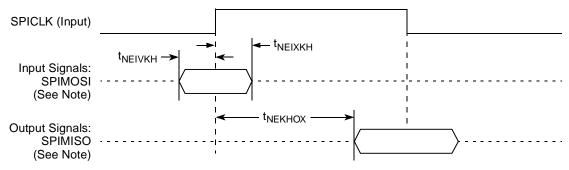

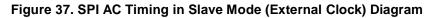

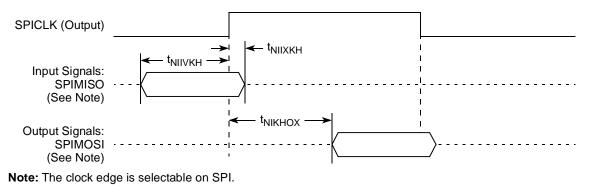

Figure 37 and Figure 38 represent the AC timings from Table 50. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 37 shows the SPI timings in slave mode (external clock).

Note: The clock edge is selectable on SPI.

Figure 38 shows the SPI timings in master mode (internal clock).

Figure 38. SPI AC Timing in Master Mode (Internal Clock) Diagram

# 18.5 Pinout Listings

Table 51 provides the pinout listing for the MPC8347E, 672 TBGA package.

### Table 51. MPC8347E (TBGA) Pinout Listing

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

|                        | PCI                                                                                                                                                                                                                                                                                                                    |          | 1                |       |

| PCI_INTA/IRQ_OUT       | B34                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> | 2     |

| PCI_RESET_OUT          | C33                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> |       |

| PCI_AD[31:0]           | G30, G32, G34, H31, H32, H33, H34,<br>J29, J32, J33, L30, K31, K33, K34,<br>L33, L34, P34, R29, R30, R33, R34,<br>T31, T32, T33, U31, U34, V31, V32,<br>V33, V34, W33, W34                                                                                                                                             | I/O      | OV <sub>DD</sub> |       |

| PCI_C/BE[3:0]          | J30, M31, P33, T34                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> |       |

| PCI_PAR                | P32                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |       |

| PCI_FRAME              | M32                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |

| PCI_TRDY               | N29                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |

| PCI_IRDY               | M34                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |

| PCI_STOP               | N31                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |

| PCI_DEVSEL             | N30                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |

| PCI_IDSEL              | J31                                                                                                                                                                                                                                                                                                                    | Ι        | OV <sub>DD</sub> |       |

| PCI_SERR               | N34                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |

| PCI_PERR               | N33                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |

| PCI_REQ[0]             | D32                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |       |

| PCI_REQ[1]/CPCI1_HS_ES | D34                                                                                                                                                                                                                                                                                                                    | I        | OV <sub>DD</sub> |       |

| PCI_REQ[2:4]           | E34, F32, G29                                                                                                                                                                                                                                                                                                          | Ι        | OV <sub>DD</sub> |       |

| PCI_GNT0               | C34                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |       |

| PCI_GNT1/CPCI1_HS_LED  | D33                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> |       |

| PCI_GNT2/CPCI1_HS_ENUM | E33                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> |       |

| PCI_GNT[3:4]           | F31, F33                                                                                                                                                                                                                                                                                                               | 0        | OV <sub>DD</sub> |       |

| M66EN                  | A19                                                                                                                                                                                                                                                                                                                    | Ι        | OV <sub>DD</sub> |       |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                             |          | 1                |       |

| MDQ[0:63]              | D5, A3, C3, D3, C4, B3, C2, D4, D2,<br>E5, G2, H6, E4, F3, G4, G3, H1, J2,<br>L6, M6, H2, K6, L2, M4, N2, P4, R2,<br>T4, P6, P3, R1, T2, AB5, AA3, AD6,<br>AE4, AB4, AC2, AD3, AE6, AE3, AG4,<br>AK5, AK4, AE2, AG6, AK3, AK2, AL2,<br>AL1, AM5, AP5, AM2, AN1, AP4, AN5,<br>AJ7, AN7, AM8, AJ9, AP6, AL7, AL9,<br>AN8 | I/O      | GV <sub>DD</sub> |       |

| Signal                        | Package Pin Number                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| MECC[0:4]/MSRCID[0:4]         | W4, W3, Y3, AA6, T1                                                                                                                                                                                              | I/O      | GV <sub>DD</sub> |       |

| MECC[5]/MDVAL                 | U1                                                                                                                                                                                                               | I/O      | GV <sub>DD</sub> |       |

| MECC[6:7]                     | Y1, Y6                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> |       |

| MDM[0:8]                      | B1, F1, K1, R4, AD4, AJ1, AP3, AP7,<br>Y4                                                                                                                                                                        | 0        | GV <sub>DD</sub> |       |

| MDQS[0:8]                     | B2, F5, J1, P2, AC1, AJ2, AN4, AL8, W2                                                                                                                                                                           | I/O      | GV <sub>DD</sub> |       |

| MBA[0:1]                      | AD1, AA5                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| MA[0:14]                      | W1, U4, T3, R3, P1, M1, N1, L3, L1,<br>K2, Y2, K3, J3, AP2, AN6                                                                                                                                                  | 0        | GV <sub>DD</sub> |       |

| MWE                           | AF1                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| MRAS                          | AF4                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| MCAS                          | AG3                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> |       |

| MCS[0:3]                      | AG2, AG1, AK1, AL4                                                                                                                                                                                               | 0        | GV <sub>DD</sub> |       |

| MCKE[0:1]                     | H3, G1                                                                                                                                                                                                           | 0        | GV <sub>DD</sub> | 3     |

| MCK[0:5]                      | U2, F4, AM3, V3, F2, AN3                                                                                                                                                                                         |          | GV <sub>DD</sub> |       |

| MCK[0:5]                      | U3, E3, AN2, V4, E1, AM4                                                                                                                                                                                         | 0        | GV <sub>DD</sub> |       |

| (T)                           | Pins Reserved for Future DDR2<br>ney should be left unconnected for MPC834                                                                                                                                       | 7)       | ·                |       |

| MODT[0:3]                     | AH3, AJ5, AH1, AJ4                                                                                                                                                                                               | _        | _                |       |

| MBA[2]                        | H4                                                                                                                                                                                                               | _        | —                |       |

| SPARE1                        | AA1                                                                                                                                                                                                              | —        | —                | 8     |

| SPARE2                        | AB1                                                                                                                                                                                                              | —        | —                | 6     |

|                               | Local Bus Controller Interface                                                                                                                                                                                   |          |                  | 1     |

| LAD[0:31]                     | AM13, AP13, AL14, AM14, AN14,<br>AP14, AK15, AJ15, AM15, AN15,<br>AP15, AM16, AL16, AN16, AP16,<br>AL17, AM17, AP17, AK17, AP18,<br>AL18, AM18, AN18, AP19, AN19,<br>AM19, AP20, AK19, AN20, AL20,<br>AP21, AN21 | I/O      | OV <sub>DD</sub> |       |

| LDP[0]/CKSTOP_OUT             | AM21                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> |       |

| LDP[1]/CKSTOP_IN              | AP22                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> |       |

| LDP[2]                        | AN22 I/O O                                                                                                                                                                                                       |          | OV <sub>DD</sub> |       |

| LDP[3]                        | AM22 I/O O                                                                                                                                                                                                       |          | OV <sub>DD</sub> |       |

| LA[27:31]                     | AK21, AP23, AN23, AP24, AK22                                                                                                                                                                                     | 0        | OV <sub>DD</sub> |       |

| LCS[0:3]                      | AN24, AL23, AP25, AN25                                                                                                                                                                                           | 0        | OV <sub>DD</sub> |       |

| LWE[0:3]/LSDDQM[0:3]/LBS[0:3] | AK23, AP26, AL24, AM25                                                                                                                                                                                           | 0        | OV <sub>DD</sub> |       |

### Table 51. MPC8347E (TBGA) Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                      | Pin Type                                                         | Power<br>Supply             | Notes |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|-------|

| LV <sub>DD</sub> 2 | C6, D9                                                                                                                                                                                                                                                  | Power for<br>three-speed<br>Ethernet #2<br>I/O (2.5 V,<br>3.3 V) | LV <sub>DD</sub> 2          |       |

| V <sub>DD</sub>    | E19, E29, F7, F9, F11,F13, F15, F17,<br>F18, F21, F23, F25, F29, H29, J6,<br>K29, M29, N6, P29, T29, U30, V6,<br>V29, W29, AB29, AC5, AD29, AF6,<br>AF29, AH29, AJ8, AJ12, AJ14, AJ16,<br>AJ18, AJ20, AJ21, AJ23, AJ25, AJ26,<br>AJ27, AJ28, AJ29, AK10 | Power for core<br>(1.2 V)                                        | V <sub>DD</sub>             |       |

| OV <sub>DD</sub>   | B22, B28, C16, C17, C24, C26, D13,<br>D15, D19, D29, E31, F28, G33, H30,<br>L29, L32, N32, P31, R31, U32, W31,<br>Y29, AA29, AC30, AE31, AF30, AG29,<br>AJ17, AJ30, AK11, AL15, AL19, AL21,<br>AL29, AL30, AM20, AM23, AM24,<br>AM26, AM28, AN11, AN13  | PCI, 10/100<br>Ethernet, and<br>other standard<br>(3.3 V)        | OV <sub>DD</sub>            |       |

| MVREF1             | M3                                                                                                                                                                                                                                                      | I                                                                | DDR<br>reference<br>voltage |       |

| MVREF2             | AD2                                                                                                                                                                                                                                                     | I                                                                | DDR<br>reference<br>voltage |       |

### Table 51. MPC8347E (TBGA) Pinout Listing (continued)

### Table 52. MPC8347E (PBGA) Pinout Listing (continued)

| Signal                                 | Package Pin Number                   | Pin Type | Power<br>Supply   | Notes    |

|----------------------------------------|--------------------------------------|----------|-------------------|----------|

| TSEC1_TXD[7:4]/GPIO2[27:30]            | N28, P25, P26, P27                   | I/O      | OV <sub>DD</sub>  |          |

| TSEC1_TXD[3:0]                         | V28, V27, V26, W28                   | 0        | LV <sub>DD1</sub> | 10       |

| TSEC1_TX_EN                            | W27                                  | 0        | LV <sub>DD1</sub> |          |

| TSEC1_TX_ER/GPIO2[31]                  | N24                                  | I/O      | OV <sub>DD</sub>  |          |

| Three-Spec                             | ed Ethernet Controller (Gigabit Ethe | ernet 2) | 1                 | 1        |

| TSEC2_COL/GPIO1[21]                    | P28                                  | I/O      | OV <sub>DD</sub>  |          |

| TSEC2_CRS/GPIO1[22]                    | AC28                                 | I/O      | LV <sub>DD2</sub> |          |

| TSEC2_GTX_CLK                          | AC27                                 | 0        | LV <sub>DD2</sub> |          |

| TSEC2_RX_CLK                           | AB25                                 | I        | LV <sub>DD2</sub> |          |

| TSEC2_RX_DV/GPIO1[23]                  | AC26                                 | I/O      | LV <sub>DD2</sub> |          |

| TSEC2_RXD[7:4]/GPIO1[26:29]            | R28, T24, T25, T26                   | I/O      | OV <sub>DD</sub>  |          |

| TSEC2_RXD[3:0]/GPIO1[13:16]            | AA25, AA26, AA27, AA28               | I/O      | LV <sub>DD2</sub> |          |

| TSEC2_RX_ER/GPIO1[25]                  | R25                                  | I/O      | OV <sub>DD</sub>  |          |

| TSEC2_TXD[7]/GPIO1[31]                 | T27                                  | I/O      | OV <sub>DD</sub>  |          |

| TSEC2_TXD[6]/DR_XCVR_TERM_SEL          | T28                                  | 0        | OV <sub>DD</sub>  |          |

| TSEC2_TXD[5]/DR_UTMI_OPMODE1           | U28                                  | 0        | OV <sub>DD</sub>  |          |

| TSEC2_TXD[4]/DR_UTMI_OPMODE0           | U27                                  | 0        | OV <sub>DD</sub>  |          |

| TSEC2_TXD[3:0]/GPIO1[17:20]            | AB26, AB27, AA24, AB28               | I/O      | LV <sub>DD2</sub> |          |

| TSEC2_TX_ER/GPIO1[24]                  | R27                                  | I/O      | OV <sub>DD</sub>  |          |

| TSEC2_TX_EN/GPIO1[12]                  | AD28                                 | I/O      | LV <sub>DD2</sub> | 3        |

| TSEC2_TX_CLK/GPIO1[30]                 | R26                                  | I/O      | OV <sub>DD</sub>  |          |

|                                        | DUART                                |          | 1                 | 4        |

| UART_SOUT[1:2]/MSRCID[0:1]/LSRCID[0:1] | B4, A4                               | 0        | OV <sub>DD</sub>  |          |

| UART_SIN[1:2]/MSRCID[2:3]/LSRCID[2:3]  | D5, C5                               | I/O      | OV <sub>DD</sub>  |          |

| UART_CTS[1]/MSRCID4/LSRCID4            | B5                                   | I/O      | OV <sub>DD</sub>  |          |

| UART_CTS[2]/MDVAL/LDVAL                | A5                                   | I/O      | OV <sub>DD</sub>  |          |

| UART_RTS[1:2]                          | D6, C6                               | 0        | OV <sub>DD</sub>  |          |

|                                        | I <sup>2</sup> C interface           |          | 1                 | 4        |

| IIC1_SDA                               | E5                                   | I/O      | OV <sub>DD</sub>  | 2        |

| IIC1_SCL                               | A6                                   | I/O      | OV <sub>DD</sub>  | 2        |

| IIC2_SDA                               | В6                                   | I/O      | OV <sub>DD</sub>  | 2        |

| IIC2_SCL                               | E7                                   | I/O      | OV <sub>DD</sub>  | 2        |

|                                        | SPI                                  | ·        | •                 | <u> </u> |

| SPIMOSI                                | D7                                   | I/O      | OV <sub>DD</sub>  |          |

### Table 52. MPC8347E (PBGA) Pinout Listing (continued)

| Signal | Package Pin Number | Pin Type | Power<br>Supply             | Notes |

|--------|--------------------|----------|-----------------------------|-------|

| MVREF1 | AF19               | I        | DDR<br>reference<br>voltage |       |

| MVREF2 | AE10               | I        | DDR<br>reference<br>voltage |       |

|        | No Connection      |          |                             |       |

| NC     | V1, V2, V5         |          |                             |       |

#### Notes:

- 1. This pin is an open-drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 2. This pin is an open-drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 3. During reset, this output is actively driven rather than three-stated.

- 4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 5. This pin should have a weak pull-up if the chip is in PCI host mode. Follow the PCI specifications.

- 6. This pin must always be tied to GND.

- 7. This pin must always be left not connected.

- 8. Thermal sensitive resistor.

- 9. It is recommended that MDIC0 be tied to GRD using an 18 Ω resistor and MDIC1 be tied to DDR power using an 18 Ω resistor.

- 10.TSEC1\_TXD[3] is required an external pull-up resistor. For proper functionality of the device, this pin must be pulled up or actively driven high during a hard reset. No external pull-down resistors are allowed to be attached to this net.

|                                        |      |                                                       | Inpu  | It Clock Fre        | quency (M | Hz) <sup>2</sup> |

|----------------------------------------|------|-------------------------------------------------------|-------|---------------------|-----------|------------------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock<br>Ratio <sup>2</sup> | 16.67 | 25                  | 33.33     | 66.67            |

|                                        |      | Ratio                                                 | C     | s <i>b_clk</i> Freq | uency (MH | z)               |

| Low                                    | 0010 | 2 : 1                                                 |       |                     |           | 133              |

| Low                                    | 0011 | 3 : 1                                                 |       |                     | 100       | 200              |

| Low                                    | 0100 | 4 : 1                                                 |       | 100                 | 133       | 266              |

| Low                                    | 0101 | 5 : 1                                                 |       | 125                 | 166       | 333              |

| Low                                    | 0110 | 6 : 1                                                 | 100   | 150                 | 200       |                  |

| Low                                    | 0111 | 7:1                                                   | 116   | 175                 | 233       |                  |

| Low                                    | 1000 | 8 : 1                                                 | 133   | 200                 | 266       |                  |

| Low                                    | 1001 | 9:1                                                   | 150   | 225                 | 300       |                  |

| Low                                    | 1010 | 10 : 1                                                | 166   | 250                 | 333       |                  |

| Low                                    | 1011 | 11 : 1                                                | 183   | 275                 |           | <u>-</u>         |

| Low                                    | 1100 | 12 : 1                                                | 200   | 300                 |           |                  |

| Low                                    | 1101 | 13 : 1                                                | 216   | 325                 |           |                  |

| Low                                    | 1110 | 14 : 1                                                | 233   |                     |           |                  |

| Low                                    | 1111 | 15 : 1                                                | 250   |                     |           |                  |

| Low                                    | 0000 | 16 : 1                                                | 266   |                     |           |                  |

| High                                   | 0010 | 4:1                                                   |       | 100                 | 133       | 266              |

| High                                   | 0011 | 6 : 1                                                 | 100   | 150                 | 200       |                  |

| High                                   | 0100 | 8 : 1                                                 | 133   | 200                 | 266       |                  |

| High                                   | 0101 | 10 : 1                                                | 166   | 250                 | 333       |                  |

| High                                   | 0110 | 12 : 1                                                | 200   | 300                 |           |                  |

| High                                   | 0111 | 14 : 1                                                | 233   |                     |           |                  |

| High                                   | 1000 | 16 : 1                                                | 266   |                     |           |                  |

Table 58. CSB Frequency Options for Agent Mode

<sup>1</sup> CFG\_CLKIN\_DIV doubles csb\_clk if set high.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode. DDR2 memory may be used at 133 MHz provided that the memory components are specified for operation at this frequency.

## 19.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). Table 59 shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in Table 59 should be considered as reserved.

#### Thermal

required in the heat sink. Minimize the size of the clearance to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

$$T_J = T_C + (R_{\theta JC} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_C$  = case temperature of the package (°C)  $R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)  $P_D$  = power dissipation (W)

# 22 Document Revision History

Table 66 provides a revision history of this document.

| Table 66. Docum | ent Revision History |

|-----------------|----------------------|

|-----------------|----------------------|

| Revision | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                             |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11       | 2/2009 | In Section 21.1, "System Clocking," removed "(AVDD1)" and "(AVDD2") from bulleted list.<br>In Section 21.2, "PLL Power Supply Filtering," in the second paragraph, changed "provide five independent filter circuits," and "the five AVDD pins" to provide four independent filter circuits," and "the four AVDD pins."                                                                           |

|          |        | In Table 35, removed row for rise time (tl2CR). Removed minimum value of tl2CF. Added note 5 stating that the device does not follow the I2C-BUS Specifications version 2.1 regarding the tl2CF AC                                                                                                                                                                                                |

|          |        | parameter.<br>In Table 54, corrected the max csb_clk to 266 MHz.                                                                                                                                                                                                                                                                                                                                  |

|          |        | In Table 60, added PLL configurations 903, 923, A03, A23, and 503 for 533 MHz                                                                                                                                                                                                                                                                                                                     |

|          |        | In Table 35, corrected $t_{LBKHOV}$ parametr to $t_{LBKLOV}$ (output data is driven on falling edge of clock in DLL bypass mode). Similarly, made the same correction to Figure 21, Figure 23, and Figure 24 for output signals.                                                                                                                                                                  |

|          |        | Added Figure 1 and Figure 4.                                                                                                                                                                                                                                                                                                                                                                      |

|          |        | In Table 9.2, clarified that AC table is for ULPI only.                                                                                                                                                                                                                                                                                                                                           |

|          |        | Added footnote 4 to Table 67.                                                                                                                                                                                                                                                                                                                                                                     |

|          |        | In Table 67, updated note 1 to say the following: "For temperature range = C, processor frequency is up to 667(TBGA) with a platform frequency of 333 and limited to 400 (PBGA) with a platform frequency of 266."                                                                                                                                                                                |

|          |        | Added footnote 10 and 11 to Table 51 and Table 52.                                                                                                                                                                                                                                                                                                                                                |

|          |        | In Table 51, Table 52, updated note 11 to say the following: "SEC1_TXD[3] is required an external pull-up resistor. For proper functionality of the device, this pin must be pulled up or actively driven high during a hard reset. No external pull-down resistors are allowed to be attached to this net."                                                                                      |

|          |        | Added footnote 6 to Table 7.                                                                                                                                                                                                                                                                                                                                                                      |

|          |        | In Table 7, updated the note 6 to say the following: "The Spread spectrum clocking. Is allowed with 1% input frequency down-spread at maximum 50KHz modulation rate regardless of input frequency."                                                                                                                                                                                               |

|          |        | In 8.1.1, removed the note "The potential applied to the input of a GMII, MII, TBI, RGMII, or RTBI receiver may exceed the potential of the receiver power supply (that is, a RGMII driver powered from a 3.6 V supply driving VOH into a RGMII receiver powered from a 2.5-V supply). Tolerance for dissimilar RGMII driver and receiver supply potentials is implicit in these specifications." |

| 10       | 4/2007 | In Table 3, "Output Drive Capability," changed the values in the Output Impedance column and added USB to the seventh row.                                                                                                                                                                                                                                                                        |

|          |        | In Table 54, "Operating Frequencies for TBGA," added column for 400 MHz.<br>In Section 21.7, "Pull-Up Resistor Requirements," deleted last two paragraphs and after first<br>paragraph, added a new paragraph.<br>Deleted Section 21.8, "JTAG Configuration Signals," and Figure 43, "JTAG Interface Connection."                                                                                 |

| 9        | 3/2007 | In Table 54, "Operating Frequencies for TBGA," in the 'Coherent system bus frequency ( <i>csb_clk</i> )' row, changed the value in the 533 MHz column to 100–333.                                                                                                                                                                                                                                 |

|          |        | In Table 60, "Suggested PLL Configurations," under the subhead, '33 MHz CLKIN/PCI_CLK Options,' added row A03 between Ref. No. 724 and 804. Under the subhead '66 MHz CLKIN/PCI_CLK Options,' added row 503 between Ref. No. 305 and 404. For Ref. No. 306, changed the CORE PLL value to 0000110.                                                                                                |

|          |        | In Section 23, "Ordering Information," replaced first paragraph and added a note.<br>In Section 23.1, "Part Numbers Fully Addressed by This Document," replaced first paragraph.                                                                                                                                                                                                                  |

**Ordering Information**

### THIS PAGE INTENTIONALLY LEFT BLANK