#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XEI

| 2000                            |                                                              |

|---------------------------------|--------------------------------------------------------------|

| Product Status                  | Active                                                       |

| Core Processor                  | PowerPC e300                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 533MHz                                                       |

| Co-Processors/DSP               | Security; SEC                                                |

| RAM Controllers                 | DDR                                                          |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (2)                                          |

| SATA                            | -                                                            |

| USB                             | USB 2.0 + PHY (2)                                            |

| Voltage - I/O                   | 2.5V, 3.3V                                                   |

| Operating Temperature           | -40°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                        |

| Package / Case                  | 672-LBGA                                                     |

| Supplier Device Package         | 672-TBGA (35x35)                                             |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8347eczuajdb |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

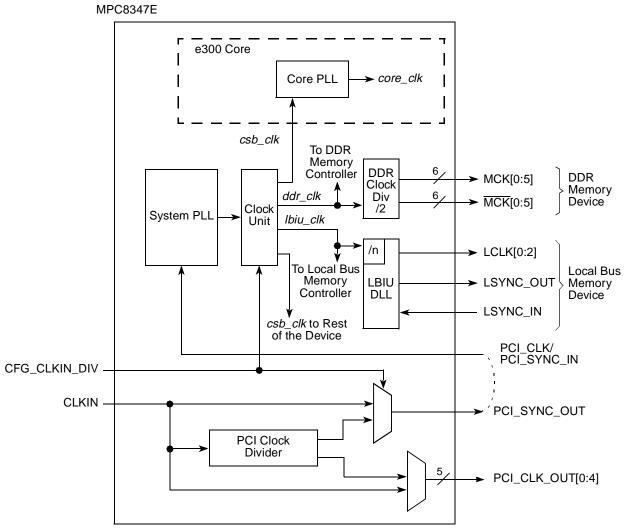

# 1 Overview

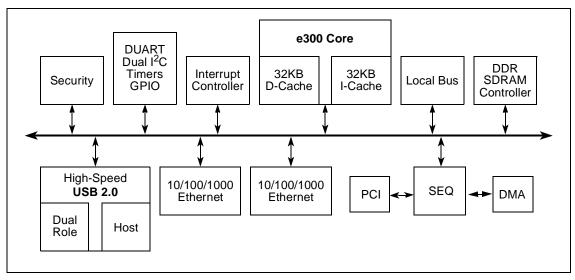

This section provides a high-level overview of the MPC8347E features. Figure 1 shows the major functional units within the MPC8347E.

### Figure 1. MPC8347E Block Diagram

Major features of the MPC8347E are as follows:

- Embedded PowerPC e300 processor core; operates at up to 667 MHz

- High-performance, superscalar processor core

- Floating-point, integer, load/store, system register, and branch processing units

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the other Freescale processor families that implement Power Architecture technology

- Double data rate, DDR SDRAM memory controller

- Programmable timing for DDR-1 SDRAM

- 32- or 64-bit data interface, up to 333-MHz data rate for TBGA, 266 MHz for PBGA

- Four banks of memory, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbit to 1 Gbit with x8/x16 data ports

- Full error checking and correction (ECC) support

- Page mode support (up to 16 simultaneous open pages)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep mode for self-refresh SDRAM

- Auto refresh

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8347E. The MPC8347E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

|                                                                                                                                     | Characteristic              | Symbol                        | Max Value                        | Unit | Notes |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|----------------------------------|------|-------|--|--|--|--|

| Core supply voltage                                                                                                                 |                             | V <sub>DD</sub> -0.3 to 1.32  |                                  | V    |       |  |  |  |  |

| PLL supply voltage                                                                                                                  |                             | AV <sub>DD</sub>              | / <sub>DD</sub> –0.3 to 1.32     |      |       |  |  |  |  |

| DDR DRAM I/O voltag                                                                                                                 | e                           | GV <sub>DD</sub> -0.3 to 3.63 |                                  | V    |       |  |  |  |  |

| Three-speed Ethernet                                                                                                                | I/O, MII management voltage | LV <sub>DD</sub>              | -0.3 to 3.63                     | V    |       |  |  |  |  |

| PCI, local bus, DUART, system control and power management, I <sup>2</sup> C, and JTAG I/O voltage                                  |                             | OV <sub>DD</sub>              | -0.3 to 3.63                     | V    |       |  |  |  |  |

| Input voltage                                                                                                                       | DDR DRAM signals            | MV <sub>IN</sub>              | –0.3 to (GV <sub>DD</sub> + 0.3) | V    | 2, 5  |  |  |  |  |

|                                                                                                                                     | DDR DRAM reference          | MV <sub>REF</sub>             | –0.3 to (GV <sub>DD</sub> + 0.3) | V    | 2, 5  |  |  |  |  |

| Three-speed Ethernet signals<br>Local bus, DUART, CLKIN, system control and<br>power management, I <sup>2</sup> C, and JTAG signals |                             | LV <sub>IN</sub>              | -0.3 to (LV <sub>DD</sub> + 0.3) | V    | 4, 5  |  |  |  |  |

|                                                                                                                                     |                             | OV <sub>IN</sub>              | –0.3 to (OV <sub>DD</sub> + 0.3) | V    | 3, 5  |  |  |  |  |

|                                                                                                                                     | PCI                         | OV <sub>IN</sub>              | -0.3 to (OV <sub>DD</sub> + 0.3) | V    | 6     |  |  |  |  |

| Storage temperature ra                                                                                                              | ange                        | T <sub>STG</sub>              | –55 to 150                       | °C   |       |  |  |  |  |

## Table 1. Absolute Maximum Ratings<sup>1</sup>

Notes:

- <sup>1</sup> Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- <sup>2</sup> Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- <sup>3</sup> Caution: OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- <sup>4</sup> Caution: LV<sub>IN</sub> must not exceed LV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

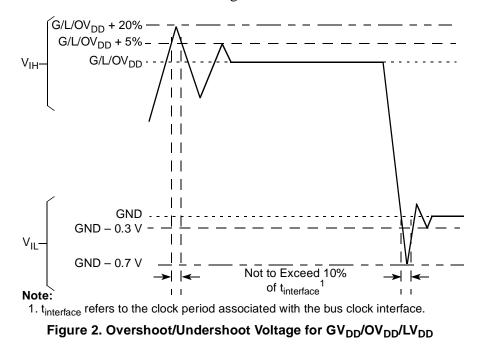

- <sup>5</sup> (M,L,O)V<sub>IN</sub> and MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

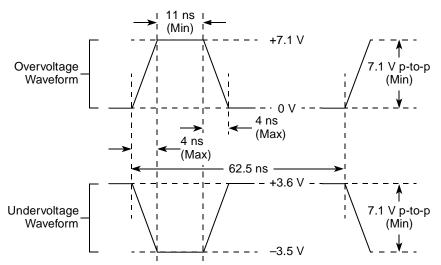

- <sup>6</sup> OV<sub>IN</sub> on the PCI interface can overshoot/undershoot according to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 3.

## 2.1.2 Power Supply Voltage Specification

Table 2 provides the recommended operating conditions for the MPC8347E. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

| Characteristic                                                                                     | Symbol            | Recommended<br>Value             | Unit | Notes |

|----------------------------------------------------------------------------------------------------|-------------------|----------------------------------|------|-------|

| Core supply voltage                                                                                | V <sub>DD</sub>   | 1.2 V ± 60 mV                    | V    | 1     |

| PLL supply voltage                                                                                 | AV <sub>DD</sub>  | 1.2 V ± 60 mV                    | V    | 1     |

| DDR DRAM I/O supply voltage                                                                        | GV <sub>DD</sub>  | 2.5 V ± 125 mV                   | V    |       |

| Three-speed Ethernet I/O supply voltage                                                            | LV <sub>DD1</sub> | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    |       |

| Three-speed Ethernet I/O supply voltage                                                            | LV <sub>DD2</sub> | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    |       |

| PCI, local bus, DUART, system control and power management, I <sup>2</sup> C, and JTAG I/O voltage | OV <sub>DD</sub>  | 3.3 V ± 330 mV                   | V    |       |

#### Note:

<sup>1</sup> GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8347E.

Figure 3 shows the undershoot and overshoot voltage of the PCI interface of the MPC8347E for the 3.3-V signals, respectively.

Figure 3. Maximum AC Waveforms on PCI Interface for 3.3-V Signaling

## 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                        | Output Impedance<br>(Ω) | Supply<br>Voltage                                         |

|----------------------------------------------------|-------------------------|-----------------------------------------------------------|

| Local bus interface utilities signals              | 40                      | OV <sub>DD</sub> = 3.3 V                                  |

| PCI signals (not including PCI output clocks)      | 25                      |                                                           |

| PCI output clocks (including PCI_SYNC_OUT)         | 40                      |                                                           |

| DDR signal                                         | 18                      | GV <sub>DD</sub> = 2.5 V                                  |

| TSEC/10/100 signals                                | 40                      | LV <sub>DD</sub> = 2.5/3.3 V                              |

| DUART, system control, I <sup>2</sup> C, JTAG, USB | 40                      | OV <sub>DD</sub> = 3.3 V                                  |

| GPIO signals                                       | 40                      | OV <sub>DD</sub> = 3.3 V,<br>LV <sub>DD</sub> = 2.5/3.3 V |

Table 3. Output Drive Capability

## 2.2 Power Sequencing

MPC8347E does not require the core supply voltage and I/O supply voltages to be applied in any particular order. Note that during the power ramp up, before the power supplies are stable, there may be a period of time that I/O pins are actively driven. After the power is stable, as long as **PORESET** is asserted, most I/O pins are three-stated. To minimize the time that I/O pins are actively driven, it is recommended to apply core voltage before I/O voltage and assert **PORESET** before the power supplies fully ramp up.

# 8 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speeds (10/100/1000 Mbps) and MII management.

# 8.1 Three-Speed Ethernet Controller (TSEC)— GMII/MII/TBI/RGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to the gigabit media independent interface (GMII), the media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), and reduced ten-bit interface (RTBI) signals except management data input/output (MDIO) and management data clock (MDC). The MII, GMII, and TBI interfaces are defined for 3.3 V, and the RGMII and RTBI interfaces are defined for 2.5 V. The RGMII and RTBI interfaces follow the Hewlett-Packard *Reduced Pin-Count Interface for Gigabit Ethernet Physical Layer Device Specification*, Version 1.2a (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

# 8.1.1 **TSEC DC Electrical Characteristics**

GMII, MII, TBI, RGMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 19 and Table 20. The RGMII and RTBI signals in Table 20 are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter            | Symbol                        | Conditions                                |                        | Min  | Мах                    | Unit |

|----------------------|-------------------------------|-------------------------------------------|------------------------|------|------------------------|------|

| Supply voltage 3.3 V | LV <sub>DD</sub> <sup>2</sup> | —                                         |                        | 2.97 | 3.63                   | V    |

| Output high voltage  | V <sub>OH</sub>               | I <sub>OH</sub> = -4.0 mA                 | LV <sub>DD</sub> = Min | 2.40 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>               | $I_{OL} = 4.0 \text{ mA}$ $LV_{DD} = Min$ |                        | GND  | 0.50                   | V    |

| Input high voltage   | V <sub>IH</sub>               |                                           |                        | 2.0  | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>               | —                                         | _                      | -0.3 | 0.90                   | V    |

| Input high current   | IIH                           | $V_{IN}^{1} = LV_{DD}$                    |                        | —    | 40                     | μΑ   |

| Input low current    | ۱ <sub>IL</sub>               | V <sub>IN</sub> <sup>1</sup> =            | GND                    | -600 | —                      | μΑ   |

Table 19. GMII/TBI and MII DC Electrical Characteristics

### Notes:

1. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

2. GMII/MII pins not needed for RGMII or RTBI operation are powered by the  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  supply.

| Parameters           | Symbol           | Conditions                                 |                        | Min       | Max                    | Unit |

|----------------------|------------------|--------------------------------------------|------------------------|-----------|------------------------|------|

| Supply voltage 2.5 V | LV <sub>DD</sub> | —                                          |                        | 2.37      | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | $I_{OH} = -1.0 \text{ mA}$ $LV_{DD} = Min$ |                        | 2.00      | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | $I_{OL} = 1.0 \text{ mA}$ $LV_{DD} = Min$  |                        | GND – 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | — LV <sub>DD</sub> = Min                   |                        | 1.7       | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                                          | LV <sub>DD</sub> = Min | -0.3      | 0.70                   | V    |

| Input high current   | I <sub>IH</sub>  | $V_{IN}^{1} = LV_{DD}$                     |                        | —         | 10                     | μA   |

| Input low current    | ۱ <sub>IL</sub>  | V <sub>IN</sub> <sup>1</sup> =             | GND                    | -15       | —                      | μΑ   |

### Table 20. RGMII/RTBI (When Operating at 2.5 V) DC Electrical Characteristics

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  symbol referenced in Table 1 and Table 2.

# 8.2 GMII, MII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

## 8.2.1 GMII Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

## 8.2.1.1 GMII Transmit AC Timing Specifications

Table 21 provides the GMII transmit AC timing specifications.

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                                     | Symbol <sup>1</sup>                   | Min   | Тур | Мах   | Unit |

|-------------------------------------------------------------------------|---------------------------------------|-------|-----|-------|------|

| GTX_CLK clock period                                                    | t <sub>GTX</sub>                      | _     | 8.0 | —     | ns   |

| GTX_CLK duty cycle                                                      | t <sub>GTXH</sub> /t <sub>GTX</sub>   | 43.75 |     | 56.25 | %    |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay                       | t <sub>GTKHDX</sub>                   | 0.5   |     | 5.0   | ns   |

| GTX_CLK clock rise time, V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>GTXR</sub>                     | _     |     | 1.0   | ns   |

| GTX_CLK clock fall time, V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>GTXF</sub>                     | _     |     | 1.0   | ns   |

| GTX_CLK125 clock period                                                 | t <sub>G125</sub> 2                   | _     | 8.0 | —     | ns   |

| GTX_CLK125 reference clock duty cycle measured at $LV_{DD}/2$           | t <sub>G125H</sub> /t <sub>G125</sub> | 45    |     | 55    | %    |

Notes:

1. The symbols for timing specifications follow the pattern t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. This symbol represents the external GTX\_CLK125 signal and does not follow the original symbol naming convention.

Table 21. GMII Transmit AC Timing Specifications

| Table 35. Local Bus General Timing Parameters—DLL Bypass <sup>9</sup> (continued) |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

| Parameter                                            | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|------------------------------------------------------|---------------------|-----|-----|------|-------|

| Local bus clock to output valid                      | t <sub>LBKLOV</sub> | _   | 3   | ns   | 3     |

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ</sub> | _   | 4   | ns   | 8     |

Notes:

- The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to the falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or the rising edge of LCLK0 (for all other inputs).

- 3. All signals are measured from  $OV_{DD}/2$  of the rising/falling edge of LCLK0 to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.

- 6. t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.the

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin equals to the load on the LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 9. DLL bypass mode is not recommended for use at frequencies above 66 MHz.

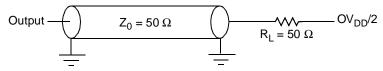

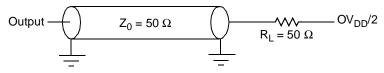

Figure 19 provides the AC test load for the local bus.

Figure 19. Local Bus C Test Load

#### Local Bus

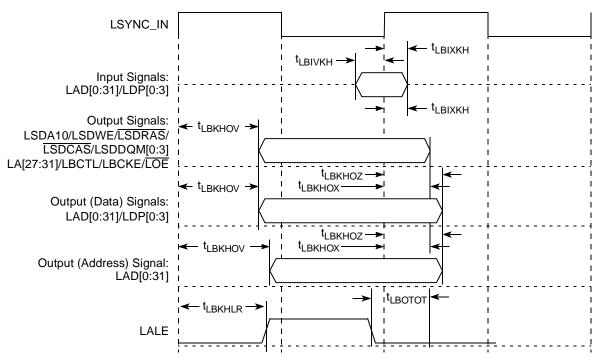

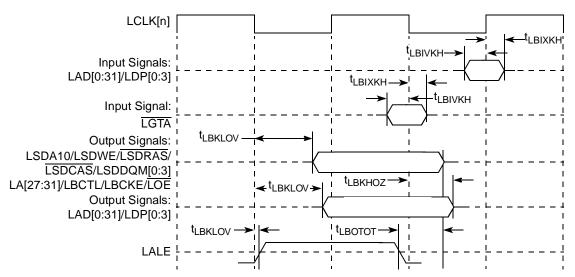

Figure 20 through Figure 25 show the local bus signals.

Figure 20. Local Bus Signals, Nonspecial Signals Only (DLL Enabled)

Figure 21. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

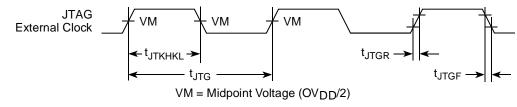

### Table 37. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup> (continued)

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Мах     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-------|

| Output hold times:<br>Boundary-scan data<br>TDO                            | <sup>t</sup> jtkldx<br><sup>t</sup> jtklox | 2<br>2 |         | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | <sup>t</sup> jtkldz<br><sup>t</sup> jtkloz | 2<br>2 | 19<br>9 | ns   | 5, 6  |

Notes:

- 1. All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50  $\Omega$  load (see Figure 26). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to  $t_{TCLK}$ .

- 6. Guaranteed by design and characterization.

Figure 26 provides the AC test load for TDO and the boundary-scan outputs of the MPC8347E.

Figure 26. AC Test Load for the JTAG Interface

Figure 27 provides the JTAG clock input timing diagram.

Figure 27. JTAG Clock Input Timing Diagram

Timers

# 14 Timers

This section describes the DC and AC electrical specifications for the timers.

# 14.1 Timer DC Electrical Characteristics

Table 43 provides the DC electrical characteristics for the MPC8347E timer pins, including TIN,  $\overline{\text{TOUT}}$ ,  $\overline{\text{TGATE}}$ , and RTC\_CLK.

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                           | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                           | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                           |      | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

Table 43. Timer DC Electrical Characteristics

# 14.2 Timer AC Timing Specifications

Table 44 provides the timer input and output AC timing specifications.

### Table 44. Timers Input AC Timing Specifications<sup>1</sup>

| Characteristic                    | Symbol <sup>2</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by external synchronous logic. Timer inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation.

# 15 GPIO

This section describes the DC and AC electrical specifications for the GPIO.

## **15.1 GPIO DC Electrical Characteristics**

Table 45 provides the DC electrical characteristics for the MPC8347E GPIO.

### **Table 45. GPIO DC Electrical Characteristics**

| Characteristic      | Symbol          | Condition                 | Min  | Max                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                           | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                           | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                           |      | ±5                     | μΑ   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _    | 0.4                    | V    |

## 15.2 GPIO AC Timing Specifications

Table 46 provides the GPIO input and output AC timing specifications.

### Table 46. GPIO Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by external synchronous logic. GPIO inputs must be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

| Signal                            | Package Pin Number         | Pin Type | Power<br>Supply  | Notes |

|-----------------------------------|----------------------------|----------|------------------|-------|

| LBCTL                             | AN26                       | 0        | OV <sub>DD</sub> |       |

| LALE                              | AK24                       | 0        | OV <sub>DD</sub> |       |

| LGPL0/LSDA10/cfg_reset_source0    | AP27                       | I/O      | OV <sub>DD</sub> |       |

| LGPL1/LSDWE/cfg_reset_source1     | AL25                       | I/O      | OV <sub>DD</sub> |       |

| LGPL2/LSDRAS/LOE                  | AJ24                       | 0        | OV <sub>DD</sub> |       |

| LGPL3/LSDCAS/cfg_reset_source2    | AN27                       | I/O      | OV <sub>DD</sub> |       |

| LGPL4/LGTA/LUPWAIT/LPBSE          | AP28                       | I/O      | OV <sub>DD</sub> |       |

| LGPL5/cfg_clkin_div               | AL26                       | I/O      | OV <sub>DD</sub> |       |

| LCKE                              | AM27                       | 0        | OV <sub>DD</sub> |       |

| LCLK[0:2]                         | AN28, AK26, AP29           | 0        | OV <sub>DD</sub> |       |

| LSYNC_OUT                         | AM12                       | 0        | OV <sub>DD</sub> |       |

| LSYNC_IN                          | AJ10                       | I        | OV <sub>DD</sub> |       |

|                                   | General Purpose I/O Timers | -        |                  | -     |

| GPIO1[0]/GTM1_TIN1/GTM2_TIN2      | F24                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[1]/GTM1_TGATE1/GTM2_TGATE2  | E24                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[2]/GTM1_TOUT1               | B25                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[3]/GTM1_TIN2/GTM2_TIN1      | D24                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[4]/GTM1_TGATE2/GTM2_TGATE1  | A25                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[5]/GTM1_TOUT2/GTM2_TOUT1    | B24                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[6]/GTM1_TIN3/GTM2_TIN4      | A24                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[7]/GTM1_TGATE3/GTM2_TGATE4  | D23                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[8]/GTM1_TOUT3               | B23                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[9]/GTM1_TIN4/GTM2_TIN3      | A23                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[10]/GTM1_TGATE4/GTM2_TGATE3 | F22                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[11]/GTM1_TOUT4/GTM2_TOUT3   | E22                        | I/O      | OV <sub>DD</sub> |       |

|                                   | USB Port 1                 |          |                  |       |

| MPH1_D0_ENABLEN/DR_D0_ENABLEN     | A26                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D1_SER_TXD/DR_D1_SER_TXD     | B26                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D2_VMO_SE0/DR_D2_VMO_SE0     | D25                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D3_SPEED/DR_D3_SPEED         | A27                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D4_DP/DR_D4_DP               | B27                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D5_DM/DR_D5_DM               | C27                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D6_SER_RCV/DR_D6_SER_RCV     | D26                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D7_DRVVBUS/DR_D7_DRVVBUS     | E26                        | I/O      | OV <sub>DD</sub> | T     |

## Table 51. MPC8347E (TBGA) Pinout Listing (continued)

| Signal | Package Pin Number                                                                                                                                                                                                                                                                                                                                          | Pin Type | Power<br>Supply | Notes |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|

|        | No Connection                                                                                                                                                                                                                                                                                                                                               |          |                 |       |

| NC     | W32, AA31, AA32, AA33, AA34,<br>AB31, AB32, AB33, AB34, AC29,<br>AC31, AC33, AC34, AD30, AD32,<br>AD33, AD34, AE29, AE30, AH32,<br>AH33, AH34, AM33, AJ31, AJ32,<br>AJ33, AJ34, AK32, AK33, AK34,<br>AM34, AL33, AL34, AK31, AH30,<br>AC32, AE32, AH31, AL32, AG34,<br>AE33, AF32, AE34, AF34, AF33,<br>AG33, AG32, AL11, AM11, AP10, Y32,<br>Y34, Y31, Y33 | _        | _               |       |

## Table 51. MPC8347E (TBGA) Pinout Listing (continued)

#### Notes:

- 1. This pin is an open-drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 2. This pin is an open-drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 3. During reset, this output is actively driven rather than three-stated.

- 4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 5. This pin should have a weak pull-up if the chip is in PCI host mode. Follow the PCI specifications.

- 6. This pin must always be tied to GND.

- 7. This pin must always be pulled up to  $OV_{DD}$ .

- 8. This pin must always be left not connected.

- 9. Thermal sensitive resistor.

- 10.It is recommended that MDIC0 be tied to GRD using an 18  $\Omega$  resistor and MDIC1 be tied to DDR power using an 18  $\Omega$  resistor.

- 11.TSEC1\_TXD[3] is required an external pull-up resistor. For proper functionality of the device, this pin must be pulled up or actively driven high during a hard reset. No external pull-down resistors are allowed to be attached to this net.

## Table 52 provides the pinout listing for the MPC8347E, 620 PBGA package.

### Table 52. MPC8347E (PBGA) Pinout Listing

| Signal            | Package Pin Number                                                                                                                                                 | Pin Type | Power<br>Supply  | Notes |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

|                   | PCI                                                                                                                                                                |          |                  |       |

| PCI1_INTA/IRQ_OUT | D20                                                                                                                                                                | 0        | OV <sub>DD</sub> | 2     |

| PCI1_RESET_OUT    | B21                                                                                                                                                                | 0        | OV <sub>DD</sub> |       |

| PCI1_AD[31:0]     | E19, D17, A16, A18, B17, B16, D16,<br>B18, E17, E16, A15, C16, D15, D14,<br>C14, A12, D12, B11, C11, E12, A10,<br>C10, A9, E11, E10, B9, B8, D9, A8,<br>C9, D8, C8 | I/O      | OV <sub>DD</sub> |       |

| PCI1_C/BE[3:0]    | A17, A14, A11, B10                                                                                                                                                 | I/O      | OV <sub>DD</sub> |       |

| PCI1_PAR          | D13                                                                                                                                                                | I/O      | OV <sub>DD</sub> |       |

| PCI1_FRAME        | B14                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI1_TRDY         | A13                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

## Table 52. MPC8347E (PBGA) Pinout Listing (continued)

| Signal                         | Package Pin Number                                                                                                                      | Pin Type | Power<br>Supply  | Notes |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| MCAS                           | AG6                                                                                                                                     | 0        | GV <sub>DD</sub> |       |

| MCS[0:3]                       | AE7, AH7, AH4, AF2                                                                                                                      | 0        | GV <sub>DD</sub> |       |

| MCKE[0:1]                      | AG23, AH23                                                                                                                              | 0        | GV <sub>DD</sub> | 3     |

| MCK[0:5]                       | AH15, AE24, AE2, AF14, AE23, AD3                                                                                                        | 0        | GV <sub>DD</sub> |       |

| MCK[0:5]                       | AG15, AD23, AE3, AG14, AF24, AD2                                                                                                        | 0        | GV <sub>DD</sub> |       |

| (The                           | Pins Reserved for Future DDR2<br>ey should be left unconnected for MPC834                                                               | 7)       |                  | 1     |

| MODT[0:3]                      | AG5, AD4, AH6, AF4                                                                                                                      | _        | _                |       |

| MBA[2]                         | AD22                                                                                                                                    |          |                  |       |

| SPARE1                         | AF12                                                                                                                                    | _        | _                | 7     |

| SPARE2                         | AG11                                                                                                                                    | _        | _                | 6     |

|                                | Local Bus Controller Interface                                                                                                          |          |                  |       |

| LAD[0:31]                      | T4, T5, T1, R2, R3, T2, R1, R4, P1, P2,<br>P3, P4, N1, N4, N2, N3, M1, M2, M3,<br>N5, M4, L1, L2, L3, K1, M5, K2, K3, J1,<br>J2, L5, J3 | I/O      | OV <sub>DD</sub> |       |

| LDP[0]/CKSTOP_OUT              | H1                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LDP[1]/CKSTOP_IN               | К5                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LDP[2]                         | H2                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LDP[3]                         | G1                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LA[27:31]                      | J4, H3, G2, F1, G3                                                                                                                      | 0        | OV <sub>DD</sub> |       |

| LCS[0:3]                       | J5, H4, F2, E1                                                                                                                          | 0        | OV <sub>DD</sub> |       |

| LWE[0:3]/LSDDQM[0:3]/LBS[0:3]  | F3, G4, D1, E2                                                                                                                          | 0        | OV <sub>DD</sub> |       |

| LBCTL                          | H5                                                                                                                                      | 0        | OV <sub>DD</sub> |       |

| LALE                           | E3                                                                                                                                      | 0        | OV <sub>DD</sub> |       |

| LGPL0/LSDA10/cfg_reset_source0 | F4                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LGPL1/LSDWE/cfg_reset_source1  | D2                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LGPL2/LSDRAS/LOE               | C1                                                                                                                                      | 0        | OV <sub>DD</sub> |       |

| LGPL3/LSDCAS/cfg_reset_source2 | C2                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LGPL4/LGTA/LUPWAIT/LPBSE       | C3                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LGPL5/cfg_clkin_div            | В3                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| LCKE                           | E4                                                                                                                                      | 0        | OV <sub>DD</sub> |       |

| LCLK[0:2]                      | D4, A3, C4                                                                                                                              | 0        | OV <sub>DD</sub> |       |

| LSYNC_OUT                      | U3                                                                                                                                      | 0        | OV <sub>DD</sub> |       |

| LSYNC_IN                       | Y2                                                                                                                                      | I        | OV <sub>DD</sub> |       |

| Signal                          | Package Pin Number                    | Pin Type | Power<br>Supply   | Notes |

|---------------------------------|---------------------------------------|----------|-------------------|-------|

| MPH0_D2_VMO_SE0/DR_D10_DPPD     | B24                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D3_SPEED/DR_D11_DMMD       | A24                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D4_DP/DR_D12_VBUS_VLD      | D23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D5_DM/DR_D13_SESS_END      | C23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D6_SER_RCV/DR_D14          | B23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D7_DRVVBUS/DR_D15_IDPULLUP | A23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_NXT/DR_RX_ACTIVE_ID        | D22                                   | I        | OV <sub>DD</sub>  |       |

| MPH0_DIR_DPPULLUP/DR_RESET      | C22                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_STP_SUSPEND/DR_TX_READY    | B22                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_PWRFAULT/DR_RX_VALIDH      | A22                                   | I        | OV <sub>DD</sub>  |       |

| MPH0_PCTL0/DR_LINE_STATE0       | E21                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_PCTL1/DR_LINE_STATE1       | D21                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_CLK/DR_RX_VALID            | C21                                   | I        | OV <sub>DD</sub>  |       |

| Р                               | rogrammable Interrupt Controller      |          |                   |       |

| MCP_OUT                         | E8                                    | 0        | OV <sub>DD</sub>  | 2     |

| IRQ0/MCP_IN/GPIO2[12]           | J28                                   | I/O      | OV <sub>DD</sub>  |       |

| IRQ[1:5]/GPIO2[13:17]           | K25, J25, H26, L24, G27               | I/O      | OV <sub>DD</sub>  |       |

| IRQ[6]/GPIO2[18]/CKSTOP_OUT     | G28                                   | I/O      | OV <sub>DD</sub>  |       |

| IRQ[7]/GPIO2[19]/CKSTOP_IN      | J26                                   | I/O      | OV <sub>DD</sub>  |       |

|                                 | Ethernet Management Interface         |          |                   |       |

| EC_MDC                          | Y24                                   | 0        | LV <sub>DD1</sub> |       |

| EC_MDIO                         | Y25                                   | I/O      | LV <sub>DD1</sub> | 2     |

|                                 | Gigabit Reference Clock               | - 1      | 1                 |       |

| EC_GTX_CLK125                   | Y26                                   | I        | LV <sub>DD1</sub> |       |

| Three-Spe                       | ed Ethernet Controller (Gigabit Ether | net 1)   | 1                 |       |

| TSEC1_COL/GPIO2[20]             | M26                                   | I/O      | OV <sub>DD</sub>  |       |

| TSEC1_CRS/GPIO2[21]             | U25                                   | I/O      | LV <sub>DD1</sub> |       |

| TSEC1_GTX_CLK                   | V24                                   | 0        | LV <sub>DD1</sub> | 3     |

| TSEC1_RX_CLK                    | U26                                   | I        | LV <sub>DD1</sub> |       |

| TSEC1_RX_DV U24 I               |                                       | I        | LV <sub>DD1</sub> |       |

| TSEC1_RX_ER/GPIO2[26]           | L28 I/O OV <sub>DD</sub>              |          |                   |       |

| TSEC1_RXD[7:4]/GPIO2[22:25]     | M27, M28, N26, N27                    | I/O      | OV <sub>DD</sub>  |       |

| TSEC1_RXD[3:0]                  | W26, W24, Y28, Y27                    | I        | LV <sub>DD1</sub> |       |

| TSEC1_TX_CLK                    | N25                                   | I        | OV <sub>DD</sub>  |       |

## Table 52. MPC8347E (PBGA) Pinout Listing (continued)

### Table 52. MPC8347E (PBGA) Pinout Listing (continued)

| Signal | Package Pin Number | Pin Type | Power<br>Supply             | Notes |

|--------|--------------------|----------|-----------------------------|-------|

| MVREF1 | AF19               | I        | DDR<br>reference<br>voltage |       |

| MVREF2 | AE10               | I        | DDR<br>reference<br>voltage |       |

|        | No Connection      |          |                             |       |

| NC     | V1, V2, V5         |          |                             |       |

### Notes:

- 1. This pin is an open-drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 2. This pin is an open-drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 3. During reset, this output is actively driven rather than three-stated.

- 4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 5. This pin should have a weak pull-up if the chip is in PCI host mode. Follow the PCI specifications.

- 6. This pin must always be tied to GND.

- 7. This pin must always be left not connected.

- 8. Thermal sensitive resistor.

- 9. It is recommended that MDIC0 be tied to GRD using an 18 Ω resistor and MDIC1 be tied to DDR power using an 18 Ω resistor.

- 10.TSEC1\_TXD[3] is required an external pull-up resistor. For proper functionality of the device, this pin must be pulled up or actively driven high during a hard reset. No external pull-down resistors are allowed to be attached to this net.

Clocking

# 19 Clocking

Figure 41 shows the internal distribution of the clocks.

Figure 41. MPC8347E Clock Subsystem

The primary clock source can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. When the MPC8347E is configured as a PCI host device, CLKIN is its primary input clock. CLKIN feeds the PCI clock divider (÷2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_CLKIN\_DIV configuration input selects whether CLKIN or CLKIN/2 is driven out on the PCI\_SYNC\_OUT signal. The OCCR[PCICD*n*] parameters select whether CLKIN or CLKIN/2 is driven out on the PCI\_CLK\_OUT n signals.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the MPC8347E to function. When the MPC8347E is configured as a PCI agent device, PCI\_CLK is the primary input clock and the CLKIN signal should be tied to GND.

# 20 Thermal

This section describes the thermal specifications of the MPC8347E.

## 20.1 Thermal Characteristics

Table 61 provides the package thermal characteristics for the  $672 \ 35 \times 35 \ \text{mm}$  TBGA of the MPC8347E.

| Characteristic                                                    | Symbol            | Value | Unit | Notes |

|-------------------------------------------------------------------|-------------------|-------|------|-------|

| Junction-to-ambient natural convection on single-layer board (1s) | R <sub>θJA</sub>  | 14    | °C/W | 1, 2  |

| Junction-to-ambient natural convection on four-layer board (2s2p) | R <sub>θJMA</sub> | 11    | °C/W | 1, 3  |

| Junction-to-ambient (@ 200 ft/min) on single-layer board (1s)     | R <sub>θJMA</sub> | 11    | °C/W | 1, 3  |

| Junction-to-ambient (@ 200 ft/min) on four-layer board (2s2p)     | R <sub>θJMA</sub> | 8     | °C/W | 1, 3  |

| Junction-to-ambient (@ 2 m/s) on single-layer board (1s)          | R <sub>θJMA</sub> | 9     | °C/W | 1, 3  |

| Junction-to-ambient (@ 2 m/s) on four-layer board (2s2p)          | R <sub>θJMA</sub> | 7     | °C/W | 1, 3  |

| Junction-to-board thermal                                         | R <sub>θJB</sub>  | 3.8   | °C/W | 4     |

| Junction-to-case thermal                                          | R <sub>θJC</sub>  | 1.7   | °C/W | 5     |

| Junction-to-package natural convection on top                     | ΨJT               | 1     | °C/W | 6     |

Table 61. Package Thermal Characteristics for TBGA

#### Notes:

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal, 1 m/s is approximately equal to 200 linear feet per minute (LFM).

- 4. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Table 62 provides the package thermal characteristics for the 620  $29 \times 29$  mm PBGA of the MPC8347E.

Table 62. Package Thermal Characteristics for PBGA

| Characteristic                                                    | Symbol            | Value | Unit | Notes |

|-------------------------------------------------------------------|-------------------|-------|------|-------|

| Junction-to-ambient natural convection on single-layer board (1s) | R <sub>θJA</sub>  | 21    | °C/W | 1, 2  |

| Junction-to-ambient natural convection on four-layer board (2s2p) | R <sub>θJMA</sub> | 15    | °C/W | 1, 3  |

| Junction-to-ambient (@ 200 ft/min) on single-layer board (1s)     | R <sub>θJMA</sub> | 17    | °C/W | 1, 3  |

| Junction-to-ambient (@ 200 ft/min) on four-layer board (2s2p)     | R <sub>θJMA</sub> | 12    | °C/W | 1, 3  |

| Junction-to-board thermal                                         | R <sub>θJB</sub>  | 6     | °C/W | 4     |

# 21.3 Decoupling Recommendations

Due to large address and data buses and high operating frequencies, the MPC8347E can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8347E system, and the MPC8347E itself requires a clean, tightly regulated source of power. Therefore, the system designer should place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the MPC8347E. These capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and GND power planes in the PCB, with short traces to minimize inductance. Capacitors can be placed directly under the device using a standard escape pattern. Others can surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, distribute several bulk storage capacitors around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors are 100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

# 21.4 Connection Recommendations

To ensure reliable operation, connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ , and GND pins of the MPC8347E.

# 21.5 Output Buffer DC Impedance

The MPC8347E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 43). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8        | 2/2007  | <ul> <li>Page 1, updated first paragraph to reflect PowerQUICC II information. Updated note after second paragraph.</li> <li>In the features list in Section 1, "Overview," corrected DDR data rate to show:</li> <li>266 MHz for PBGA parts for all silicon revisions</li> <li>333 MHz for DDR for TBGA parts for silicon Rev. 1.x</li> </ul>                                                                                                                                               |

|          |         | In Table 5, "MPC8347E Typical I/O Power Dissipation," added GV <sub>DD</sub> 1.8-V values for DDR2; added table footnote to designate rates that apply only to the TBGA package.<br>In Figure 43, "JTAG Interface Connection," updated with new figure.                                                                                                                                                                                                                                      |

|          |         | In Section 23, "Ordering Information," replicated note from document introduction.                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |         | In Section 23.1, "Part Numbers Fully Addressed by This Document," replaced third sentence of first paragraph directing customer to product summary page for available frequency configuration parts. Updated back page information.                                                                                                                                                                                                                                                          |

| 7        | 8/2006  | Changed all references to revision 2.0 silicon to revision 3.0 silicon.<br>Changed V <sub>IH</sub> minimum value in Table 36, "JTAG Interface DC Electrical Characteristics," to                                                                                                                                                                                                                                                                                                             |

|          |         | OV <sub>DD</sub> – 0.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |         | In Table 60, "Suggested PLL Configurations," deleted reference-number rows 902 and 703.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6        | 3/2006  | <ul> <li>Section 2, "Electrical Characteristics," moved to second section and all other section, table, and figure numbering change accordingly.</li> <li>Table 7, "CLKIN AC Timing Specifications:" Changed max rise and fall time from 1.2 to 2.3.</li> <li>Table 22, "GMII Receive AC Timing Specifications:" Changed min t<sub>TTKHDX</sub> from 0.5 to 1.0.</li> <li>Table 30, "MII Management AC Timing Specifications:" Changed max value of t<sub>MDKHDX</sub> from 70 to</li> </ul> |

|          |         | <ul> <li>170.</li> <li>Table 34, "Local Bus General Timing Parameters—DLL on:" Changed min t<sub>LBIVKH2</sub> from 1.7 to 2.2.</li> <li>Table 36, "JTAG interface DC Electrical Characteristics:" Changed V<sub>IH</sub> input high voltage min to 2.0.</li> <li>Table 54, "Operating Frequencies for TBGA:"</li> </ul>                                                                                                                                                                     |

|          |         | <ul> <li>Updated TBD values.</li> <li>Changed maximum coherent system bus frequency for TBGA 667-MHz device to 333 MHz.<br/>Table 55, "Operating Frequencies for PBGA:"</li> </ul>                                                                                                                                                                                                                                                                                                           |

|          |         | <ul> <li>Updated TBD values.</li> <li>Changed PBGA maximum coherent system bus frequency to 266 MHz, and maximum DDR memory bus frequency to 133 MHz.</li> <li>Table 60, "Suggested PLL Configurations": Removed some values from suggested PLL</li> </ul>                                                                                                                                                                                                                                   |

|          |         | configurations for reference numbers 902, 922, 903, and 923.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |         | Table 67, "Part Numbering Nomenclature": Updated TBD values in note 1.<br>Added Table 68, "SVR Settings."<br>Added Section 23.2, "Part Marking."                                                                                                                                                                                                                                                                                                                                             |

| 5        | 10/2005 | In Table 57, updated AAVID 30x30x9.4 mm Pin Fin (natural convection) junction-to-ambient thermal resistance, from 11 to 10.                                                                                                                                                                                                                                                                                                                                                                  |

| 4        | 9/2005  | Added Table 2, "MPC8347E Typical I/O Power Dissipation."                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3        | 8/2005  | Table 1: Updated values for power dissipation that were TBD in Revision 2.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2        | 5/2005  | Table 1: Typical values for power dissipation are changed to TBD.         Table 48: Footnote numbering was wrong. THERM0 should have footnote 9 instead of 8.                                                                                                                                                                                                                                                                                                                                |

### Table 66. Document Revision History (continued)