#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 400MHz                                                                |

| Co-Processors/DSP               | Security; SEC                                                         |

| RAM Controllers                 | DDR                                                                   |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | •                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 + PHY (2)                                                     |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 672-LBGA                                                              |

| Supplier Device Package         | 672-LBGA (35x35)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8347evvagd |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

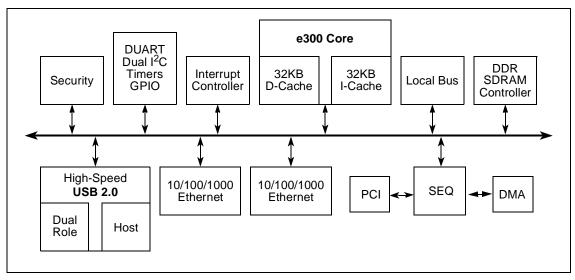

This section provides a high-level overview of the MPC8347E features. Figure 1 shows the major functional units within the MPC8347E.

### Figure 1. MPC8347E Block Diagram

Major features of the MPC8347E are as follows:

- Embedded PowerPC e300 processor core; operates at up to 667 MHz

- High-performance, superscalar processor core

- Floating-point, integer, load/store, system register, and branch processing units

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the other Freescale processor families that implement Power Architecture technology

- Double data rate, DDR SDRAM memory controller

- Programmable timing for DDR-1 SDRAM

- 32- or 64-bit data interface, up to 333-MHz data rate for TBGA, 266 MHz for PBGA

- Four banks of memory, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbit to 1 Gbit with x8/x16 data ports

- Full error checking and correction (ECC) support

- Page mode support (up to 16 simultaneous open pages)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep mode for self-refresh SDRAM

- Auto refresh

- On-the-fly power management using CKE

- Registered DIMM support

- 2.5-V SSTL2 compatible I/O

- Dual three-speed (10/100/1000) Ethernet controllers (TSECs)

- Dual controllers designed to comply with IEEE 802.3<sup>®</sup>, 802.3<sup>w</sup>, 802.3<sup>w</sup>, 802.3<sup>w</sup>, 802.3<sup>w</sup>, 802.3<sup>w</sup>

- Ethernet physical interfaces:

- 1000 Mbps IEEE Std. 802.3 GMII/RGMII, IEEE Std. 802.3z TBI/RTBI, full-duplex

- 10/100 Mbps IEEE Std. 802.3 MII full- and half-duplex

- Buffer descriptors are backward-compatible with MPC8260 and MPC860T 10/100 programming models

- 9.6-Kbyte jumbo frame support

- RMON statistics support

- Internal 2-Kbyte transmit and 2-Kbyte receive FIFOs per TSEC module

- MII management interface for control and status

- Programmable CRC generation and checking

- PCI interface

- Designed to comply with PCI Specification Revision 2.2

- Data bus width:

- 32-bit data PCI interface operating at up to 66 MHz

- PCI 3.3-V compatible

- PCI host bridge capabilities

- PCI agent mode on PCI interface

- PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Posting of processor-to-PCI and PCI-to-memory writes

- On-chip arbitration supporting five masters on PCI

- Accesses to all PCI address spaces

- Parity supported

- Selectable hardware-enforced coherency

- Address translation units for address mapping between host and peripheral

- Dual address cycle for target

- Internal configuration registers accessible from PCI

- Security engine is optimized to handle all the algorithms associated with IPSec, SSL/TLS, SRTP, IEEE Std. 802.11i<sup>®</sup>, iSCSI, and IKE processing. The security engine contains four crypto-channels, a controller, and a set of crypto execution units (EUs):

- Public key execution unit (PKEU) :

- RSA and Diffie-Hellman algorithms

- Programmable field size up to 2048 bits

- Elliptic curve cryptography

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard (DES) execution unit (DEU)

- DES and 3DES algorithms

- Two key (K1, K2) or three key (K1, K2, K3) for 3DES

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric-key cipher

- Key lengths of 128, 192, and 256 bits

- ECB, CBC, CCM, and counter (CTR) modes

- ARC four execution unit (AFEU)

- Stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- Message digest execution unit (MDEU)

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Random number generator (RNG)

- Four crypto-channels, each supporting multi-command descriptor chains

- Static and/or dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Universal serial bus (USB) dual role controller

- USB on-the-go mode with both device and host functionality

- Complies with USB specification Rev. 2.0

- Can operate as a stand-alone USB device

- One upstream facing port

- Six programmable USB endpoints

- Can operate as a stand-alone USB host controller

- USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations

- External PHY with UTMI, serial and UTMI+ low-pin interface (ULPI)

- Universal serial bus (USB) multi-port host controller

- Can operate as a stand-alone USB host controller

- USB root hub with one or two downstream-facing ports

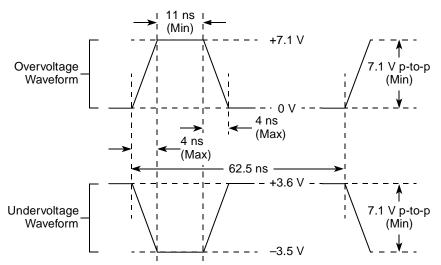

Figure 3 shows the undershoot and overshoot voltage of the PCI interface of the MPC8347E for the 3.3-V signals, respectively.

Figure 3. Maximum AC Waveforms on PCI Interface for 3.3-V Signaling

## 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                        | Output Impedance<br>(Ω) | Supply<br>Voltage                                         |

|----------------------------------------------------|-------------------------|-----------------------------------------------------------|

| Local bus interface utilities signals              | 40                      | OV <sub>DD</sub> = 3.3 V                                  |

| PCI signals (not including PCI output clocks)      | 25                      |                                                           |

| PCI output clocks (including PCI_SYNC_OUT)         | 40                      |                                                           |

| DDR signal                                         | 18                      | GV <sub>DD</sub> = 2.5 V                                  |

| TSEC/10/100 signals                                | 40                      | LV <sub>DD</sub> = 2.5/3.3 V                              |

| DUART, system control, I <sup>2</sup> C, JTAG, USB | 40                      | OV <sub>DD</sub> = 3.3 V                                  |

| GPIO signals                                       | 40                      | OV <sub>DD</sub> = 3.3 V,<br>LV <sub>DD</sub> = 2.5/3.3 V |

Table 3. Output Drive Capability

# 2.2 Power Sequencing

MPC8347E does not require the core supply voltage and I/O supply voltages to be applied in any particular order. Note that during the power ramp up, before the power supplies are stable, there may be a period of time that I/O pins are actively driven. After the power is stable, as long as **PORESET** is asserted, most I/O pins are three-stated. To minimize the time that I/O pins are actively driven, it is recommended to apply core voltage before I/O voltage and assert **PORESET** before the power supplies fully ramp up.

9 USB

This section provides the AC and DC electrical specifications for the USB interface of the MPC8347E.

## 9.1 USB DC Electrical Characteristics

Table 31 provides the DC electrical characteristics for the USB interface.

| Parameter                                            | Symbol          | Min                    | Мах                    | Unit |

|------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current                                        | I <sub>IN</sub> | —                      | ±5                     | μA   |

| High-level output voltage, I <sub>OH</sub> = −100 μA | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$     | V <sub>OL</sub> | _                      | 0.2                    | V    |

### Table 31. USB DC Electrical Characteristics

# 9.2 USB AC Electrical Specifications

Table 32 describes the general timing parameters of the USB interface of the MPC8347E.

| Table 32. USB General Timing | Parameters ( | ULPI Mode Only) |

|------------------------------|--------------|-----------------|

|------------------------------|--------------|-----------------|

| Parameter                              | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|----------------------------------------|---------------------|-----|-----|------|-------|

| USB clock cycle time                   | t <sub>USCK</sub>   | 15  | _   | ns   | 2–5   |

| Input setup to USB clock—all inputs    | t <sub>USIVKH</sub> | 4   | —   | ns   | 2–5   |

| Input hold to USB clock—all inputs     | t <sub>USIXKH</sub> | 1   | —   | ns   | 2–5   |

| USB clock to output valid—all outputs  | t <sub>USKHOV</sub> | —   | 7   | ns   | 2–5   |

| Output hold from USB clock—all outputs | t <sub>USKHOX</sub> | 2   | _   | ns   | 2–5   |

Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>USIXKH</sub> symbolizes USB timing (US) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes USB timing (US) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to USB clock.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of the USB clock to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

### Table 37. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup> (continued)

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Мах     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-------|

| Output hold times:<br>Boundary-scan data<br>TDO                            | <sup>t</sup> jtkldx<br><sup>t</sup> jtklox | 2<br>2 |         | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | <sup>t</sup> jtkldz<br><sup>t</sup> jtkloz | 2<br>2 | 19<br>9 | ns   | 5, 6  |

Notes:

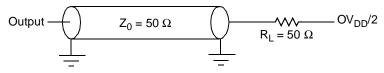

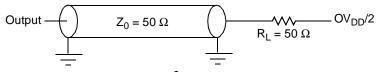

- 1. All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50  $\Omega$  load (see Figure 26). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to  $t_{TCLK}$ .

- 6. Guaranteed by design and characterization.

Figure 26 provides the AC test load for TDO and the boundary-scan outputs of the MPC8347E.

Figure 26. AC Test Load for the JTAG Interface

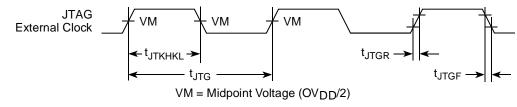

Figure 27 provides the JTAG clock input timing diagram.

Figure 27. JTAG Clock Input Timing Diagram

| Parameter                                                                       | Symbol <sup>1</sup> | Min                                | Max | Unit |

|---------------------------------------------------------------------------------|---------------------|------------------------------------|-----|------|

| Fall time of both SDA and SCL signals <sup>5</sup>                              | t <sub>I2CF</sub>   |                                    | 300 | ns   |

| Setup time for STOP condition                                                   | t <sub>I2PVKH</sub> | 0.6                                |     | μs   |

| Bus free time between a STOP and START condition                                | t <sub>I2KHDX</sub> | 1.3                                | _   | μs   |

| Noise margin at the LOW level for each connected device (including hysteresis)  | V <sub>NL</sub>     | $0.1 \times OV_{DD}$               | —   | V    |

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times \text{OV}_{\text{DD}}$ | —   | V    |

## Table 39. I<sup>2</sup>C AC Electrical Specifications (continued)

Notes:

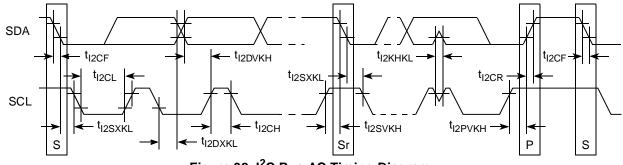

- 1. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>12DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>12SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) goes invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the stop condition (P) reaches the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

- MPC8347E provides a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IH</sub>(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum t<sub>I2DVKH</sub> must be met only if the device does not stretch the LOW period (t<sub>I2CL</sub>) of the SCL signal.

- 4.  $C_B$  = capacitance of one bus line in pF.

- 5.) The MPC8347E does not follow the "I2C-BUS Specifications" version 2.1 regarding the tI2CF AC parameter.

Figure 31 provides the AC test load for the  $I^2C$ .

Figure 31. I<sup>2</sup>C AC Test Load

Figure 32 shows the AC timing diagram for the  $I^2C$  bus.

Figure 32. I<sup>2</sup>C Bus AC Timing Diagram

Timers

# 14 Timers

This section describes the DC and AC electrical specifications for the timers.

# 14.1 Timer DC Electrical Characteristics

Table 43 provides the DC electrical characteristics for the MPC8347E timer pins, including TIN,  $\overline{\text{TOUT}}$ ,  $\overline{\text{TGATE}}$ , and RTC\_CLK.

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                           | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                           | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                           |      | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

Table 43. Timer DC Electrical Characteristics

# 14.2 Timer AC Timing Specifications

Table 44 provides the timer input and output AC timing specifications.

### Table 44. Timers Input AC Timing Specifications<sup>1</sup>

| Characteristic                    | Symbol <sup>2</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by external synchronous logic. Timer inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation.

|                                            | Cos47E (TBGA) Findut Listing (Co | <b>_</b> |                   | 1     |

|--------------------------------------------|----------------------------------|----------|-------------------|-------|

| Signal                                     | Package Pin Number               | Pin Type | Power<br>Supply   | Notes |

| MPH1_NXT/DR_SESS_VLD_NXT                   | D27                              | Ι        | OV <sub>DD</sub>  |       |

| MPH1_DIR_DPPULLUP/<br>DR_XCVR_SEL_DPPULLUP | A28                              | I/O      | OV <sub>DD</sub>  |       |

| MPH1_STP_SUSPEND/<br>DR_STP_SUSPEND        | F26                              | 0        | OV <sub>DD</sub>  |       |

| MPH1_PWRFAULT/<br>DR_RX_ERROR_PWRFAULT     | E27                              | I        | OV <sub>DD</sub>  |       |

| MPH1_PCTL0/DR_TX_VALID_PCTL0               | A29                              | 0        | OV <sub>DD</sub>  |       |

| MPH1_PCTL1/DR_TX_VALIDH_PCTL1              | D28                              | 0        | OV <sub>DD</sub>  |       |

| MPH1_CLK/DR_CLK                            | B29                              | I        | OV <sub>DD</sub>  |       |

|                                            | USB Port 0                       |          |                   |       |

| MPH0_D0_ENABLEN/DR_D8_CHGVBUS              | C29                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D1_SER_TXD/DR_D9_DCHGVBUS             | A30                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D2_VMO_SE0/DR_D10_DPPD                | E28                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D3_SPEED/DR_D11_DMMD                  | B30                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D4_DP/DR_D12_VBUS_VLD                 | C30                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D5_DM/DR_D13_SESS_END                 | A31                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D6_SER_RCV/DR_D14                     | B31                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D7_DRVVBUS/DR_D15_IDPULLUP            | C31                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_NXT/DR_RX_ACTIVE_ID                   | B32                              | I        | OV <sub>DD</sub>  |       |

| MPH0_DIR_DPPULLUP/DR_RESET                 | A32                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_STP_SUSPEND/DR_TX_READY               | A33                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_PWRFAULT/DR_RX_VALIDH                 | C32                              | I        | OV <sub>DD</sub>  |       |

| MPH0_PCTL0/DR_LINE_STATE0                  | D31                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_PCTL1/DR_LINE_STATE1                  | E30                              | I/O      | OV <sub>DD</sub>  |       |

| MPH0_CLK/DR_RX_VALID                       | B33                              | I        | OV <sub>DD</sub>  |       |

| Р                                          | rogrammable Interrupt Controller |          |                   |       |

| MCP_OUT                                    | AN33                             | 0        | OV <sub>DD</sub>  | 2     |

| IRQ0/MCP_IN/GPIO2[12]                      | C19                              | I/O      | OV <sub>DD</sub>  |       |

| IRQ[1:5]/GPIO2[13:17]                      | C22, A22, D21, C21, B21          | I/O      | OV <sub>DD</sub>  |       |

| IRQ[6]/GPIO2[18]/CKSTOP_OUT                | A21                              | I/O      | OV <sub>DD</sub>  |       |

| IRQ[7]/GPIO2[19]/CKSTOP_IN                 | C20                              | I/O      | OV <sub>DD</sub>  |       |

|                                            | Ethernet Management Interface    | 1        | 1                 |       |

| EC_MDC                                     | A7                               | 0        | LV <sub>DD1</sub> |       |

| EC_MDIO                                    | E9                               | I/O      | LV <sub>DD1</sub> | 2     |

### Table 51. MPC8347E (TBGA) Pinout Listing (continued)

| Signal                          | Package Pin Number                    | Pin Type | Power<br>Supply   | Notes |

|---------------------------------|---------------------------------------|----------|-------------------|-------|

| MPH0_D2_VMO_SE0/DR_D10_DPPD     | B24                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D3_SPEED/DR_D11_DMMD       | A24                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D4_DP/DR_D12_VBUS_VLD      | D23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D5_DM/DR_D13_SESS_END      | C23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D6_SER_RCV/DR_D14          | B23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_D7_DRVVBUS/DR_D15_IDPULLUP | A23                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_NXT/DR_RX_ACTIVE_ID        | D22                                   | I        | OV <sub>DD</sub>  |       |

| MPH0_DIR_DPPULLUP/DR_RESET      | C22                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_STP_SUSPEND/DR_TX_READY    | B22                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_PWRFAULT/DR_RX_VALIDH      | A22                                   | I        | OV <sub>DD</sub>  |       |

| MPH0_PCTL0/DR_LINE_STATE0       | E21                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_PCTL1/DR_LINE_STATE1       | D21                                   | I/O      | OV <sub>DD</sub>  |       |

| MPH0_CLK/DR_RX_VALID            | C21                                   | I        | OV <sub>DD</sub>  |       |

| Р                               | rogrammable Interrupt Controller      |          |                   |       |

| MCP_OUT                         | E8                                    | 0        | OV <sub>DD</sub>  | 2     |

| IRQ0/MCP_IN/GPIO2[12]           | J28                                   | I/O      | OV <sub>DD</sub>  |       |

| IRQ[1:5]/GPIO2[13:17]           | K25, J25, H26, L24, G27               | I/O      | OV <sub>DD</sub>  |       |

| IRQ[6]/GPIO2[18]/CKSTOP_OUT     | G28                                   | I/O      | OV <sub>DD</sub>  |       |

| IRQ[7]/GPIO2[19]/CKSTOP_IN      | J26                                   | I/O      | OV <sub>DD</sub>  |       |

|                                 | Ethernet Management Interface         | ŀ        |                   |       |

| EC_MDC                          | Y24                                   | 0        | LV <sub>DD1</sub> |       |

| EC_MDIO                         | Y25                                   | I/O      | LV <sub>DD1</sub> | 2     |

|                                 | Gigabit Reference Clock               | - 1      | 1                 |       |

| EC_GTX_CLK125                   | Y26                                   | I        | LV <sub>DD1</sub> |       |

| Three-Spe                       | ed Ethernet Controller (Gigabit Ether | net 1)   | 1                 |       |

| TSEC1_COL/GPIO2[20]             | M26                                   | I/O      | OV <sub>DD</sub>  |       |

| TSEC1_CRS/GPIO2[21]             | U25                                   | I/O      | LV <sub>DD1</sub> |       |

| TSEC1_GTX_CLK                   | V24                                   | 0        | LV <sub>DD1</sub> | 3     |

| TSEC1_RX_CLK                    | U26                                   | I        | LV <sub>DD1</sub> |       |

| TSEC1_RX_DV                     | U24                                   | I        | LV <sub>DD1</sub> |       |

| TSEC1_RX_ER/GPIO2[26]           | L28                                   | I/O      | OV <sub>DD</sub>  |       |

| TSEC1_RXD[7:4]/GPIO2[22:25]     | M27, M28, N26, N27                    | I/O      | OV <sub>DD</sub>  |       |

| TSEC1_RXD[3:0]                  | W26, W24, Y28, Y27                    | I        | LV <sub>DD1</sub> |       |

| TSEC1_TX_CLK                    | N25                                   | I        | OV <sub>DD</sub>  |       |

## Table 52. MPC8347E (PBGA) Pinout Listing (continued)

### Table 52. MPC8347E (PBGA) Pinout Listing (continued)

| Signal | Package Pin Number | Pin Type | Power<br>Supply             | Notes |

|--------|--------------------|----------|-----------------------------|-------|

| MVREF1 | AF19               | I        | DDR<br>reference<br>voltage |       |

| MVREF2 | AE10               | I        | DDR<br>reference<br>voltage |       |

|        | No Connection      |          |                             |       |

| NC     | V1, V2, V5         |          |                             |       |

### Notes:

- 1. This pin is an open-drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 2. This pin is an open-drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

- 3. During reset, this output is actively driven rather than three-stated.

- 4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 5. This pin should have a weak pull-up if the chip is in PCI host mode. Follow the PCI specifications.

- 6. This pin must always be tied to GND.

- 7. This pin must always be left not connected.

- 8. Thermal sensitive resistor.

- 9. It is recommended that MDIC0 be tied to GRD using an 18 Ω resistor and MDIC1 be tied to DDR power using an 18 Ω resistor.

- 10.TSEC1\_TXD[3] is required an external pull-up resistor. For proper functionality of the device, this pin must be pulled up or actively driven high during a hard reset. No external pull-down resistors are allowed to be attached to this net.

|                                        |      |                                                       | Input Clock Frequency (MHz) <sup>2</sup> |                              |       |       |

|----------------------------------------|------|-------------------------------------------------------|------------------------------------------|------------------------------|-------|-------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock<br>Ratio <sup>2</sup> | 16.67                                    | 25                           | 33.33 | 66.67 |

|                                        |      | Ratio                                                 | C                                        | <i>b_clk</i> Frequency (MHz) |       |       |

| Low                                    | 0010 | 2 : 1                                                 |                                          |                              |       | 133   |

| Low                                    | 0011 | 3 : 1                                                 |                                          |                              | 100   | 200   |

| Low                                    | 0100 | 4 : 1                                                 |                                          | 100                          | 133   | 266   |

| Low                                    | 0101 | 5 : 1                                                 |                                          | 125                          | 166   | 333   |

| Low                                    | 0110 | 6 : 1                                                 | 100                                      | 150                          | 200   |       |

| Low                                    | 0111 | 7:1                                                   | 116                                      | 175                          | 233   |       |

| Low                                    | 1000 | 8 : 1                                                 | 133                                      | 200                          | 266   |       |

| Low                                    | 1001 | 9:1                                                   | 150                                      | 225                          | 300   |       |

| Low                                    | 1010 | 10 : 1                                                | 166                                      | 250                          | 333   |       |

| Low                                    | 1011 | 11 : 1                                                | 183                                      | 275                          |       | 1     |

| Low                                    | 1100 | 12 : 1                                                | 200                                      | 300                          |       |       |

| Low                                    | 1101 | 13 : 1                                                | 216                                      | 325                          |       |       |

| Low                                    | 1110 | 14 : 1                                                | 233                                      |                              | 1     |       |

| Low                                    | 1111 | 15 : 1                                                | 250                                      |                              |       |       |

| Low                                    | 0000 | 16 : 1                                                | 266                                      |                              |       |       |

| High                                   | 0010 | 4:1                                                   |                                          | 100                          | 133   | 266   |

| High                                   | 0011 | 6 : 1                                                 | 100                                      | 150                          | 200   |       |

| High                                   | 0100 | 8 : 1                                                 | 133                                      | 200                          | 266   |       |

| High                                   | 0101 | 10 : 1                                                | 166                                      | 250                          | 333   |       |

| High                                   | 0110 | 12 : 1                                                | 200                                      | 300                          |       |       |

| High                                   | 0111 | 14 : 1                                                | 233                                      |                              |       |       |

| High                                   | 1000 | 16 : 1                                                | 266                                      |                              |       |       |

Table 58. CSB Frequency Options for Agent Mode

<sup>1</sup> CFG\_CLKIN\_DIV doubles csb\_clk if set high.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode. DDR2 memory may be used at 133 MHz provided that the memory components are specified for operation at this frequency.

# 19.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). Table 59 shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in Table 59 should be considered as reserved.

|          | Tyco Electronics<br>Chip Coolers <sup>TM</sup><br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com         | 800-522-2800 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|--------------|

|          | Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                             | 603-635-5102 |

| Interfac | ce material vendors include the following:                                                                                            |              |

|          | Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01801                                                                                  | 781-935-4850 |

|          | Internet: www.chomerics.com                                                                                                           |              |

|          | Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>P.O. Box 994<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

|          | Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                        | 888-642-7674 |

|          | The Bergquist Company<br>18930 West 78th St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                            | 800-347-4572 |

# 20.3 Heat Sink Attachment

When heat sinks are attached, an interface material is required, preferably thermal grease and a spring clip. The spring clip should connect to the printed-circuit board, either to the board itself, to hooks soldered to the board, or to a plastic stiffener. Avoid attachment forces that can lift the edge of the package or peel the package from the board. Such peeling forces reduce the solder joint lifetime of the package. The recommended maximum force on the top of the package is 10 lb force (4.5 kg force). Any adhesive attachment should attach to painted or plastic surfaces, and its performance should be verified under the application requirements.

## 20.3.1 Experimental Determination of the Junction Temperature with a Heat Sink

When a heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally

#### Thermal

required in the heat sink. Minimize the size of the clearance to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

$$T_J = T_C + (R_{\theta JC} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_C$  = case temperature of the package (°C)  $R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)  $P_D$  = power dissipation (W)

# 21.3 Decoupling Recommendations

Due to large address and data buses and high operating frequencies, the MPC8347E can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8347E system, and the MPC8347E itself requires a clean, tightly regulated source of power. Therefore, the system designer should place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the MPC8347E. These capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and GND power planes in the PCB, with short traces to minimize inductance. Capacitors can be placed directly under the device using a standard escape pattern. Others can surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, distribute several bulk storage capacitors around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors are 100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

# 21.4 Connection Recommendations

To ensure reliable operation, connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ , and GND pins of the MPC8347E.

# 21.5 Output Buffer DC Impedance

The MPC8347E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 43). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

#### System Design Information

the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for the output pins.

# 21.7 Pull-Up Resistor Requirements

The MPC8347E requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open-drain pins, including I<sup>2</sup>C pins, the Ethernet Management MDIO pin, and IPIC interrupt pins.

For more information on required pull-up resistors and the connections required for the JTAG interface, refer to application note AN2931, *PowerQUICC<sup>TM</sup> Design Checklist*.

#### **Ordering Information**

| Table | 68. | SVR | Settings | (continued) |

|-------|-----|-----|----------|-------------|

|-------|-----|-----|----------|-------------|

| ſ | MPC8347E | PBGA | 8054_0010 |

|---|----------|------|-----------|

| F | MPC8347  | PBGA | 8055_0010 |

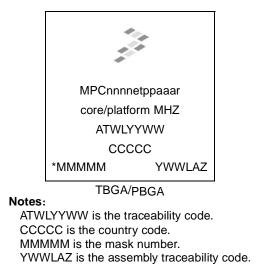

## 23.2 Part Marking

Parts are marked as in the example shown in Figure 44.

Figure 44. Freescale Part Marking for TBGA or PBGA Devices

### THIS PAGE INTENTIONALLY LEFT BLANK

**Ordering Information**

## THIS PAGE INTENTIONALLY LEFT BLANK

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. IIEEE 802.3, 802.3u, 802.3x, 802.3z, 802.3ac, 802.11i, and 1149.1 are trademarks or registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2005–2009. All rights reserved.

Document Number: MPC8347EEC Rev. 11 02/2009