#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Core Processor                  | PowerPC e300                                                          |

|---------------------------------|-----------------------------------------------------------------------|

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 533MHz                                                                |

| Co-Processors/DSP               | Security; SEC                                                         |

| RAM Controllers                 | DDR                                                                   |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 + PHY (2)                                                     |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 672-LBGA                                                              |

| Supplier Device Package         | 672-LBGA (35x35)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8347ezuajd |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

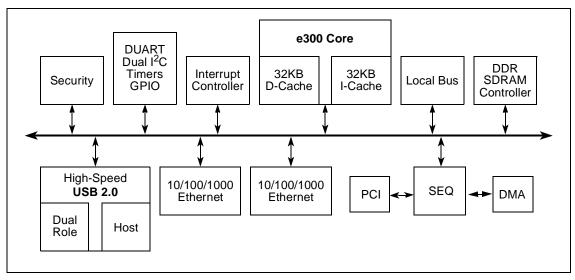

This section provides a high-level overview of the MPC8347E features. Figure 1 shows the major functional units within the MPC8347E.

#### Figure 1. MPC8347E Block Diagram

Major features of the MPC8347E are as follows:

- Embedded PowerPC e300 processor core; operates at up to 667 MHz

- High-performance, superscalar processor core

- Floating-point, integer, load/store, system register, and branch processing units

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the other Freescale processor families that implement Power Architecture technology

- Double data rate, DDR SDRAM memory controller

- Programmable timing for DDR-1 SDRAM

- 32- or 64-bit data interface, up to 333-MHz data rate for TBGA, 266 MHz for PBGA

- Four banks of memory, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbit to 1 Gbit with x8/x16 data ports

- Full error checking and correction (ECC) support

- Page mode support (up to 16 simultaneous open pages)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep mode for self-refresh SDRAM

- Auto refresh

- Programmable field size up to 2048 bits

- Elliptic curve cryptography

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard (DES) execution unit (DEU)

- DES and 3DES algorithms

- Two key (K1, K2) or three key (K1, K2, K3) for 3DES

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric-key cipher

- Key lengths of 128, 192, and 256 bits

- ECB, CBC, CCM, and counter (CTR) modes

- ARC four execution unit (AFEU)

- Stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- Message digest execution unit (MDEU)

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Random number generator (RNG)

- Four crypto-channels, each supporting multi-command descriptor chains

- Static and/or dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Universal serial bus (USB) dual role controller

- USB on-the-go mode with both device and host functionality

- Complies with USB specification Rev. 2.0

- Can operate as a stand-alone USB device

- One upstream facing port

- Six programmable USB endpoints

- Can operate as a stand-alone USB host controller

- USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations

- External PHY with UTMI, serial and UTMI+ low-pin interface (ULPI)

- Universal serial bus (USB) multi-port host controller

- Can operate as a stand-alone USB host controller

- USB root hub with one or two downstream-facing ports

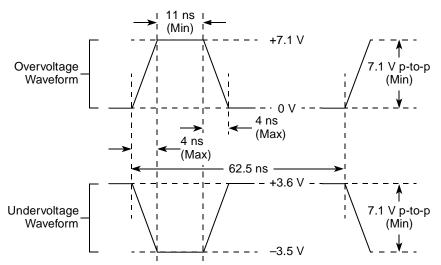

Figure 3 shows the undershoot and overshoot voltage of the PCI interface of the MPC8347E for the 3.3-V signals, respectively.

Figure 3. Maximum AC Waveforms on PCI Interface for 3.3-V Signaling

### 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                        | Output Impedance<br>(Ω) | Supply<br>Voltage                                         |

|----------------------------------------------------|-------------------------|-----------------------------------------------------------|

| Local bus interface utilities signals              | 40                      | OV <sub>DD</sub> = 3.3 V                                  |

| PCI signals (not including PCI output clocks)      | 25                      |                                                           |

| PCI output clocks (including PCI_SYNC_OUT)         | 40                      |                                                           |

| DDR signal                                         | 18                      | GV <sub>DD</sub> = 2.5 V                                  |

| TSEC/10/100 signals                                | 40                      | LV <sub>DD</sub> = 2.5/3.3 V                              |

| DUART, system control, I <sup>2</sup> C, JTAG, USB | 40                      | OV <sub>DD</sub> = 3.3 V                                  |

| GPIO signals                                       | 40                      | OV <sub>DD</sub> = 3.3 V,<br>LV <sub>DD</sub> = 2.5/3.3 V |

Table 3. Output Drive Capability

### 2.2 Power Sequencing

MPC8347E does not require the core supply voltage and I/O supply voltages to be applied in any particular order. Note that during the power ramp up, before the power supplies are stable, there may be a period of time that I/O pins are actively driven. After the power is stable, as long as **PORESET** is asserted, most I/O pins are three-stated. To minimize the time that I/O pins are actively driven, it is recommended to apply core voltage before I/O voltage and assert **PORESET** before the power supplies fully ramp up.

#### DDR SDRAM

#### Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter         | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|-------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end | t <sub>DDKLME</sub> | -0.9 | 0.3 | ns   | 7     |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

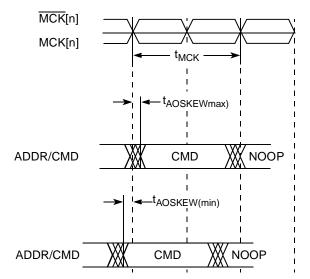

- 3. In the source synchronous mode, MCK/MCK can be shifted in 1/4 applied cycle increments through the clock control register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8349E PowerQUICC<sup>™</sup> II Pro Integrated Host Processor Family Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8347E.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the MPC8347E. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

Figure 5 shows the DDR SDRAM output timing for address skew with respect to any MCK.

Figure 5. Timing Diagram for t<sub>AOSKEW</sub> Measurement

Figure 6 provides the AC test load for the DDR bus.

#### DDR SDRAM

| Load                                               | Delay | Unit |

|----------------------------------------------------|-------|------|

| 4 devices (12 pF)                                  | 3.0   | ns   |

| 9 devices (27 pF)                                  | 3.6   | ns   |

| 36 devices (108 pF) + 40 pF compensation capacitor | 5.0   | ns   |

| 36 devices (108 pF) + 80 pF compensation capacitor | 5.2   | ns   |

#### Table 16. Expected Delays for Address/Command

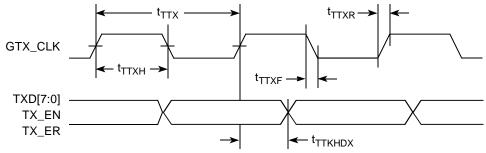

Figure 13 shows the TBI transmit AC timing diagram.

Figure 13. TBI Transmit AC Timing Diagram

### 8.2.3.2 TBI Receive AC Timing Specifications

Table 26 provides the TBI receive AC timing specifications.

#### Table 26. TBI Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                                   | Symbol <sup>1</sup>                 | Min | Тур  | Мах | Unit |

|-----------------------------------------------------------------------|-------------------------------------|-----|------|-----|------|

| PMA_RX_CLK clock period                                               | t <sub>TRX</sub>                    |     | 16.0 |     | ns   |

| PMA_RX_CLK skew                                                       | t <sub>SKTRX</sub>                  | 7.5 | —    | 8.5 | ns   |

| RX_CLK duty cycle                                                     | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | —    | 60  | %    |

| RXD[7:0], RX_DV, RX_ER (RCG[9:0]) setup time to rising PMA_RX_CLK     | t <sub>trdvkh</sub> 2               | 2.5 | —    | —   | ns   |

| RXD[7:0], RX_DV, RX_ER (RCG[9:0]) hold time to rising PMA_RX_CLK      | t <sub>TRDXKH</sub> 2               | 1.5 | _    | —   | ns   |

| RX_CLK clock rise time V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>TRXR</sub>                   | 0.7 | —    | 2.4 | ns   |

| RX_CLK clock fall time V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>TRXF</sub>                   | 0.7 | —    | 2.4 | ns   |

Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript SK followed by the clock that is being skewed (TRX).

</sub>

2. Setup and hold time of even numbered RCG are measured from the riding edge of PMA\_RX\_CLK1. Setup and hold times of odd-numbered RCG are measured from the riding edge of PMA\_RX\_CLK0.

9 USB

This section provides the AC and DC electrical specifications for the USB interface of the MPC8347E.

### 9.1 USB DC Electrical Characteristics

Table 31 provides the DC electrical characteristics for the USB interface.

| Parameter                                            | Symbol          | Min                    | Мах                    | Unit |

|------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current                                        | I <sub>IN</sub> | —                      | ±5                     | μA   |

| High-level output voltage, I <sub>OH</sub> = −100 μA | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$     | V <sub>OL</sub> | _                      | 0.2                    | V    |

#### Table 31. USB DC Electrical Characteristics

## 9.2 USB AC Electrical Specifications

Table 32 describes the general timing parameters of the USB interface of the MPC8347E.

| Table 32. USB General Timing | Parameters ( | ULPI Mode Only) |

|------------------------------|--------------|-----------------|

|------------------------------|--------------|-----------------|

| Parameter                              | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|----------------------------------------|---------------------|-----|-----|------|-------|

| USB clock cycle time                   | t <sub>USCK</sub>   | 15  | _   | ns   | 2–5   |

| Input setup to USB clock—all inputs    | t <sub>USIVKH</sub> | 4   | —   | ns   | 2–5   |

| Input hold to USB clock—all inputs     | t <sub>USIXKH</sub> | 1   | —   | ns   | 2–5   |

| USB clock to output valid—all outputs  | t <sub>USKHOV</sub> | —   | 7   | ns   | 2–5   |

| Output hold from USB clock—all outputs | t <sub>USKHOX</sub> | 2   | _   | ns   | 2–5   |

Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>USIXKH</sub> symbolizes USB timing (US) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes USB timing (US) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to USB clock.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of the USB clock to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

| Table 35. Local Bus General Timing Parameters—DLL Bypass <sup>9</sup> (continued) |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

| Parameter                                            | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|------------------------------------------------------|---------------------|-----|-----|------|-------|

| Local bus clock to output valid                      | t <sub>LBKLOV</sub> | _   | 3   | ns   | 3     |

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ</sub> | _   | 4   | ns   | 8     |

Notes:

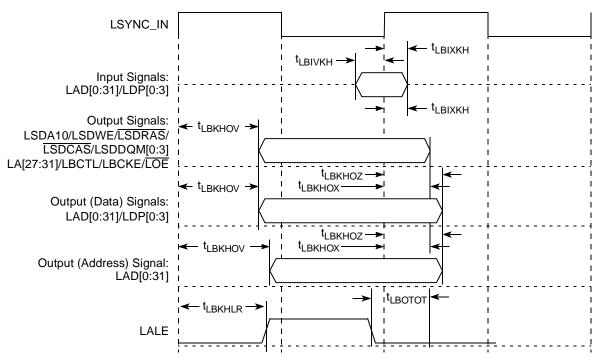

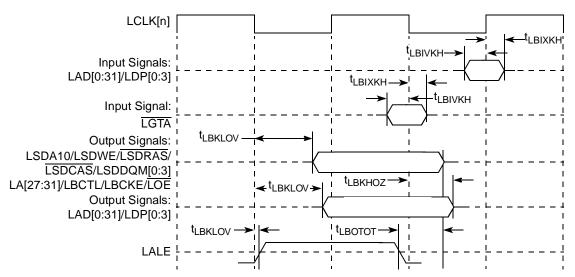

- The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to the falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or the rising edge of LCLK0 (for all other inputs).

- 3. All signals are measured from  $OV_{DD}/2$  of the rising/falling edge of LCLK0 to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.

- 6. t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.the

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin equals to the load on the LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 9. DLL bypass mode is not recommended for use at frequencies above 66 MHz.

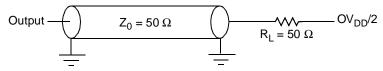

Figure 19 provides the AC test load for the local bus.

Figure 19. Local Bus C Test Load

#### Local Bus

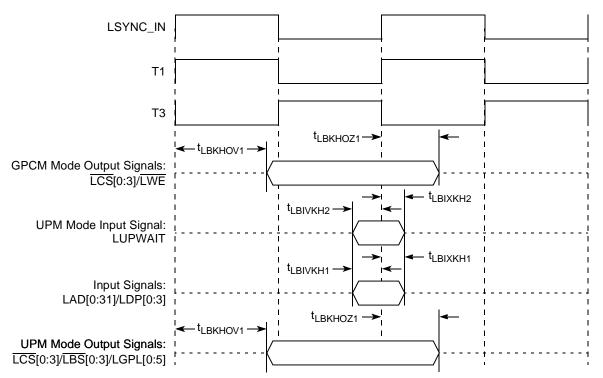

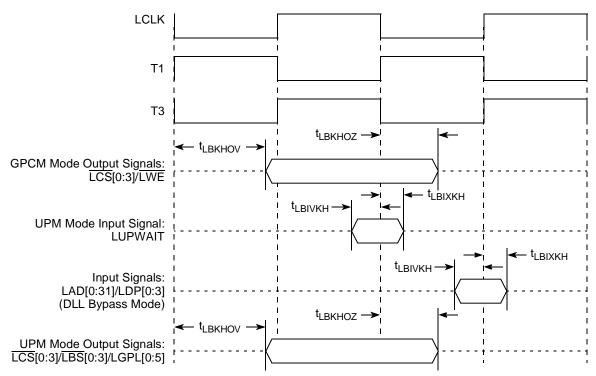

Figure 20 through Figure 25 show the local bus signals.

Figure 20. Local Bus Signals, Nonspecial Signals Only (DLL Enabled)

Figure 21. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

Figure 22. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Enabled)

Figure 23. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Bypass Mode)

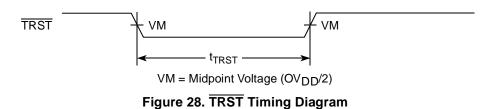

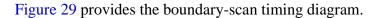

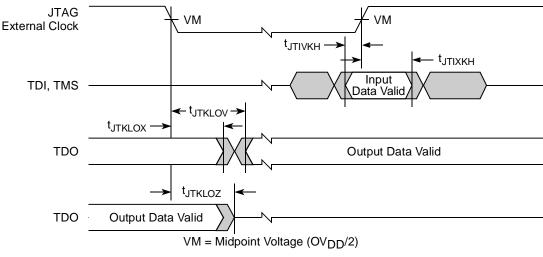

JTAG

Figure 28 provides the TRST timing diagram.

Figure 29. Boundary-Scan Timing Diagram

Figure 30 provides the test access port timing diagram.

Figure 30. Test Access Port Timing Diagram

17 SPI

This section describes the SPI DC and AC electrical specifications.

### 17.1 SPI DC Electrical Characteristics

Table 49 provides the SPI DC electrical characteristics.

#### Table 49. SPI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                           | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                           | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                           |      | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

### 17.2 SPI AC Timing Specifications

Table 50 provides the SPI input and output AC timing specifications.

#### Table 50. SPI AC Timing Specifications<sup>1</sup>

| Characteristic                                          | Symbol <sup>2</sup> | Min | Мах | Unit |

|---------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs valid—Master mode (internal clock) delay    | t <sub>NIKHOV</sub> |     | 6   | ns   |

| SPI outputs hold—Master mode (internal clock) delay     | t <sub>NIKHOX</sub> | 0.5 |     | ns   |

| SPI outputs valid—Slave mode (external clock) delay     | t <sub>NEKHOV</sub> |     | 8   | ns   |

| SPI outputs hold—Slave mode (external clock) delay      | t <sub>NEKHOX</sub> | 2   |     | ns   |

| SPI inputs—Master mode (internal clock input setup time | t <sub>NIIVKH</sub> | 4   |     | ns   |

| SPI inputs—Master mode (internal clock input hold time  | t <sub>NIIXKH</sub> | 0   |     | ns   |

| SPI inputs—Slave mode (external clock) input setup time | t <sub>NEIVKH</sub> | 4   |     | ns   |

| SPI inputs—Slave mode (external clock) input hold time  | t <sub>NEIXKH</sub> | 2   |     | ns   |

Notes:

1. Output specifications are measured from the 50 percent level of the rising edge of CLKIN to the 50 percent level of the signal. Timings are measured at the pin.

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>NIKHOX</sub> symbolizes the internal timing (NI) for the time SPICLK clock reference (K) goes to the high state (H) until outputs (O) are invalid (X).

</sub>

## 18.5 Pinout Listings

Table 51 provides the pinout listing for the MPC8347E, 672 TBGA package.

#### Table 51. MPC8347E (TBGA) Pinout Listing

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|--|

|                        | PCI                                                                                                                                                                                                                                                                                                                    |          | 1                |       |  |

| PCI_INTA/IRQ_OUT       | B34                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> | 2     |  |

| PCI_RESET_OUT          | C33                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> |       |  |

| PCI_AD[31:0]           | G30, G32, G34, H31, H32, H33, H34,<br>J29, J32, J33, L30, K31, K33, K34,<br>L33, L34, P34, R29, R30, R33, R34,<br>T31, T32, T33, U31, U34, V31, V32,<br>V33, V34, W33, W34                                                                                                                                             | I/O      | OV <sub>DD</sub> |       |  |

| PCI_C/BE[3:0]          | J30, M31, P33, T34                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> |       |  |

| PCI_PAR                | P32                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |       |  |

| PCI_FRAME              | M32                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |  |

| PCI_TRDY               | N29                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |  |

| PCI_IRDY               | M34                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |  |

| PCI_STOP               | N31                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |  |

| PCI_DEVSEL             | N30                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |  |

| PCI_IDSEL              | J31                                                                                                                                                                                                                                                                                                                    | Ι        | OV <sub>DD</sub> |       |  |

| PCI_SERR               | N34                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |  |

| PCI_PERR               | N33                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5     |  |

| PCI_REQ[0]             | D32                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |       |  |

| PCI_REQ[1]/CPCI1_HS_ES | D34                                                                                                                                                                                                                                                                                                                    | I        | OV <sub>DD</sub> |       |  |

| PCI_REQ[2:4]           | E34, F32, G29                                                                                                                                                                                                                                                                                                          | I        | OV <sub>DD</sub> |       |  |

| PCI_GNT0               | C34                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |       |  |

| PCI_GNT1/CPCI1_HS_LED  | D33                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> |       |  |

| PCI_GNT2/CPCI1_HS_ENUM | E33                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub> |       |  |

| PCI_GNT[3:4]           | F31, F33                                                                                                                                                                                                                                                                                                               | 0        | OV <sub>DD</sub> |       |  |

| M66EN                  | A19                                                                                                                                                                                                                                                                                                                    | I        | OV <sub>DD</sub> |       |  |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                             |          |                  |       |  |

| MDQ[0:63]              | D5, A3, C3, D3, C4, B3, C2, D4, D2,<br>E5, G2, H6, E4, F3, G4, G3, H1, J2,<br>L6, M6, H2, K6, L2, M4, N2, P4, R2,<br>T4, P6, P3, R1, T2, AB5, AA3, AD6,<br>AE4, AB4, AC2, AD3, AE6, AE3, AG4,<br>AK5, AK4, AE2, AG6, AK3, AK2, AL2,<br>AL1, AM5, AP5, AM2, AN1, AP4, AN5,<br>AJ7, AN7, AM8, AJ9, AP6, AL7, AL9,<br>AN8 | I/O      | GV <sub>DD</sub> |       |  |

| Signal                                     | Package Pin Number         | Pin Type | Power<br>Supply  | Notes |

|--------------------------------------------|----------------------------|----------|------------------|-------|

|                                            | General Purpose I/O Timers |          | 1                |       |

| GPIO1[0]/GTM1_TIN1/GTM2_TIN2               | D27                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[1]/GTM1_TGATE1/GTM2_TGATE2           | E26                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[2]/GTM1_TOUT1                        | D28                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[3]/GTM1_TIN2/GTM2_TIN1               | G25                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[4]/GTM1_TGATE2/GTM2_TGATE1           | J24                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[5]/GTM1_TOUT2/GTM2_TOUT1             | F26                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[6]/GTM1_TIN3/GTM2_TIN4               | E27                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[7]/GTM1_TGATE3/GTM2_TGATE4           | E28                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[8]/GTM1_TOUT3                        | H25                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[9]/GTM1_TIN4/GTM2_TIN3               | F27                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[10]/GTM1_TGATE4/GTM2_TGATE3          | K24                        | I/O      | OV <sub>DD</sub> |       |

| GPIO1[11]/GTM1_TOUT4/GTM2_TOUT3            | G26                        | I/O      | OV <sub>DD</sub> |       |

|                                            | USB Port 1                 |          | 4                |       |

| MPH1_D0_ENABLEN/DR_D0_ENABLEN              | C28                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D1_SER_TXD/DR_D1_SER_TXD              | F25                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D2_VMO_SE0/DR_D2_VMO_SE0              | B28                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D3_SPEED/DR_D3_SPEED                  | C27                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D4_DP/DR_D4_DP                        | D26                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D5_DM/DR_D5_DM                        | E25                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D6_SER_RCV/DR_D6_SER_RCV              | C26                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_D7_DRVVBUS/DR_D7_DRVVBUS              | D25                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_NXT/DR_SESS_VLD_NXT                   | B26                        | I        | OV <sub>DD</sub> |       |

| MPH1_DIR_DPPULLUP/<br>DR_XCVR_SEL_DPPULLUP | E24                        | I/O      | OV <sub>DD</sub> |       |

| MPH1_STP_SUSPEND/<br>DR_STP_SUSPEND        | A27                        | 0        | OV <sub>DD</sub> |       |

| MPH1_PWRFAULT/<br>DR_RX_ERROR_PWRFAULT     | C25                        | I        | OV <sub>DD</sub> |       |

| MPH1_PCTL0/DR_TX_VALID_PCTL0               | A26                        | 0        | OV <sub>DD</sub> |       |

| MPH1_PCTL1/DR_TX_VALIDH_PCTL1              | B25                        | 0        | OV <sub>DD</sub> |       |

| MPH1_CLK/DR_CLK                            | A25                        | I        | OV <sub>DD</sub> |       |

|                                            | USB Port 0                 |          |                  |       |

| MPH0_D0_ENABLEN/DR_D8_CHGVBUS              | D24                        | I/O      | OV <sub>DD</sub> |       |

| MPH0_D1_SER_TXD/DR_D9_DCHGVBUS             | C24                        | I/O      | OV <sub>DD</sub> |       |

#### Table 52. MPC8347E (PBGA) Pinout Listing (continued)

#### Clocking

Table 54 provides the operating frequencies for the MPC8347E TBGA under recommended operating conditions (see Table 2).

| Characteristic <sup>1</sup>                          | 400 MHz   | 533 MHz   | 667 MHz    | Unit |

|------------------------------------------------------|-----------|-----------|------------|------|

| e300 core frequency ( <i>core_clk</i> )              | 266–400   | 266–533   | 266–667    | MHz  |

| Coherent system bus frequency ( <i>csb_clk</i> )     | 100–266   | 100–266   | 100–333    | MHz  |

| DDR and memory bus frequency (MCLK) <sup>2</sup>     | 100–133   | 100–133   | 100–166.67 | MHz  |

| Local bus frequency (LCLK <i>n</i> ) <sup>3</sup>    | 16.67–133 | 16.67–133 | 16.67–133  | MHz  |

| PCI input frequency (CLKIN or PCI_CLK)               | 25–66     | 25–66     | 25–66      | MHz  |

| Security core maximum internal operating frequency   | 133       | 133       | 166        | MHz  |

| USB_DR, USB_MPH maximum internal operating frequency | 133       | 133       | 166        | MHz  |

#### Table 54. Operating Frequencies for TBGA

<sup>1</sup> The CLKIN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen so that the resulting *csb\_clk*, MCLK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[ENCCM], SCCR[USBDRCM], and SCCR[USBMPHCM] must be programmed so that the maximum internal operating frequency of the Security core and USB modules does not exceed the respective values listed in this table.

<sup>2</sup> The DDR data rate is 2x the DDR memory bus frequency.

<sup>3</sup> The local bus frequency is 1/2, 1/4, or 1/8 of the *lbiu\_clk* frequency (depending on LCCR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBIUCM]).

Table 55 provides the operating frequencies for the MPC8347E PBGA under recommended operating conditions.

| Characteristic <sup>1</sup>                          | 266 MHz | 333 MHz | 400 MHz | Unit |

|------------------------------------------------------|---------|---------|---------|------|

| e300 core frequency ( <i>core_clk</i> )              | 200–266 | 200–400 | MHz     |      |

| Coherent system bus frequency ( <i>csb_clk</i> )     |         | MHz     |         |      |

| Local bus frequency (LCLKn) <sup>2</sup>             |         | MHz     |         |      |

| PCI input frequency (CLKIN or PCI_CLK)               |         | MHz     |         |      |

| Security core maximum internal operating frequency   |         | MHz     |         |      |

| USB_DR, USB_MPH maximum internal operating frequency | 133     |         |         |      |

#### Table 55. Operating Frequencies for PBGA

<sup>1</sup> The CLKIN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen so that the resulting *csb\_clk*, MCLK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[ENCCM], SCCR[USBDRCM], and SCCR[USBMPHCM] must be programmed so that the maximum internal operating frequency of the Security core and USB modules does not exceed the respective values listed in this table.

<sup>2</sup> The local bus frequency is 1/2, 1/4, or 1/8 of the *lbiu\_clk* frequency (depending on LCCR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBIUCM]).

|                                        |      | ach alk                                               | Input Clock Frequency (MHz) <sup>2</sup> |                     |             |       |  |

|----------------------------------------|------|-------------------------------------------------------|------------------------------------------|---------------------|-------------|-------|--|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock<br>Ratio <sup>2</sup> | 16.67                                    | 25                  | 33.33       | 66.67 |  |

|                                        |      | Kallo                                                 | C                                        | s <i>b_clk</i> Freq | uency (MHz) |       |  |

| Low                                    | 0010 | 2 : 1                                                 |                                          |                     |             | 133   |  |

| Low                                    | 0011 | 3 : 1                                                 | -                                        |                     | 100         | 200   |  |

| Low                                    | 0100 | 4 : 1                                                 |                                          | 100                 | 133         | 266   |  |

| Low                                    | 0101 | 5 : 1                                                 |                                          | 125                 | 166         | 333   |  |

| Low                                    | 0110 | 6 : 1                                                 | 100                                      | 150                 | 200         |       |  |

| Low                                    | 0111 | 7:1                                                   | 116                                      | 175                 | 233         |       |  |

| Low                                    | 1000 | 8 : 1                                                 | 133                                      | 200                 | 266         |       |  |

| Low                                    | 1001 | 9 : 1                                                 | 150                                      | 225                 | 300         |       |  |

| Low                                    | 1010 | 10 : 1                                                | 166                                      | 250                 | 333         |       |  |

| Low                                    | 1011 | 11 : 1                                                | 183                                      | 275                 |             |       |  |

| Low                                    | 1100 | 12 : 1                                                | 200                                      | 300                 |             |       |  |

| Low                                    | 1101 | 13 : 1                                                | 216                                      | 325                 |             |       |  |

| Low                                    | 1110 | 14 : 1                                                | 233                                      |                     | -           |       |  |

| Low                                    | 1111 | 15 : 1                                                | 250                                      |                     |             |       |  |

| Low                                    | 0000 | 16 : 1                                                | 266                                      |                     |             |       |  |

| High                                   | 0010 | 2 : 1                                                 |                                          |                     |             | 133   |  |

| High                                   | 0011 | 3 : 1                                                 |                                          |                     | 100         | 200   |  |

| High                                   | 0100 | 4 : 1                                                 |                                          |                     | 133         | 266   |  |

| High                                   | 0101 | 5 : 1                                                 |                                          |                     | 166         | 333   |  |

| High                                   | 0110 | 6 : 1                                                 |                                          |                     | 200         |       |  |

| High                                   | 0111 | 7 : 1                                                 |                                          |                     | 233         |       |  |

| High                                   | 1000 | 8 : 1                                                 |                                          |                     |             |       |  |

Table 57. CSB Frequency Options for Host Mode

<sup>1</sup> CFG\_CLKIN\_DIV selects the ratio between CLKIN and PCI\_SYNC\_OUT.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode. DDR2 memory may be used at 133 MHz provided that the memory components are specified for operation at this frequency.

| Ref<br>No. <sup>1</sup> | RCWL |             | RCWL 400 MHz Device                          |                      | 533 MHz Device        |                                              |                      | 667 MHz Device        |                                              |                      |                       |

|-------------------------|------|-------------|----------------------------------------------|----------------------|-----------------------|----------------------------------------------|----------------------|-----------------------|----------------------------------------------|----------------------|-----------------------|

|                         | SPMF | CORE<br>PLL | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) |

|                         |      |             |                                              | 33 M                 |                       | PCI_CLK                                      | Options              | <u>I</u>              | Į                                            |                      | 1                     |

| 922                     | 1001 | 0100010     | _                                            | —                    | —                     | —                                            | _                    | f300                  | 33                                           | 300                  | 300                   |

| 723                     | 0111 | 0100011     | 33                                           | 233                  | 350                   | 33                                           | 233                  | 350                   | 33                                           | 233                  | 350                   |

| 604                     | 0110 | 0000100     | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   |

| 624                     | 0110 | 0100100     | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   |

| 803                     | 1000 | 0000011     | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   |

| 823                     | 1000 | 0100011     | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   |

| 903                     | 1001 | 0000011     | <u>_</u>                                     |                      |                       | 33                                           | 300                  | 450                   | 33                                           | 300                  | 450                   |

| 923                     | 1001 | 0100011     |                                              |                      |                       | 33                                           | 300                  | 450                   | 33                                           | 300                  | 450                   |

| 704                     | 0111 | 0000011     |                                              |                      |                       | 33                                           | 233                  | 466                   | 33                                           | 233                  | 466                   |

| 724                     | 0111 | 0100011     |                                              |                      |                       | 33                                           | 233                  | 466                   | 33                                           | 233                  | 466                   |

| A03                     | 1010 | 0000011     |                                              |                      |                       | 33                                           | 333                  | 500                   | 33                                           | 333                  | 500                   |

| 804                     | 1000 | 0000100     |                                              |                      |                       | 33                                           | 266                  | 533                   | 33                                           | 266                  | 533                   |

| 705                     | 0111 | 0000101     |                                              |                      |                       | —                                            |                      | 33                    | 233                                          | 583                  |                       |

| 606                     | 0110 | 0000110     |                                              | _                    |                       | —                                            |                      |                       | 33                                           | 200                  | 600                   |

| 904                     | 1001 | 0000100     |                                              | _                    |                       | _                                            |                      |                       | 33                                           | 300                  | 600                   |

| 805                     | 1000 | 0000101     |                                              | _                    |                       | —                                            |                      |                       | 33                                           | 266                  | 667                   |

| A04                     | 1010 | 0000100     |                                              | _                    |                       | —                                            |                      |                       | 33                                           | 333                  | 667                   |

|                         |      |             |                                              | 66 M                 |                       | /PCI_CLK                                     | Options              |                       |                                              |                      |                       |

| 304                     | 0011 | 0000100     | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   |

| 324                     | 0011 | 0100100     | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   |

| 403                     | 0100 | 0000011     | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   |

| 423                     | 0100 | 0100011     | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   |

| 305                     | 0011 | 0000101     |                                              | _                    |                       | 66                                           | 200                  | 500                   | 66                                           | 200                  | 500                   |

| 503                     | 0101 | 0000011     | —                                            |                      |                       | 66                                           | 333                  | 500                   | 66                                           | 333                  | 500                   |

| 404                     | 0100 | 0000100     | _                                            |                      |                       | 66                                           | 266                  | 533                   | 66                                           | 266                  | 533                   |

| 306                     | 0011 | 0000110     | —                                            |                      |                       | · _                                          |                      |                       | 66                                           | 200                  | 600                   |

| 405                     | 0100 | 0000101     | —                                            |                      |                       | _                                            |                      | 66                    | 266                                          | 667                  |                       |

| 504                     | 0101 | 0000100     |                                              |                      |                       |                                              |                      |                       | 66                                           | 333                  | 667                   |

<sup>1</sup> The PLL configuration reference number is the hexadecimal representation of RCWL, bits 4–15 associated with the SPMF and COREPLL settings given in the table.

<sup>2</sup> The input clock is CLKIN for PCI host mode or PCI\_CLK for PCI agent mode.

#### Thermal

required in the heat sink. Minimize the size of the clearance to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

$$T_J = T_C + (R_{\theta JC} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_C$  = case temperature of the package (°C)  $R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)  $P_D$  = power dissipation (W)

System Design Information

# 21 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8347E.

## 21.1 System Clocking

The MPC8347E includes two PLLs:

- 1. The platform PLL generates the platform clock from the externally supplied CLKIN input. The frequency ratio between the platform and CLKIN is selected using the platform PLL ratio configuration bits as described in Section 19.1, "System PLL Configuration."

- 2. The e300 core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 19.2, "Core PLL Configuration."

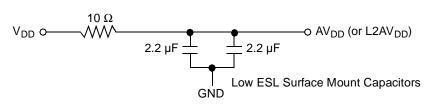

## 21.2 PLL Power Supply Filtering

Each PLL gets power through independent power supply pins (AV<sub>DD</sub>1, AV<sub>DD</sub>2, respectively). The AV<sub>DD</sub> level should always equal to  $V_{DD}$ , and preferably these voltages are derived directly from  $V_{DD}$  through a low frequency filter scheme.

There are a number of ways to provide power reliably to the PLLs, but the recommended solution is to provide four independent filter circuits as illustrated in Figure 42, one to each of the four  $AV_{DD}$  pins. Independent filters to each PLL reduce the opportunity to cause noise injection from one PLL to the other.

The circuit filters noise in the PLL resonant frequency range from 500 kHz to 10 MHz. It should be built with surface mount capacitors with minimum effective series inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

To minimize noise coupled from nearby circuits, each circuit should be placed as closely as possible to the specific  $AV_{DD}$  pin being supplied. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of package, without the inductance of vias.

Figure 42 shows the PLL power supply filter circuit.

Figure 42. PLL Power Supply Filter Circuit

## 21.3 Decoupling Recommendations

Due to large address and data buses and high operating frequencies, the MPC8347E can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8347E system, and the MPC8347E itself requires a clean, tightly regulated source of power. Therefore, the system designer should place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the MPC8347E. These capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and GND power planes in the PCB, with short traces to minimize inductance. Capacitors can be placed directly under the device using a standard escape pattern. Others can surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, distribute several bulk storage capacitors around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors are 100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

### 21.4 Connection Recommendations

To ensure reliable operation, connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ , and GND pins of the MPC8347E.

## 21.5 Output Buffer DC Impedance

The MPC8347E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 43). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .