#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Package / Case                          | -<br>672-LBGA       |

|-----------------------------------------|---------------------|

| Operating Temperature Security Features | 0°C ~ 105°C (TA)    |

| Voltage - I/O                           | 2.5V, 3.3V          |

| USB                                     | USB 2.0 + PHY (2)   |

| SATA                                    | -                   |

| Ethernet                                | 10/100/1000Mbps (2) |

| Display & Interface Controllers         | •                   |

| Graphics Acceleration                   | Νο                  |

| RAM Controllers                         | DDR                 |

| Co-Processors/DSP                       | •                   |

| Speed                                   | 533MHz              |

| Number of Cores/Bus Width               | 1 Core, 32-Bit      |

| Core Processor                          | PowerPC e300        |

| Product Status                          | Obsolete            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Clock Input Timing**

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8347E.

# 4.1 DC Electrical Characteristics

Table 7 provides the clock input (CLKIN/PCI\_SYNC\_IN) DC timing specifications for the MPC8347E.

| Parameter                 | Condition                                                                                                        | Symbol          | Min  | Мах                    | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage        | _                                                                                                                | V <sub>IH</sub> | 2.7  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage         | _                                                                                                                | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| CLKIN input current       | $0 V \le V_{IN} \le OV_{DD}$                                                                                     | I <sub>IN</sub> | —    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $\begin{array}{c} 0 \ V \leq V_{IN} \leq 0.5 \ V \ or \\ OV_{DD} - 0.5 \ V \leq V_{IN} \leq OV_{DD} \end{array}$ | I <sub>IN</sub> | —    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $0.5 \text{ V} \leq \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                        | I <sub>IN</sub> | —    | ±50                    | μA   |

Table 6. CLKIN DC Timing Specifications

# 4.2 AC Electrical Characteristics

The primary clock source for the MPC8347E can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. Table 7 provides the clock input (CLKIN/PCI\_CLK) AC timing specifications for the MPC8347E.

Table 7. CLKIN AC Timing Specifications

| Parameter/Condition              | Symbol                               | Min | Typical | Max  | Unit | Notes |

|----------------------------------|--------------------------------------|-----|---------|------|------|-------|

| CLKIN/PCI_CLK frequency          | <b>f</b> CLKIN                       | _   | —       | 66   | MHz  | 1, 6  |

| CLKIN/PCI_CLK cycle time         | t <sub>CLKIN</sub>                   | 15  | —       | _    | ns   | _     |

| CLKIN/PCI_CLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>    | 0.6 | 1.0     | 2.3  | ns   | 2     |

| CLKIN/PCI_CLK duty cycle         | t <sub>KHK</sub> /t <sub>CLKIN</sub> | 40  | —       | 60   | %    | 3     |

| CLKIN/PCI_CLK jitter             | _                                    |     | —       | ±150 | ps   | 4, 5  |

Notes:

1. **Caution:** The system, core, USB, security, and TSEC must not exceed their respective maximum or minimum operating frequencies.

2. Rise and fall times for CLKIN/PCI\_CLK are measured at 0.4 and 2.7 V.

3. Timing is guaranteed by design and characterization.

4. This represents the total input jitter—short term and long term—and is guaranteed by design.

5. The CLKIN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track CLKIN drivers with the specified jitter.

6. The Spread spectrum clocking. Is allowed with 1% input frequency down-spread at maximum 50KHz modulation rate regardless of input frequency.

#### DDR SDRAM

### Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter         | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|-------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end | t <sub>DDKLME</sub> | -0.9 | 0.3 | ns   | 7     |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. In the source synchronous mode, MCK/MCK can be shifted in 1/4 applied cycle increments through the clock control register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8349E PowerQUICC<sup>™</sup> II Pro Integrated Host Processor Family Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8347E.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the MPC8347E. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

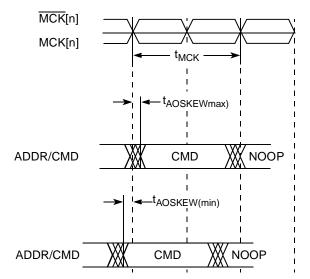

Figure 5 shows the DDR SDRAM output timing for address skew with respect to any MCK.

Figure 5. Timing Diagram for t<sub>AOSKEW</sub> Measurement

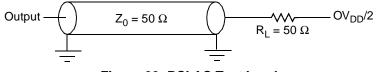

Figure 6 provides the AC test load for the DDR bus.

| Parameter                                            | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Output hold from local bus clock for LAD/LDP         | t <sub>LBKHOX2</sub> | 1   | —   | ns   | 3     |

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ</sub>  | —   | 3.8 | ns   | 8     |

Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to the rising edge of LSYNC\_IN.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.

- 6. t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin equals the load on the LAD output pins.

- 8. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

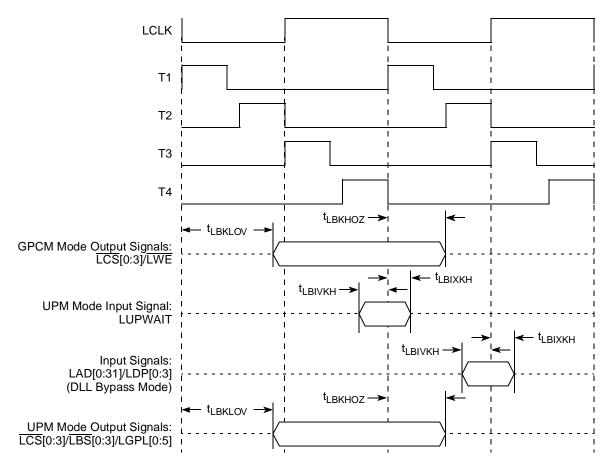

### Table 35. Local Bus General Timing Parameters—DLL Bypass<sup>9</sup>

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 15  | _   | ns   | 2     |

| Input setup to local bus clock                              | t <sub>LBIVKH</sub>  | 7   | _   | ns   | 3, 4  |

| Input hold from local bus clock                             | t <sub>lbixkh</sub>  | 1.0 | —   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | _   | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3   | —   | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 |     | ns   | 7     |

Local Bus

Figure 24. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (DLL Bypass Mode)

# 11 JTAG

JTAG

This section describes the DC and AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8347E

# **11.1 JTAG DC Electrical Characteristics**

Table 36 provides the DC electrical characteristics for the IEEE Std. 1149.1 (JTAG) interface of the MPC8347E.

| Characteristic      | Symbol          | Condition                 | Min                    | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------------------------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                           | OV <sub>DD</sub> - 0.3 | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                           | -0.3                   | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                           |                        | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4                    | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —                      | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —                      | 0.4                    | V    |

Table 36. JTAG interface DC Electrical Characteristics

# 11.2 JTAG AC Timing Specifications

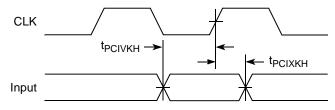

This section describes the AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8347E. Table 37 provides the JTAG AC timing specifications as defined in Figure 27 through Figure 30.

## Table 37. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                            | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Notes |

|------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation           | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  |       |

| JTAG external clock cycle time                       | t <sub>JTG</sub>                           | 30       | —        | ns   |       |

| JTAG external clock pulse width measured at 1.4 V    | t <sub>JTKHKL</sub>                        | 15       | —        | ns   |       |

| JTAG external clock rise and fall times              | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns   |       |

| TRST assert time                                     | t <sub>TRST</sub>                          | 25       | —        | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI  | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO            | <sup>t</sup> jtkldv<br><sup>t</sup> jtklov | 2<br>2   | 11<br>11 | ns   | 5     |

### Table 41. PCI AC Timing Specifications at 66 MHz<sup>1</sup> (continued)

| Parameter             | Symbol <sup>2</sup> | Min | Max | Unit | Notes |

|-----------------------|---------------------|-----|-----|------|-------|

| Input hold from clock | t <sub>PCIXKH</sub> | 0   | —   | ns   | 3, 5  |

Notes:

- 1. PCI timing depends on M66EN and the ratio between PCI1/PCI2. Refer to the PCI chapter of the reference manual for a description of M66EN.

- 2. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.</sub>

- 3. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

- 4. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Input timings are measured at the pin.

### Table 42 provides the PCI AC timing specifications at 33 MHz.

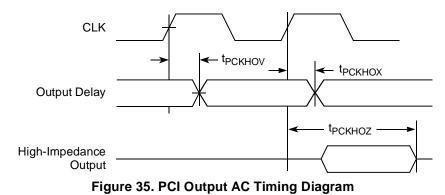

| Parameter                      | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|--------------------------------|---------------------|-----|-----|------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | _   | 11  | ns   | 2     |

| Output hold from clock         | <sup>t</sup> РСКНОХ | 2   | -   | ns   | 2     |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | _   | 14  | ns   | 2, 3  |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns   | 2, 4  |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   |     | ns   | 2, 4  |

#### Notes:

- The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

- 2. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

- 3. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

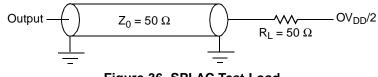

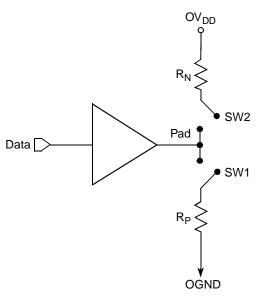

### Figure 33 provides the AC test load for PCI.

Figure 33. PCI AC Test Load

Figure 34 shows the PCI input AC timing diagram.

Figure 34. PCI Input AC Timing Diagram

Figure 35 shows the PCI output AC timing diagram.

MPC8347E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 11

# 15 GPIO

This section describes the DC and AC electrical specifications for the GPIO.

# **15.1 GPIO DC Electrical Characteristics**

Table 45 provides the DC electrical characteristics for the MPC8347E GPIO.

#### **Table 45. GPIO DC Electrical Characteristics**

| Characteristic      | Symbol          | Condition                 | Min  | Max                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                           | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                           | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                           |      | ±5                     | μΑ   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _    | 0.4                    | V    |

# 15.2 GPIO AC Timing Specifications

Table 46 provides the GPIO input and output AC timing specifications.

#### Table 46. GPIO Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

#### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by external synchronous logic. GPIO inputs must be valid for at least t<sub>PIWID</sub> ns to ensure proper operation. SPI

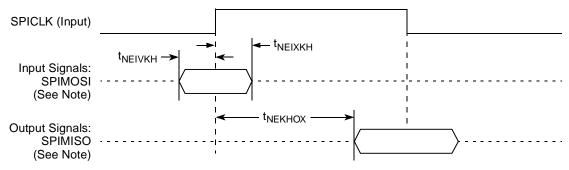

Figure 36 provides the AC test load for the SPI.

Figure 36. SPI AC Test Load

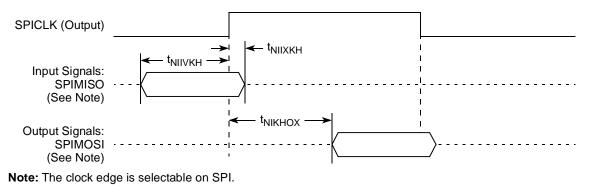

Figure 37 and Figure 38 represent the AC timings from Table 50. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 37 shows the SPI timings in slave mode (external clock).

Note: The clock edge is selectable on SPI.

Figure 38 shows the SPI timings in master mode (internal clock).

Figure 38. SPI AC Timing in Master Mode (Internal Clock) Diagram

| Signal                        | Package Pin Number                     | Pin Type | Power<br>Supply   | Notes |  |  |  |

|-------------------------------|----------------------------------------|----------|-------------------|-------|--|--|--|

| Gigabit Reference Clock       |                                        |          |                   |       |  |  |  |

| EC_GTX_CLK125                 | C8                                     | I        | LV <sub>DD1</sub> |       |  |  |  |

| Three-Sj                      | peed Ethernet Controller (Gigabit Eth  | ernet 1) |                   |       |  |  |  |

| TSEC1_COL/GPIO2[20]           | A17                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC1_CRS/GPIO2[21]           | F12                                    | I/O      | LV <sub>DD1</sub> |       |  |  |  |

| TSEC1_GTX_CLK                 | D10                                    | 0        | LV <sub>DD1</sub> | 3     |  |  |  |

| TSEC1_RX_CLK                  | A11                                    | I        | LV <sub>DD1</sub> |       |  |  |  |

| TSEC1_RX_DV                   | B11                                    | I        | LV <sub>DD1</sub> |       |  |  |  |

| TSEC1_RX_ER/GPIO2[26]         | B17                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC1_RXD[7:4]/GPIO2[22:25]   | B16, D16, E16, F16                     | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC1_RXD[3:0]                | E10, A8, F10, B8                       | I        | LV <sub>DD1</sub> |       |  |  |  |

| TSEC1_TX_CLK                  | D17                                    | I        | OV <sub>DD</sub>  |       |  |  |  |

| TSEC1_TXD[7:4]/GPIO2[27:30]   | A15, B15, A14, B14                     | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC1_TXD[3:0]                | A10, E11, B10, A9                      | 0        | LV <sub>DD1</sub> | 11    |  |  |  |

| TSEC1_TX_EN                   | B9                                     | 0        | LV <sub>DD1</sub> |       |  |  |  |

| TSEC1_TX_ER/GPIO2[31]         | A16                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| Three-S                       | peed Ethernet Controller (Gigabit Ethe | ernet 2) | •                 | •     |  |  |  |

| TSEC2_COL/GPIO1[21]           | C14                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_CRS/GPIO1[22]           | D6                                     | I/O      | LV <sub>DD2</sub> |       |  |  |  |

| TSEC2_GTX_CLK                 | A4                                     | 0        | LV <sub>DD2</sub> |       |  |  |  |

| TSEC2_RX_CLK                  | B4                                     | I        | LV <sub>DD2</sub> |       |  |  |  |

| TSEC2_RX_DV/GPIO1[23]         | E6                                     | I/O      | LV <sub>DD2</sub> |       |  |  |  |

| TSEC2_RXD[7:4]/GPIO1[26:29]   | A13, B13, C13, A12                     | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_RXD[3:0]/GPIO1[13:16]   | D7, A6, E8, B7                         | I/O      | LV <sub>DD2</sub> |       |  |  |  |

| TSEC2_RX_ER/GPIO1[25]         | D14                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_TXD[7]/GPIO1[31]        | B12                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_TXD[6]/DR_XCVR_TERM_SEL | C12                                    | 0        | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_TXD[5]/DR_UTMI_OPMODE1  | D12                                    | 0        | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_TXD[4]/DR_UTMI_OPMODE0  | E12                                    | 0        | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_TXD[3:0]/GPIO1[17:20]   | B5, A5, F8, B6                         | I/O      | LV <sub>DD2</sub> |       |  |  |  |

| TSEC2_TX_ER/GPIO1[24]         | F14                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| TSEC2_TX_EN/GPIO1[12]         | C5                                     | I/O      | LV <sub>DD2</sub> | 3     |  |  |  |

| TSEC2_TX_CLK/GPIO1[30]        | E14                                    | I/O      | OV <sub>DD</sub>  |       |  |  |  |

## Table 51. MPC8347E (TBGA) Pinout Listing (continued)

| Table 51. MPC8347E (TBGA) | Pinout Listing (continued) |

|---------------------------|----------------------------|

|---------------------------|----------------------------|

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pin Type                                                                                                        | Power<br>Supply    | Notes    |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|----------|

|                    | System Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                 |                    |          |

| PORESET            | C18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I                                                                                                               | OV <sub>DD</sub>   |          |

| HRESET             | B18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                                                                                                             | OV <sub>DD</sub>   | 1        |

| SRESET             | D18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                                                                                                             | OV <sub>DD</sub>   | 2        |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                 |                    | <u>.</u> |

| THERM0             | K32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I                                                                                                               |                    | 9        |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |                    |          |

| AV <sub>DD</sub> 1 | L31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Power for e300<br>PLL (1.2 V)                                                                                   | AV <sub>DD</sub> 1 |          |

| AV <sub>DD</sub> 2 | AP12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for<br>system PLL<br>(1.2 V)                                                                              | AV <sub>DD</sub> 2 |          |

| AV <sub>DD</sub> 3 | AE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Power for DDR<br>DLL (1.2 V)                                                                                    | AV <sub>DD</sub> 3 |          |

| AV <sub>DD</sub> 4 | AJ13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for LBIU<br>DLL (1.2 V)                                                                                   | AV <sub>DD</sub> 4 |          |

| GND                | <ul> <li>A1, A34, C1, C7, C10, C11, C15, C23,<br/>C25, C28, D1, D8, D20, D30, E7, E13,<br/>E15, E17, E18, E21, E23, E25, E32,<br/>F6, F19, F27, F30, F34, G31, H5, J4,<br/>J34, K30, L5, M2, M5, M30, M33, N3,<br/>N5, P30, R5, R32, T5, T30, U6, U29,<br/>U33, V2, V5, V30, W6, W30, Y30,<br/>AA2, AA30, AB2, AB6, AB30, AC3,<br/>AC6, AD31, AE5, AF2, AF5, AF31,<br/>AG30, AG31, AH4, AJ3, AJ19, AJ22,<br/>AK7, AK13, AK14, AK16, AK18, AK20,<br/>AK25, AK28, AL3, AL5, AL10, AL12,<br/>AL22, AL27, AM1, AM6, AM7, AN12,<br/>AN17, AN34, AP1, AP8, AP34</li> </ul> |                                                                                                                 |                    |          |

| GV <sub>DD</sub>   | A2, E2, G5, G6, J5, K4, K5, L4, N4, P5,<br>R6, T6, U5, V1, W5, Y5, AA4, AB3,<br>AC4, AD5, AF3, AG5, AH2, AH5, AH6,<br>AJ6, AK6, AK8, AK9, AL6                                                                                                                                                                                                                                                                                                                                                                                                                        | Power for DDR<br>DRAM I/O<br>voltage<br>(2.5 V)                                                                 | GV <sub>DD</sub>   |          |

| LV <sub>DD</sub> 1 | C9, D11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power for<br>three-speed<br>Ethernet #1<br>and for<br>Ethernet<br>management<br>interface I/O<br>(2.5 V, 3.3 V) | LV <sub>DD</sub> 1 |          |

## Table 52. MPC8347E (PBGA) Pinout Listing (continued)

| Signal                | Package Pin Number       | Pin Type                           | Power<br>Supply    | Notes |

|-----------------------|--------------------------|------------------------------------|--------------------|-------|

| SPIMISO               | C7                       | I/O                                | OV <sub>DD</sub>   |       |

| SPICLK                | B7                       | I/O                                | OV <sub>DD</sub>   |       |

| SPISEL                | A7                       | I                                  | OV <sub>DD</sub>   |       |

|                       | Clocks                   |                                    |                    |       |

| PCI_CLK_OUT[0:2]      | Y1, W3, W2               | 0                                  | OV <sub>DD</sub>   |       |

| PCI_CLK_OUT[3]/LCS[6] | W1                       | 0                                  | OV <sub>DD</sub>   |       |

| PCI_CLK_OUT[4]/LCS[7] | V3                       | 0                                  | OV <sub>DD</sub>   |       |

| PCI_SYNC_IN/PCI_CLOCK | U4                       | I                                  | OV <sub>DD</sub>   |       |

| PCI_SYNC_OUT          | U5                       | 0                                  | OV <sub>DD</sub>   | 3     |

| RTC/PIT_CLOCK         | E9                       | I                                  | $OV_{DD}$          |       |

| CLKIN                 | W5                       | I                                  | $OV_{DD}$          |       |

|                       | JTAG                     |                                    |                    | •     |

| тск                   | H27                      | I                                  | OV <sub>DD</sub>   |       |

| TDI                   | H28                      | I                                  | $OV_{DD}$          | 4     |

| TDO                   | M24                      | 0                                  | OV <sub>DD</sub>   | 3     |

| TMS                   | J27                      | I                                  | OV <sub>DD</sub>   | 4     |

| TRST                  | K26                      | I                                  | OV <sub>DD</sub>   | 4     |

|                       | Test                     |                                    |                    | •     |

| TEST                  | F28                      | I                                  | OV <sub>DD</sub>   | 6     |

| TEST_SEL              | ТЗ                       | I                                  | OV <sub>DD</sub>   | 6     |

|                       | РМС                      |                                    |                    | •     |

| QUIESCE               | K27                      | 0                                  | OV <sub>DD</sub>   |       |

|                       | System Control           |                                    |                    | •     |

| PORESET               | K28                      | I                                  | OV <sub>DD</sub>   |       |

| HRESET                | M25                      | I/O                                | OV <sub>DD</sub>   | 1     |

| SRESET                | L27                      | I/O                                | OV <sub>DD</sub>   | 2     |

|                       | Thermal Management       |                                    |                    |       |

| THERM0                | B15                      | I                                  | _                  | 8     |

|                       | Power and Ground Signals |                                    |                    |       |

| AV <sub>DD</sub> 1    | C15                      | Power for e300<br>PLL (1.2 V)      | AV <sub>DD</sub> 1 |       |

| AV <sub>DD</sub> 2    | U1                       | Power for<br>system PLL<br>(1.2 V) | AV <sub>DD</sub> 2 |       |

As shown in Figure 41, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create the coherent system bus clock ( $csb\_clk$ ), the internal clock for the DDR controller ( $ddr\_clk$ ), and the internal clock for the local bus interface unit ( $lbiu\_clk$ ).

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$csb\_clk = \{PCI\_SYNC\_IN \times (1 + CFG\_CLKIN\_DIV)\} \times SPMF$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 + CFG\_CLKIN\_DIV) is the CLKIN frequency.

The *csb\_clk* serves as the clock input to the e300 core. A second PLL inside the e300 core multiplies the *csb\_clk* frequency to create the internal clock for the e300 core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL), which is loaded at power-on reset or by one of the hard-coded reset options. See the chapter on reset, clocking, and initialization in the *MPC8349E Reference Manual* for more information on the clock subsystem.

The internal *ddr\_clk* frequency is determined by the following equation:

$ddr_clk = csb_clk \times (1 + RCWL[DDRCM])$

$ddr_clk$  is not the external memory bus frequency;  $ddr_clk$  passes through the DDR clock divider (÷2) to create the differential DDR memory bus clock outputs (MCK and MCK). However, the data rate is the same frequency as  $ddr_clk$ .

The internal *lbiu\_clk* frequency is determined by the following equation:

$lbiu_clk = csb_clk \times (1 + RCWL[LBIUCM])$

*lbiu\_clk* is not the external local bus frequency; *lbiu\_clk* passes through the LBIU clock divider to create the external local bus clock outputs (LSYNC\_OUT and LCLK[0:2]). The LBIU clock divider ratio is controlled by LCCR[CLKDIV].

In addition, some of the internal units may have to be shut off or operate at lower frequency than the  $csb\_clk$  frequency. Those units have a default clock ratio that can be configured by a memory-mapped register after the device exits reset. Table 53 specifies which units have a configurable clock frequency.

| Unit                     | Default<br>Frequency | Options                                   |

|--------------------------|----------------------|-------------------------------------------|

| TSEC1                    | csb_clk/3            | Off, csb_clk, csb_clk/2, csb_clk/3        |

| TSEC2, I <sup>2</sup> C1 | csb_clk/3            | Off, csb_clk, csb_clk/2, csb_clk/3        |

| Security core            | csb_clk/3            | Off, csb_clk, csb_clk/2, csb_clk/3        |

| USB DR, USB MPH          | csb_clk/3            | Off, csb_clk, csb_clk/2, <i>csb_clk/3</i> |

| PCI and DMA complex      | csb_clk              | Off, <i>csb_clk</i>                       |

Table 53. Configurable Clock Units

#### Clocking

Table 54 provides the operating frequencies for the MPC8347E TBGA under recommended operating conditions (see Table 2).

| Characteristic <sup>1</sup>                          | 400 MHz   | 533 MHz   | 667 MHz    | Unit |

|------------------------------------------------------|-----------|-----------|------------|------|

| e300 core frequency ( <i>core_clk</i> )              | 266–400   | 266–533   | 266–667    | MHz  |

| Coherent system bus frequency ( <i>csb_clk</i> )     | 100–266   | 100–266   | 100–333    | MHz  |

| DDR and memory bus frequency (MCLK) <sup>2</sup>     | 100–133   | 100–133   | 100–166.67 | MHz  |

| Local bus frequency (LCLK <i>n</i> ) <sup>3</sup>    | 16.67–133 | 16.67–133 | 16.67–133  | MHz  |

| PCI input frequency (CLKIN or PCI_CLK)               | 25–66     | 25–66     | 25–66      | MHz  |

| Security core maximum internal operating frequency   | 133       | 133       | 166        | MHz  |

| USB_DR, USB_MPH maximum internal operating frequency | 133       | 133       | 166        | MHz  |

### Table 54. Operating Frequencies for TBGA

<sup>1</sup> The CLKIN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen so that the resulting *csb\_clk*, MCLK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[ENCCM], SCCR[USBDRCM], and SCCR[USBMPHCM] must be programmed so that the maximum internal operating frequency of the Security core and USB modules does not exceed the respective values listed in this table.

<sup>2</sup> The DDR data rate is 2x the DDR memory bus frequency.

<sup>3</sup> The local bus frequency is 1/2, 1/4, or 1/8 of the *lbiu\_clk* frequency (depending on LCCR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBIUCM]).

Table 55 provides the operating frequencies for the MPC8347E PBGA under recommended operating conditions.

| Characteristic <sup>1</sup>                          | 266 MHz   | 333 MHz | 400 MHz | Unit |

|------------------------------------------------------|-----------|---------|---------|------|

| e300 core frequency ( <i>core_clk</i> )              | 200–266   | 200–333 | 200–400 | MHz  |

| Coherent system bus frequency ( <i>csb_clk</i> )     |           | MHz     |         |      |

| Local bus frequency (LCLKn) <sup>2</sup>             | 16.67–133 |         |         |      |

| PCI input frequency (CLKIN or PCI_CLK)               | 25–66     |         |         |      |

| Security core maximum internal operating frequency   | 133       |         |         | MHz  |

| USB_DR, USB_MPH maximum internal operating frequency | 133       |         |         | MHz  |

### Table 55. Operating Frequencies for PBGA

<sup>1</sup> The CLKIN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen so that the resulting *csb\_clk*, MCLK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[ENCCM], SCCR[USBDRCM], and SCCR[USBMPHCM] must be programmed so that the maximum internal operating frequency of the Security core and USB modules does not exceed the respective values listed in this table.

<sup>2</sup> The local bus frequency is 1/2, 1/4, or 1/8 of the *lbiu\_clk* frequency (depending on LCCR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBIUCM]).

# **19.1 System PLL Configuration**

The system PLL is controlled by the RCWL[SPMF] parameter. Table 56 shows the multiplication factor encodings for the system PLL.

| RCWL[SPMF] | System PLL Multiplication<br>Factor |

|------------|-------------------------------------|

| 0000       | × 16                                |

| 0001       | Reserved                            |

| 0010       | × 2                                 |

| 0011       | × 3                                 |

| 0100       | × 4                                 |

| 0101       | × 5                                 |

| 0110       | × 6                                 |

| 0111       | × 7                                 |

| 1000       | × 8                                 |

| 1001       | × 9                                 |

| 1010       | × 10                                |

| 1011       | × 11                                |

| 1100       | × 12                                |

| 1101       | × 13                                |

| 1110       | × 14                                |

| 1111       | × 15                                |

Table 56. System PLL Multiplication Factors

As described in Section 19, "Clocking," the LBIUCM, DDRCM, and SPMF parameters in the reset configuration word low and the CFG\_CLKIN\_DIV configuration input signal select the ratio between the primary clock input (CLKIN or PCI\_CLK) and the internal coherent system bus clock (*csb\_clk*). Table 57 and Table 58 show the expected frequency values for the CSB frequency for select *csb\_clk* to CLKIN/PCI\_SYNC\_IN ratios.

|                                        |      | ach alls                                              | Inpu  |                     |           | Hz) <sup>2</sup> |

|----------------------------------------|------|-------------------------------------------------------|-------|---------------------|-----------|------------------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock<br>Ratio <sup>2</sup> | 16.67 | 25                  | 33.33     | 66.67            |

|                                        |      | Kallo                                                 | C     | s <i>b_clk</i> Freq | uency (MH | z)               |

| Low                                    | 0010 | 2 : 1                                                 |       |                     |           | 133              |

| Low                                    | 0011 | 3 : 1                                                 | -     |                     | 100       | 200              |

| Low                                    | 0100 | 4 : 1                                                 | -     | 100                 | 133       | 266              |

| Low                                    | 0101 | 5 : 1                                                 | -     | 125                 | 166       | 333              |

| Low                                    | 0110 | 6 : 1                                                 | 100   | 150                 | 200       |                  |

| Low                                    | 0111 | 7:1                                                   | 116   | 175                 | 233       |                  |

| Low                                    | 1000 | 8:1                                                   | 133   | 200                 | 266       |                  |

| Low                                    | 1001 | 9:1                                                   | 150   | 225                 | 300       |                  |

| Low                                    | 1010 | 10 : 1                                                | 166   | 250                 | 333       |                  |

| Low                                    | 1011 | 11 : 1                                                | 183   | 275                 |           |                  |

| Low                                    | 1100 | 12 : 1                                                | 200   | 300                 |           |                  |

| Low                                    | 1101 | 13 : 1                                                | 216   | 325                 |           |                  |

| Low                                    | 1110 | 14 : 1                                                | 233   |                     |           |                  |

| Low                                    | 1111 | 15 : 1                                                | 250   |                     |           |                  |

| Low                                    | 0000 | 16 : 1                                                | 266   |                     |           |                  |

| High                                   | 0010 | 2 : 1                                                 |       |                     |           | 133              |

| High                                   | 0011 | 3 : 1                                                 |       |                     | 100       | 200              |

| High                                   | 0100 | 4 : 1                                                 |       |                     | 133       | 266              |

| High                                   | 0101 | 5 : 1                                                 |       |                     | 166       | 333              |

| High                                   | 0110 | 6 : 1                                                 |       |                     | 200       |                  |

| High                                   | 0111 | 7 : 1                                                 |       |                     | 233       |                  |

| High                                   | 1000 | 8 : 1                                                 |       |                     |           |                  |

Table 57. CSB Frequency Options for Host Mode

<sup>1</sup> CFG\_CLKIN\_DIV selects the ratio between CLKIN and PCI\_SYNC\_OUT.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode. DDR2 memory may be used at 133 MHz provided that the memory components are specified for operation at this frequency. where:

$R_{\theta IA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device-related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

The thermal performance of devices with heat sinks has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, air flow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

Table 63 and Table 64 show heat sink thermal resistance for TBGA and PBGA of the MPC8347E.

Table 63. Heat Sink and Thermal Resistance of MPC8347E (TBGA)

| Heat Sink Assuming Thermal Grease                                     | Air Flow           | 35 	imes 35  mm TBGA |

|-----------------------------------------------------------------------|--------------------|----------------------|

| neat Sink Assuming Merinal Grease                                     |                    | Thermal Resistance   |

| AAVID $30 \times 30 \times 9.4$ mm pin fin                            | Natural convection | 10                   |

| AAVID $30 \times 30 \times 9.4$ mm pin fin                            | 1 m/s              | 6.5                  |

| AAVID $30 \times 30 \times 9.4$ mm pin fin                            | 2 m/s              | 5.6                  |

| AAVID 31 $\times$ 35 $\times$ 23 mm pin fin                           | Natural convection | 8.4                  |

| AAVID 31 $\times$ 35 $\times$ 23 mm pin fin                           | 1 m/s              | 4.7                  |

| AAVID 31 $\times$ 35 $\times$ 23 mm pin fin                           | 2 m/s              | 4                    |

| Wakefield, $53 \times 53 \times 25$ mm pin fin                        | Natural convection | 5.7                  |

| Wakefield, $53 \times 53 \times 25$ mm pin fin                        | 1 m/s              | 3.5                  |

| Wakefield, $53 \times 53 \times 25$ mm pin fin                        | 2 m/s              | 2.7                  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion            | Natural convection | 6.7                  |

| MEI, 75 $\times$ 85 $\times$ 12 no adjacent board, extrusion          | 1 m/s              | 4.1                  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion            | 2 m/s              | 2.8                  |

| MEI, 75 $\times$ 85 $\times$ 12 mm, adjacent board, 40 mm side bypass | 1 m/s              | 3.1                  |

#### Table 64. Heat Sink and Thermal Resistance of MPC8347E (PBGA)

| Heat Sink Assuming Thermal Grease          | Air Flow           | $29 \times 29 \text{ mm PBGA}$ |  |

|--------------------------------------------|--------------------|--------------------------------|--|

| Treat onic Assuming Thermal Orease         | All How            | Thermal Resistance             |  |

| AAVID $30 \times 30 \times 9.4$ mm pin fin | Natural convection | 13.5                           |  |

| AAVID $30 \times 30 \times 9.4$ mm pin fin | 1 m/s              | 9.6                            |  |

|          | Tyco Electronics<br>Chip Coolers <sup>TM</sup><br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com         | 800-522-2800 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|--------------|

|          | Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                             | 603-635-5102 |

| Interfac | ce material vendors include the following:                                                                                            |              |

|          | Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01801                                                                                  | 781-935-4850 |

|          | Internet: www.chomerics.com                                                                                                           |              |

|          | Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>P.O. Box 994<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

|          | Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                        | 888-642-7674 |

|          | The Bergquist Company<br>18930 West 78th St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                            | 800-347-4572 |

# 20.3 Heat Sink Attachment

When heat sinks are attached, an interface material is required, preferably thermal grease and a spring clip. The spring clip should connect to the printed-circuit board, either to the board itself, to hooks soldered to the board, or to a plastic stiffener. Avoid attachment forces that can lift the edge of the package or peel the package from the board. Such peeling forces reduce the solder joint lifetime of the package. The recommended maximum force on the top of the package is 10 lb force (4.5 kg force). Any adhesive attachment should attach to painted or plastic surfaces, and its performance should be verified under the application requirements.

## 20.3.1 Experimental Determination of the Junction Temperature with a Heat Sink

When a heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally

#### System Design Information

Figure 43. Driver Impedance Measurement

Two measurements give the value of this resistance and the strength of the driver current source. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = (1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

Table 65 summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet,<br>DUART, Control,<br>Configuration, Power<br>Management | PCI Signals<br>(Not Including PCI<br>Output Clocks) | PCI Output Clocks<br>(Including<br>PCI_SYNC_OUT) | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| R <sub>P</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| Differential   | NA                                                                            | NA                                                  | NA                                               | NA        | Z <sub>DIFF</sub> | Ω    |

**Table 65. Impedance Characteristics**

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

# 21.6 Configuration Pin Multiplexing

The MPC8347E power-on configuration options can be set through external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see the customer-visible configuration pins). These pins are used as output only pins in normal operation.

However, while HRESET is asserted, these pins are treated as inputs, and the value on these pins is latched when PORESET deasserts. Then the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8        | 2/2007  | <ul> <li>Page 1, updated first paragraph to reflect PowerQUICC II information. Updated note after second paragraph.</li> <li>In the features list in Section 1, "Overview," corrected DDR data rate to show:</li> <li>266 MHz for PBGA parts for all silicon revisions</li> <li>333 MHz for DDR for TBGA parts for silicon Rev. 1.x</li> </ul>                                                                                                           |  |

|          |         | In Table 5, "MPC8347E Typical I/O Power Dissipation," added GV <sub>DD</sub> 1.8-V values for DDR2; added table footnote to designate rates that apply only to the TBGA package.<br>In Figure 43, "JTAG Interface Connection," updated with new figure.                                                                                                                                                                                                  |  |

|          |         | In Section 23, "Ordering Information," replicated note from document introduction.                                                                                                                                                                                                                                                                                                                                                                       |  |

|          |         | In Section 23.1, "Part Numbers Fully Addressed by This Document," replaced third sentence of first paragraph directing customer to product summary page for available frequency configuration parts. Updated back page information.                                                                                                                                                                                                                      |  |

| 7        | 8/2006  | Changed all references to revision 2.0 silicon to revision 3.0 silicon.<br>Changed V <sub>IH</sub> minimum value in Table 36, "JTAG Interface DC Electrical Characteristics," to                                                                                                                                                                                                                                                                         |  |

|          |         | OV <sub>DD</sub> – 0.3.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|          |         | In Table 60, "Suggested PLL Configurations," deleted reference-number rows 902 and 703.                                                                                                                                                                                                                                                                                                                                                                  |  |

| 6        | 3/2006  | Section 2, "Electrical Characteristics," moved to second section and all other section, table, and figure numbering change accordingly.<br>Table 7, "CLKIN AC Timing Specifications:" Changed max rise and fall time from 1.2 to 2.3.<br>Table 22, "GMII Receive AC Timing Specifications:" Changed min t <sub>TTKHDX</sub> from 0.5 to 1.0.<br>Table 30, "MII Management AC Timing Specifications:" Changed max value of t <sub>MDKHDX</sub> from 70 to |  |

|          |         | <ul> <li>170.</li> <li>Table 34, "Local Bus General Timing Parameters—DLL on:" Changed min t<sub>LBIVKH2</sub> from 1.7 to 2.2.</li> <li>Table 36, "JTAG interface DC Electrical Characteristics:" Changed V<sub>IH</sub> input high voltage min to 2.0.</li> <li>Table 54, "Operating Frequencies for TBGA:"</li> </ul>                                                                                                                                 |  |

|          |         | <ul> <li>Updated TBD values.</li> <li>Changed maximum coherent system bus frequency for TBGA 667-MHz device to 333 MHz.<br/>Table 55, "Operating Frequencies for PBGA:"</li> </ul>                                                                                                                                                                                                                                                                       |  |

|          |         | <ul> <li>Updated TBD values.</li> <li>Changed PBGA maximum coherent system bus frequency to 266 MHz, and maximum DDR memory bus frequency to 133 MHz.</li> <li>Table 60, "Suggested PLL Configurations": Removed some values from suggested PLL</li> </ul>                                                                                                                                                                                               |  |

|          |         | configurations for reference numbers 902, 922, 903, and 923.                                                                                                                                                                                                                                                                                                                                                                                             |  |

|          |         | Table 67, "Part Numbering Nomenclature": Updated TBD values in note 1.<br>Added Table 68, "SVR Settings."<br>Added Section 23.2, "Part Marking."                                                                                                                                                                                                                                                                                                         |  |

| 5        | 10/2005 | In Table 57, updated AAVID 30x30x9.4 mm Pin Fin (natural convection) junction-to-ambient thermal resistance, from 11 to 10.                                                                                                                                                                                                                                                                                                                              |  |

| 4        | 9/2005  | Added Table 2, "MPC8347E Typical I/O Power Dissipation."                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 3        | 8/2005  | Table 1: Updated values for power dissipation that were TBD in Revision 2.                                                                                                                                                                                                                                                                                                                                                                               |  |

| 2        | 5/2005  | Table 1: Typical values for power dissipation are changed to TBD.         Table 48: Footnote numbering was wrong. THERM0 should have footnote 9 instead of 8.                                                                                                                                                                                                                                                                                            |  |

#### Table 66. Document Revision History (continued)