# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 51                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 16K x 8                                                                      |

| RAM Size                   | 80K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152ret6        |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | 3.16                 | Timers                                                                                                                      | and watchdogs                                                                                                                                                                                                                                                                                                                                                  | 28                                                                                        |

|--------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|        |                      | 3.16.1                                                                                                                      | General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11)                                                                                                                                                                                                                                                                                         | . 28                                                                                      |

|        |                      | 3.16.2                                                                                                                      | Basic timers (TIM6 and TIM7)                                                                                                                                                                                                                                                                                                                                   | . 29                                                                                      |

|        |                      | 3.16.3                                                                                                                      | SysTick timer                                                                                                                                                                                                                                                                                                                                                  | . 29                                                                                      |

|        |                      | 3.16.4                                                                                                                      | Independent watchdog (IWDG)                                                                                                                                                                                                                                                                                                                                    | . 29                                                                                      |

|        |                      | 3.16.5                                                                                                                      | Window watchdog (WWDG)                                                                                                                                                                                                                                                                                                                                         | . 29                                                                                      |

|        | 3.17                 | Commu                                                                                                                       | inication interfaces                                                                                                                                                                                                                                                                                                                                           | 29                                                                                        |

|        |                      | 3.17.1                                                                                                                      | I <sup>2</sup> C bus                                                                                                                                                                                                                                                                                                                                           | . 29                                                                                      |

|        |                      | 3.17.2                                                                                                                      | Universal synchronous/asynchronous receiver transmitter (USART) .                                                                                                                                                                                                                                                                                              | . 29                                                                                      |

|        |                      | 3.17.3                                                                                                                      | Serial peripheral interface (SPI)                                                                                                                                                                                                                                                                                                                              | . 30                                                                                      |

|        |                      | 3.17.4                                                                                                                      | Inter-integrated sound (I2S)                                                                                                                                                                                                                                                                                                                                   | . 30                                                                                      |

|        |                      | 3.17.5                                                                                                                      | Universal serial bus (USB)                                                                                                                                                                                                                                                                                                                                     | . 30                                                                                      |

|        | 3.18                 | CRC (c                                                                                                                      | yclic redundancy check) calculation unit                                                                                                                                                                                                                                                                                                                       | 30                                                                                        |

|        | 3.19                 | Develo                                                                                                                      | oment support                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                        |

|        |                      | 3.19.1                                                                                                                      | Serial wire JTAG debug port (SWJ-DP)                                                                                                                                                                                                                                                                                                                           | . 31                                                                                      |

|        |                      | 3.19.2                                                                                                                      | Embedded Trace Macrocell™                                                                                                                                                                                                                                                                                                                                      | . 31                                                                                      |

| 4      | Din d                | occrinti                                                                                                                    | ons                                                                                                                                                                                                                                                                                                                                                            | 32                                                                                        |

| 4      | F III U              | escripti                                                                                                                    | 0115                                                                                                                                                                                                                                                                                                                                                           | 02                                                                                        |

| 4<br>5 |                      |                                                                                                                             | oping                                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

| 5      | Mem                  | ory map                                                                                                                     | oping                                                                                                                                                                                                                                                                                                                                                          | 55                                                                                        |

|        | Mem<br>Elect         | ory map<br>rical ch                                                                                                         | oping                                                                                                                                                                                                                                                                                                                                                          | 55<br>56                                                                                  |

| 5      | Mem                  | ory map<br>rical ch<br>Parame                                                                                               | aracteristics                                                                                                                                                                                                                                                                                                                                                  | <b>55</b><br><b>56</b><br>56                                                              |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1                                                                                      | oping         aracteristics         eter conditions         Minimum and maximum values                                                                                                                                                                                                                                                                         | <b>55</b><br><b>56</b><br>. 56                                                            |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2                                                                             | aracteristics         eter conditions         Minimum and maximum values         Typical values                                                                                                                                                                                                                                                                | <b>55</b><br><b>56</b><br>56<br>. 56<br>. 56                                              |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3                                                                    | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves                                                                                                                                                                                                                                         | <b>55</b><br><b>56</b><br>. 56<br>. 56<br>. 56                                            |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                           | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor                                                                                                                                                                                                               | <b>55</b><br><b>56</b><br>56<br>56<br>56<br>56<br>56<br>56                                |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                  | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage                                                                                                                                                                                     | <b>55</b><br><b>56</b><br>. 56<br>. 56<br>. 56<br>. 56<br>. 56                            |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                         | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme                                                                                                                                                         | <b>55</b><br><b>56</b><br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>56                    |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7                                | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme                                                                                                                | <b>55</b><br><b>56</b><br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>58        |

| 5      | Memo<br>Elect<br>6.1 | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                         | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme                                                                                                                                                         | <b>55</b><br><b>56</b><br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>58        |

| 5      | Mem<br>Elect         | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8                       | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme                                                                                                                | <b>55</b><br><b>56</b><br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>58<br>58  |

| 5      | Memo<br>Elect<br>6.1 | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut            | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical values         Dading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement                                                                         | <b>55</b><br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>58<br>58<br>59               |

| 5      | Memo<br>Elect<br>6.1 | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut            | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement         e maximum ratings                                              | <b>55</b><br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>58<br>58<br>59<br>60         |

| 5      | Memo<br>Elect<br>6.1 | ory map<br>rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operati | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement         e maximum ratings         ng conditions | <b>55</b><br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>58<br>59<br>60<br>60<br>60<br>. 61 |

| Table 47. | I <sup>2</sup> C characteristics                                                |

|-----------|---------------------------------------------------------------------------------|

| Table 48. | SCL frequency (f <sub>PCI K1</sub> = 32 MHz, V <sub>DD</sub> = VDD_I2C = 3.3 V) |

| Table 49. | SPI characteristics                                                             |

| Table 50. | USB startup time                                                                |

| Table 51. | USB DC electrical characteristics                                               |

| Table 52. | USB: full speed electrical characteristics                                      |

| Table 53. | I2S characteristics                                                             |

| Table 54. | ADC clock frequency                                                             |

| Table 55. | ADC characteristics                                                             |

| Table 56. | ADC accuracy                                                                    |

| Table 57. | Maximum source impedance R <sub>AIN</sub> max 106                               |

| Table 58. | DAC characteristics                                                             |

| Table 59. | Operational amplifier characteristics                                           |

| Table 60. | Temperature sensor calibration values                                           |

| Table 61. | Temperature sensor characteristics                                              |

| Table 62. | Comparator 1 characteristics                                                    |

| Table 63. | Comparator 2 characteristics                                                    |

| Table 64. | LCD controller characteristics                                                  |

| Table 65. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data 115  |

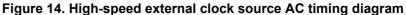

| Table 66. | LQPF100, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data 117  |

| Table 67. | LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical data 120     |

| Table 68. | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array             |

|           | package mechanical data                                                         |

| Table 69. | WLCSP104, 0.4 mm pitch wafer level chip scale package mechanical data 127       |

| Table 70. | WLCSP104, 0.4 mm pitch recommended PCB design rules                             |

| Table 71. | Thermal characteristics                                                         |

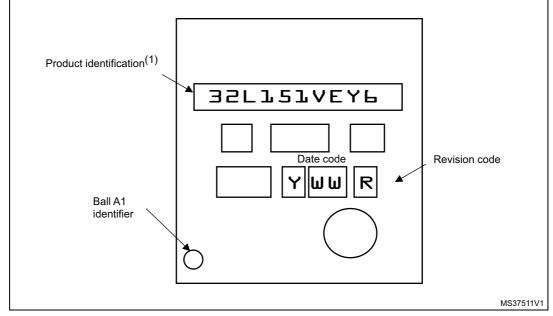

| Table 72. | STM32L151xE and STM32L152xE Ordering information scheme                         |

| Table 73. | Document revision history                                                       |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151xE and STM32L152xE ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontroller product line. STM32L151xE and STM32L152xE devices are microcontrollers with a Flash memory density of 512 Kbytes.

The ultra-low-power STM32L151xE and STM32L152xE family includes devices in 5 different package types: from 64 pins to 144 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151xE and STM32L152xE microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, wired and wireless sensors, video intercom

- Utility metering

This STM32L151xE and STM32L152xE datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038). The application note "Getting started with STM32L1xxxx hardware development" (AN3216) gives a hardware implementation overview. Both documents are available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 technical reference manual, available from the www.arm.com website. *Figure 1* shows the general block diagram of the device family.

## 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- System clock source: three different clock sources can be used to drive the master clock SYSCLK:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz).

When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

## 3.13 Ultra-low-power comparators and reference voltage

The STM32L151xE and STM32L152xE devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with fixed threshold

- One comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or a sub-multiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1 µA typical).

# 3.14 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

## 3.15 Touch sensing

The STM32L151xE and STM32L152xE devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 34 capacitive sensing channels distributed over 11 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. The capacitive sensing acquisition only requires few external components to operate. This acquisition is managed directly by the GPIOs, timers and analog I/O groups (see Section 3.14: System configuration controller and routing interface).

Reliable touch sensing functionality can be quickly and easily implemented using the free STM32L1xx STMTouch touch sensing firmware library.

# 3.16 Timers and watchdogs

The ultra-low-power STM32L151xE and STM32L152xE devices include seven generalpurpose timers, two basic timers, and two watchdog timers.

*Table 6* compares the features of the general-purpose and basic timers.

| Timer Counter resolution Counter type |        | Prescaler factor     | DMA<br>request<br>generation       | Capture/compare<br>channels | Complementary<br>outputs |    |  |  |

|---------------------------------------|--------|----------------------|------------------------------------|-----------------------------|--------------------------|----|--|--|

| TIM2,<br>TIM3,<br>TIM4                | 16-bit | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                         | 4                        | No |  |  |

| TIM5                                  | 32-bit | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                         | 4                        | No |  |  |

| TIM9                                  | 16-bit | Up, down,<br>up/down | Any integer between<br>1 and 65536 | No                          | 2                        | No |  |  |

| TIM10,<br>TIM11                       | 16-bit | Up                   | Any integer between<br>1 and 65536 | No                          | 1                        | No |  |  |

| TIM6,<br>TIM7                         | 16-bit | Up                   | Any integer between<br>1 and 65536 | Yes                         | 0                        | No |  |  |

Table 6. Timer feature comparison

# 3.16.1 General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11)

There are seven synchronizable general-purpose timers embedded in the STM32L151xE and STM32L152xE devices (see *Table 6* for differences).

## TIM2, TIM3, TIM4, TIM5

TIM2, TIM3, TIM4 are based on 16-bit auto-reload up/down counter. TIM5 is based on a 32bit auto-reload up/down counter. They include a 16-bit prescaler. They feature four independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures/output compares/PWMs on the largest packages.

TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

## TIM10, TIM11 and TIM9

TIM10 and TIM11 are based on a 16-bit auto-reload upcounter. TIM9 is based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers.

DocID025433 Rev 8

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

## 3.16.2 Basic timers (TIM6 and TIM7)

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

## 3.16.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches 0.

## 3.16.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

## 3.16.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.17 Communication interfaces

## 3.17.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7- and 10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

## 3.17.2 Universal synchronous/asynchronous receiver transmitter (USART)

The three USART and two UART interfaces are able to communicate at speeds of up to 4 Mbit/s. They support IrDA SIR ENDEC and have LIN Master/Slave capability. The three USARTs provide hardware management of the CTS and RTS signals and are ISO 7816 compliant.

All USART/UART interfaces can be served by the DMA controller.

|         | I        | Pins    |        |           |             |                         | Din Type<br>(1)<br>Pin Type<br>(1)<br>Bin Type<br>(1)<br>Entre<br>(after<br>reset) |                       | Pin functions                                         |                                           |  |  |  |

|---------|----------|---------|--------|-----------|-------------|-------------------------|------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------|-------------------------------------------|--|--|--|

| LQFP144 | UFBGA132 | LQFP100 | LQFP64 | WLCSP104  | Pin name    | Pin Type <sup>(1)</sup> |                                                                                    |                       | Alternate functions                                   | Additional<br>functions                   |  |  |  |

| 34      | L2       | 23      | 14     | K9        | PA0-WKUP1   | I/O                     | FT                                                                                 | PA0                   | TIM2_CH1_ETR/<br>TIM5_CH1/<br>USART2_CTS              | WKUP1/RTC_TA<br>MP2/ADC_IN0/<br>COMP1_INP |  |  |  |

| 35      | M2       | 24      | 15     | L9        | PA1         | I/O                     | FT                                                                                 | PA1                   | TIM2_CH2/TIM5_CH2/<br>USART2_RTS/<br>LCD_SEG0         | ADC_IN1/<br>COMP1_INP/<br>OPAMP1_VINP     |  |  |  |

| 36      | -        | 25      | 16     | J8        | PA2         | I/O                     | _                                                                                  |                       |                                                       | ADC_IN2/<br>COMP1_INP/<br>OPAMP1_VINM     |  |  |  |

| -       | K3       | -       | -      | -         | PA2         | I/O                     | FT                                                                                 | PA2                   | TIM2_CH3/TIM5_CH3/<br>TIM9_CH1/<br>USART2_TX/LCD_SEG1 | ADC_IN2/<br>COMP1_INP                     |  |  |  |

| -       | M3       | -       | -      |           | OPAMP1_VINM | I                       | тс                                                                                 | OPAMP1_<br>VINM       | -                                                     | -                                         |  |  |  |

| 37      | L3       | 26      | 17     | H7        | PA3         | I/O                     | TC PA3 TIM9_CH2                                                                    |                       | TIM2_CH4/TIM5_CH4/<br>TIM9_CH2/<br>USART2_RX/LCD_SEG2 | ADC_IN3/<br>COMP1_INP/<br>OPAMP1_VOUT     |  |  |  |

| 38      | -        | 27      | 18     | K8        | $V_{SS_4}$  | S                       | -                                                                                  | V <sub>SS_4</sub>     | -                                                     | -                                         |  |  |  |

| 39      | -        | 28      | 19     | L8,<br>M9 | $V_{DD_4}$  | S                       | -                                                                                  | $V_{DD_4}$            | -                                                     | -                                         |  |  |  |

| 40      | J4       | 29      | 20     | J7        | PA4         | I/O                     | тс                                                                                 | PA4                   | SPI1_NSS/SPI3_NSS/<br>I2S3_WS/<br>USART2_CK           | ADC_IN4/<br>DAC_OUT1/<br>COMP1_INP        |  |  |  |

| 41      | K4       | 30      | 21     | M8        | PA5         | I/O                     | тс                                                                                 | PA5                   | TIM2_CH1_ETR/<br>SPI1_SCK                             | ADC_IN5/<br>DAC_OUT2/<br>COMP1_INP        |  |  |  |

| 42      | L4       | 31      | 22     | H6        | PA6         | I/O                     | FT                                                                                 | —                     |                                                       | ADC_IN6/<br>COMP1_INP/<br>OPAMP2_VINP     |  |  |  |

| 43      | -        | 32      | 23     | K7        | PA7         | I/O                     | FT                                                                                 | T PA7 SPI1_MOSI/ COMI |                                                       | ADC_IN7/<br>COMP1_INP/<br>OPAMP2_VINM     |  |  |  |

| -       | J5       | -       | -      | -         | PA7         | I/O                     | FT                                                                                 | PA7                   | TIM3_CH2/TIM11_CH1/<br>SPI1_MOSI/<br>LCD_SEG4         | ADC_IN7/<br>COMP1_INP                     |  |  |  |

| Table 8. STM32L151xE and STM32L152xE | pin definitions | (continued) |

|--------------------------------------|-----------------|-------------|

|--------------------------------------|-----------------|-------------|

| Pin  |

|------|

| des  |

| crip |

| tio  |

| S    |

|           | 1      |          | Tal          | ble 9. Alte    | rnate fui     | nction inp           | ut/output   | t (continued   | l)          |   |        |    |          |              |

|-----------|--------|----------|--------------|----------------|---------------|----------------------|-------------|----------------|-------------|---|--------|----|----------|--------------|

|           |        |          |              |                | Digit         | al alternat          | e function  | number         |             |   |        |    |          |              |

|           | AFIO0  | AFIO1    | AFIO2        | AFIO3          | AFIO4         | AFIO5                | AFIO6       | AFIO7          | AFIO8       | • | AFIO11 | •  | AFIO14   | AFIO15       |

| Port name |        | I        |              | I              | 1             | Alterna              | te functior | 1              | I           | 1 |        | 11 |          | I            |

|           | SYSTEM | TIM2     | TIM3/4/<br>5 | TIM9/<br>10/11 | I2C1/2        | SPI1/2               | SPI3        | USART1/2/<br>3 | UART4/<br>5 | - | LCD    | -  | CPRI     | SYSTEM       |

| PB9       | -      | -        | TIM4_CH4     | TIM11_CH1      | I2C1_SDA      | -                    | -           | -              | -           | - | COM3   | -  | -        | EVENT<br>OUT |

| PB10      | -      | TIM2_CH3 | -            | -              | I2C2_SCL      | -                    | -           | USART3_TX      | -           | - | SEG10  | -  | -        | EVENT<br>OUT |

| PB11      | -      | TIM2_CH4 | -            | -              | I2C2_SDA      | -                    | -           | USART3_RX      | -           | - | SEG11  | -  | -        | EVENT<br>OUT |

| PB12      | -      | -        | -            | TIM10_CH1      | I2C2_SM<br>BA | SPI2_NSS<br>I2S2_WS  | -           | USART3_CK      | -           | - | SEG12  | -  | -        | EVENT<br>OUT |

| PB13      | -      | -        | -            | TIM9_CH1       | -             | SPI2_SCK<br>I2S2_CK  | -           | USART3_CTS     | -           | - | SEG13  | -  | -        | EVENT<br>OUT |

| PB14      | -      | -        | -            | TIM9_CH2       | -             | SPI2_MISO            | -           | USART3_RTS     | -           | - | SEG14  | -  | -        | EVENT<br>OUT |

| PB15      | -      | -        | -            | TIM11_CH1      | -             | SPI2_MOSI<br>I2S2_SD | -           | -              | -           | - | SEG15  | -  | -        | EVENT<br>OUT |

| PC0       | -      | -        | -            | -              | -             | -                    | -           | -              | -           | - | SEG18  | -  | TIMx_IC1 | EVENT<br>OUT |

| PC1       | -      | -        | -            | -              | -             | -                    | -           | -              | -           | - | SEG19  | -  | TIMx_IC2 | EVENT<br>OUT |

| PC2       | -      | -        | -            | -              | -             | -                    | -           | -              | -           | - | SEG20  | -  | TIMx_IC3 | EVENT<br>OUT |

| PC3       | -      | -        | -            | -              | -             | -                    | -           | -              | -           | - | SEG21  | -  | TIMx_IC4 | EVENT<br>OUT |

| PC4       | -      | -        | -            | -              | -             | -                    | -           | -              | -           | - | SEG22  | -  | TIMx_IC1 | EVENT<br>OUT |

| PC5       | -      | -        | -            | -              | -             | -                    | -           | -              | -           | - | SEG23  | -  | TIMx_IC2 | EVENT<br>OUT |

| PC6       | -      | -        | TIM3_CH1     | -              | -             | I2S2_MCK             | -           | -              | -           | - | SEG24  | -  | TIMx_IC3 | EVENT<br>OUT |

DocID025433 Rev 8

48/134

STM32L151xE STM32L152xE

| Symbol | Parameter                  | Conditions       | Min | Max | Unit |

|--------|----------------------------|------------------|-----|-----|------|

| TJ     | Junction temperature range | 6 suffix version | -40 | 105 | °C   |

|        | Sunction temperature range | 7 suffix version | -40 | 110 | C    |

#### Table 13. General operating conditions (continued)

1. When the ADC is used, refer to Table 55: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up .

3. To sustain a voltage higher than VDD+0.3V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 71: Thermal characteristics on page 129).

In low-power dissipation state, T<sub>A</sub> can be extended to -40°C to 105°C temperature range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 71: Thermal characteristics on page 129*).

## 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the conditions summarized in *Table 13*.

| Symbol                               | Parameter                      | Conditions                                   | Min  | Тур  | Max  | Unit  |  |

|--------------------------------------|--------------------------------|----------------------------------------------|------|------|------|-------|--|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                         | 0    | -    | ∞    |       |  |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector disabled                        | 0    | -    | 1000 | μs/V  |  |

| ٩٥٥٧                                 | V <sub>DD</sub> fall time rate | BOR detector enabled                         | 20   | -    | ∞    | μ3/ ν |  |

|                                      |                                | BOR detector disabled                        | 0    | -    | 1000 |       |  |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            |                                              | -    | 2    | 3.3  | ms    |  |

| 'RSTTEMPO` '                         |                                | $V_{DD}$ rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6  | 1115  |  |

| N .                                  | Power on/power down reset      | Falling edge                                 | 1    | 1.5  | 1.65 |       |  |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                  | 1.3  | 1.5  | 1.65 |       |  |

| V                                    | Brown-out reset threshold 0    | Falling edge                                 | 1.67 | 1.7  | 1.74 |       |  |

| V <sub>BOR0</sub>                    |                                | Rising edge                                  | 1.69 | 1.76 | 1.8  | v     |  |

| N/ -                                 | Brown-out reset threshold 1    | Falling edge                                 | 1.87 | 1.93 | 1.97 | v     |  |

| V <sub>BOR1</sub>                    |                                | Rising edge                                  | 1.96 | 2.03 | 2.07 |       |  |

| N .                                  | Brown-out reset threshold 2    | Falling edge                                 | 2.22 | 2.30 | 2.35 | ]     |  |

| V <sub>BOR2</sub>                    |                                | Rising edge                                  | 2.31 | 2.41 | 2.44 |       |  |

Table 14. Embedded reset and power control block characteristics

## 6.3.3 Embedded internal reference voltage

The parameters given in *Table 16* are based on characterization results, unless otherwise specified.

| Table 15. Embedde | ed internal reference voltage | calibration values |

|-------------------|-------------------------------|--------------------|

|                   | B i ti                        |                    |

| Calibration value name | Description                                                                         | Memory address            |

|------------------------|-------------------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 30 °C ±5 °C<br>V <sub>DDA</sub> = 3 V ±10 mV | 0x1FF8 00F8 - 0x1FF8 00F9 |

| Symbol                                  | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit               |

|-----------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------------------|

| V <sub>REFINT out</sub> <sup>(1)</sup>  | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +110 °C                                                      | 1.202 | 1.224 | 1.242 | V                  |

| I <sub>REFINT</sub>                     | Internal reference current consumption                                                       | -                                                                                       | -     | 1.4   | 2.3   | μA                 |

| T <sub>VREFINT</sub>                    | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms                 |

| V <sub>VREF_MEAS</sub>                  | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V                  |

| A <sub>VREF_MEAS</sub>                  | Accuracy of factory-measured V <sub>REF</sub> value <sup>(2)</sup>                           | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV                 |

| T <sub>Coeff</sub> <sup>(3)</sup>       | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +110 °C                                                       | -     | 25    | 100   | ppm/°<br>C         |

| A <sub>Coeff</sub> <sup>(3)</sup>       | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm                |

| V <sub>DDCoeff</sub> <sup>(3)</sup>     | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V              |

| T <sub>S_vrefint</sub> <sup>(3)</sup>   | ADC sampling time when reading the internal reference voltage                                | -                                                                                       | 4     | -     | -     | μs                 |

| T <sub>ADC_BUF</sub> <sup>(3)</sup>     | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs                 |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>     | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA                 |

| I <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output current (4)                                                                  | -                                                                                       | -     | -     | 1     | μA                 |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF                 |

| I <sub>LPBUF</sub> <sup>(3)</sup>       | Consumption of reference voltage buffer for VREF_OUT and COMP                                | -                                                                                       | -     | 730   | 1200  | nA                 |

| V <sub>REFINT_DIV1</sub> <sup>(3)</sup> | 1/4 reference voltage                                                                        | -                                                                                       | 24    | 25    | 26    | %                  |

| V <sub>REFINT_DIV2</sub> <sup>(3)</sup> | 1/2 reference voltage                                                                        | -                                                                                       | 49    | 50    | 51    | V <sub>REFIN</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup> | 3/4 reference voltage                                                                        | -                                                                                       | 74    | 75    | 76    | Т                  |

## Table 16. Embedded internal reference voltage

1. Guaranteed by test in production.

2. The internal  $V_{REF}$  value is individually measured in production and stored in dedicated EEPROM bytes.

3. Guaranteed by characterization results.

4. To guarantee less than 1% VREF\_OUT deviation.

#### DocID025433 Rev 8

| Peripheral |        | Туріса                                                    |                                                           |                                                           |                            |                      |

|------------|--------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|----------------------------|----------------------|

|            |        | Range 1,<br>V <sub>CORE</sub> =<br>1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =<br>1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =<br>1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and run | Unit                 |

|            | TIM2   | 12.0                                                      | 10.0                                                      | 8.0                                                       | 10.0                       |                      |

|            | TIM3   | 10.5                                                      | 8.8                                                       | 7.0                                                       | 8.8                        |                      |

|            | TIM4   | 10.4                                                      | 8.8                                                       | 7.0                                                       | 8.8                        |                      |

|            | TIM5   | 13.8                                                      | 11.5                                                      | 9.1                                                       | 11.5                       |                      |

|            | TIM6   | 3.9                                                       | 3.0                                                       | 2.5                                                       | 3.0                        |                      |

|            | TIM7   | 3.8                                                       | 3.3                                                       | 2.6                                                       | 3.3                        |                      |

|            | LCD    | 4.2                                                       | 3.6                                                       | 2.8                                                       | 3.6                        |                      |

|            | WWDG   | 2.9                                                       | 2.5                                                       | 2.1                                                       | 2.5                        |                      |

|            | SPI2   | 5.4                                                       | 4.4                                                       | 3.5                                                       | 4.4                        |                      |

| APB1       | SPI3   | 5.5                                                       | 4.6                                                       | 3.7                                                       | 4.6                        | µA/MHz               |

| AFDI       | USART2 | 7.6                                                       | 6.2                                                       | 4.9                                                       | 6.2                        | (f <sub>HCLK</sub> ) |

|            | USART3 | 7.6                                                       | 6.2                                                       | 5.0                                                       | 6.2                        |                      |

|            | USART4 | 7.3                                                       | 6.1                                                       | 4.8                                                       | 6.1                        |                      |

|            | USART5 | 7.6                                                       | 6.3                                                       | 5.0                                                       | 6.3                        |                      |

|            | I2C1   | 7.3                                                       | 6.1                                                       | 4.8                                                       | 6.1                        |                      |

|            | I2C2   | 7.2                                                       | 5.9                                                       | 4.7                                                       | 5.9                        |                      |

|            | USB    | 13.0                                                      | 11.2                                                      | 8.9                                                       | 11.2                       |                      |

|            | PWR    | 2.6                                                       | 2.3                                                       | 1.9                                                       | 2.3                        |                      |

|            | DAC    | 5.9                                                       | 5.0                                                       | 4.0                                                       | 5.0                        |                      |

|            | COMP   | 3.9                                                       | 3.3                                                       | 2.6                                                       | 3.3                        |                      |

Table 24. Peripheral current consumption<sup>(1)</sup>

- 3. Data based on a differential IDD measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

- Data based on a differential IDD measurement between DAC in reset configuration and continuous DAC conversion of VDD/2. DAC is in buffered mode, output is left floating.

- 5. Including supply current of internal reference voltage.

- 6 In Low-power sleep and run mode, the Flash memory must always be in power-down mode.

## 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under the conditions summarized in Table 13.

| Symbol                                                                         | Parameter                                                                            | Conditions                                                        | Тур     | Max <sup>(1)</sup> | Unit |  |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------|--------------------|------|--|

| t <sub>WUSLEEP</sub>                                                           | Wakeup from Sleep mode                                                               | f <sub>HCLK</sub> = 32 MHz                                        | 0.4     | -                  |      |  |

| +                                                                              | Wakeup from Low-power sleep                                                          | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                      | 46      | 3 -                |      |  |

| <sup>t</sup> wusleep_lp                                                        | mode, f <sub>HCLK</sub> = 262 kHz                                                    | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                 | 46      | -                  |      |  |

| Wakeup from Stop mode,<br>regulator in Run mode<br>ULP bit = 1 and FWU bit = 1 |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 8.2     | -                  |      |  |

|                                                                                |                                                                                      | $f_{HCLK} = f_{MSI} = 4.2 \text{ MHz}$<br>Voltage range 1 and 2   | 7.7 8.9 |                    |      |  |

|                                                                                | Wakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 8.2     | 13.1               | μs   |  |

| <sup>t</sup> WUSTOP                                                            |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 10.2    | 13.4               |      |  |

|                                                                                |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 16      | 20                 |      |  |

|                                                                                |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 31      | 37                 |      |  |

|                                                                                |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 57      | 66                 |      |  |

|                                                                                |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 112     | 123                |      |  |

|                                                                                |                                                                                      | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 221     | 236                |      |  |

| +                                                                              | Wakeup from Standby mode<br>ULP bit = 1 and FWU bit = 1                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 58      | 104                |      |  |

| <sup>t</sup> wustdby                                                           | Wakeup from Standby mode<br>FWU bit = 0                                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.6     | 3.25               | ms   |  |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization, unless otherwise specified

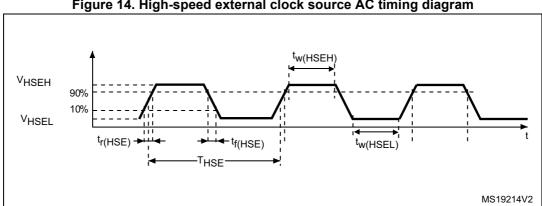

#### 6.3.6 **External clock source characteristics**

## High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.The external clock signal has to respect the I/O characteristics in Section 6.3.12. However, the recommended clock input waveform is shown in Figure 14.

| Symbol                                       | Parameter                           | Conditions                  | Min         | Тур | Max                | Unit |

|----------------------------------------------|-------------------------------------|-----------------------------|-------------|-----|--------------------|------|

| f                                            | User external clock source          | CSS is on or<br>PLL is used | 1           | 8   | 32                 | MHz  |

| f <sub>HSE_ext</sub> frequency               | CSS is off, PLL<br>not used         | 0                           | 8           | 32  | MHz                |      |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |                             | $0.7V_{DD}$ | -   | V <sub>DD</sub>    | v    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  |                             | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             | -                           | 12          | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |                             | -           | -   | 20                 | 113  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            |                             | -           | 2.6 | -                  | pF   |

| Table 26. High-speed external user clock characteristics <sup>(1)</sup> | Table 26. | Hiah-speed | external us | ser clock o | characteristics <sup>(1)</sup> |

|-------------------------------------------------------------------------|-----------|------------|-------------|-------------|--------------------------------|

|-------------------------------------------------------------------------|-----------|------------|-------------|-------------|--------------------------------|

1. Guaranteed by design.

## 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table* 37. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                        | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP144, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2    | 4B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP144, T <sub>A</sub> = +25<br>°C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

Table 37. EMS characteristics

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

## **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under the conditions summarized in *Table 13*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                        | Parameter Conditions       |                       | Max <sup>(2)</sup>    | Unit |  |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|-----------------------|-----------------------|------|--|

| _                                                                          |                                  | Master mode                | -                     | 16                    |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                     | 16                    | MHz  |  |

|                                                                            |                                  | Slave transmitter          | -                     | 12 <sup>(3)</sup>     |      |  |

| $t_{r(SCK)}^{(2)} t_{f(SCK)}^{(2)}$                                        | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                     | 6                     | ns   |  |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                    | 70                    | %    |  |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>    | -                     |      |  |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>    | -                     |      |  |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2-5 | t <sub>SCK</sub> /2+3 |      |  |