# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 83                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 16K × 8                                                                      |

| RAM Size                   | 80K × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 25x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152vet6        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 47. | I <sup>2</sup> C characteristics                                                |

|-----------|---------------------------------------------------------------------------------|

| Table 48. | SCL frequency (f <sub>PCI K1</sub> = 32 MHz, V <sub>DD</sub> = VDD_I2C = 3.3 V) |

| Table 49. | SPI characteristics                                                             |

| Table 50. | USB startup time                                                                |

| Table 51. | USB DC electrical characteristics                                               |

| Table 52. | USB: full speed electrical characteristics                                      |

| Table 53. | I2S characteristics                                                             |

| Table 54. | ADC clock frequency                                                             |

| Table 55. | ADC characteristics                                                             |

| Table 56. | ADC accuracy                                                                    |

| Table 57. | Maximum source impedance R <sub>AIN</sub> max 106                               |

| Table 58. | DAC characteristics                                                             |

| Table 59. | Operational amplifier characteristics                                           |

| Table 60. | Temperature sensor calibration values                                           |

| Table 61. | Temperature sensor characteristics                                              |

| Table 62. | Comparator 1 characteristics                                                    |

| Table 63. | Comparator 2 characteristics                                                    |

| Table 64. | LCD controller characteristics                                                  |

| Table 65. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data 115  |

| Table 66. | LQPF100, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data 117  |

| Table 67. | LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical data 120     |

| Table 68. | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array             |

|           | package mechanical data                                                         |

| Table 69. | WLCSP104, 0.4 mm pitch wafer level chip scale package mechanical data 127       |

| Table 70. | WLCSP104, 0.4 mm pitch recommended PCB design rules                             |

| Table 71. | Thermal characteristics                                                         |

| Table 72. | STM32L151xE and STM32L152xE Ordering information scheme                         |

| Table 73. | Document revision history                                                       |

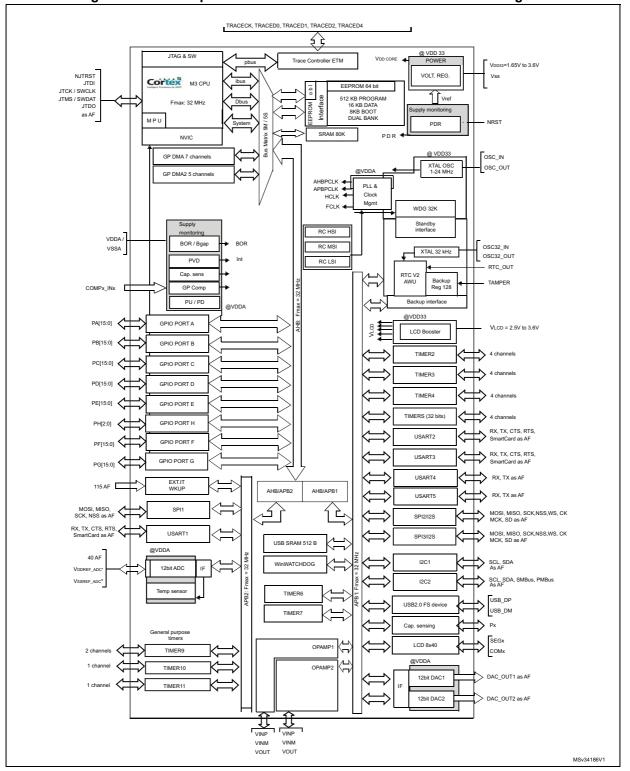

# 3 Functional overview

#### Figure 1. Ultra-low-power STM32L151xE and STM32L152xE block diagram

DocID025433 Rev 8

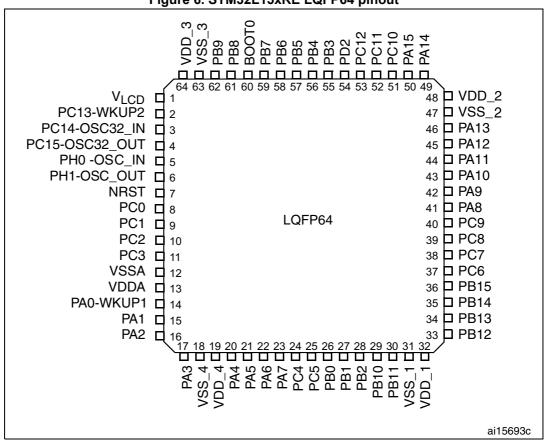

Figure 6. STM32L15xRE LQFP64 pinout

1. This figure shows the package top view.

|   | F       | igure <i>i</i> | . 31 101. | 52L15X |        | VLC3F        | 2104 b  | anout           |                  |

|---|---------|----------------|-----------|--------|--------|--------------|---------|-----------------|------------------|

|   | 1       | 2              | 3         | 4      | 5      | 6            | 7       | 8               | 9                |

| А | VSS_2   | PDO            | (PD4)     | (PD7)  | (PB4)  | (PB5)        | воото   | (PE1)           | VDD_3            |

| В | (PA15)  | PC12           | (PD5)     | PD6    | РВЗ    | (РВ7)        | PEO     | VDD_3           | (PE5)            |

| С | (DD_2)  | PC11           | (PD2)     | (PD3)  | (PB6)  | (PB9)        | (VSS_3) | (PE4)           | PC13<br>WKUP2    |

| D | (PH2)   | VSS_2          | (PA14)    | (PD1)  | PB8    | (PE2)        | (PE3)   | PC14<br>QSC3ZIN | PC15<br>OSC32OUT |

| E | PA11    | (PA12)         | (PA13)    | PC10   |        | PE6<br>WKUP3 | VLCD    | VSS_5           | VDD_5            |

| F | (PA9)   | PA10           | PA8       | PC9    |        | PCO          | NRST    | PHO<br>OSCIN    | PH1<br>OSCOUT    |

| G | PC7     | PC8            | (PD15)    | (PD11) |        | VDDA         | VREF+   | PC3             | PC2              |

| н | PC6     | (PD13)         | (PD12)    | PD8    |        | (PA6)        | (PA3)   | VREF-           | PC1              |

| J | (PD14)  | PD9            | (PB13)    | (PB12) | PE10   | РВО          | (PA4)   | (PA2)           | VSSA             |

| к | (PD10)  | (PB15)         |           | (PE15) | (PE13) | (PB1)        | (PA7)   | VSS_4           | PA0<br>WKUP1     |

| L | (PB14)  | (VSS_1)        | (PB11)    | (PE14) | (PE11) | PE7          | PC4     | VDD_4           | PA1              |

| М | (VSS_1) | (PB10)         | (PE12)    | PE9    | (PE8)  | (PB2)        | PC5     | (PA5)           | VDD_4            |

| Ĺ |         |                |           |        |        |              |         |                 |                  |

|   |         |                |           |        |        |              |         |                 |                  |

Figure 7. STM32L15xVEY WLCSP104 ballout

1. This figure shows the package top view.

Table 7. Legend/abbreviations used in the pinout table

| Name          | Abbreviation | Definition                                                                                                                           |  |  |  |  |

|---------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name      |              | Inless otherwise specified in brackets below the pin name, the pin function uring and after reset is the same as the actual pin name |  |  |  |  |

|               | S            | Supply pin                                                                                                                           |  |  |  |  |

| Pin type      | I            | Input only pin                                                                                                                       |  |  |  |  |

|               | I/O          | Input / output pin                                                                                                                   |  |  |  |  |

|               | FT           | 5 V tolerant I/O                                                                                                                     |  |  |  |  |

| I/O structure | TC           | Standard 3.3 V I/O                                                                                                                   |  |  |  |  |

|               | В            | Dedicated BOOT0 pin                                                                                                                  |  |  |  |  |

|               | RST          | Bidirectional reset pin with embedded weak pull-up resistor                                                                          |  |  |  |  |

DocID025433 Rev 8

| S         |

|-----------|

| -         |

|           |

| <u> </u>  |

| ω         |

| Ň         |

| ř         |

| <u>``</u> |

| (1)       |

| ~         |

| 5         |

| <u> </u>  |

| Π         |

| 10        |

| S         |

| _         |

| Ż         |

| $\geq$    |

| ω         |

| N         |

|           |

| <u>``</u> |

| (Th       |

| Ň         |

| 5         |

| <u> </u>  |

| П         |

|                   |        |       |              |                | Digi   | tal alternat        | e function           | number         |             |   |                          |   |          |              |

|-------------------|--------|-------|--------------|----------------|--------|---------------------|----------------------|----------------|-------------|---|--------------------------|---|----------|--------------|

|                   | AFIO0  | AFIO1 | AFIO2        | AFIO3          | AFIO4  | AFIO5               | AFIO6                | AFIO7          | AFIO8       |   | AFIO11                   |   | AFIO14   | AFIO15       |

| Port name         |        |       |              |                |        | Alterna             | te functior          | 1              |             |   |                          |   |          | <u>I</u>     |

|                   | SYSTEM | TIM2  | TIM3/4/<br>5 | TIM9/<br>10/11 | I2C1/2 | SPI1/2              | SPI3                 | USART1/2/<br>3 | UART4/<br>5 | - | LCD                      | - | CPRI     | SYSTEM       |

| PC7               | -      | -     | TIM3_CH2     | -              | -      | -                   | I2S3_MCK             | -              | -           | - | SEG25                    | - | TIMx_IC4 | EVENT<br>OUT |

| PC8               | -      | -     | TIM3_CH3     | -              | -      | -                   | -                    | -              | -           | - | SEG26                    | - | TIMx_IC1 | EVENT<br>OUT |

| PC9               | -      | -     | TIM3_CH4     | -              | -      | -                   | -                    | -              | -           | - | SEG27                    | - | TIMx_IC2 | EVENT<br>OUT |

| PC10              | -      | -     | -            | -              | -      | -                   | SPI3_SCK<br>I2S3_CK  | USART3_TX      | UART4_TX    | - | COM4/<br>SEG28/<br>SEG40 | - | TIMx_IC3 | EVENT<br>OUT |

| PC11              | -      | -     | -            | -              | -      | -                   | SPI3_MISO            | USART3_RX      | UART4_RX    | - | COM5/<br>SEG29<br>/SEG41 | - | TIMx_IC4 | EVENT<br>OUT |

| PC12              | -      | -     | -            | -              | -      | -                   | SPI3_MOSI<br>I2S3_SD | USART3_CK      | UART5_TX    | - | COM6/<br>SEG30/<br>SEG42 | - | TIMx_IC1 | EVENT<br>OUT |

| PC13-WKUP2        | -      | -     | -            | -              | -      | -                   | -                    | -              | -           | - | -                        | - | TIMx_IC2 | EVENT<br>OUT |

| PC14<br>OSC32_IN  | -      | -     | -            | -              | -      | -                   | -                    | -              | -           | - | -                        | - | TIMx_IC3 | EVENT<br>OUT |

| PC15<br>OSC32_OUT | -      | -     | -            | -              | -      | -                   | -                    | -              | -           | - | -                        | - | TIMx_IC4 | EVENT<br>OUT |

| PD0               | -      | -     | -            | TIM9_CH1       | -      | SPI2_NSS<br>I2S2_WS | -                    | -              | -           | - | -                        | - | TIMx_IC1 | EVENT<br>OUT |

| PD1               | -      | -     | -            | -              | -      | SPI2 SCK<br>I2S2_CK | -                    | -              | -           | - | -                        | - | TIMx_IC2 | EVENT<br>OUT |

| PD2               | -      | -     | TIM3_ETR     | -              | -      | -                   | -                    | -              | UART5_RX    | - | COM7/<br>SEG31/<br>SEG43 | - | TIMx_IC3 | EVENT<br>OUT |

| PD3               | -      | -     | -            | -              | -      | SPI2_MISO           | -                    | USART2_CTS     | _           | - | -                        | - | TIMx_IC4 | EVENT<br>OUT |

DocID025433 Rev 8

577

49/134

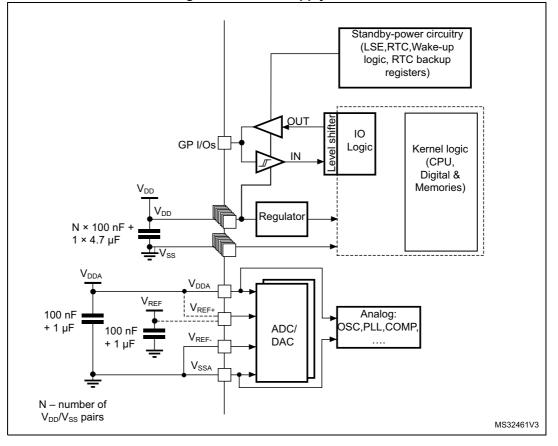

## 6.1.6 Power supply scheme

Figure 11. Power supply scheme

- Positive current injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 10* for maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 10: Voltage characteristics* for the maximum allowed input voltage values.

- 6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

#### Table 12. Thermal characteristics

# 6.3 Operating conditions

### 6.3.1 General operating conditions

| Symbol                          | Parameter Conditions                                                                |                                          | Min  | Max                  | Unit |  |

|---------------------------------|-------------------------------------------------------------------------------------|------------------------------------------|------|----------------------|------|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                                        |                                          |      |                      |      |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                                       | -                                        | 0    | 32                   | MHz  |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                                       | -                                        | 0    | 32                   |      |  |

|                                 |                                                                                     | BOR detector disabled                    | 1.65 | 3.6                  |      |  |

| V <sub>DD</sub>                 | Standard operating voltage                                                          | BOR detector enabled, at power on        | 1.8  | 3.6                  | V    |  |

|                                 |                                                                                     | BOR detector disabled, after power on    | 1.65 | 3.6                  |      |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC not used)                                  | Must be the same voltage as              | 1.65 | 3.6                  | V    |  |

|                                 | Analog operating voltage<br>(ADC or DAC used)                                       | V <sub>DD</sub> <sup>(2)</sup>           | 1.8  | 3.6                  |      |  |

|                                 |                                                                                     | FT pins; 2.0 V ⊴V <sub>DD</sub>          | -0.3 | 5.5 <sup>(3)</sup>   |      |  |

| V                               | I/O input voltage                                                                   | FT pins; $V_{DD} < 2.0 V$                |      | 5.25 <sup>(3)</sup>  | v    |  |

| V <sub>IN</sub>                 |                                                                                     | BOOT0 pin                                | 0    | 5.5                  | V    |  |

|                                 |                                                                                     | Any other pin                            | -0.3 | V <sub>DD</sub> +0.3 |      |  |

|                                 |                                                                                     | UFBGA132 package                         | -    | 333                  |      |  |

|                                 |                                                                                     | LQFP144 package                          | -    | 500                  |      |  |

| $P_D$                           | Power dissipation at TA = 85 °C for<br>suffix 6 or TA = 105 °C for suffix $7^{(4)}$ | LQFP100 package                          | -    | 465                  | mW   |  |

|                                 |                                                                                     | LQFP64 package                           | -    | 435                  |      |  |

|                                 |                                                                                     | WLCSP104 package                         | -    | 435                  |      |  |

| т.                              | Ambient temperature for 6 suffix version                                            | Maximum power dissipation <sup>(5)</sup> | -40  | 85                   | °C   |  |

| ΤΑ                              | Ambient temperature for 7 suffix version                                            | Maximum power dissipation                | -40  | 105                  |      |  |

| Table 13. | General | operating | conditions |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

### 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table* 37. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                        | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP144, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2    | 4B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP144, T <sub>A</sub> = +25<br>°C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

Table 37. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           |           | Conditions                                                                              |                             | Max vs.                     |                              |         |      |

|------------------|-----------|-----------------------------------------------------------------------------------------|-----------------------------|-----------------------------|------------------------------|---------|------|

|                  | Parameter |                                                                                         | Monitored<br>frequency band | 4 MHz<br>voltage<br>range 3 | 16 MHz<br>voltage<br>range 2 | voltage | Unit |

|                  |           | $V_{DD} = 3.6 V,$<br>$T_A = 25 °C,$<br>LQFP144 package<br>compliant with IEC<br>61967-2 | 0.1 to 30 MHz               | -14                         | -6                           | -4      |      |

| e                |           |                                                                                         | 30 to 130 MHz               | -11                         | 0                            | 9       | dBµV |

| S <sub>EMI</sub> |           |                                                                                         | 130 MHz to 1GHz             | -7                          | -1                           | 9       |      |

|                  |           |                                                                                         | SAE EMI Level               | 1                           | 2                            | 2.5     | -    |

Table 38. EMI characteristics

#### 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1. standard.

| Symbol                | Ratings Conditions                                       |                                            | Class                                            | Maximu<br>m<br>value <sup>(1)</sup> | Uni<br>t |   |

|-----------------------|----------------------------------------------------------|--------------------------------------------|--------------------------------------------------|-------------------------------------|----------|---|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model) | $T_A = +25 $ °C, conforming to JESD22-A114 |                                                  | 2                                   | 2000     | V |

| V <sub>ESD(CDM)</sub> | Electrostatic                                            | $T_A = +25 \ ^{\circ}C$ , conforming       | LQFP144<br>and<br>WLCSP104<br>packages           | C3                                  | 250      |   |

|                       |                                                          | to ANSI/ESD STM5.3.1.                      | packages<br>except<br>LQFP144<br>and<br>WLCSP104 | C4                                  | 500      | V |

Table 39. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

#### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset occurrence oscillator frequency deviation, LCD levels).

The test results are given in the Table 41.

|                  |                                                | Functional s       |                    |      |

|------------------|------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                    | Negative injection | Positive injection | Unit |

|                  | Injected current on all 5 V tolerant (FT) pins | -5 <sup>(1)</sup>  | NA                 |      |

| I <sub>INJ</sub> | Injected current on BOOT0                      | -0                 | NA                 | mA   |

|                  | Injected current on any other pin              | -5 <sup>(1)</sup>  | +5                 |      |

| Table 41. I/O current | injection | susceptibility |

|-----------------------|-----------|----------------|

|-----------------------|-----------|----------------|

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 45*)

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under the conditions summarized in *Table 13*.

| Symbol                                | Parameter                                          | Conditions                                                   | Min                       | Тур                               | Max                 | Unit |

|---------------------------------------|----------------------------------------------------|--------------------------------------------------------------|---------------------------|-----------------------------------|---------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                       | -                                                            | -                         | -                                 | 0.3 V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high<br>level voltage                   | -                                                            | 0.39V <sub>DD</sub> +0.59 | -                                 | -                   | V    |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NRST output low                                    | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -                         | -                                 | 0.4                 | v    |

| VOL(NRST)                             | level voltage                                      | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -                         | -                                 | 0.4                 |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage hysteresis            | -                                                            | -                         | 10%V <sub>DD</sub> <sup>(2)</sup> | -                   | mV   |

| R <sub>PU</sub>                       | Weak pull-up<br>equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30                        | 45                                | 60                  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered<br>pulse                       | -                                                            | -                         | -                                 | 50                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(3)</sup>  | NRST input not<br>filtered pulse                   | -                                                            | 350                       | -                                 | -                   | ns   |

Table 45. NRST pin characteristics

1. Guaranteed by design.

2. With a minimum of 200 mV.

3. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

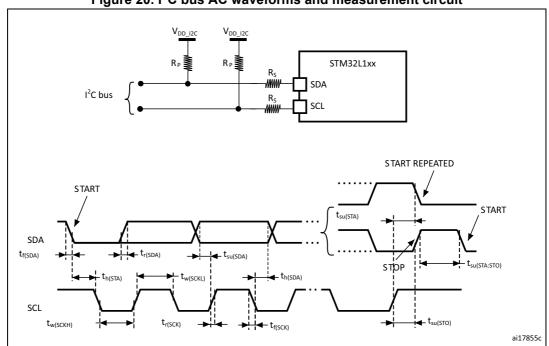

Figure 20. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$  = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD\_12C}$  is the I2C bus power supply.

- 4. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

| f (kUz)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801B                  |

| 300                    | 0x8024                  |

| 200                    | 0x8035                  |

| 100                    | 0x00A0                  |

| 50                     | 0x0140                  |

| 20                     | 0x0320                  |

### Table 48. SCL frequency ( $f_{PCLK1}$ = 32 MHz, $V_{DD} = V_{DD_{12C}} = 3.3 V$ )<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

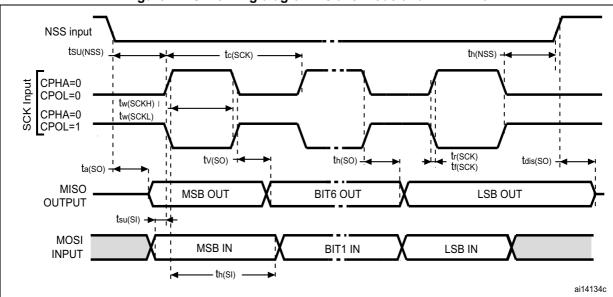

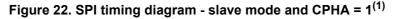

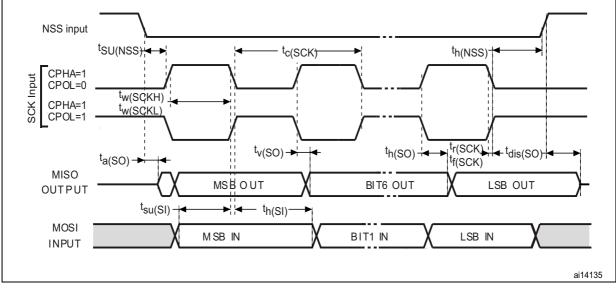

Figure 21. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

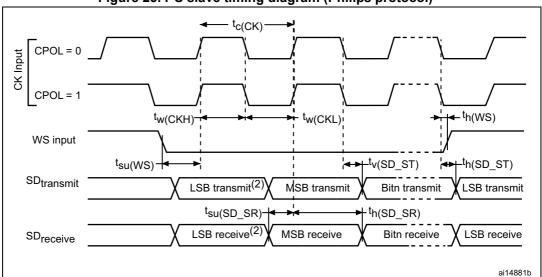

Figure 25. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3 ×  $V_{DD}$  and 0.7 ×  $V_{DD}.$

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

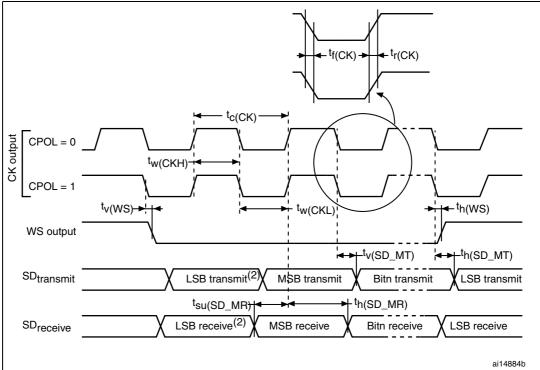

#### Figure 26. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

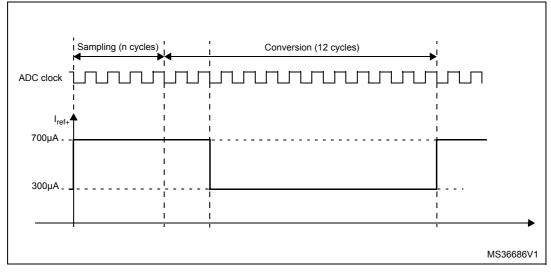

# Figure 29. Maximum dynamic current consumption on V<sub>REF+</sub> supply pin during ADC conversion

#### Table 57. Maximum source impedance R<sub>AIN</sub> max<sup>(1)</sup>

|            |                                    | R <sub>AIN</sub> m               | ax (kΩ)                          |                                                        |     |

|------------|------------------------------------|----------------------------------|----------------------------------|--------------------------------------------------------|-----|

| Ts<br>(µs) | Multiplexe                         | d channels                       | Direct c                         | Ts (cycles)<br>f <sub>ADC</sub> =16 MHz <sup>(2)</sup> |     |

|            | 2.4 V < V <sub>DDA</sub> < 3.6 V 1 | 1.8 V < V <sub>DDA</sub> < 2.4 V | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V                       | ADC |

| 0.25       | Not allowed                        | Not allowed                      | 0.7                              | Not allowed                                            | 4   |

| 0.5625     | 0.8                                | Not allowed                      | 2.0                              | 1.0                                                    | 9   |

| 1          | 2.0                                | 0.8                              | 4.0                              | 3.0                                                    | 16  |

| 1.5        | 3.0                                | 1.8                              | 6.0                              | 4.5                                                    | 24  |

| 3          | 6.8                                | 4.0                              | 15.0                             | 10.0                                                   | 48  |

| 6          | 15.0                               | 10.0                             | 30.0                             | 20.0                                                   | 96  |

| 12         | 32.0                               | 25.0                             | 50.0                             | 40.0                                                   | 192 |

| 24         | 50.0                               | 50.0                             | 50.0                             | 50.0                                                   | 384 |

1. Guaranteed by design.

2. Number of samples calculated for  $f_{ADC}$  = 16 MHz. For  $f_{ADC}$  = 8 and 4 MHz the number of sampling cycles can be reduced with respect to the minimum sampling time Ts (µs),

#### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 11*. The applicable procedure depends on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 100 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

| Symbol               | Par                                                                                                     | ameter         | Condition <sup>(1)</sup>                                   | Min <sup>(2)</sup>       | Тур  | Max <sup>(2)</sup> | Unit |  |

|----------------------|---------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------|--------------------------|------|--------------------|------|--|

|                      | Power supply                                                                                            | Normal mode    | DC                                                         | -                        | -85  | -                  |      |  |

| PSRR                 | rejection ratio                                                                                         | Low-power mode | - DC                                                       | -                        | -90  | -                  | dB   |  |

|                      |                                                                                                         | Normal mode    | N > 2 4 M                                                  | 400                      | 1000 | 3000               |      |  |

| GBW                  | Dondwidth                                                                                               | Low-power mode | - V <sub>DD</sub> >2.4 V                                   | 150                      | 300  | 800                | kHZ  |  |

| GBW                  | Bandwidth                                                                                               | Normal mode    | - V <sub>DD</sub> <2.4 V                                   | 200                      | 500  | 2200               | КПД  |  |

|                      |                                                                                                         | Low-power mode | V <sub>DD</sub> <2.4 V                                     | 70                       | 150  | 800                |      |  |

|                      |                                                                                                         | Normal mode    | $V_{DD}$ >2.4 V<br>(between 0.1 V and $V_{DD}$ -0.1 V)     | -                        | 700  | -                  |      |  |

| SR                   | Slew rate                                                                                               | Low-power mode | V <sub>DD</sub> >2.4 V                                     | -                        | 100  | -                  | V/ms |  |

|                      |                                                                                                         | Normal mode    | N2 4 M                                                     | -                        | 300  | -                  |      |  |

|                      |                                                                                                         | Low-power mode | - V <sub>DD</sub> <2.4 V                                   | -                        | 50   | -                  |      |  |

| 40                   | Open loop gain                                                                                          | Normal mode    |                                                            | 55                       | 100  | -                  | dB   |  |

| AO                   | Open loop gain                                                                                          | Low-power mode |                                                            | 65                       | 110  | -                  |      |  |

| RL                   | Resistive load                                                                                          | Normal mode    | V <24V                                                     | 4                        | -    | -                  | kΩ   |  |

| κL                   | Resistive load                                                                                          | Low-power mode | - V <sub>DD</sub> <2.4 V                                   | 20                       | -    | -                  |      |  |

| CL                   | Capacitive load                                                                                         |                | -                                                          | -                        | -    | 50                 | pF   |  |

| VOH <sub>SAT</sub>   | High saturation voltage                                                                                 | Normal mode    |                                                            | V <sub>DD</sub> -<br>100 | -    | -                  | mV   |  |

| 0,11                 |                                                                                                         | Low-power mode | I <sub>LOAD</sub> = max or                                 | V <sub>DD</sub> -50      | -    | -                  |      |  |

| VO                   | Low saturation                                                                                          | Normal mode    | - R <sub>L</sub> = min                                     | -                        | -    | 100                |      |  |

| VOL <sub>SAT</sub>   | voltage                                                                                                 | Low-power mode |                                                            | -                        | -    | 50                 |      |  |

| φm                   | Phase margin                                                                                            |                | -                                                          | -                        | 60   | -                  | 0    |  |

| GM                   | Gain margin                                                                                             |                | -                                                          | -                        | -12  | -                  | dB   |  |

| t <sub>OFFTRIM</sub> | Offset trim time: during calibration,<br>minimum time needed between two<br>steps to have 1 mV accuracy |                | -                                                          | -                        | 1    | -                  | ms   |  |

| t                    | Wakeup time                                                                                             | Normal mode    | $C_L \leq 50 \text{ pf}, R_L \geq 4 \text{ k}\Omega$       | -                        | 10   | -                  |      |  |

| t <sub>WAKEUP</sub>  | Wakeup time                                                                                             | Low-power mode | $C_L \leq 50 \text{ pf},$<br>$R_L \geq 20 \text{ k}\Omega$ | -                        | 30   | -                  | μs   |  |

| Table 59. Operational | amplifier characteristics | (continued) |

|-----------------------|---------------------------|-------------|

| Tuble oprovidentia    |                           | (oonanaoa)  |

Operating conditions are limited to junction temperature (0 °C to 105 °C) when V<sub>DD</sub> is below 2 V. Otherwise to the full ambient temperature range (-40 °C to 85 °C, -40 °C to 105 °C).

2. Guaranteed by characterization results.

- 1. Guaranteed by characterization results.

- 2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

- 3. Comparator consumption only. Internal reference voltage not included.

| Table 63. Comparator 2 characteristics                         |                                               |                                                                                                                                          |      |     |                    |            |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|--|--|--|

| Symbol                                                         | Parameter                                     | Conditions                                                                                                                               | Min  | Тур | Max <sup>(1)</sup> | Unit       |  |  |  |

| V <sub>DDA</sub>                                               | Analog supply voltage                         | -                                                                                                                                        | 1.65 | -   | 3.6                | V          |  |  |  |

| V <sub>IN</sub>                                                | Comparator 2 input voltage range              | -                                                                                                                                        | 0    | -   | V <sub>DDA</sub>   | V          |  |  |  |

| +.                                                             | Comparator startup time                       | Fast mode                                                                                                                                | -    | 15  | 20                 |            |  |  |  |

| t <sub>start</sub>                                             |                                               | Slow mode                                                                                                                                | -    | 20  | 25                 |            |  |  |  |

| +                                                              | Propagation delay <sup>(2)</sup> in slow mode | 1.65 V ⊴V <sub>DDA</sub> ⊴2.7 V                                                                                                          | -    | 1.8 | 3.5                |            |  |  |  |

| t <sub>d slow</sub>                                            |                                               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                           | -    | 2.5 | 6                  | μs         |  |  |  |

| 4                                                              | Propagation delay <sup>(2)</sup> in fast mode | 1.65 V ⊴V <sub>DDA</sub> ⊴2.7 V                                                                                                          | -    | 0.8 | 2                  |            |  |  |  |

| t <sub>d fast</sub> Propagation delay <sup>(2)</sup> in fast r |                                               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                           |      | 1.2 | 4                  |            |  |  |  |

| V <sub>offset</sub>                                            | Comparator offset error                       |                                                                                                                                          | -    | ±4  | ±20                | mV         |  |  |  |

| dThreshold/<br>dt                                              | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$<br>$T_A = 0 \text{ to } 50 \circ C$<br>$V_{-} = V_{REFINT}$<br>$3/4 V_{REFINT}$<br>$1/2 V_{REFINT}$<br>$1/4 V_{REFINT}$ | -    | 15  | 100                | ppm<br>/°C |  |  |  |

| 1                                                              | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                | -    | 3.5 | 5                  |            |  |  |  |

| I <sub>COMP2</sub>                                             |                                               | Slow mode                                                                                                                                | -    | 0.5 | 2                  | μA         |  |  |  |

| Table 63. | Com   | parator | 2 | characteristics |

|-----------|-------|---------|---|-----------------|

|           | 00111 | purator | - | onunuotoristios |

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

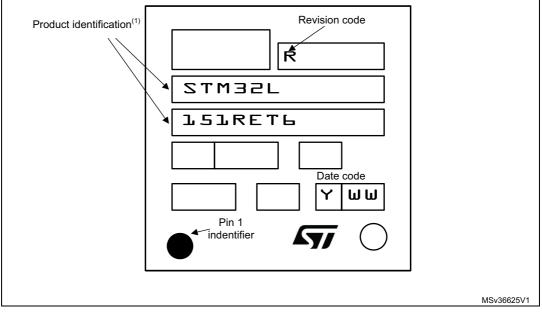

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

#### Figure 39. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

| Curren el          |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol             | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |

| А                  | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.023  |

| A1                 | -     | 0.175       | -     | -      | 0.0069                | -      |

| A2                 | -     | 0.38        | -     | -      | 0.015                 | -      |

| A3 <sup>(2)</sup>  | -     | 0.025       | -     | -      | 0.001                 | -      |

| ø b <sup>(3)</sup> | 0.22  | 0.25        | 0.28  | 0.0087 | 0.0098                | 0.011  |

| D                  | 4.06  | 4.095       | 4.13  | 0.1598 | 0.1612                | 0.1626 |

| E                  | 5.059 | 5.094       | 5.129 | 0.1992 | 0.2006                | 0.2019 |

| е                  | -     | 0.4         | -     | -      | 0.0157                | -      |

| e1                 | -     | 3.2         | -     | -      | 0.126                 | -      |

| e2                 | -     | 4.4         | -     | -      | 0.1732                | -      |

| F                  | -     | 0.447       | -     | -      | 0.0176                | -      |

| G                  | -     | 0.347       | -     | -      | 0.0137                | -      |

| aaa                | -     | -           | 0.1   | -      | -                     | 0.0039 |

| bbb                | -     | -           | 0.1   | -      | -                     | 0.0039 |

| ССС                | -     | -           | 0.1   | -      | -                     | 0.0039 |

| ddd                | -     | -           | 0.05  | -      | -                     | 0.002  |

| eee                | -     | -           | 0.05  | -      | -                     | 0.002  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

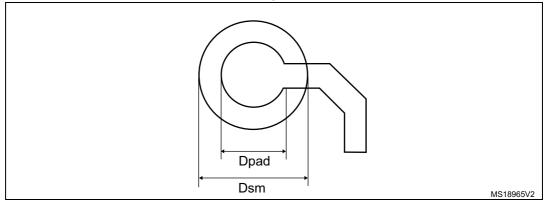

# Figure 44. WLCSP104, 0.4 mm pitch wafer level chip scale package recommended footprint

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID025433 Rev 8