# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Obsolete                                                  |

| Core Processor                  | 68040                                                     |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                            |

| Speed                           | 25MHz                                                     |

| Co-Processors/DSP               | -                                                         |

| RAM Controllers                 | -                                                         |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | -                                                         |

| SATA                            | -                                                         |

| USB                             | -                                                         |

| Voltage - I/O                   | 5.0V                                                      |

| Operating Temperature           | 0°C ~ 70°C (TA)                                           |

| Security Features               | -                                                         |

| Package / Case                  | 184-BCQFP                                                 |

| Supplier Device Package         | 184-CQFP (31.3x31.3)                                      |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68040fe25a |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| 5.4.2               | Transfer in Progress (TIP)                            | 5-8            |

| 5.4.3               | Transfer Acknowledge (TA)                             |                |

| 5.4.4               | Transfer Error Acknowledge (TEA)                      |                |

| 5.4.5               | Transfer Cache Inhibit (TCI)                          | 5-9            |

| 5.4.6               | Transfer Burst Inhibit (TBI)                          | 5-9            |

| 5.5                 | Snoop Control Signals                                 | 5-9            |

| 5.5.1               | Snoop Control (SC1, SC0)                              | 5-9            |

| 5.5.2               | Memory Inhibit (MI)                                   | 5-9            |

| 5.6                 | Arbitration Signals                                   | 5-10           |

| 5.6.1               | Bus Request (BR)                                      | 5-10           |

| 5.6.2               | Bus Grant (BG)                                        |                |

| 5.6.3               | Bus Busy (BB)                                         |                |

| 5.7                 | Processor Control Signals                             |                |

| 5.7.1               | Cache Disable (CDIS)                                  |                |

| 5.7.2               | Reset In (RSTI)                                       |                |

| 5.7.3               | Reset Out (RSTO)                                      |                |

| 5.8                 | Interrupt Control Signals                             |                |

| 5.8.1               | Interrupt Priority Level (IPL2–IPL0)                  |                |

| 5.8.2               | Interrupt Pending Status (IPEND)                      |                |

| 5.8.3               | Autovector (AVEC)                                     |                |

| 5.9                 | Status And Clock Signals                              |                |

| 5.9.1               | Processor Status (PST3–PST0)                          |                |

| 5.9.2               | Bus Clock (BCLK)                                      |                |

| 5.9.3               | Processor Clock (PCLK)—Not on MC68040V and MC68EC040V |                |

| 5.10                | MMU Disable (MDIS)—Not on MC68EC040                   |                |

| 5.11                | Data Latch Enable (DLE)—Only on MC68040               |                |

| 5.12                | Test Signals                                          |                |

| 5.12.1              | Test Clock (TCK)                                      |                |

| 5.12.2              | Test Mode Select (TMS)                                |                |

| 5.12.3              | Test Data In (TDI)                                    |                |

| 5.12.4              | Test Data Out (TDO)                                   |                |

| 5.12.5              | Test Reset (TRST)—Not on MC68040V and MC68EC040V      |                |

| 5.13                | Power Supply Connections                              |                |

| 5.14                | Signal Summary                                        | 5-16           |

#### Section 6 IEEE 1149.1 Test Access Port (JTAG)

| 6.1 | Overview                      | 2 |

|-----|-------------------------------|---|

| 6.2 | Instruction Shift Register6-3 | 3 |

|     | EXTEST                        |   |

#### M68040 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

the logical addresses of the currently executing process. Portions of translation tables can be dynamically allocated as the process requires additional memory.

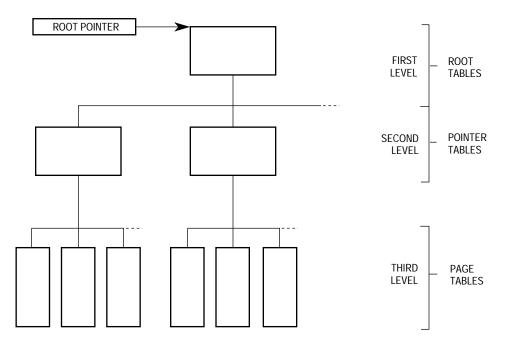

Figure 3-7. Translation Table Structure

The current privilege mode determines the use of the URP or SRP for translation of the access. The root pointer contains the base address of the translation table's root-level table. The translation table consists of tables of descriptors. The table descriptors of the root- and pointer-levels can be either resident or invalid. The page descriptors of the page-level table can be resident, indirect, or invalid. A page descriptor defines the physical address of a page frame in memory that corresponds to the logical address of a page. An indirect descriptor, which contains a pointer to the actual page descriptor, can be used when two or more logical addresses access a single page descriptor.

The table search uses logical addresses to access the translation tables. Figure 3-8 illustrates a logical address format, which is segmented into four fields: root index (RI), pointer index (PI), page index (PGI), and page offset. The first three fields extracted from the logical address index the base address for each table level. The seven bits of the logical address RI field are multiplied by 4 or shifted to the left by two bits. This sum is concatenated with the upper 23 bits of the appropriate root pointer (URP or SRP) to yield the physical address of a root-level table descriptor. Each of the 128 root-level table descriptors corresponds to a 32-Mbyte block of memory and points to the base of a pointer-level table.

#### **Descriptor Address**

This 30-bit field, which contains the physical address of a page descriptor, is only used in indirect descriptors.

#### G—Global

When this bit is set, it indicates the entry is global. PFLUSH instruction variants that specify nonglobal entries do not invalidate global entries, even when all other selection criteria are satisfied. If these PFLUSH variants are not used, then system software can use this bit.

#### M-Modified

This bit identifies a modified page. The M68040 sets the M-bit in the corresponding page descriptor before a write operation to a page for which the M-bit is clear, except for write-protect or supervisor violations. The read portion of a read-modify-write access is considered a write for updating purposes. The M68040 never clears this bit.

#### PDT—Page Descriptor Type

This field identifies the descriptor as an invalid descriptor, a page descriptor for a resident page, or an indirect pointer to another page descriptor.

00 = Invalid

This code indicates that the descriptor is invalid. An invalid descriptor can represent a nonresident page or a logical address range that is out of bounds. All other bits in the descriptor are ignored. When an invalid descriptor is encountered, an ATC entry is created for the logical address with the resident bit in the MMUSR clear.

#### 01 or 11 = Resident

These codes indicate that the page is resident.

10 = Indirect

This code indicates that the descriptor is an indirect descriptor. Bits 31–2 contain the physical address of the page descriptor. This encoding is invalid for a page descriptor pointed to by an indirect descriptor.

#### Physical Address

This 20-bit field contains the physical base address of a page in memory. The logical address supplies the low-order bits of the address required to index into the page. When the page size is 8-Kbyte, the least significant bit of this field is not used.

#### S—Supervisor Protected

This bit identifies a page as supervisor only. Only programs operating in the supervisor mode are allowed to access the portion of the logical address space mapped by this descriptor when the S-bit is set. If the bit is clear, both supervisor and user accesses are allowed.

### 4.7.1 Instruction Cache

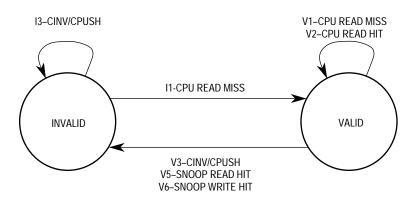

The IU uses the instruction cache to store instruction prefetches as it requests them. Instruction prefetches are normally requested from sequential memory locations except when a change of program flow occurs (e.g., a branch taken) or when an instruction that can modify the status register (SR) is executed, in which case the instruction pipe is automatically flushed and refilled. The instruction cache supports a line-based protocol that allows individual cache lines to be in either the invalid or valid states.

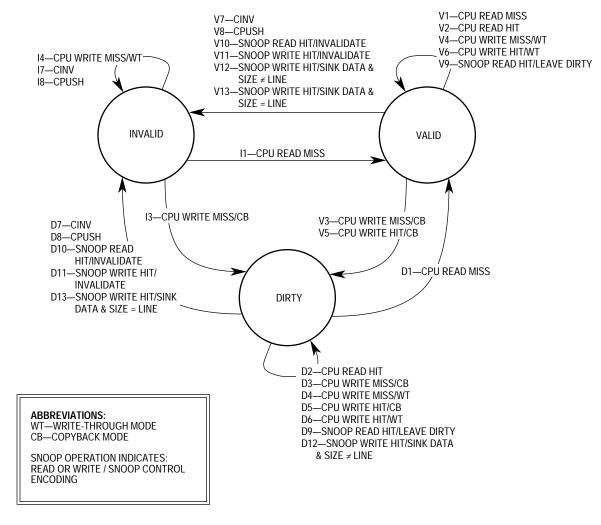

For instruction prefetch requests that hit in the cache, the half-line selected by physical address bit 3 is multiplexed onto the internal instruction data bus. When an access misses in the cache, the cache controller requests the line containing the required data from memory and places it in the cache. If available, an invalid line is selected and updated with the tag and data from memory. The line state then changes from invalid to valid by setting the V-bit. If all lines in the set are already valid, a pseudo-random replacement algorithm is used to select one of the four cache lines replacing the tag and data contents of the line with the new line information. Figure 4-5 illustrates the instruction-cache line state transitions resulting from processor and snoop controller accesses. Transitions are labeled with a capital letter, indicating the previous state, followed by a number indicating the specific case listed in Table 4-3.

Figure 4-5. Instruction-Cache Line State Diagram

Figure 4-6. Data-Cache Line State Diagram

| DLE:<br>PCLK:<br>BCLK:<br>IPL:<br>RSTI:<br>CDIS:<br>MDIS:<br>EGND:<br>EVDD:<br>IGND:<br>IVDD:<br>CGND:<br>CVDD:<br>PGND:<br>PVDD: | linkage<br>linkage<br>linkage<br>linkage<br>linkage<br>linkage | bit;<br>bit;<br>bit;<br>bit_vector(0 to 2);<br>bit;<br>bit;<br>bit;<br>bit_vector(1 to 23);<br>bit_vector(1 to 12);<br>bit_vector(1 to 12);<br>bit_vector(1 to 7);<br>bit_vector(1 to 2);<br>bit_vector(1 to 3);<br>bit_vector(1 to 2) |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                   | linkage                                                        | bit_vector(1 to 2)                                                                                                                                                                                                                     |

| ),                                                                                                                                |                                                                |                                                                                                                                                                                                                                        |

use STD\_1149\_1\_1990.all; attribute PIN\_MAP of MC68040 : entity is PHYSICAL\_PIN\_MAP;

—18x18 PGA Pin Map

|         | x18 : PIN_MAP_STRING :=                                     |   |   |

|---------|-------------------------------------------------------------|---|---|

| "TDI:   | S3,                                                         | " | & |

| "TDO:   | Τ2,                                                         | " | & |

| "TMS:   | S5,                                                         | " | & |

| "TCK:   | S4,                                                         | " | & |

| "TRST:  | ТЗ,                                                         | " | & |

| "RSTO:  | R3,                                                         | " | & |

| "IPEND: | S1,                                                         | " | & |

| "CIOUT: | R1,                                                         | " | & |

| "UPA:   | (Q3, Q1),                                                   | " | & |

| "TT:    | (P3, P2),                                                   | " | & |

| "A:     | (L18, K18, J17, J18, H18, G18, G16, F18, E18, F16, P1, N3,  | " | & |

| "       | N1, M1, L1, K1, K2, J1, H1, J2, G1, F1, E1, G3,             | " | & |

| "       | D1, F3, E2, C1, E3, B1, D3, A1),                            | " | & |

| "D:     | (C3, B3, C4, A2, A3, A4, A5, A6, B7, A7, A8, A9,            | " | & |

| "       | A10, A11, A12, A13, B11, A14, B12, A15, A16, A17, B16, C15, | " | & |

| "       | A18, C16, B18, D16, C18, E16, E17, D18),                    | " | & |

| "LOCKE: | R18,                                                        | " | & |

| "LOCK:  | S18,                                                        | " | & |

| "R_W:   | N16,                                                        | " | & |

| "TLN:   | (Q18, P18),                                                 | " | & |

| "TM:    | (N18, M18, K17),                                            | " | & |

| "SIZ:   | (P17, P16),                                                 | " | & |

| "MI:    | Q16,                                                        | " | & |

| "BR:    | T18,                                                        | " | & |

| "TS:    | R16,                                                        | " | & |

| "BB:    | T17,                                                        | " | & |

| "TIP:   | R15,                                                        | " | & |

| "PST:   | (T15, S14, R14, T16),                                       | " | & |

| "TA:    | T14,                                                        | " | & |

| "TEA:   | S13,                                                        | " | & |

| "BG:    | T13,                                                        | " | & |

| "SC:    | (T12, S12),                                                 | " | & |

| "TBI:   | S11,                                                        | " | & |

| "AVEC:  | T11,                                                        | " | & |

|         |                                                             |   |   |

| num        | cell             | port             | function | safe      | ccell | dsval | rslt       |   |        |               |

|------------|------------------|------------------|----------|-----------|-------|-------|------------|---|--------|---------------|

| "0         | (BC_2,           | RSTO,            | output2, | X),       |       |       |            | " | &      |               |

| "1         | (BC_2,           | IPEND,           | output2, | X),       |       |       |            | " | &      |               |

| "2         | (BC_2,           | CIOUT,           | output3, | Х,        | 156,  | 0,    | Z),<br>Z), | " | &      | —156 = io.0   |

| "3         | (BC_2,           | UPA(0),          | output3, | Х,        | 156,  | 0,    | Z),        | " | &      |               |

| "4         | (BC_2,           | UPA(1),          | output3, | Х,        | 156,  | 0,    | Z),        | " | &      |               |

| "5         | (BC_2,           | TT(0),           | output3, | Х,        | 156,  | 0,    | Z),        | " | &      |               |

| "6         | (BC_4,           | TT(0),           | input,   | X),       |       |       | ,          | " | &      |               |

| "7         | (BC_2,           | TT(1),           | output3, | X,        | 156,  | 0,    | Z),        | " | &      |               |

| "8         | (BC_4,           | TT(1),           | input,   | X),       |       |       | ,          | " | &      |               |

| "9         | (BC_2,           | A(10),           | output3, | X,        | 150,  | 0,    | Z),        | " | &      | —150 = io.ab  |

| "10        | (BC_4,           | A(10),           | input,   | Х),       | ,     | - )   | ,,         | " | &      |               |

| "11        | (BC_2,           | A(11),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "12        | (BC_4,           | A(11),           | input,   | X),       | ,     | σ,    | _/,        | " | &      |               |

| "13        | (BC_2,           | A(12),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "14        | (BC_4,           | A(12),           | input,   | X),       | ,     | -,    | _,,        | " | &      |               |

| "15        | (BC_2,           | A(13),           | output3, | Х,        | 150,  | 0,    | Z),        |   | &      |               |

| "16        | (BC_4,           | A(13),           | input,   | X),       | 100,  | 0,    | _/,        | " | &      |               |

| "17        | (BC_2,           | A(14),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "18        | (BC_2,<br>(BC_4, | A(14),           | input,   | Х,<br>Х), | 100,  | 0,    | ∠),        | " | &      |               |

| "19        | (BC_2,           | A(15),           | output3, | Х),<br>Х, | 150,  | 0,    | Z),        |   | &      |               |

| "20        | (BC_2,<br>(BC_4, | A(15),           | input,   | Х,<br>Х), | 100,  | 0,    | ∠),        |   | &      |               |

| "20<br>"21 | (BC_4,<br>(BC_2, | A(15),<br>A(16), | output3, | л),<br>Х, | 150,  | 0,    | 7)         |   | &      |               |

| "22        | (BC_2,<br>(BC_4, | A(16),<br>A(16), |          |           | 150,  | 0,    | Z),        |   | &      |               |

| "23        |                  |                  | input,   | X),       | 150   | 0     | 7)         |   | &      |               |

| 23<br>"24  | (BC_2,           | A(17),           | output3, | X,        | 150,  | 0,    | Z),        | " | &<br>& |               |

|            | (BC_4,           | A(17),           | input,   | X),       | 150   | 0     | 7)         | " |        |               |

| "25<br>"26 | (BC_2,           | A(18),           | output3, | X,        | 150,  | 0,    | Z),        | " | &      |               |

| "26<br>"27 | (BC_4,           | A(18),           | input,   | X),       | 450   | •     |            | " | &      |               |

| "27<br>"20 | (BC_2,           | A(19),           | output3, | X,        | 150,  | 0,    | Z),        |   | &      |               |

| "28        | (BC_4,           | A(19),           | input,   | X),       | 450   | •     |            | " | &      |               |

| "29        | (BC_2,           | A(20),           | output3, | Х,        | 150,  | 0,    | Z),        |   | &      |               |

| "30        | (BC_4,           | A(20),           | input,   | X),       | 450   | •     |            |   | &      |               |

| "31        | (BC_2,           | A(21),           | output3, | Х,        | 150,  | 0,    | Z),        |   | &      |               |

| "32        | (BC_4,           | A(21),           | input,   | X),       |       |       | _`         | " | &      |               |

| "33        | (BC_2,           | A(22),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "34        | (BC_4,           | A(22),           | input,   | X),       |       | _     |            | " | &      |               |

| "35        | (BC_2,           | A(23),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "36        | (BC_4,           | A(23),           | input,   | X),       |       |       |            | " | &      |               |

| "37        | (BC_2,           | A(24),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "38        | (BC_4,           | A(24),           | input,   | X),       |       |       |            | " | &      |               |

| "39        | (BC_2,           | A(25),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "40        | (BC_4,           | A(25),           | input,   | X),       |       |       |            | " | &      |               |

| "41        | (BC_2,           | A(26),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "42        | (BC_4,           | A(26),           | input,   | X),       |       |       |            | " | &      |               |

| "43        | (BC_2,           | A(27),           | output3, | Х,        | 150,  | 0,    | Z),        | " | &      |               |

| "44        | (BC_4,           | A(27),           | input,   | X),       |       |       |            | " | &      |               |

| "45        | (BC_2,           | A(28),           | output3, | X,        | 150,  | 0,    | Z),        | " | &      |               |

| "46        | (BC_4,           | A(28),           | input,   | X),       |       |       |            | " | &      |               |

| "47        | (BC_2,           | A(29),           | output3, | X,        | 150,  | 0,    | Z),        | " | &      |               |

| "48        | (BC_4,           | A(29),           | input,   | X),       |       |       |            | " | &      |               |

| "49        | (BC_2,           | A(30),           | output3, | X,        | 150,  | 0,    | Z),        | " | &      |               |

| "50        | (BC_4,           | A(30),           | input,   | X),       |       |       | -          | " | &      |               |

| "51        | (BC_2,           | A(31),           | output3, | X,        | 150,  | 0,    | Z),        | " | &      |               |

| "52        | (BC_4,           | A(31),           | input,   | X),       |       |       |            | " | &      |               |

| "53        | (BC_2,           | D(0),            | output3, | X,        | 151,  | 0,    | Z),        | " | &      | — 151 = io.db |

| "54        | (BC_2,           | D(1),            | output3, | X,        | 151,  | 0,    | Z),<br>Z), | " | &      |               |

| "55        | (BC_2,           | D(2),            | output3, | X,        | 151,  | 0,    | Z),        | " | &      |               |

| "56        | (BC_2,           | D(3),            | output3, | X,        | 151,  | 0,    | Z),        | " | &      |               |

|            | 、 _ /            | × //             | • •      |           | ,     |       | , ,        |   |        |               |

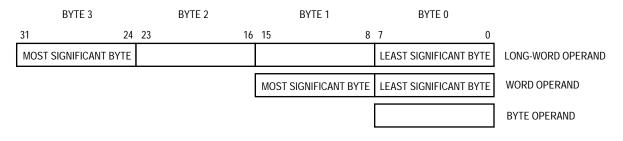

### 7.2 DATA TRANSFER MECHANISM

Figure 7-2 illustrates how the bus designates operands for transfers on a byte boundary system. The integer unit handles floating-point operands as a sequence of related long-word operands. These designations are used in the figures and descriptions that follow.

#### Figure 7-2. Internal Operand Representation

Figure 7-3 illustrates general multiplexing between an internal register and the external bus. The internal register connects to the external data bus through the internal data bus and multiplexer. The data multiplexer establishes the necessary connections for different combinations of address and data sizes.

Unlike the MC68020 and MC68030 processors, the M68040 does not support dynamic bus sizing and expects the referenced device to accept the requested access width. The MC68150 dynamic bus sizer is designed to allow the 32-bit M68040, MC68EC040, MC68LC040 bus to communicate bidirectionally with 32-, 16-, or 8-bit peripherals and memories. It dynamically recognizes the size of the selected peripheral or memory device and then reads or writes the appropriate data from that location. Refer to MC68150/D, *MC68150 Dynamic Bus Sizer*, for information on this device.

Blocks of memory that must be contiguous, such as for code storage or program stacks, must be 32 bits wide. Byte- and word-sized I/O ports that return an interrupt vector during interrupt acknowledge cycles must be mapped into the low-order 8 or 16 bits, respectively, of the data bus.

The multiplexer takes the four bytes of the 32-bit bus transfer and routes them to their required positions. For example, byte 0 would normally be routed to D31–D24, but it can also be routed to any other byte position supporting a misaligned data transfer. The same is true for any of the other operand bytes. The transfer size (SIZ0 and SIZ1) and byte offset (A1 and A0) signals determine the positioning of the bytes (see Table 7-1). The size indicated on the SIZx signals corresponds to the size of the operand transfer for the entire bus cycle. During an operand transfer, A31–A2 indicate the long-word base address for the first byte of the operand to be accessed; A1 and A0 indicate the byte offset from the base. For a burst-inhibited line transfer, A1 and A0 for each of the four accesses (the burst-inhibited line transfer and three long-word transfers) are copied from the lowest two bits of the access address used to initiate the line transfer.

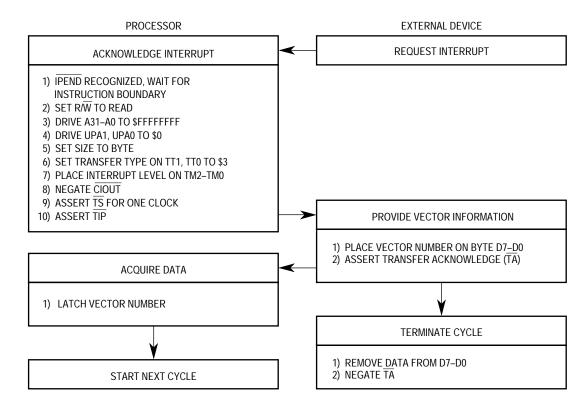

The interrupt acknowledge bus cycle is a read transfer. It differs from a normal read cycle in the following respects:

- 1. TT1 and TT0 = \$3 to indicate an acknowledged bus cycle.

- 2. Address signals A31–A0 are set to all ones (\$FFFFFFF).

- 3. TM2–TM0 are set to the interrupt request level (the inverted values of IPL2–IPL0).

The responding device places the vector number on the data bus during the interrupt acknowledge bus cycle, and the cycle is terminated normally with  $\overline{TA}$ . Figures 7-21 and 7-22 illustrate a flowchart and functional timing diagram for an interrupt acknowledge cycle terminated with  $\overline{TA}$ .

Figure 7-21. Interrupt Acknowledge Bus Cycle Flowchart

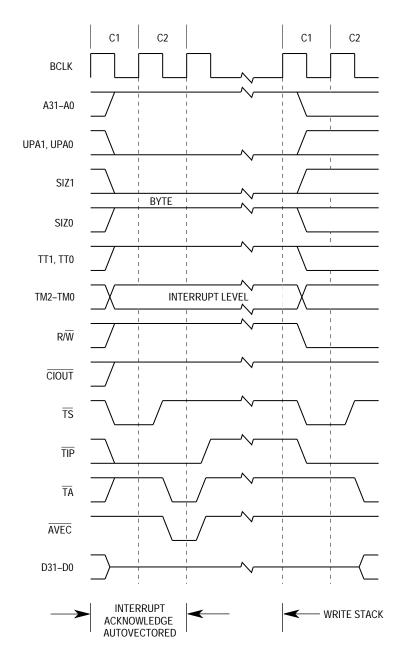

generates the vector number, which is the sum of the interrupt priority level plus 24 (\$18). There are seven distinct autovectors that can be used, corresponding to the seven levels of interrupts available with IPL2–IPL0 signals. Figure 7-23 illustrates a functional timing diagram for an autovector operation.

Figure 7-23. Autovector Interrupt Acknowledge Bus Cycle Timing

**7.5.1.3 SPURIOUS INTERRUPT ACKNOWLEDGE BUS CYCLE.** When a device does not respond to an interrupt acknowledge bus cycle with TA, or  $\overline{AVEC}$  and TA, the external logic typically returns the transfer error acknowledge signal (TEA). In this case, the M68040 automatically generates the spurious interrupt vector number 24 (\$18) instead of the interrupt vector number. If TA and TEA are both asserted, the processor retries the cycle.

To properly control termination of a bus cycle for a bus error or retry condition, TA and TEA must be asserted and negated for the same rising edge of BCLK. Table 7-5 lists the control signal combinations and the resulting bus cycle terminations. Bus error and retry terminations during burst cycles operate as described in **7.4.2 Line Read Transfers** and **7.4.4 Line Write Transfers**.

| Case No. | TA   | TEA  | Result                                                                 |

|----------|------|------|------------------------------------------------------------------------|

| 1        | High | Low  | Bus Error—Terminate and Take Bus Error Exception,<br>Possibly Deferred |

| 2        | Low  | Low  | Retry Operation—Terminate and Retry                                    |

| 3        | Low  | High | Normal Cycle Terminate and Continue                                    |

| 4        | High | High | Insert Wait States                                                     |

Table 7-5. TA and TEA Assertion Results

### 7.6.1 Bus Errors

The system hardware can use the  $\overline{TEA}$  signal to abort the current bus cycle when a fault is detected. A bus error is recognized during a bus cycle when  $\overline{TA}$  is negated and  $\overline{TEA}$  is asserted. When the processor recognizes a bus error condition for an access, the access is terminated immediately. A line access that has  $\overline{TEA}$  asserted for one of the four longword transfers aborts without completing the remaining transfers, regardless of whether the line transfer uses a burst or burst-inhibited access.

When TEA is asserted to terminate a bus cycle, the M68040 can enter access error exception processing immediately following the bus cycle, or it can defer processing the exception. The instruction prefetch mechanism requests instruction words from the instruction memory unit before it is ready to execute them. If a bus error occurs on an instruction fetch, the processor does not take the exception until it attempts to use the instruction. Should an intervening instruction cause a branch or should a task switch occur, the access error exception for the unused access does not occur. Similarly, if a bus error is detected on the second, third, or fourth long-word transfer for a line read access, an access error exception is taken only if the execution unit is specifically requesting that long word. Otherwise, the line is not placed in the cache, and the processor repeats the line access when another access references the line. If a misaligned operand spans two long words in a line, a bus error on either the first or second transfer for the line causes exception processing to begin immediately. A bus error termination for any write accesses or for read accesses that reference data specifically requested by the execution unit causes the processor to begin exception processing immediately. Refer to Section 8 Exception Processing for details of access error exception processing.

When a bus error terminates an access, the contents of the corresponding cache can be affected in different ways, depending on the type of access. For a cache line read to replace a valid instruction or data cache line, the cache line being filled is invalidated before the bus cycle begins and remains invalid if the replacement line access is terminated with a bus error. If a dirty data cache line is being replaced and a bus error occurs during the replacement line read, the dirty line is restored from an internal push

### 7.6.3 Double Bus Fault

A double bus fault occurs when an access or address error occurs during the exception processing sequence—e.g., the processor attempts to stack several words containing information about the state of the machine while processing an access error exception. If a bus error occurs during the stacking operation, the second error is considered a double bus fault.

The M68040 indicates a double bus fault condition by continuously driving PST3–PST0 with an encoded value of \$5 until the processor is reset. Only an external reset operation can restart a halted processor. While the processor is halted, negating BR and forcing all outputs to a high-impedance state releases the external bus.

A second access or address error that occurs during execution of an exception handler or later, does not cause a double bus fault. A bus cycle that is retried does not constitute a bus error or contribute to a double bus fault. The processor continues to retry the same bus cycle as long as external hardware requests it.

## 7.7 BUS SYNCHRONIZATION

The M68040 integer unit generates access requests to the instruction and data memory units to support integer and floating-point operations. Both the <ea> fetch and write-back stages of the integer unit pipeline perform accesses to the data memory unit, with effective address fetches assigned a higher priority. This priority allows data read and write accesses to occur out of order, with a memory write access potentially delayed for many clocks while allowing read accesses generated by later instructions to complete. The processor detects a read access that references earlier data waiting to be written (address collisions) and allows the corresponding write access to complete. A given sequence of read accesses or write accesses is completed in order, and reordering only occurs with writes relative to reads. Figure 2-1 in **Section 2 Integer Unit** illustrates the integer pipeline stages.

Besides address collisions, the instruction restart model used for exception processing in the M68040 causes another potential problem. After the operand fetch for an instruction, an exception that causes the instruction to be aborted can occur, resulting in another access for the operand after the instruction restarts. For example, an exception could occur after a read access of an I/O device's status register. The exception causes the instruction to be read again. If the first read accesses clears the status bits, the status information is lost, and the instruction obtains incorrect data.

Designating the memory page containing the address of the device as serialized noncachable prevents multiple out-of-order accesses to devices sensitive to such accesses. When the data memory unit detects an attempt to read an operand from a page designated as serialized noncachable, it allows all pending write accesses to complete before beginning the external read access. The definition of a page as noncachable versus serialized noncachable only affects read accesses. When a write operation reaches the integer unit's write-back stage, all previous instructions have completed. When a read access to a serialized noncachable page begins, only a bus error exception

If a floating-point exception is pending from a previous floating-point instruction, a preinstruction exception is taken. After the appropriate exception handler is executed, the conditional instruction is restarted. When the FPU pipeline is idle (all previous floatingpoint instructions have completed) and no exceptions are pending, the processor evaluates the conditional predicate and checks for a BSUN exception before executing the conditional instruction.

**9.7.1.1 MASKABLE EXCEPTION CONDITIONS.** A BSUN exception occurs if the conditional predicate is one of the IEEE nonaware branches and the FPCC NAN bit is set. When the processor detects this condition, it sets the BSUN bit in the FPSR EXC byte.

- a. If the user BSUN exception handler is disabled, the floating-point condition is evaluated as if it were the equivalent IEEE aware conditional predicate. No exceptions are taken.

- b. If the user BSUN exception handler is enabled, the processor takes a floating-point pre-instruction exception. A \$0 stack frame is saved, and vector number 48 is generated to access the BSUN exception vector. The BSUN entry in the processor's vector table points to the M68040FPSP BSUN exception handler.

For MC68881/MC68882 compatibility, the M68040FPSP updates the FPIAR by copying the PC value in the pre-instruction stack frame to the FPIAR. The M68040FPSP BSUN exception handler restores the FPU to its exceptional state, cleans up the stack to the state prior to the M68040FPSP BSUN exception handler's execution, and continues instruction execution at the user BSUN exception handler. No parameters are passed to the user BSUN exception handler since the M68040FPSP BSUN exception handler provides the illusion that it never existed.

The user BSUN exception handler must execute an FSAVE as its first floating-point instruction. FSAVE allows other floating-point instructions to execute without reporting the BSUN exception again, although none of the state frame values are useful in the execution of the user BSUN exception handler. The BSUN exception is unique in that the exception is taken before the conditional predicate is evaluated. If the user BSUN exception handler does not set the PC to the instruction following the one that caused BSUN exception when returning, the exception is executed again. Therefore, it is the responsibility of the user BSUN exception handler to prevent the conditional instruction from taking the BSUN exception again. There are four ways to prevent taking the exception again:

- 1. Incrementing the stored PC in the stack bypasses the conditional instruction. This technique applies to situations where a fall-through is desired. Note that accurate calculation of the PC increment requires detailed knowledge of the size of the conditional instruction being bypassed.

- 2. Clearing the NAN bit prevents the exception from being taken again. However, this alone cannot deterministically control the result's indication (true or false) that would be returned when the conditional instruction reexecutes.

- 3. Disabling the BSUN bit also prevents the exception from being taken again. Like the second method, this method cannot control the result indication (true or false) that would be returned when the conditional instruction reexecutes.

|                         | BFF                     | FO <sup>a,b</sup>   | BF                      | INS <sup>a,c</sup>  | BFTST <sup>a</sup>      |                     |

|-------------------------|-------------------------|---------------------|-------------------------|---------------------|-------------------------|---------------------|

| Addressing<br>Mode      | <ea><br/>Calculate</ea> | Execute             | <ea><br/>Calculate</ea> | Execute             | <ea><br/>Calculate</ea> | Execute             |

| Dn                      | <sub>3/4</sub> d        | 6/7 <sup>d</sup>    | 2/3 <sup>d</sup>        | 5/6 <sup>d</sup>    | 1/2 <sup>d</sup>        | 3/4 d               |

| An                      | _                       | —                   | _                       | —                   | _                       | —                   |

| (An)                    | 9                       | 2L + 9              | 9                       | 2L + 7              | 9                       | 2L + 7              |

| (An)+                   | _                       | —                   |                         | —                   | —                       | —                   |

| –(An)                   | —                       | _                   | —                       | —                   | —                       | —                   |

| (d <sub>16</sub> ,An)   | 9                       | 2 <sub>L</sub> + 9  | 9                       | 2 <sub>L</sub> + 7  | 9                       | 2L + 7              |

| (d <sub>16</sub> ,PC)   | 10                      | 3L + 9              | _                       | —                   | 10                      | 3L + 7              |

| (xxx).W, (xxx).L        | 9                       | 2 <sub>L</sub> + 9  | 9                       | 2 <sub>L</sub> + 7  | 9                       | 2 <sub>L</sub> + 7  |

| # <xxx></xxx>           | _                       | _                   | _                       | —                   | —                       | —                   |

| (d <sub>8</sub> ,An,Xn) | 10                      | 12                  | 10                      | 10                  | 10                      | 10                  |

| (d <sub>8</sub> ,PC,Xn) | 11                      | 1 <sub>L</sub> + 12 |                         | —                   | 11                      | 1 <sub>L</sub> + 10 |

| (BR,Xn)                 | 13                      | 1 <sub>L</sub> + 14 | 13                      | 1 <sub>L</sub> + 12 | 13                      | 1 <sub>L</sub> + 12 |

| (bd,BR,Xn)              | 14                      | 1 <sub>L</sub> + 15 | 14                      | 1 <sub>L</sub> + 13 | 14                      | 1 <sub>L</sub> + 13 |

| ([bd,BR,Xn])            | 16                      | 1 <sub>L</sub> + 17 | 16                      | 1 <sub>L</sub> + 15 | 16                      | 1 <sub>L</sub> + 15 |

| ([bd,BR,Xn],od)         | 17                      | 1 <sub>L</sub> + 18 | 17                      | 1 <sub>L</sub> + 16 | 17                      | 1 <sub>L</sub> + 16 |

| ([bd,BR],Xn)            | 17                      | 3 <sub>L</sub> + 16 | 17                      | 3 <sub>L</sub> + 14 | 17                      | 3L + 14             |

| ([bd,BR],Xn,od)         | 18                      | 3 <sub>L</sub> + 17 | 18                      | 3 <sub>L</sub> + 15 | 18                      | 3 <sub>L</sub> + 15 |

### **10.6 INTEGER UNIT INSTRUCTION TIMINGS (Continued)**

NOTES:

a. This instruction interlocks the <ea> calculate and execute stages.

b. If the bit field spans a long-word boundary, add two clocks to the execute time. Two memory addresses are accessed in this case.

c. If the bit field spans a long-word boundary, add seven clocks to both the <ea> calculate and execute times. Two memory addresses are accessed in this case.

d. If the bit field spans a long-word boundary, add ten and nine clocks to both the <ea> calculate and execute times, respectively. Two memory addresses are accessed in this case.

|                         | MOVES <ea>,An<sup>*</sup> MOVES <ea>,Dn<sup>*</sup></ea></ea> |                     | MOVES Rn, <ea>*</ea>    |                     |                         |                     |

|-------------------------|---------------------------------------------------------------|---------------------|-------------------------|---------------------|-------------------------|---------------------|

| Addressing<br>Mode      | <ea><br/>Calculate</ea>                                       | Execute             | <ea><br/>Calculate</ea> | Execute             | <ea><br/>Calculate</ea> | Execute             |

| Dn                      | _                                                             | —                   | _                       | —                   | —                       | _                   |

| An                      | —                                                             | —                   | —                       | —                   | _                       | —                   |

| (An)                    | 28                                                            | 4L + 24             | 20                      | 4L + 19             | 13                      | 4L + 9              |

| (An)+                   | 28                                                            | 4L + 24             | 20                      | 4L + 19             | 13                      | 4L + 9              |

| –(An)                   | 17                                                            | 2 <sub>L</sub> + 15 | 11                      | 12                  | 11                      | 2L + 9              |

| (d <sub>16</sub> ,An)   | 29                                                            | 4L + 24             | 21                      | 4L + 19             | 14                      | 4L + 9              |

| (d <sub>16</sub> ,PC)   | _                                                             | —                   | _                       | —                   | —                       | —                   |

| (xxx).W, (xxx).L        | 17                                                            | 2 <sub>L</sub> + 15 | 11                      | 4 <sub>L</sub> + 10 | 11                      | 2L + 9              |

| # <xxx></xxx>           | —                                                             | —                   | _                       | —                   | —                       | —                   |

| (dg,An,Xn)              | 29                                                            | 1 <sub>L</sub> + 27 | 21                      | 1 <sub>L</sub> + 22 | 14                      | 1 <sub>L</sub> + 12 |

| (d <sub>8</sub> ,PC,Xn) | —                                                             | —                   | —                       | —                   | —                       | —                   |

| (BR,Xn)                 | 21                                                            | 2 <sub>L</sub> + 19 | 15                      | 2L + 14             | 15                      | 2 <sub>L</sub> + 13 |

| (bd,BR,Xn)              | 22                                                            | 2L + 20             | 16                      | 2L + 15             | 16                      | 2 <sub>L</sub> + 14 |

| ([bd,BR,Xn])            | 35                                                            | 2 <sub>L</sub> + 32 | 26                      | 2 <sub>L</sub> + 27 | 21                      | 2 <sub>L</sub> + 17 |

| ([bd,BR,Xn],od)         | 31                                                            | 2L + 29             | 23                      | 2L + 24             | 20                      | 2 <sub>L</sub> + 18 |

| ([bd,BR],Xn)            | 36                                                            | 4L + 31             | 27                      | 4L + 26             | 21                      | 4 <sub>L</sub> + 16 |

| ([bd,BR],Xn,od)         | 32                                                            | 4 <sub>L</sub> + 28 | 24                      | 4 <sub>L</sub> + 23 | 21                      | 4 <sub>L</sub> + 17 |

# **10.6 INTEGER UNIT INSTRUCTION TIMINGS (Continued)**

\*Times listed are typical. This instruction interlocks the <ea> calculate and execute stages and synchronizes some portions of the processor before execution.

NOTE: Do not cover up microprocessor markings with an adhesive mounted heat sink.

#### Figure 11-10. Heat Sink with Adhesive

All pin-fin heat sinks tested were made from extrusion aluminum products. The planar face of the heat-sink matting to the package should have a good degree of planarity; if it has any curvature, the curvature should be convex at the central region of the heat-sink surface to provide intimate physical contact to the PGA surface. This heat sinks meet this criteria. Nonplanar, concave curvature in the central regions of the heat sink results in poor thermal contact to the package.

Although there are several ways to attach a heat sink to the package, it is easiest to use a demountable heat-sink attachment called "E-Z attach for PGA packages" (see Figure 11-33). A steel spring clamps the heat sink and the package to a plastic frame. Besides the height of the heat sink and plastic frame, no additional height is added to the package. The interface between the ceramic package and the aluminum heat sink was evaluated for both dry and wet interfaces in still air. The thermal grease reduced the  $\theta_{CA}$  quite significantly (about 2.5 °C/W) in still air. An attachment with thermal grease provided about the same thermal performance as if a thermal epoxy had been used.

I

#### MC68LC040 REV2.3 (01/29/2000)

a pending unimplemented floating-point instruction exception. The access error exception handler then completes the write-backs in software, and exception processing for the unimplemented floating-point instruction exception begins immediately after return from the access error handler.

3. The processor begins exception processing for the unimplemented floating-point instruction by making an internal copy of the current SR. The processor then enters the supervisor mode and clears the trace bits (T1 and T0). It creates a format \$4 stack frame and saves the internal copy of the SR, PC, vector offset, calculated effective address, and PC value of the faulted instruction in the stack frame.

The effective address field of the format \$4 stack frame contains the calculated effective address of the operand for the faulted floating-point instruction using the addressing mode in which the effective address is calculated. For immediate and register direct addressing modes, this field is \$0. The saved PC value is the logical address of the instruction that follows the unimplemented floating-point instruction. This value will be restored during RTE execution. The vector offset format number (\$4) is used for this eight-word stack frame. Note that an MC68040 cannot correctly handle a stack format \$4. The PC of the faulted instruction contains a long-word PC of the floating-point instruction that caused the trap to occur. The information is provided so that the instruction is available for software emulation of floating-point instructions. The processor generates exception vector number 11 for the unimplemented F-line instruction exception vector, fetches the address of the F-line exception handler from the exception vector table, and begins execution of the handler after prefetching instructions to fill the pipeline. Refer to **Section 8 Exception Processing** for details about exception processing.

#### A.5.2 MC68LC040 Stack Frames

When the processor executes an RTE instruction, it examines the stack frame on top of the active supervisor stack to determine if it is a valid frame and what type of context restoration it requires. The MC68LC040 provides five different stack frames for exception processing and allows for an MC68040-specific stack frame. The set of frames includes four- and six-word stack frames, a four-word throwaway stack frame, an access error stack frame, and a new eight-word unimplemented floating-point stack frame. The stack frame that the MC68040 can generate and the MC68LC040 can process is the floating-point post-instruction stack frame. Refer to **Section 8 Exception Processing** for details about exception stack frames.

| Stack Frames | Exception Types | Stacked PC Points To |

|--------------|-----------------|----------------------|

|--------------|-----------------|----------------------|

M68040 USER'S MANUAL

Figure B-11. Snoop Miss Timing

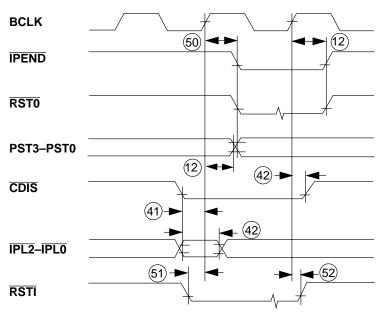

Figure B-12. Other Signal Timing

B-19

M68040 USER'S MANUAL

MOTOROLA

L

### C.7.3 DC Electrical Specifications (V<sub>CC</sub> = 3.3 Vdc ±10 %)

| Characteristic                                                                                                                                               | Symbol          | Min | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| Input High Voltage                                                                                                                                           | VIH             | 2   | 5.5 | V    |

| Input Low Voltage                                                                                                                                            | VIL             | GND | 0.8 | V    |

| Overshoot                                                                                                                                                    | —               | —   | TBD | V    |

| Input Leakage Current @ 0.5/2.4 V During Normal Operation Only<br>AVEC, BCLK, BG, CDIS, MDIS <sup>1</sup> , IPLx, RSTI, SCx,<br>TBI, TLNx, TCI, TCK, TEA     | l <sub>in</sub> | TBD | TBD | μA   |

| Hi-Z (Off-State) Leakage Current @ 0.5/2.4 V During Normal Operation<br>An, BB, CIOUT, Dn, LOCK, LOCKE, R/W, SIZx, TA, TDO,<br>TIP, TMx, TLNx, TS, TTx, UPAx | ITSI            | TBD | TBD | μΑ   |

| Signal Low Input Current, V <sub>IL</sub> = 0.8 V<br>TMS, TDI                                                                                                | ١Ľ              | TBD | TBD | mA   |

| Signal High Input Current, VIH = 2.0 V<br>TMS, TDI                                                                                                           | ΙH              | TBD | TBD | mA   |

| Output High Voltage IOH = 5ma                                                                                                                                | VOH             | 2.4 | _   | V    |

| Output Low Voltage IOL = 5ma                                                                                                                                 | VOL             | —   | 0.5 | V    |

| Capacitance2, V <sub>in</sub> = 0 V, f = 1 MHz                                                                                                               | C <sub>in</sub> | _   | TBD | pF   |

NOTES:

1. There is no  $\overline{\text{MDIS}}$  on the MC68EC040V.

2. Capacitance is periodically sampled rather than 100% tested.

# **C.7.4 Power Dissipation**

|                                                                                      | 25 MHz | 33 MHz |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------|--------|--------|--|--|--|--|--|--|--|--|

| Worst Case (V <sub>CC</sub> = 3.6 V , T <sub>A</sub> = 0°C)                          |        |        |  |  |  |  |  |  |  |  |

| MC68040V                                                                             | TBD    | 2 W    |  |  |  |  |  |  |  |  |

| MC68EC040V                                                                           | TBD    | 2 W    |  |  |  |  |  |  |  |  |

| LPSTOP Mode - No output loads, not driving bus                                       |        |        |  |  |  |  |  |  |  |  |

| MC68040V                                                                             | TBD    | TBD    |  |  |  |  |  |  |  |  |

| MC68EC040V                                                                           | TBD    | TBD    |  |  |  |  |  |  |  |  |

| Typical Values (V <sub>CC</sub> = 3.3 V, T <sub>J</sub> = TBD°C)* - Normal Operation |        |        |  |  |  |  |  |  |  |  |

| MC68040V                                                                             | TBD    | 1.5 W  |  |  |  |  |  |  |  |  |

| MC68EC040V                                                                           | TBD    | 1.5 W  |  |  |  |  |  |  |  |  |

\*This information is for system reliability purposes.

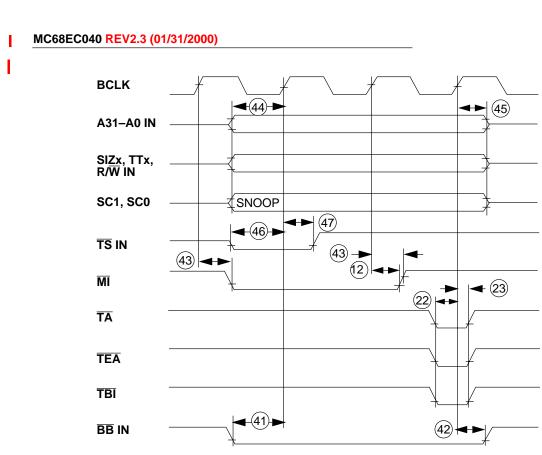

### C.7.7 Input AC Timing Specifications (See Figures C-13 to C-21)

| PRELIMINARY |                                                                 |             |     |        |     |        |      |      |  |  |

|-------------|-----------------------------------------------------------------|-------------|-----|--------|-----|--------|------|------|--|--|

| Num         | Characteristic                                                  | 0–16.67 MHz |     | 25 MHz |     | 33 MHz |      |      |  |  |

|             |                                                                 | Min         | Max | Min    | Max | Min    | Max  | Unit |  |  |

| 15          | Data-In Valid to BCLK (Setup)                                   | 5           | —   | 5      | —   | 4      | —    | ns   |  |  |

| 16          | BCLK to Data-In Invalid (Hold)                                  | 4           | —   | 4      | —   | 4      | _    | ns   |  |  |

| 17          | BCLK to Data-In High Impedance (Read Followed by Write)         | _           | 49  | _      | 49  | _      | 36.5 | ns   |  |  |

| 22a         | TA Valid to BCLK (Setup)                                        | 10          | —   | 10     |     | 10     | —    | ns   |  |  |

| 22b         | TEA Valid to BCLK (Setup)                                       | 10          | —   | 10     | —   | 10     | —    | ns   |  |  |

| 22c         | TCI Valid to BCLK (Setup)                                       | 10          | —   | 10     | —   | 10     | —    | ns   |  |  |

| 22d         | TBI Valid to BCLK (Setup)                                       | 11          | —   | 11     | —   | 10     | _    | ns   |  |  |

| 23          | BCLK to TA, TEA, TCI, TBI Invalid (Hold)                        | 2           | —   | 2      | —   | 2      | —    | ns   |  |  |

| 24          | AVEC Valid to BCLK (Setup)                                      | 5           | —   | 5      | —   | 5      | _    | ns   |  |  |

| 25          | BCLK to AVEC Invalid (Hold)                                     | 2           | —   | 2      |     | 2      | —    | ns   |  |  |

| 41a         | BB Valid to BCLK (Setup)                                        | 7           | —   | 7      |     | 7      | —    | ns   |  |  |

| 41b         | BG Valid to BCLK (Setup)                                        | 8           | —   | 8      |     | 7      | _    | ns   |  |  |

| 41c         | CDIS, MDIS* Valid to BCLK (Setup)                               | 10          | —   | 10     |     | 8      | _    | ns   |  |  |

| 41d         | IPLx Valid to BCLK (Setup)                                      | 4           | —   | 4      |     | 3      | —    | ns   |  |  |

| 42          | BCLK to BB, BG, CDIS, MDIS*, IPLx Invalid<br>(Hold)             | 2           | _   | 2      | _   | 2      | _    | ns   |  |  |

| 44a         | Address Valid to BCLK (Setup)                                   | 8           | —   | 8      |     | 7      | _    | ns   |  |  |

| 44b         | SIZx Valid to BCLK (Setup)                                      | 12          | —   | 12     |     | 8      | _    | ns   |  |  |

| 44c         | TTx Valid to BCLK (Setup)                                       | 6           | —   | 6      |     | 8.5    | _    | ns   |  |  |

| 44d         | R/W Valid to BCLK (Setup)                                       | 6           | —   | 6      |     | 5      | —    | ns   |  |  |

| 44e         | SCx Valid to BCLK (Setup)                                       | 10          | —   | 10     |     | 11     | _    | ns   |  |  |

| 45          | BCLK to Address SIZx, TTx, R/W, SCx<br>Invalid (Hold)           | 2           | _   | 2      | _   | 2      | _    | ns   |  |  |

| 46          | TS Valid to BCLK (Setup)                                        | 5           | —   | 5      |     | 9      | _    | ns   |  |  |

| 47          | BCLK to TS Invalid (Hold)                                       | 2           | —   | 2      |     | 2      | —    | ns   |  |  |

| 49          | BCLK to BB High Impedance<br>(Processor Assumes Bus Mastership) | _           | 9   | _      | 9   | _      | 9    | ns   |  |  |

| 51          | RSTI Valid to BCLK                                              | 5           | —   | 5      |     | 4      | _    | ns   |  |  |

| 52          | BCLK to RSTI Invalid                                            | 2           | —   | 2      | _   | 2      | _    | ns   |  |  |

| В           | LFO change to valid IPLx, RSTI (setup)                          | 5           | —   | 5      |     | 5      |      | ns   |  |  |

| D           | IPEND valid to IPLx invalid (Hold)                              | 0           | _   | 0      | _   | 0      |      | ns   |  |  |

| V           | RSTI pulse width, leaving LPSTOP mode                           | 10          | —   | 10     | _   | 10     | —    | ns   |  |  |

| Z           | IPLx, RSTI valid to LFO change (Hold)                           | 500         |     | 500    | _   | 500    |      | ns   |  |  |

NOTE: \*Not on the MC68EC040V.