#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Obsolete                                                    |

| Core Processor                  | 68040                                                       |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 33MHz                                                       |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | -                                                           |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | -                                                           |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 5.0V                                                        |

| Operating Temperature           | 0°C ~ 70°C (TA)                                             |

| Security Features               | -                                                           |

| Package / Case                  | 184-BCQFP                                                   |

| Supplier Device Package         | 184-CQFP (31.3x31.3)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68lc040fe33a |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

| C.7                 | MC68040V and MC68EC040V Electrical Characteristics | C-19           |

| C.7.1               | Maximum Ratings                                    | C-19           |

| C.7.2               | Thermal Characteristics                            | C-19           |

| C.7.3               | DC Electrical Specifications                       | C-20           |

| C.7.4               | Power Dissipation                                  | C-20           |

| C.7.5               | Clock AC Timing Specifications                     | C-21           |

| C.7.6               | Output AC Timing Specifications                    | C-22           |

| C.7.7               | Input AC Timing Specifications                     | C-23           |

#### Appendix D M68000 Family Summary

#### Appendix E Floating-Point Emulation (M68040FPSP)

Index

# LIST OF TABLES (Continued)

| Table<br>Numbe                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page<br>Numbei                                                           |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 8-5<br>8-6                                                                  | Write-Back Data Alignment<br>Access Error Stack Frame Combinations                                                                                                                                                                                                                                                                                                                                                                          |                                                                          |

| 9-1<br>9-2<br>9-3<br>9-4<br>9-5<br>9-6<br>9-7<br>9-8<br>9-9<br>9-10<br>9-11 | Floating-Point Control Register Encodings<br>MC68040 FPU Data Formats and Data Types<br>Single-Precision Real Format Summary<br>Double-Precision Real Format Summary<br>Extended-Precision Real Format Summary<br>Packed Decimal Real Format Summary<br>Floating-Point Condition Code Encodings<br>Floating-Point Conditional Tests<br>Floating-Point Exception Vectors<br>Unimplemented Instructions<br>Possible Operand Errors Exceptions | 9-3<br>9-7<br>9-8<br>9-9<br>9-10<br>9-11<br>9-17<br>9-19<br>9-20<br>9-21 |

| 9-12<br>9-13<br>9-14<br>9-15<br>9-16                                        | Overflow Rounding Mode Values<br>Underflow Rounding Mode Values<br>Possible Divide by Zero Exceptions<br>Divide by Zero Rounding Mode Values<br>State Frame Field Information                                                                                                                                                                                                                                                               | 9-32<br>9-34<br>9-36<br>9-37<br>9-44                                     |

| 10-1<br>10-2<br>10-3<br>10-4                                                | Instruction Timing Index<br>Number of Memory Accesses<br>CINV Timing<br>CPUSH Best and Worst Case Timing                                                                                                                                                                                                                                                                                                                                    | 10-3<br>10-8                                                             |

| 11-1<br>11-2<br>11-3                                                        | Maximum Power Dissipation for Output Buffer Mode Configuration<br>Thermal Parameters with No Heat Sink or Airflow<br>Thermal Parameters with Forced Airflow and<br>No Heat Sink for the MC68040                                                                                                                                                                                                                                             | 11-17                                                                    |

| 11-4<br>11-5<br>11-6                                                        | Thermal Parameters with Forced Airflow and<br>No Heat Sink for the MC68LC040 and MC68EC040<br>Thermal Parameters with Heat Sink and No Airflow<br>Thermal Parameters with Heat Sink and Airflow                                                                                                                                                                                                                                             | 11-21                                                                    |

| C-1<br>C-2<br>C-3                                                           | Additional MC68040V and MC68EC040V Signals<br>Bus Encodings During LPSTOP Broadcast Cycle<br>IEEE Standard 1149.1A Instructions                                                                                                                                                                                                                                                                                                             | C-4                                                                      |

| E-1<br>E-2<br>E-3<br>E-4                                                    | MC68040 Floating-Point Instructions<br>MC68040FPSP Floating-Point Instructions<br>Support for Data Types and Data Formats<br>Exception Conditions                                                                                                                                                                                                                                                                                           | E-3<br>E-4                                                               |

### **1.7 DATA FORMAT SUMMARY**

The M68040 supports the basic data formats of the M68000 family. Some data formats apply only to the IU, some only to the FPU, and some to both. In addition, the instruction set supports operations on other data formats such as memory addresses.

The operand data formats supported by the IU are the standard twos-complement data formats defined in the M68000 family architecture plus a new data format (16-byte block) for the MOVE16 instruction. Registers, memory, or instructions themselves can contain IU operands. The operand size for each instruction is either explicitly encoded in the instruction or implicitly defined by the instruction operation.

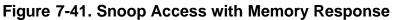

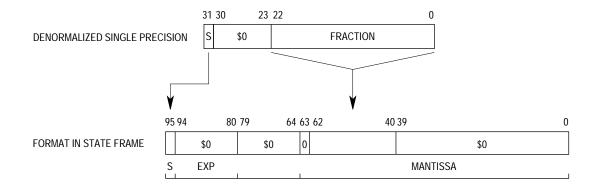

Whenever an integer is used in a floating-point operation, the FPU automatically converts it to an extended-precision floating-point number before using the integer. The FPU implements single- and double-precision floating-point data formats as defined by the IEEE 754 standard. The FPU does not directly support packed decimal real format. However, by trapping as an unimplemented data format instead of as an illegal instruction, software emulation supports the packed decimal format. Additionally, each data format has a special encoding that represents one of five data types: normalized numbers, denormalized numbers, zeros, infinities, and not-a-numbers (NANs). Table 1-1 lists the data formats for both the IU and the FPU. Refer to M68000PM/AD, *M68000 Family Programmer's Reference Manual,* for details on data format organization in registers and memory.

| Operand Data Format        | Size      | Supported In | Notes                                         |

|----------------------------|-----------|--------------|-----------------------------------------------|

| Bit                        | 1 Bit     | IJ           | —                                             |

| Bit Field                  | 1–32 Bits | U            | Field of Consecutive Bits                     |

| Binary-Coded Decimal (BCD) | 8 Bits    | U            | Packed: 2 Digits/Byte; Unpacked: 1 Digit/Byte |

| Byte Integer               | 8 Bits    | IU, FPU      | —                                             |

| Word Integer               | 16 Bits   | IU, FPU      | —                                             |

| Long-Word Integer          | 32 Bits   | IU, FPU      | —                                             |

| Quad-Word Integer          | 64 Bits   | IJ           | Any Two Data Registers                        |

| 16-Byte                    | 128 Bits  | IJ           | Memory Only, Aligned to 16-Byte Boundary      |

| Single-Precision Real      | 32 Bits   | FPU          | 1-Bit Sign, 8-Bit Exponent, 23-Bit Fraction   |

| Double-Precision Real      | 64 Bits   | FPU          | 1-Bit Sign, 11-Bit Exponent, 52-Bit Fraction  |

| Extended-Precision Real    | 80 Bits   | FPU          | 1-Bit Sign, 15-Bit Exponent, 64-Bit Mantissa  |

Table 1-1. M68040 Data Formats

### **1.8 ADDRESSING CAPABILITIES SUMMARY**

The M68040 supports the basic addressing modes of the M68000 family. The register indirect addressing modes support postincrement, predecrement, offset, and indexing, which are particularly useful for handling data structures common to sophisticated

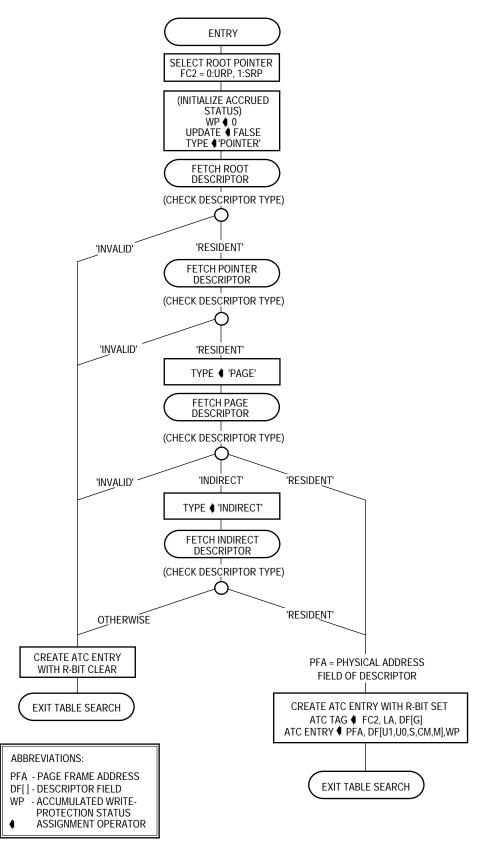

Figure 3-9. Detailed Flowchart of Table Search Operation

### **3.2.6 Address Translation Protection**

The M68040 MMUs provide separate translation tables for supervisor and user address spaces. The translation tables contain both mapping and protection information. Each table and page descriptor includes a write-protect (W) bit that can be set to provide write protection at any level. Page descriptors also contain a supervisor-only (S) bit that can limit access to programs operating at the supervisor privilege level.

The protection mechanisms can be used individually or in any combination to protect:

- Supervisor address space from accesses by user programs.

- User address space from accesses by other user programs.

- Supervisor and user program spaces from write accesses (implicitly supported by designating all memory pages used for program storage as write protected).

- One or more pages of memory from write accesses.

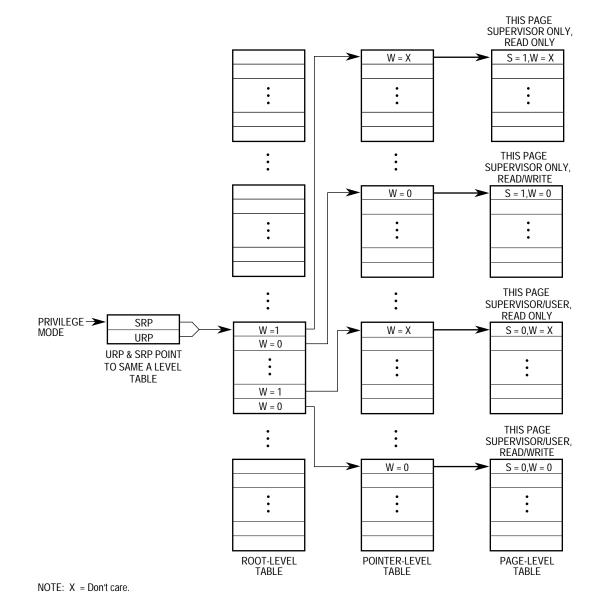

**3.2.6.1 SUPERVISOR AND USER TRANSLATION TABLES.** One way of protecting supervisor and user address spaces from unauthorized accesses is to use separate supervisor and user translation tables. Separate trees protect supervisor programs and data from accesses by user programs and user programs and data from accesses by supervisor programs. Access is granted to the supervisor programs that can accesses any area of memory with MOVES. The translation table pointed to by the SRP is selected for all other supervisor mode accesses. This translation table can be common to all tasks. Figure 3-17 illustrates separate translation tables for supervisor accesses and for two user tasks that share the common supervisor space. Each user task has an translation table with unique mappings for the logical addresses in its user address space.

**3.2.6.2 SUPERVISOR ONLY.** A second mechanism protects supervisor programs and data without requiring segmenting of the logical address space into supervisor and user address spaces. Page descriptors contain S-bits to protect areas of memory from access by user programs. When a table search for a user access encounters an S-bit set in a page descriptor, the table search ends, and an ATC descriptor corresponding to the logical address is created with the S-bit set. A subsequent retry of the user access results in an access error exception being taken. The S-bit can be used to protect one or more pages from user program access. Supervisor and user mode accesses can share descriptors by using indirect descriptors or by sharing tables. The entire user and supervisor address spaces can be mapped together by loading the same root pointer address into both the SRP and URP registers.

Figure 3-19. Translation Table Using S-Bit and W-Bit To Set Protection

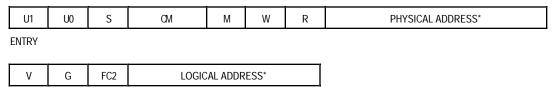

Each ATC entry consists of a physical address, attribute information from a corresponding page descriptor, and a tag that contains a logical address and status information. Figure 3-21, which illustrates the entry and tag fields, is followed by field definitions listed in alphabetical order.

TAG

\* For 4-Kbyte page sizes this field uses address bits 31–12; for 8-Kbyte page sizes, bits 31–13.

### Figure 3-21. ATC Entry and Tag Fields

#### CM—Cache Mode

This field selects the cache mode and accesses serialization as follows:

- 00 = Cachable, Write-through

- 01 = Cachable, Copyback

- 10 = Noncachable, Serialized

- 11 = Noncachable

Section 4 Instruction and Data Caches provides detailed information on caching modes, and Section 7 Bus Operation provides information on serialization.

#### FC2—Function Code Bit 2 (Supervisor/User)

This bit contains the function code corresponding to the logical address in this entry. FC2 is set for supervisor mode accesses and cleared for user mode accesses.

#### G—Global

When set, this bit indicates the entry is global. Global entries are not invalidated by the PFLUSH instruction variants that specify nonglobal entries, even when all other selection criteria are satisfied.

#### Logical Address

This 13-bit field contains the most significant logical address bits for this entry. All 16 bits of this field are used in the comparison of this entry to an incoming logical address when the page size is 4 Kbytes. For 8-Kbytes pages, the least significant bit of this field is ignored.

#### M-Modified

The modified bit is set when a valid write access to the logical address corresponding to the entry occurs. If the M-bit is clear and a write access to this logical address is attempted, the M68040 suspends the access, initiates a table search to set the M-bit in the page descriptor, and writes over the old ATC entry with the current page descriptor information. The MMU then allows the original write access to be performed. This

# SECTION 4 INSTRUCTION AND DATA CACHES

#### NOTE

Ignore all references to the memory management unit (MMU) when reading for the MC68EC040 and MC68EC040V. The functionality of the MC68040 transparent translation registers has been changed in the MC68EC040 and MC68EC040V to the access control registers. Refer to **Appendix B MC68EC040** for details.

The M68040 contains two independent, 4-Kbyte, on-chip caches located in the physical address space. Accessing instruction words and data simultaneously through separate caches increases instruction throughput. The M68040 caches improve system performance by providing cached data to the on-chip execution unit with very low latency. Systems with an alternate bus master receive increased bus availability.

Figure 4-1 illustrates the instruction and data caches contained in the instruction and data memory units. The appropriate memory unit independently services instruction prefetch and data requests from the integer unit (IU). The memory units translate the logical address in parallel with indexing into the cache. If the translated address matches one of the cache entries, the access hits in the cache. For a read operation, the memory unit supplies the data to the IU, and for a write operation, the memory unit updates the cache. If the access does not match one of the cache entries (misses in the cache) or a write access must be written through to memory, the memory unit sends an external bus request to the bus controller. The bus controller then reads or writes the required data.

Cache coherency in the M68040 is optimized for multimaster applications in which the M68040 is the caching master sharing memory with one or more noncaching masters (such as DMA controllers). The M68040 implements a bus snooper that maintains cache coherency by monitoring an alternate bus master's access and performing cache maintenance operations as requested by the alternate bus master. Matching cache entries can be invalidated during the alternate bus master's access to memory, or memory can be inhibited to allow the M68040 to respond to the access as a slave. For an external write operation, the processor can intervene in the access and update its internal caches (sink data). For an external read operation, the processor supplies cached data to the alternate bus muster (source data). This prevents the M68040 caches from accumulating old or invalid copies of data (stale data). Alternate bus masters are allowed access to locally modified data within the caches that is no longer consistent with external memory (dirty data). Allowing memory pages to be specified as write-through instead of copyback also supports cache coherency. When a processor writes to write-through pages, external

### 5.8.2 Interrupt Pending Status (IPEND)

This output signal indicates that an interrupt request has been recognized internally and exceeds the current interrupt priority mask in the status register (SR). External devices (other bus masters) can use IPEND to predict processor operation on the next instruction boundaries. IPEND is not intended for use as an interrupt acknowledge to external peripheral devices. Refer to Section 7 Bus Operation for bus information related to interrupts and to Section 8 Exception Processing for interrupt information.

### 5.8.3 Autovector (AVEC)

This input signal is asserted with TA during an interrupt acknowledge transfer to request internal generation of the vector number. Refer to **Section 7 Bus Operation** for more information about automatic vectors.

### 5.9 STATUS AND CLOCK SIGNALS

The following paragraphs explain the signals that provide timing, test control, and the internal processor status.

### 5.9.1 Processor Status (PST3–PST0)

These outputs indicate the internal execution unit's status. The timing is synchronous with BCLK, and the status may have nothing to do with the current bus transfer. The PSTx signal is updated depending on the type of PSTx encoding. There are two classes of PSTx encodings. The first class is associated with instruction boundaries, and the second class indicates the processor's present status. Table 5-6 lists the definition of the encodings.

The encodings 0, 8, 4, 5, C, D, E, and F indicate the present status and do not reflect a specific stage of the pipe. These encodings persist as long as the processor stays in the indicated state. The default encoding 0 (user) or 8 (supervisor) is indicated if none of the above conditions apply. The encodings 1, 2, 3, 9, A, and B belong to the first class of PSTx encoding. This class indicates that the instruction is in its last instruction execution stage. These encodings exist for only one BCLK period per instruction and are mutually exclusive.

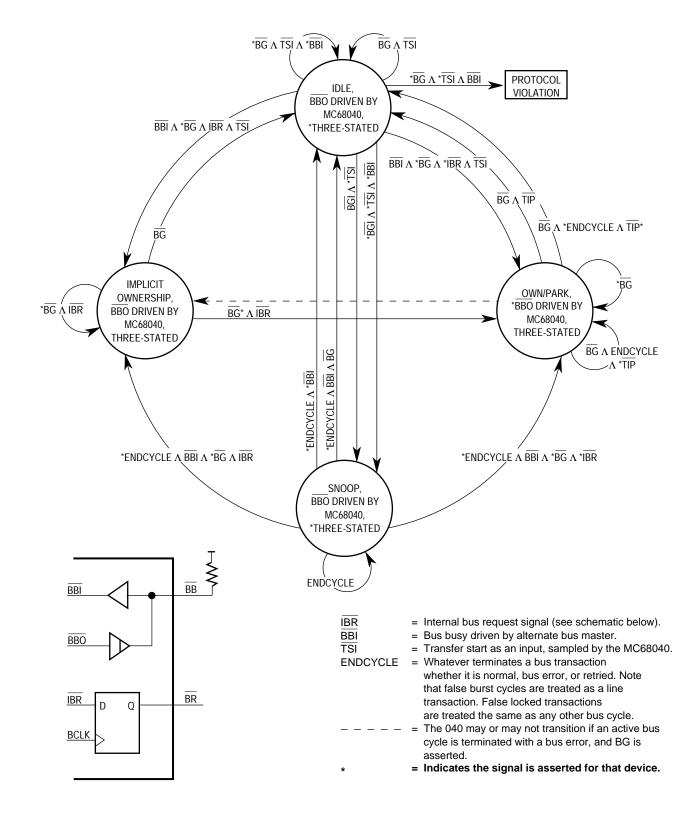

Figure 7-30. M68040 Internal Interpretation State Diagram and External Bus Arbiter Circuit

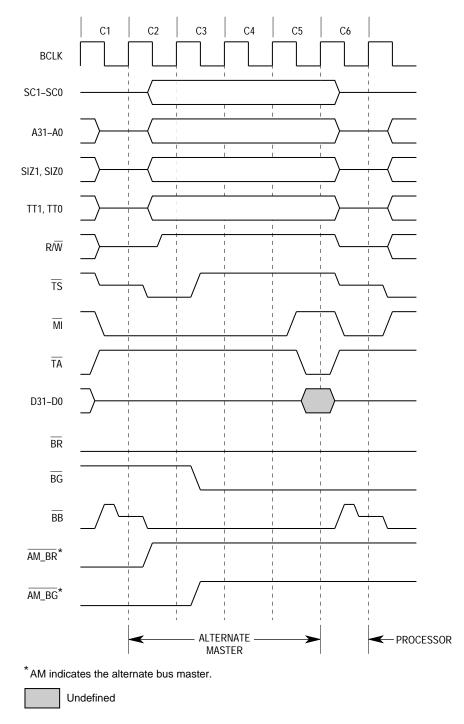

illustrated, which results in a memory access having the equivalent of two wait states. Variations in the timing required by snooping logic to access the caches can delay the negation of  $\overline{\text{MI}}$  by up to two additional clocks. External logic must ensure that the termination signals negate at all rising BCLK edges in which  $\overline{\text{MI}}$  is asserted. Otherwise, if one of the termination signals is asserted, either the M68040 ignores all termination signals, reading them as negated, or the M68040 exhibits improper operation.

| Mnemonic | Definition                    | Equation                          | Predicate | BSUN Bit Set |

|----------|-------------------------------|-----------------------------------|-----------|--------------|

|          | IEEE I                        | Nonaware Tests                    |           |              |

| EQ       | Equal                         | Z                                 | 000001    | No           |

| NE       | Not Equal                     | Z                                 | 001110    | No           |

| GT       | Greater Than                  | NAN V Z V N                       | 010010    | Yes          |

| NGT      | Not Greater Than              | NAN V Z V N                       | 011101    | Yes          |

| GE       | Greater Than or Equal         | Z V (NAN V N)                     | 010011    | Yes          |

| NGE      | Not Greater Than or Equal     | NAN V (Ν Λ Ζ)                     | 011100    | Yes          |

| LT       | Less Than                     | $N \Lambda (\overline{NAN V Z})$  | 010100    | Yes          |

| NLT      | Not Less Than                 | NAN V (Z V N)                     | 011011    | Yes          |

| LE       | Less Than or Equal            | $Z V (N \Lambda \overline{NAN})$  | 010101    | Yes          |

| NLE      | Not Less Than or Equal        | NAN V (N VZ)                      | 011010    | Yes          |

| GL       | Greater or Less Than          | NAN V Z                           | 010110    | Yes          |

| NGL      | Not Greater or Less Than      | NAN V Z                           | 011001    | Yes          |

| GLE      | Greater, Less, or Equal       | NAN                               | 010111    | Yes          |

| NGLE     | Not Greater, Less, or Equal   | NAN                               | 011000    | Yes          |

|          | IEEE                          | E Aware Tests                     |           |              |

| EQ       | Equal                         | Z                                 | 000001    | No           |

| NE       | Not Equal                     | Z                                 | 001110    | No           |

| OGT      | Ordered Greater Than          | NAN V Z V N                       | 000010    | No           |

| ULE      | Unordered or Less or Equal    | NAN V Z V N                       | 001101    | No           |

| OGE      | Ordered Greater Than or Equal | Z V (NAN V N)                     | 000011    | No           |

| ULT      | Unordered or Less Than        | NAN V (N $\Lambda \overline{Z}$ ) | 001100    | No           |

| OLT      | Ordered Less Than             | $N \Lambda (\overline{NAN V Z})$  | 000100    | No           |

| UGE      | Unordered or Greater or Equal | NAN V Z V N                       | 001011    | No           |

| OLE      | Ordered Less Than or Equal    | $Z V (N \Lambda \overline{NAN})$  | 000101    | No           |

| UGT      | Unordered or Greater Than     | NAN V (N V Z)                     | 001010    | No           |

| OGL      | Ordered Greater or Less Than  | NAN V Z                           | 000110    | No           |

| UEQ      | Unordered or Equal            | NAN V Z                           | 001001    | No           |

| OR       | Ordered                       | NAN                               | 000111    | No           |

| UN       | Unordered                     | NAN                               | 001000    | No           |

|          | Misce                         | llaneous Tests                    |           |              |

| F        | False                         | False                             | 000000    | No           |

| Т        | True                          | True                              | 001111    | No           |

| SF       | Signaling False               | False                             | 010000    | Yes          |

| ST       | Signaling True                | True                              | 011111    | Yes          |

| SEQ      | Signaling Equal               | Z                                 | 010001    | Yes          |

| SNE      | Signaling Not Equal           | Z                                 | 011110    | Yes          |

#### Table 9-8. Floating-Point Conditional Tests

NOTE: All condition codes with an overbar indicate cleared bits; all other bits are set.

# 9.7 FLOATING-POINT ARITHMETIC EXCEPTIONS

The following eight user floating-point arithmetic exceptions are listed in order of priority. The MC68040 generates the first seven exceptions in hardware and the eighth only in software.

- Branch/Set on Unordered (BSUN)

- Signaling Not-A-Number (SNAN)

- Operand Error (OPERR)

- Overflow (OVFL)

- Underflow (UNFL)

- Divide by Zero (DZ)

- Inexact 2 (INEX2)

- Inexact 1 (INEX1)

INEX1 exception is the condition that exists when a packed decimal operand cannot be converted exactly to the extended-precision format in the current rounding mode. Since

| FSAVE State<br>Frame Field | Contents                                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------------------------|

|                            | INEX (FMOVE to Register, FABS, and FNEG)                                                                        |

| CMDREG1B                   | Exception Instruction Command Word                                                                              |

| FPTEMP                     | Unrounded, Extended-Precision Intermediate Result                                                               |

| STAG                       | Source Operand Tag = Normalized                                                                                 |

| E1                         | Always 1                                                                                                        |

| Т                          | Always 0                                                                                                        |

|                            | INEX (FADD, FSUB, FMUL, FDIV, and FSQRT)                                                                        |

| CMDREG3B                   | Encoded Exception Instruction Command Word                                                                      |

| WBTEMP                     | WBTS, WBTE, and WBTM = intermediate result sign, biased 15-bit exponent, and 64-bit mantissa prior to rounding. |

| WBTE15                     | Either 1 or 0, generally useless for INEX exceptions.                                                           |

| WBTM1, WBTM0,<br>SBIT      | Guard, round, and sticky of intermediate result's 67-bit mantissa.                                              |

| E3                         | Always 1                                                                                                        |

| Т                          | Either 1 or 0                                                                                                   |

|                            | INEX (FMOVE to Memory)                                                                                          |

| CMDREG1B                   | FMOVE Instruction Command Word                                                                                  |

| FPTEMP                     | Intermediate result with mantissa prior to rounding.                                                            |

| STAG                       | Source Operand Tag = Normalized                                                                                 |

| E1                         | Always 1                                                                                                        |

| Т                          | Always 1                                                                                                        |

#### Table 9-16. State Frame Field Information (Concluded)

NOTE: If the M68040FPSP unimplemented exception handler is used, the above state frame information applies. The CMDREG1B or CMDREG3B fields of the state frame are modified as appropriate to encode the unimplemented instruction opcode. It is the user exception handler's responsibility to use the E3 and E1 field encodings to recognize which state frame information applies. When E3 = 1 and E1 = 1, E3 takes priority and the state frame information for E3 = 1 must be used.

| Instruction                     | Page     | Instruction           | Page  | Instruction | Page  |

|---------------------------------|----------|-----------------------|-------|-------------|-------|

| FSAVE <ea></ea>                 | 10-33    | MOVEP                 | 10-11 | ROL         | 10-26 |

| FScc                            | 10-32    | MOVEQ                 | 10-11 | ROR         | 10-26 |

| FSQRT                           | 10-30,36 | MOVES <ea>,An</ea>    | 10-24 | ROXL        | 10-27 |

| FSUB                            | 10-30,35 | MOVES <ea>,Dn</ea>    | 10-24 | ROXR        | 10-27 |

| FTRAPcc                         | 10-29    | MOVES Rn, <ea></ea>   | 10-24 | RTD         | 10-11 |

| FTST <ea>, FPn</ea>             | 10-30    | MULS.W/L              | 10-25 | RTE         | 10-11 |

| ILLEGAL                         | 10-11    | MULU.W/L              | 10-25 | RTR         | 10-11 |

| JMP                             | 10-20    | NBCD                  | 10-25 | RTS         | 10-11 |

| JSR                             | 10-21    | NEG                   | 10-26 | SBCD        | 10-11 |

| LEA                             | 10-21    | NEGX                  | 10-26 | Scc         | 10-27 |

| LINK                            | 10-11    | NOP                   | 10-11 | SUB         | 10-13 |

| LSL                             | 10-14    | NOT                   | 10-26 | SUBA        | 10-27 |

| LSR                             | 10-14    | OR                    | 10-13 | SUBI        | 10-13 |

| MOVE                            | 10-9,10  | ORI                   | 10-13 | SUBQ        | 10-14 |

| MOVE from CCR                   | 10-21    | ORI # <xxx>,CCR</xxx> | 10-11 | SUBX        | 10-11 |

| MOVE from SR                    | 10-22    | ORI # <xxx>,SR</xxx>  | 10-11 | SWAP        | 10-11 |

| MOVE to CCR                     | 10-22    | PACK                  | 10-11 | TAS         | 10-28 |

| MOVE to SR                      | 10-22    | PEA                   | 10-26 | TRAP#       | 10-11 |

| MOVE USP                        | 10-11    | PFLUSH                | 10-11 | TRAPcc      | 10-11 |

| MOVE16                          | 10-11    | PFLUSHA               | 10-11 | TRAPV       | 10-11 |

| MOVEA.L                         | 10-23    | PFLUSHAN              | 10-11 | TST         | 10-13 |

| MOVEC                           | 10-11    | PFLUSHN (An)          | 10-11 | UNLK        | 10-11 |

| MOVEM <list>,<ea></ea></list>   | 10-23    | PTESTR, PTESTW        | 10-11 | UNPK        | 10-11 |

| MOVEM.L <ea>,<list></list></ea> | 10-23    | RESET                 | 10-11 |             |       |

### Table 10.1. Instruction Timing Index (Continued)

Instructions using the brief and full extension word format addressing modes cause the <ea> calculate and execute stages to operate in an interlocked manner. When these instructions wait to begin execution in the execution stage, there is a similar increase in the <ea> calculate time. Figure 10-3 illustrates this effect for an ADD instruction using a brief format extension word. The ADD instruction stalls for two clocks waiting to enter the execution stage. Since this time exceeds by one clock the ADD lead time, the ADD instruction remains in the <ea> calculate stage for one additional clock. If the ADD instruction was in the execution stage for two clocks, the ABCD instruction would not have stalled in the <ea> calculate stage.

|                     | LABEL    | INSTRUCT       | TION        | <ea><br/>CALCULATE</ea> | EXECUTE |             |

|---------------------|----------|----------------|-------------|-------------------------|---------|-------------|

|                     | P1       | TRAPF          |             | 1                       | 1       |             |

|                     | A        |                | D0,D1       | 3                       | 3       |             |

|                     | B        |                | 4(A0,D3),D2 | 5                       | 1L + 4  |             |

|                     | N1<br>N2 | TRAPF<br>TRAPF |             | 1<br>1                  | 1       |             |

|                     | INZ      | INALL          |             | I                       | I I     |             |

|                     |          |                |             |                         |         |             |

|                     | C1 C2    | C3             | C4 C5       | C6 C7                   | C8 C9   | C10 C11 C12 |

| <ea> CALCULATE</ea> | P1 A     | В              | ВВ          | B* B                    | B N1    | N2          |

| <ea> FETCH</ea>     | P1       | A              | ВВ          | ВВ                      | ВВ      | N1 N2       |

| EXECUTE             |          | P1             | AA          | AB                      | ВВ      | B N1 N2     |

| WRITE-BACK          |          |                |             |                         |         |             |

NOTE: \*Possible stalls in this stage.

Figure 10-3. Interlocked Stages

12.2.1 MC68040 Pin Grid Array

| Т |                              | O<br>TDO                | $\frac{\circ}{\text{TRST}}$ | O<br>GND | $\frac{\circ}{\text{CDIS}}$ | $\frac{\circ}{\text{IPL2}}$                                | $\frac{\circ}{\text{IPL1}}$ | $\frac{\circ}{IPL0}$    | O<br>DLE  | O<br>TCI                   | $\frac{\circ}{\text{AVEC}}$ | ⊖<br>SC0 | $\frac{\bigcirc}{BG}$ | $\frac{\circ}{TA}$ | O<br>PST0           | O<br>PST3               | $\frac{\bigcirc}{BB}$ | $\frac{\bigcirc}{BR}$ |

|---|------------------------------|-------------------------|-----------------------------|----------|-----------------------------|------------------------------------------------------------|-----------------------------|-------------------------|-----------|----------------------------|-----------------------------|----------|-----------------------|--------------------|---------------------|-------------------------|-----------------------|-----------------------|

| S | $\frac{\circ}{\text{IPEND}}$ | O<br>GND                | O<br>TDI                    | о<br>тск | O<br>TMS                    | $\frac{\circ}{\text{MDIS}}$                                | $\frac{\circ}{\text{RSTI}}$ | $^{\circ}_{\rm V_{CC}}$ | O<br>GND  | O<br>GND                   | ⊖<br>TBI                    | O<br>SC1 | $\frac{\circ}{TEA}$   | O<br>PST1          | O<br>GND            | $^{\circ}_{\rm V_{CC}}$ | O<br>GND              |                       |

| R | $\frac{\circ}{\text{CIOUT}}$ | $^{\circ}_{\rm V_{CC}}$ | $\frac{\circ}{\text{RSTO}}$ | O<br>GND | ∘<br>V <sub>CC</sub>        | O<br>GND                                                   | O<br>BCLK                   | ∘<br>V <sub>CC</sub>    | O<br>PCLK | O<br>GND                   | O<br>GND                    | ∘<br>Vcc | O<br>GND              | O<br>PST2          | $\frac{\circ}{TIP}$ | $\frac{\circ}{TS}$      | °<br>V <sub>CC</sub>  |                       |

| Q | O<br>UPA1                    | O<br>GND                | O<br>UPA0                   |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | <u>○</u><br>MI          | O<br>GND              | O<br>TLN0             |

| Р | О<br>А10                     | O<br>TT1                | ○<br>TT0                    |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | O<br>SIZ1               | O<br>SIZO             | o<br>TLN1             |

| Ν | О<br>А12                     | O<br>GND                | О<br>А11                    |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | o<br>R/₩                | O<br>GND              | ○<br>TM0              |

| М | О<br>А13                     | °<br>V <sub>CC</sub>    | $^{\circ}_{\rm V_{CC}}$     |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | O<br>GND                | °<br>Vcc              | O<br>TM1              |

| L | О<br>А14                     | O<br>GND                | O<br>GND                    |          |                             | MC68040 PINOUT<br>(BOTTOM VIEW)<br>18 X 18 CAVITY DOWN PGA |                             |                         |           |                            |                             |          |                       |                    |                     | °<br>VCC                | O<br>GND              | О<br>А0               |

| К | О<br>А15                     | 0<br>A16                | O<br>GND                    |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | O<br>GND                | O<br>TM2              | О<br>А1               |

| J | О<br>А17                     | 0<br>A19                | $^{\circ}$ V <sub>CC</sub>  |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | $^{\circ}_{\rm V_{CC}}$ | О<br>А2               | О<br>АЗ               |

| Η | О<br>А18                     | O<br>GND                | $^{\circ}_{\rm V_{CC}}$     |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | ○<br>Vcc                | O<br>GND              | О<br>А4               |

| G | ○<br>A20                     | $^{\circ}_{\rm V_{CC}}$ | ○<br>A23                    |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | ○<br>A6                 | °<br>V <sub>CC</sub>  | О<br>А5               |

| F | О<br>А21                     | O<br>GND                | ○<br>A25                    |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | О<br>А9                 | O<br>GND              | О<br>А7               |

| Ε | О<br>А22                     | О<br>А26                | О<br>А28                    |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | 0<br>D29                | 0<br>D30              | 0<br>A8               |

| D | ○<br>A24                     | O<br>GND                | ○<br>A30                    |          |                             |                                                            |                             |                         |           |                            |                             |          |                       |                    |                     | ○<br>D27                | O<br>GND              | 0<br>D31              |

| С | О<br>А27                     | ∘<br>Vcc                | 0<br>D0                     | 0<br>D2  | $^{\circ}$ V <sub>CC</sub>  | O<br>GND                                                   | O<br>GND                    | $^{\circ}_{\rm V_{CC}}$ | o<br>GND  | $^{\circ}$ V <sub>CC</sub> | O<br>GND                    | o<br>Vcc | O<br>GND              | ○<br>Vcc           | O<br>D23            | ○<br>D25                | ○<br>Vcc              | ○<br>D28              |

| В | О<br>А29                     | O<br>GND                | 0<br>D1                     | O<br>GND | ∘<br>V <sub>CC</sub>        | o<br>GND                                                   | 0<br>D8                     | O<br>GND                | ∘<br>Vcc  | O<br>GND                   | O<br>D16                    | 0<br>D18 | O<br>GND              | °<br>Vcc           | O<br>GND            | 0<br>D22                | O<br>GND              | О<br>D26              |

| A | О<br>А31                     | 0<br>D3                 | 0<br>D4                     | О<br>D5  | О<br>D6                     | 0<br>D7                                                    | 0<br>D9                     | 0<br>D10                | 0<br>D11  | 0<br>D12                   | O<br>D13                    | 0<br>D14 | 0<br>D15              | 0<br>D17           | 0<br>D19            | 0<br>D20                | 0<br>D21              | О<br>D24              |

|   | 1                            | 2                       | 3                           | 4        | 5                           | 6                                                          | 7                           | 8                       | 9         | 10                         | 11                          | 12       | 13                    | 14                 | 15                  | 16                      | 17                    | 18                    |

| Pin Group      | GND                                                                                                          | V <sub>CC</sub>                                              |

|----------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| PLL            | S9, R6, R10                                                                                                  | R8, S8                                                       |

| Internal Logic | C6, C7, C9, C11, C13, K3, K16, L3, M16, R4,<br>R11, R13, S6, S10, T4                                         | C5, C8, C10, C12, C14, H3, H16, J3, J16, L16,<br>M3, R5, R12 |

| Output Drivers | B2, B4, B6, B8, B10, B13, B15, B17, D2, D17,<br>F2, F17, H2, H17, L2, L17, N2, N17, Q2, Q17,<br>S2, S15, S17 | B5, B9, B14, C2, C17, G2, G17, M2, M17, R2,<br>R17, S16      |

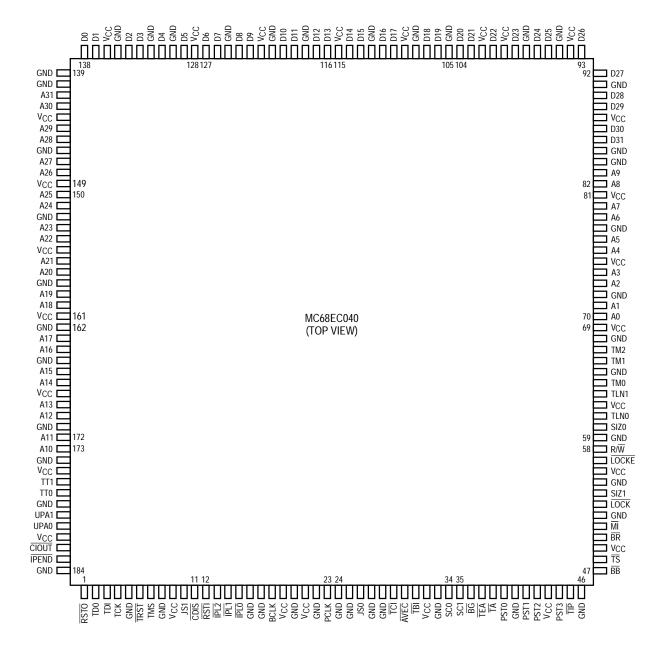

### 12.2.6 MC68EC040 Quad Flat Pack

### MC68EC040 184 Pin QFP Pin Assignment

| Pin Group      | GND                                                               | V <sub>CC</sub>                                             |

|----------------|-------------------------------------------------------------------|-------------------------------------------------------------|

| PLL            | 17, 22, 24                                                        | 19, 21                                                      |

| Internal Logic | 5, 8, 10, 27, 28, 33, 55, 68, 95, 108, 121, 162,<br>130, 135, 174 | 9, 32, 56, 69, 81, 94, 100, 109, 122, 136, 149,<br>161, 175 |

| Output Drivers |                                                                   | 43, 49, 62, 75, 88, 102, 115, 128, 143, 155, 168,<br>181    |

#### MC68LC040 REV2.3 (01/29/2000) L

#### A.6.6 A.6.7 Output AC Timing Specifications (see Figures A-5\* to A-9)

|     |                                                                                                  | 20 MHz |     | 25 MHz |     | 33  | MHz | 40 MHz |     | Unit |

|-----|--------------------------------------------------------------------------------------------------|--------|-----|--------|-----|-----|-----|--------|-----|------|

| Num | Characteristic                                                                                   | Min    | Мах | Min    | Max | Min | Мах | Min    | Max | Uni  |

| 11  | BCLK to Address, CIOUT, LOCK,<br>LOCKE, PSTx, R/W, SIZx,<br>TLNx,TMx, TTx, UPAx<br>Valid         | 11.5   | 35  | 9      | 30  | 6.5 | 25  | 5.25   | 24  | nS   |

| 12  | BCLK to Output Invalid (Output<br>Hold)                                                          | 11.5   | _   | 9      | _   | 6.5 | _   | 5.25   | _   | nS   |

| 13  | BCLK to TS Valid                                                                                 | 11.5   | 35  | 9      | 30  | 6.5 | 25  | 5.25   | 24  | nS   |

| 14  | BCLK to TIP Valid                                                                                | 11.5   | 35  | 9      | 30  | 6.5 | 25  | 5.25   | 24  | nS   |

| 18  | BCLK to Data-Out Valid                                                                           | 11.5   | 37  | 9      | 32  | 6.5 | 27  | 5.25   | 26  | nS   |

| 19  | BCLK to Data-Out Invalid (Output<br>Hold)                                                        | 11.5   | _   | 9      | _   | 6.5 | _   | 5.25   | _   | nS   |

| 20  | BCLK to Output Low Impedance                                                                     | 11.5   | _   | 9      | -   | 6.5 | _   | 5.25   | _   | nS   |

| 21  | BCLK to Data-Out High<br>Impedance                                                               | 11.5   | 25  | 9      | 20  | 6.5 | 17  | 5.25   | 16  | nS   |

| 38  | BCLK to Address, CIOUT, LOCK,<br>LOCKE, R/W, SIZx, TS, TLNx,<br>TMx, TTx, UPAx High<br>Impedance | 11.5   | 23  | 9      | 18  | 6.5 | 15  | 5.25   | 14  | nS   |

| 39  | BCLK to BB, TA, TIP High<br>Impedance                                                            | 23     | 33  | 19     | 28  | 14  | 25  | 11.5   | 22  | nS   |

| 40  | BCLK to BR, BB Valid                                                                             | 11.5   | 35  | 9      | 30  | 6.5 | 23  | 5.25   | 14  | nS   |

| 43  | BCLK to MI Valid                                                                                 | 11.5   | 35  | 9      | 30  | 6.5 | 25  | 5.25   | 24  | nS   |

| 48  | BCLK to TA Valid                                                                                 | 11.5   | 35  | 9      | 30  | 6.5 | 25  | 5.25   | 24  | nS   |

| 50  | BCLK to IPEND, PSTx, RSTO<br>Valid                                                               | 11.5   | 35  | 9      | 30  | 6.5 | 25  | 5.25   | 24  | nS   |

\*Output timing is specified for a valid signal measured at the pin. Timing is specified driving an unterminated 30- $\Omega$ transmission line with a length characterized by a 2.5-nS one-way propagation delay. Buffer output impedance is typically 30  $\Omega$ ; the buffer specifications include approximately 5 nS for the signal to propagate the length of the transmission line and back.

|             |                                                    | Applies To |         |         |

|-------------|----------------------------------------------------|------------|---------|---------|

| Instruction | Notes                                              | MC68020    | MC68030 | MC68040 |

| MOVE16      | New Instruction                                    |            |         |         |

| MOVEC       | Supports New Control Registers                     |            |         |         |

| MULS, MULU  | Supports 32-Bit Operands                           |            |         |         |

| PACK        | New Instruction                                    |            |         |         |

| PFLUSH      | MMU Instruction                                    |            |         |         |

| PLOAD       | MMU Instruction                                    |            |         |         |

| PMOVE       | MMU Instruction                                    |            |         |         |

| PTEST       | MMU Instruction                                    |            |         |         |

| RTM         | New Instruction                                    |            |         |         |

| TST         | Supports Program Counter Relative Addressing Modes |            |         |         |

| TRAPcc      | New Instruction                                    |            |         |         |

| UNPK        | New Instruction                                    |            |         |         |

### MC68020, MC68030, and MC68040 Instruction Set Extensions (Continued)