Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorSTM8Core Size8-BitSpeed16MHzConnectivityPC, IrDA, LINbus, SPI, UART/USARTProipheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O38Program Memory Size32KB (32K × 8)Program Memory TypeFLASHEEPROM Size128 × 8Valdage - Supply (Vcc/Vdd)295 ∨ 5.5∨National ConvertersAD 10x10bOperating Temperature40°C ~ 85°C (TA)Mounting TypeSuface MountProkage / Case48-LQFP (XCC)Prokage / Case48-LQFP (XCC)Prokage / Case48-LQFP (XCC)Prokage Num48-LQFP (XCC)Prokage Num48-LQFP (XCC)Prokage NumHutps://www.exfl.com/product-detail/stmicroelectronics/stm805056tbf | Details                    |                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|

| Core Size8-BitSpeed16MHzConnectivityPC, IrDA, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O38Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size2x X 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPAll LQFP (7x7)18-100000000000000000000000000000000000                                                                                                                                                             | Product Status             | Active                                                                 |

| Speed16MHzConnectivityPC, IrDA, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O38Program Memory Size32KB (32K × 8)Program Memory TypeFLASHEEPROM Size128 × 8RAM Size2K × 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature4.0°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7)                                                                                                                                                                                                   | Core Processor             | STM8                                                                   |

| ConnectivityPC, IrDA, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O38Program Memory Size32KB (32K × 8)Program Memory TypeFLASHEEPROM Size128 × 8RAM Size2K × 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7)                                                                                                                                                                                                                                    | Core Size                  | 8-Bit                                                                  |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O38Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2,95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7)                                                                                                                                                                                                                                                          | Speed                      | 16MHz                                                                  |

| Number of I/O38Program Memory Size32KB (32K × 8)Program Memory TypeFLASHEEPROM Size128 × 8RAM Size2K × 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                            | Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature4.0°C ~ 85°C (TA)Mounting Type8L-QFPSuppler Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                        | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Program Memory TypeFLASHEEPROM Size128 x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                            | Number of I/O              | 38                                                                     |

| EEPROM Size128 × 8RAM Size2K × 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                    | Program Memory Size        | 32KB (32K x 8)                                                         |

| RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                      | Program Memory Type        | FLASH                                                                  |

| Voltage - Supply (Vcc/Vdd)2.95V ~ 5.5VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                    | EEPROM Size                | 128 x 8                                                                |

| Data ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                          | RAM Size                   | 2K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Converters            | A/D 10x10b                                                             |

| Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Oscillator Type            | Internal                                                               |

| Package / Case     48-LQFP       Supplier Device Package     48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Supplier Device Package     48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mounting Type              | Surface Mount                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Package / Case             | 48-LQFP                                                                |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s005c6t6tr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supplier Device Package    | 48-LQFP (7x7)                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s005c6t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

13

| 12.2  | Software tools                   | 95             |

|-------|----------------------------------|----------------|

|       | 12.2.1 STM8 toolset              | <i>)</i> 5     |

|       | 12.2.2 C and assembly toolchains | <del>)</del> 5 |

| 12.3  | Programming tools                | 95             |

| Revis | on history9                      | 6              |

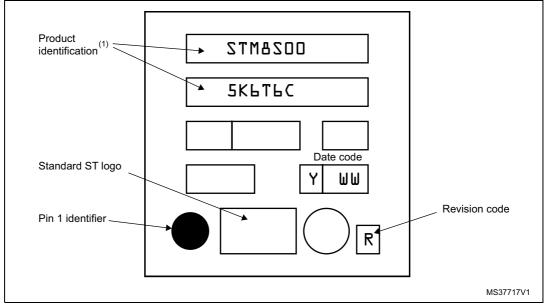

| Figure 49. | LQFP32 marking example (package top view)                           | . 90 |

|------------|---------------------------------------------------------------------|------|

| Figure 50. | STM8S005C6/K6 value line ordering information scheme <sup>(1)</sup> | . 93 |

# 4 **Product overview**

The following section intends to give an overview of the basic features of the STM8S005C6/K6 value line functional modules and peripherals.

For more detailed information please refer to the corresponding family reference manual (RM0016).

# 4.1 Central processing unit STM8

The 8-bit STM8 core is designed for code efficiency and performance.

It contains six internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing and 80 instructions.

### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching for most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16-Mbyte linear memory space

- 16-bit stack pointer access to a 64 K-level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for look-up tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

### 4.14.1 UART2

#### **Main features**

- 1 Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN master mode

- Single wire half duplex mode

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

#### LIN master mode

- Emission: generates 13-bit synch. break frame

- Reception: detects 11-bit break frame

### LIN slave mode

- Autonomous header handling one-single interrupt per valid message header

- Automatic baud rate synchronization maximum tolerated initial clock deviation ± 15%

- Synch. delimiter checking

- 11-bit LIN synch. break detection break detection always active

- Parity check on the LIN identifier field

- LIN error management

- Hot plugging support

### 4.14.2 SPI

- Maximum speed: 8 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

# 4.14.3 I<sup>2</sup>C

- I<sup>2</sup>C master features

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds

- Standard speed (up to 100 kHz)

- Fast speed (up to 400 kHz)

| Table 8. General hardware register map (continued) |                  |                                                          |                                            |                     |  |  |

|----------------------------------------------------|------------------|----------------------------------------------------------|--------------------------------------------|---------------------|--|--|

| Address                                            | Block            | Register label                                           | Register name                              | Reset<br>status     |  |  |

| 0x00 50CC                                          |                  | CLK_HSITRIMR                                             | HSI clock calibration trimming register    | 0x00                |  |  |

| 0x00 50CD                                          | CLK              | CLK_SWIMCCR                                              | SWIM clock control register                | 0bXXXX<br>XXX0      |  |  |

| 0x00 50CE to<br>0x00 50D0                          |                  |                                                          | Reserved area (3 bytes)                    |                     |  |  |

| 0x00 50D1                                          | WWDG             | WWDG_CR                                                  | WWDG control register                      | 0x7F                |  |  |

| 0x00 50D2                                          | - WWDG           | WWDG_WR                                                  | WWDR window register                       | 0x7F                |  |  |

| 0x00 50D3 to<br>0x00 50DF                          |                  |                                                          | Reserved area (13 bytes)                   |                     |  |  |

| 0x00 50E0                                          |                  | IWDG_KR                                                  | IWDG key register                          | 0xXX <sup>(2)</sup> |  |  |

| 0x00 50E1                                          | IWDG             | IWDG_PR                                                  | IWDG prescaler register                    | 0x00                |  |  |

| 0x00 50E2                                          |                  | IWDG_RLR                                                 | IWDG reload register                       | 0xFF                |  |  |

| 0x00 50E3 to<br>0x00 50EF                          |                  |                                                          | Reserved area (13 bytes)                   |                     |  |  |

| 0x00 50F0                                          |                  | AWU_CSR1                                                 | AWU control/status register 1              | 0x00                |  |  |

| 0x00 50F1                                          | AWU              | AWU_APR                                                  | AWU asynchronous prescaler buffer register | 0x3F                |  |  |

| 0x00 50F2                                          |                  | AWU_TBR                                                  | R AWU timebase selection register          |                     |  |  |

| 0x00 50F3                                          | BEEP             | BEEP_CSR                                                 | BEEP control/status register               | 0x1F                |  |  |

| 0x00 50F4 to<br>0x00 50FF                          |                  |                                                          | Reserved area (12 bytes)                   |                     |  |  |

| 0x00 5200                                          |                  | SPI_CR1                                                  | SPI_CR1 SPI control register 1             |                     |  |  |

| 0x00 5201                                          |                  | SPI_CR2                                                  | SPI control register 2                     | 0x00                |  |  |

| 0x00 5202                                          |                  | SPI_ICR                                                  | SPI interrupt control register             | 0x00                |  |  |

| 0x00 5203                                          | SPI              | SPI_SR                                                   | SPI status register                        | 0x02                |  |  |

| 0x00 5204                                          | 351              | SPI_DR                                                   | SPI data register                          | 0x00                |  |  |

| 0x00 5205                                          |                  | SPI_CRCPR                                                | SPI CRC polynomial register                | 0x07                |  |  |

| 0x00 5206                                          |                  | SPI_RXCRCR                                               | SPI Rx CRC register                        | 0xFF                |  |  |

| 0x00 5207                                          |                  | SPI_TXCRCR                                               | SPI Tx CRC register                        | 0xFF                |  |  |

| 0x00 5208 to<br>0x00 520F                          |                  |                                                          | Reserved area (8 bytes)                    |                     |  |  |

| 0x00 5210                                          |                  | I2C_CR1                                                  | I <sup>2</sup> C control register 1        | 0x00                |  |  |

| 0x00 5211                                          |                  | I2C_CR2                                                  | I <sup>2</sup> C control register 2        | 0x00                |  |  |

| 0x00 5212                                          | I <sup>2</sup> C | I2C_FREQR                                                | I <sup>2</sup> C frequency register        | 0x00                |  |  |

| 0x00 5213                                          |                  | I2C_OARL I <sup>2</sup> C own address register low 0x00  |                                            |                     |  |  |

| 0x00 5214                                          |                  | I2C_OARH I <sup>2</sup> C own address register high 0x00 |                                            |                     |  |  |

| 0x00 5215                                          |                  | Reserved                                                 |                                            |                     |  |  |

Table 8. General hardware register map (continued)

DocID022186 Rev 4

| Table 8. General nardware register map (continued)         Reset |       |                                                   |                                         |      |

|------------------------------------------------------------------|-------|---------------------------------------------------|-----------------------------------------|------|

| Address                                                          | Block | Register label                                    | Register label Register name            |      |

| 0x00 5300                                                        |       | TIM2_CR1                                          | TIM2 control register 1                 | 0x00 |

| 0x00 5301                                                        |       | TIM2_IER                                          | TIM2 interrupt enable register          | 0x00 |

| 0x00 5302                                                        |       | TIM2_SR1                                          | TIM2 status register 1                  | 0x00 |

| 0x00 5303                                                        | -     | TIM2_SR2                                          | TIM2 status register 2                  | 0x00 |

| 0x00 5304                                                        |       | TIM2_EGR                                          | TIM2 event generation register          | 0x00 |

| 0x00 5305                                                        |       | TIM2_CCMR1                                        | TIM2 capture/compare mode register 1    | 0x00 |

| 0x00 5306                                                        |       | TIM2_CCMR2                                        | TIM2 capture/compare mode register 2    | 0x00 |

| 0x00 5307                                                        |       | TIM2_CCMR3                                        | TIM2 capture/compare mode register 3    | 0x00 |

| 0x00 5308                                                        |       | TIM2_CCER1                                        | TIM2 capture/compare enable register 1  | 0x00 |

| 0x00 5309                                                        |       | TIM2_CCER2                                        | TIM2 capture/compare enable register 2  | 0x00 |

| 0x00 530A                                                        | TIM2  | TIM2_CNTRH                                        | TIM2 counter high                       | 0x00 |

| 0x00 530B                                                        |       | TIM2_CNTRL                                        | TIM2 counter low                        | 0x00 |

| 00 530C0x                                                        |       | TIM2_PSCR                                         | TIM2 prescaler register                 | 0x00 |

| 0x00 530D                                                        |       | TIM2_ARRH                                         | TIM2 auto-reload register high          | 0xFF |

| 0x00 530E                                                        |       | TIM2_ARRL                                         | TIM2_ARRL TIM2 auto-reload register low |      |

| 0x00 530F                                                        |       | TIM2_CCR1H                                        | TIM2 capture/compare register 1 high    | 0x00 |

| 0x00 5310                                                        |       | TIM2_CCR1L                                        | TIM2 capture/compare register 1 low     | 0x00 |

| 0x00 5311                                                        |       | TIM2_CCR2H                                        | TIM2 capture/compare reg. 2 high        | 0x00 |

| 0x00 5312                                                        |       | TIM2_CCR2L                                        | TIM2 capture/compare register 2 low     | 0x00 |

| 0x00 5313                                                        |       | TIM2_CCR3H                                        | TIM2 capture/compare register 3 high    | 0x00 |

| 0x00 5314                                                        |       | TIM2_CCR3L TIM2 capture/compare register 3 low    |                                         | 0x00 |

| 0x00 5315 to<br>0x00 531F                                        |       | I                                                 | Reserved area (11 bytes)                | ·    |

| 0x00 5320                                                        |       | TIM3_CR1                                          | TIM3 control register 1                 | 0x00 |

| 0x00 5321                                                        |       | TIM3_IER                                          | TIM3 interrupt enable register          | 0x00 |

| 0x00 5322                                                        |       | TIM3_SR1                                          | TIM3 status register 1                  | 0x00 |

| 0x00 5323                                                        |       | TIM3_SR2                                          | TIM3 status register 2                  | 0x00 |

| 0x00 5324                                                        |       | TIM3_EGR                                          | TIM3 event generation register          | 0x00 |

| 0x00 5325                                                        | ТІМЗ  | TIM3_CCMR1                                        | TIM3 capture/compare mode register 1    | 0x00 |

| 0x00 5326                                                        |       | TIM3_CCMR2 TIM3 capture/compare mode register 2   |                                         | 0x00 |

| 0x00 5327                                                        |       | TIM3_CCER1 TIM3 capture/compare enable register 1 |                                         | 0x00 |

| 0x00 5328                                                        | -     | TIM3_CNTRH                                        | NTRH TIM3 counter high                  |      |

| 0x00 5329                                                        |       | TIM3_CNTRL                                        | TIM3 counter low                        | 0x00 |

| 0x00 532A                                                        | -     | TIM3_PSCR                                         | TIM3 prescaler register                 | 0x00 |

| Table 8 | General | hardware     | register | man | (continued) | 1 |

|---------|---------|--------------|----------|-----|-------------|---|

|         | Concrai | inal a wai c | regioter | map | loonanaca   | , |

### STM8S005C6 STM8S005K6

- 1. Depends on the previous reset source.

- 2. Write only register.

| Address                   | Block                    | Register Label                                  | Register Name                          | Reset<br>Status |  |

|---------------------------|--------------------------|-------------------------------------------------|----------------------------------------|-----------------|--|

| 0x00 7F00                 |                          | A                                               | Accumulator                            | 0x00            |  |

| 0x00 7F01                 |                          | PCE                                             | Program counter extended               | 0x00            |  |

| 0x00 7F02                 |                          | PCH                                             | Program counter high                   | 0x00            |  |

| 0x00 7F03                 |                          | PCL                                             | Program counter low                    | 0x00            |  |

| 0x00 7F04                 |                          | ХН                                              | X index register high                  | 0x00            |  |

| 0x00 7F05                 | CPU <sup>(1)</sup>       | XL                                              | X index register low                   | 0x00            |  |

| 0x00 7F06                 |                          | YH                                              | Y index register high                  | 0x00            |  |

| 0x00 7F07                 |                          | YL                                              | Y index register low                   | 0x00            |  |

| 0x00 7F08                 |                          | SPH                                             | Stack pointer high                     | 0x17            |  |

| 0x00 7F09                 |                          | SPL Stack pointer low                           |                                        | 0xFF            |  |

| 0x00 7F0A                 |                          | CCR Condition code register                     |                                        | 0x28            |  |

| 0x00 7F0B to<br>0x00 7F5F | Reserved area (85 bytes) |                                                 |                                        |                 |  |

| 0x00 7F60                 | CPU                      | CFG_GCR                                         | Global configuration register          | 0x00            |  |

| 0x00 7F70                 |                          | ITC_SPR1 Interrupt software priority register 1 |                                        | 0xFF            |  |

| 0x00 7F71                 |                          | ITC_SPR2                                        | Interrupt software priority register 2 | 0xFF            |  |

| 0x00 7F72                 |                          | ITC_SPR3                                        |                                        |                 |  |

| 0x00 7F73                 | ITC                      | ITC_SPR4                                        | Interrupt software priority register 4 | 0xFF            |  |

| 0x00 7F74                 | ne                       | ITC_SPR5                                        | Interrupt software priority register 5 | 0xFF            |  |

| 0x00 7F75                 |                          | ITC_SPR6                                        | Interrupt software priority register 6 | 0xFF            |  |

| 0x00 7F76                 |                          | ITC_SPR7                                        | Interrupt software priority register 7 | 0xFF            |  |

| 0x00 7F77                 |                          | ITC_SPR8                                        | Interrupt software priority register 8 | 0xFF            |  |

| 0x00 7F78 to<br>0x00 7F79 | Reserved area (2 bytes)  |                                                 |                                        |                 |  |

| 0x00 7F80                 | SWIM                     | SWIM_CSR                                        | SWIM control status register           | 0x00            |  |

| 0x00 7F81 to<br>0x00 7F8F | Reserved area (15 bytes) |                                                 |                                        |                 |  |

### Table 9. CPU/SWIM/debug module/interrupt controller registers

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time<br>This configures the stabilization time.<br>0x00: 2048 HSE cycles<br>0xB4: 128 HSE cycles<br>0xD2: 8 HSE cycles<br>0xE1: 0.5 HSE cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OPT6            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OPT7            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OPTBL           | <ul> <li>BL[7:0] Bootloader option byte</li> <li>For STM8S products, this option is checked by the boot ROM code after reset. Depending on the content of addresses 0x487E, 0x487F, and 0x8000 (reset vector), the CPU jumps to the bootloader or to the reset vector. Refer to the UM0560 (STM8L/S bootloader manual) for more details.</li> <li>For STM8L products, the bootloader option bytes are on addresses 0xXXXX and 0xXXXX+1 (2 bytes). These option bytes control whether the bootloader is active or not. For more details, refer to the UM0560 (STM8L/S bootloader to to to the UM0560 (STM8L/S bootloader to to to to to the UM0560 (STM8L/S bootloader to to</li></ul> |

Table 12. Option byte description (continued)

| Option byte number | Description <sup>(1)</sup>                                                                                                                                                                                                                             |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>AFR7Alternate function remapping option 7</li> <li>0: AFR7 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D4 alternate function = BEEP</li> <li>AFR6 Alternate function remapping option 6</li> </ul>   |

|                    | 0: AFR6 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port B5 alternate function = $I^2C\_SDA$ ; port B4 alternate function = $I^2C\_SCL$                                                                                 |

|                    | AFR5 Alternate function remapping option 5                                                                                                                                                                                                             |

|                    | 0: AFR5 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port B3 alternate function = TIM1_ETR, port B2 alternate function =<br>TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate<br>function = TIM1_CH1N |

|                    | AFR4 Alternate function remapping option 4                                                                                                                                                                                                             |

| OPT2               | <ul> <li>0: AFR4 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D alternate function = TIM1_CH4</li> </ul>                                                                                                       |

|                    | AFR3 Alternate function remapping option 3                                                                                                                                                                                                             |

|                    | <ul> <li>0: AFR3 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D0 alternate function = TIM1_BKIN</li> </ul>                                                                                                     |

|                    | AFR2 Alternate function remapping option 2                                                                                                                                                                                                             |

|                    | <ul> <li>0: AFR2 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D0 alternate function = CLK_CCO</li> </ul>                                                                                                       |

|                    | Note: AFR2 option has priority over AFR3 if both are activated                                                                                                                                                                                         |

|                    | AFR1 Alternate function remapping option 1                                                                                                                                                                                                             |

|                    | 0: AFR1 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port A3 alternate function = TIM3_CH1; port D2 alternate function<br>TIM2_CH3                                                                                       |

|                    | AFR0 Alternate function remapping option 0                                                                                                                                                                                                             |

|                    | <ul> <li>0: AFR0 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D3 alternate function = ADC_ETR</li> </ul>                                                                                                       |

1. Do not use more than one remapping option in the same port.

2. Refer to the pinout description.

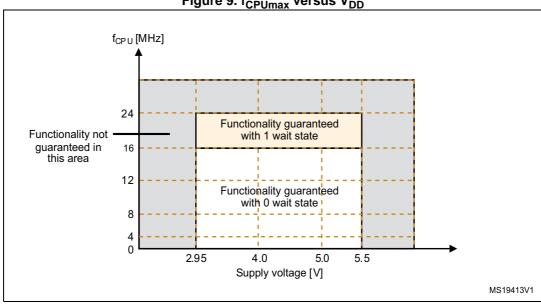

Figure 9. f<sub>CPUmax</sub> versus V<sub>DD</sub>

| Table 18. Operating conditions at power-up/power-o | lown |

|----------------------------------------------------|------|

|----------------------------------------------------|------|

| Symbol                | Parameter                                  | Conditions             | Min              | Тур  | Max                | Unit  |

|-----------------------|--------------------------------------------|------------------------|------------------|------|--------------------|-------|

| +                     | V <sub>DD</sub> rise time rate             | -                      | 2 <sup>(1)</sup> | -    | x                  | μs/V  |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate             | -                      | 2 <sup>(1)</sup> | -    | 8                  | μ5/ ν |

| t <sub>TEMP</sub>     | Reset release<br>delay                     | V <sub>DD</sub> rising | -                | -    | 1.7 <sup>(1)</sup> | ms    |

| V <sub>IT+</sub>      | Power-on reset<br>threshold <sup>(2)</sup> | -                      | 2.65             | 2.8  | 2.95               | V     |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold               | -                      | 2.58             | 2.73 | 2.88               | V     |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis              | -                      | -                | 70   | -                  | mV    |

1. Guaranteed by design, not tested in production.

-

If V<sub>DD</sub> is below 2.95 V, the code execution is guaranteed above the V<sub>IT</sub> and <sub>VIT+</sub> thresholds. RAM content is kept. The EEPROM programming sequence must not be initiated. 2.

| Symbol   | Parameter                    | Condi                                                       | Тур                                   | Max $^{(1)}$ | Unit |                |

|----------|------------------------------|-------------------------------------------------------------|---------------------------------------|--------------|------|----------------|

|          |                              |                                                             | HSE crystal osc. (16 MHz)             | 3.2          | -    |                |

|          |                              | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz)          | 2.6 3.2      |      |                |

|          | Supply<br>current in         |                                                             | HSI RC osc. (16 MHz)                  | 2.5          | 3.2  |                |

|          | run mode,                    | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSE user ext. clock (16 MHz)          | 1.6          | 2.2  |                |

|          | code<br>executed<br>from RAM |                                                             | HSI RC osc. (16 MHz)                  | 1.3          | 2.0  |                |

|          |                              | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)                |              | -    |                |

| 1        |                              | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.55         | -    | <b>س</b> ۸     |

| IDD(RUN) |                              | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 7.7          | -    | - mA<br>-<br>- |

|          |                              |                                                             | HSE user ext. clock (16 MHz)          | 7.0          | 8.0  |                |

|          | Supply<br>current in         |                                                             | HSI RC osc.(16 MHz)                   | 7.0          | 8.0  |                |

|          | run mode,                    | f <sub>CPU</sub> = f <sub>MASTER</sub> = 2 MHz              | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 1.5          | -    |                |

|          | code<br>executed             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.35         | 2.0  |                |

|          | from Flash                   | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)                |              | -    |                |

|          |                              | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.6          | -    |                |

| Table 19. Total current consum | ntion with code executio | n in run mode at Vaa – 5 V              |

|--------------------------------|--------------------------|-----------------------------------------|

| Table 13. Total current consum | plion with code executio | m m m u m u m u u m u u u u u u u u u u |

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

### Total current consumption in wait mode

| Symbol               | Parameter                         | Condit                                                      | Тур                                   | Max <sup>(1)</sup> | Unit |    |

|----------------------|-----------------------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|----|

| I <sub>DD(WFI)</sub> |                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 2.15               | -    |    |

|                      |                                   |                                                             | HSE user ext. clock (16 MHz)          | 1.55               | 2.0  |    |

|                      | Supply<br>current in<br>wait mode |                                                             | HSI RC osc. (16 MHz)                  | 1.5                | 1.9  |    |

|                      |                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.3                | -    | mA |

|                      |                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.7                | -    |    |

|                      |                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.5                | -    |    |

| Table 21. Total current consumption | n in wait mode at V <sub>DD</sub> = 5 V |

|-------------------------------------|-----------------------------------------|

|-------------------------------------|-----------------------------------------|

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

# Table 22. Total current consumption in wait mode at $V_{DD}$ = 3.3 V

| Symbol               | Parameter | Condit                                                      | Тур                          | Max <sup>(1)</sup>                    | Unit |    |  |

|----------------------|-----------|-------------------------------------------------------------|------------------------------|---------------------------------------|------|----|--|

|                      |           |                                                             | HSE crystal osc. (16 MHz)    | 1.75                                  | -    |    |  |

|                      |           | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz) | 1.55                                  | 2.0  |    |  |

|                      | -         |                                                             | HSI RC osc. (16 MHz)         | 1.5                                   | 1.9  |    |  |

| I <sub>DD(WFI)</sub> |           | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)         | 1.3                                   | -    | mA |  |

|                      |           | wait mode $f_{CPU} = f_{MASTER}/128 =$<br>15.625 kHz        |                              | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.7  | -  |  |

|                      |           | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | LSI RC osc. (128 kHz)        | 0.5                                   | -    |    |  |

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

### Total current consumption in active halt mode

|                     |                                    |                                                   | Conditions                | S                                  |      |                    |      |  |

|---------------------|------------------------------------|---------------------------------------------------|---------------------------|------------------------------------|------|--------------------|------|--|

| Symbol              | Parameter                          | Main voltage<br>regulator<br>(MVR) <sup>(2)</sup> | Flash mode <sup>(3)</sup> | Clock source                       | Тур  | Max <sup>(1)</sup> | Unit |  |

|                     |                                    |                                                   | Operating mode            | HSE crystal oscillator<br>(16 MHz) | 1080 | -                  |      |  |

|                     |                                    | On                                                |                           | LSI RC oscillator<br>(128 kHz)     | 200  | 320                |      |  |

| I <sub>DD(AH)</sub> | Supply current in active halt mode | Supply current in                                 | Dower down mode           | HSE crystal oscillator<br>(16 MHz) | 1030 | -                  | μA   |  |

|                     |                                    |                                                   | T Ower-down mode          | LSI RC oscillator<br>(128 kHz)     | 140  | 270                |      |  |

|                     |                                    | Off                                               | Operating mode            | LSI RC oscillator                  | 68   | 120                |      |  |

|                     |                                    |                                                   | Power-down mode           | (128 kHz)                          | 12   | 60                 |      |  |

1. Data based on characterization results, not tested in production.

2. Configured by the REGAH bit in the CLK\_ICKR register.

3. Configured by the AHALT bit in the FLASH\_CR1 register.

### Table 24. Total current consumption in active halt mode at $V_{DD}$ = 3.3 V

| Symbol  |                                  |                                                   | Conditio                  | ns                        |     | Max                |      |

|---------|----------------------------------|---------------------------------------------------|---------------------------|---------------------------|-----|--------------------|------|

|         | Parameter                        | Main voltage<br>regulator<br>(MVR) <sup>(2)</sup> | Flash mode <sup>(3)</sup> | Clock source              | Тур | at<br>85° C<br>(1) | Unit |

|         |                                  |                                                   | Operating mode            | HSE crystal osc. (16 MHz) | 680 | -                  |      |

|         |                                  | On                                                |                           | LSI RC osc. (128 kHz)     | 200 | -<br>320<br>-      |      |

|         | Supply current<br>in active halt | On                                                |                           | HSE crystal osc. (16 MHz) | 630 | -                  |      |

| IDD(AH) | mode                             |                                                   | Fower-down mode           | LSI RC osc. (128 kHz)     | 140 | 270                | μA   |

|         |                                  | Off                                               | Operating mode            | LSI RC osc. (128 kHz)     | 66  | 120                |      |

|         |                                  |                                                   | Power-down mode           |                           | 10  | 60                 |      |

1. Data based on characterization results, not tested in production.

2. Configured by the REGAH bit in the CLK\_ICKR register.

3. Configured by the AHALT bit in the FLASH\_CR1 register.

| Symbol                              | Parameter                                   | Conditions                              | Min | Тур | Мах                                            | Unit |  |

|-------------------------------------|---------------------------------------------|-----------------------------------------|-----|-----|------------------------------------------------|------|--|

| f <sub>HSE</sub>                    | External high speed oscillator<br>frequency | -                                       | 1   | -   | 16                                             | MHz  |  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                       | -   | 220 | -                                              | kΩ   |  |

| C <sup>(1)</sup>                    | Recommended load capacitance (2)            | -                                       | -   | -   | 20                                             | pF   |  |

|                                     | HSE oscillator power consumption            | C = 20 pF,<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (startup)<br>1.6 (stabilized) <sup>(3)</sup> | mA   |  |

| IDD(HSE)                            |                                             | C = 10 pF,<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (startup)<br>1.2 (stabilized) <sup>(3)</sup> | mA   |  |

| 9 <sub>m</sub>                      | Oscillator transconductance                 | -                                       | 5   | -   | -                                              | mA/V |  |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | $V_{\text{DD}}$ is stabilized           | -   | 1   | -                                              | ms   |  |

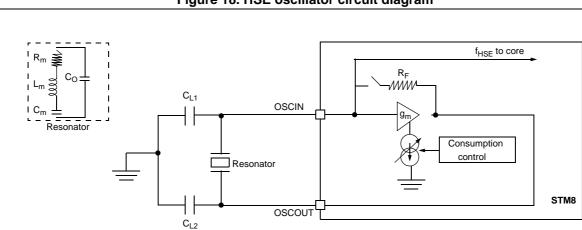

### Table 31. HSE oscillator characteristics

1. C is approximately equivalent to 2 x crystal Cload.

The oscillator selection can be optimized in terms of supply current using a high quality resonator with small R<sub>m</sub> value. 2. Refer to crystal manufacturer for more details

3. Data based on characterization results, not tested in production.

t<sub>SU(HSE)</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 24 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. 4.

### Figure 18. HSE oscillator circuit diagram

### HSE oscillator critical g<sub>m</sub> formula

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

R<sub>m</sub>: Notional resistance (see crystal specification) L<sub>m</sub>: Notional inductance (see crystal specification) C<sub>m</sub>: Notional capacitance (see crystal specification) Co: Shunt capacitance (see crystal specification) C<sub>L1</sub>=C<sub>L2</sub>=C: Grounded external capacitance g<sub>m</sub> >> g<sub>mcrit</sub>

DocID022186 Rev 4

### 9.3.6 I/O port pin characteristics

### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                          | Parameter                                       | Conditions                                  | Min                   | Тур | Max                     | Unit |

|---------------------------------|-------------------------------------------------|---------------------------------------------|-----------------------|-----|-------------------------|------|

| V <sub>IL</sub>                 | Input low level voltage                         |                                             | -0.3                  | -   | 0.3 x V <sub>DD</sub>   | V    |

| V <sub>IH</sub>                 | Input high level<br>voltage                     | $V_{DD} = 5 V$                              | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                       |                                             | -                     | 700 | -                       | mV   |

| $R_{pu}$                        | Pull-up resistor                                | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$         | 30                    | 55  | 80                      | kΩ   |

| t <sub>R</sub> , t <sub>F</sub> | Rise and fall time                              | Fast I/Os<br>Load = 50 pF                   | -                     | -   | 35 <sup>(2)</sup>       | ns   |

|                                 | (10% - 90%)                                     | Standard and high sink I/Os<br>Load = 50 pF | -                     | -   | 125 <sup>(2)</sup>      | ns   |

| I <sub>lkg</sub>                | Input leakage<br>current,<br>analog and digital | $V_{SS} \leq V_{IN} \leq V_{DD}$            | -                     | -   | ±1 <sup>(3)</sup>       | μA   |

| I <sub>lkg ana</sub>            | Analog input<br>leakage current                 | $V_{SS} \leq V_{IN} \leq V_{DD}$            | -                     | -   | ±250 <sup>(3)</sup>     | nA   |

| l <sub>lkg(inj)</sub>           | Leakage current in<br>adjacent I/O              | Injection current ±4 mA                     | -                     | -   | ±1 <sup>(3)</sup>       | μA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

2. Data guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

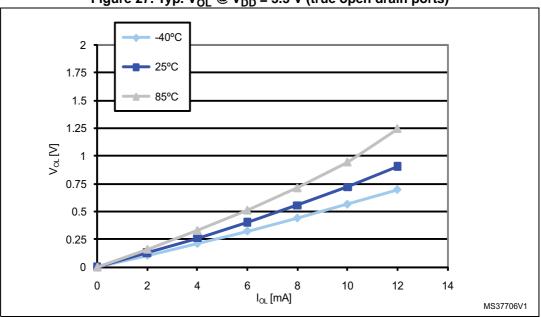

Figure 27. Typ. V<sub>OL</sub> @ V<sub>DD</sub> = 3.3 V (true open drain ports)

Figure 28. Typ.  $V_{OL} @ V_{DD} = 5 V$  (high sink ports)

### 9.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions             | Min                         | <b>Typ</b> <sup>1)</sup> | Max                   | Unit |  |  |  |  |

|-------------------------|----------------------------------------------|------------------------|-----------------------------|--------------------------|-----------------------|------|--|--|--|--|

| V <sub>IL(NRST)</sub>   | NRST input low level voltage <sup>(1)</sup>  | -                      | -0.3 V                      | -                        | 0.3 x V <sub>DD</sub> |      |  |  |  |  |

| V <sub>IH(NRST)</sub>   | NRST input high level voltage <sup>(1)</sup> | -                      | $0.7 	ext{ x V}_{	ext{DD}}$ | -                        | V <sub>DD</sub> + 0.3 | V    |  |  |  |  |

| V <sub>OL(NRST)</sub>   | NRST output low level voltage <sup>(1)</sup> | I <sub>OL</sub> = 2 mA | -                           | -                        | 0.5                   |      |  |  |  |  |

| R <sub>PU(NRST)</sub>   | NRST pull-up resistor <sup>(2)</sup>         | -                      | 30                          | 55                       | 80                    | kΩ   |  |  |  |  |

| t <sub>IFP(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>     | -                      | -                           | -                        | 75                    | ns   |  |  |  |  |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse <sup>(3)</sup> | -                      | 500                         | -                        | -                     | ns   |  |  |  |  |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(1)</sup>             | -                      | 15                          | -                        | -                     | μs   |  |  |  |  |

### Table 40. NRST pin characteristics

1. Data based on characterization results, not tested in production.

2. The  $\rm R_{PU}$  pull-up equivalent resistor is based on a resistive transistor

3. Data guaranteed by design, not tested in production.

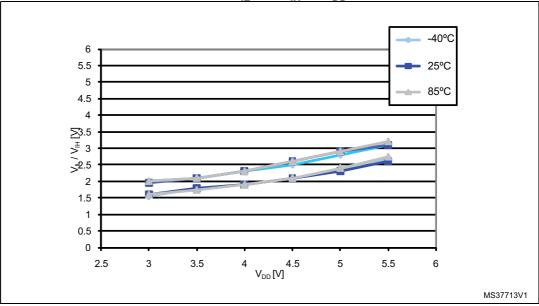

### Figure 34. Typical NRST V<sub>IL</sub> and V<sub>IH</sub> vs V<sub>DD</sub> @ 3 temperatures

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 13 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-Oct-2011 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                          |

| 09-Jan-2012 | 2        | <ul> <li>Updated:</li> <li>t<sub>RET</sub> in <i>Table 35: Flash program memory/data</i><br/><i>EEPROM memory</i>,</li> <li>R<sub>PU</sub> in <i>Table 40: NRST pin characteristics</i> and<br/><i>Table 36: I/O static characteristics</i>,</li> <li>the notes related to V<sub>CAP</sub> in <i>Section 9.3: Operating</i><br/><i>conditions</i>.</li> </ul>                             |

| 13-Jun-2012 | 3        | Updated the temperature condition for factory calibrated ACC <sub>HSI</sub> in <i>Table 32: HSI oscillator characteristics</i> .<br>Changed SCK input to SCK output in <i>Figure 40: SPI timing diagram - master mode(1)</i> .                                                                                                                                                            |

| 26-Mar-2015 | 4        | <ul> <li>Updated:</li> <li>the buffer size in Section 4.13: Analog-to-digital converter (ADC1),</li> <li>the disclaimer.</li> <li>Added:</li> <li>the note to Power-on reset threshold in Table 18: Operating conditions at power-up/power-down,</li> <li>Figure 46: LQFP48 marking example (package top view),</li> <li>Figure 49: LQFP32 marking example (package top view).</li> </ul> |

Table 53. Document revision history