Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorSTM8    |                                                          |

|-------------------------------------------|----------------------------------------------------------|

| Core Processor STM8                       |                                                          |

|                                           |                                                          |

| Core Size 8-Bit                           |                                                          |

| Speed 16MHz                               |                                                          |

| Connectivity I <sup>2</sup> C, IrDA, LINb | us, SPI, UART/USART                                      |

| Peripherals Brown-out De                  | tect/Reset, POR, PWM, WDT                                |

| Number of I/O 25                          |                                                          |

| Program Memory Size 32KB (32K x 8         | )                                                        |

| Program Memory Type FLASH                 |                                                          |

| EEPROM Size 128 x 8                       |                                                          |

| RAM Size 2K x 8                           |                                                          |

| Voltage - Supply (Vcc/Vdd) 2.95V ~ 5.5V   |                                                          |

| Data Converters A/D 7x10b                 |                                                          |

| Oscillator Type Internal                  |                                                          |

| Operating Temperature -40°C ~ 85°C        | (TA)                                                     |

| Mounting Type Surface Mount               | t                                                        |

| Package / Case 32-LQFP                    |                                                          |

| Supplier Device Package32-LQFP (7x7)      |                                                          |

| Purchase URL https://www.e                | -xfl.com/product-detail/stmicroelectronics/stm8s005k6t6c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

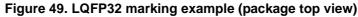

| Figure 49. | LQFP32 marking example (package top view)                           | . 90 |

|------------|---------------------------------------------------------------------|------|

| Figure 50. | STM8S005C6/K6 value line ordering information scheme <sup>(1)</sup> | . 93 |

### 4.5 Clock controller

The clock controller distributes the system clock ( $f_{MASTER}$ ) coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

#### Features

- **Clock prescaler:** To get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching:** Clock sources can be changed safely on the fly in run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management:** To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- *Master clock sources*: Four different clock sources can be used to drive the master clock:

- 1-16 MHz high-speed external crystal (HSE)

- Up to 16 MHz high-speed user-external clock (HSE user-ext)

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

- **Startup clock:** After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): This feature can be enabled by software. If an HSE clock failure occurs, the internal RC (16 MHz/8) is automatically selected by the CSS and an interrupt can optionally be generated.

- **Configurable main clock output (CCO):** This outputs an external clock for use by the application.

| Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock |

|---------|---------------------|---------|---------------------|---------|---------------------|---------|---------------------|

| PCKEN17 | TIM1                | PCKEN13 | UART2               | PCKEN27 | Reserved            | PCKEN23 | ADC                 |

| PCKEN16 | TIM3                | PCKEN12 | Reserved            | PCKEN26 | Reserved            | PCKEN22 | AWU                 |

| PCKEN15 | TIM2                | PCKEN11 | SPI                 | PCKEN25 | Reserved            | PCKEN21 | Reserved            |

| PCKEN14 | TIM4                | PCKEN10 | l <sup>2</sup> C    | PCKEN24 | Reserved            | PCKEN20 | Reserved            |

Table 2. Peripheral clock gating bit assignments in CLK\_PCKENR1/2 registers

### 4.6 **Power management**

For efficent power management, the application can be put in one of four different lowpower modes. You can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- *Wait mode*: In this mode, the CPU is stopped, but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active halt mode with regulator on: In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in active halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active halt mode with regulator off: This mode is the same as active halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- *Halt mode*: In this mode the microcontroller uses the least power. The CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

## 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application perfectly.

The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- 1. Timeout: at 16 MHz CPU clock the time-out period can be adjusted between 75 μs up to 64 ms.

- 2. Refresh out of window: The downcounter is refreshed before its value is lower than the one stored in the window register.

| Pin nu | umber  |                                    |      |          | Inpu     | t              |           | Out   | Output |    | -                              |                                   |                                                      |

|--------|--------|------------------------------------|------|----------|----------|----------------|-----------|-------|--------|----|--------------------------------|-----------------------------------|------------------------------------------------------|

| LQFP48 | LQFP32 | Pin name                           | Type | floating | ndw      | Ext. interrupt | High sink | Speed | OD     | РР | Main function<br>(after reset) | Default<br>alternate<br>function  | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | NRST                               | I/O  |          | <u>X</u> |                |           |       |        |    | Reset                          |                                   |                                                      |

| 2      | 2      | PA1/OSCIN                          | I/O  | X        | х        |                |           | 01    | х      | х  | Port A1                        | Resonator/<br>crystal in          |                                                      |

| 3      | 3      | PA2/OSCOUT                         | I/O  | <u>x</u> | х        | Х              |           | 01    | Х      | х  | Port A2                        | Resonator/<br>crystal out         |                                                      |

| 4      | -      | V <sub>SSIO_1</sub>                | S    |          |          |                |           |       |        |    | I/O groun                      | d                                 |                                                      |

| 5      | 4      | V <sub>SS</sub>                    | S    |          |          |                |           |       |        |    | Digital gro                    | ound                              |                                                      |

| 6      | 5      | VCAP                               | S    |          |          |                |           |       |        |    | 1.8 V reg                      | ulator capacitor                  |                                                      |

| 7      | 6      | V <sub>DD</sub>                    | S    |          |          |                |           |       |        |    | Digital po                     | wer supply                        |                                                      |

| 8      | 7      | V <sub>DDIO_1</sub>                | S    |          |          |                |           |       |        |    | I/O powe                       | r supply                          |                                                      |

| 9      | -      | PA3/TIM2_CH3                       | I/O  | X        | х        | Х              |           | 01    | Х      | х  | Port A3                        | Timer 2 -<br>channel3             | TIM3_CH1<br>[AFR1]                                   |

| 10     | -      | PA4                                | I/O  | X        | Х        | Х              | HS        | O3    | Х      | Х  | Port A4                        |                                   |                                                      |

| 11     | -      | PA5                                | I/O  | X        | Х        | Х              | HS        | O3    | Х      | Х  | Port A5                        |                                   |                                                      |

| 12     | -      | PA6                                | I/O  | X        | Х        | Х              | HS        | O3    | Х      | Х  | Port A6                        |                                   |                                                      |

| -      | 8      | PF4/AIN12 <sup>(1)</sup>           | I/O  | X        | х        |                |           | 01    | х      | х  | Port F4                        | Analog input<br>12 <sup>(2)</sup> |                                                      |

| 13     | 9      | V <sub>DDA</sub>                   | S    |          |          |                |           |       |        |    | Analog po                      | ower supply                       |                                                      |

| 14     | 10     | V <sub>SSA</sub>                   | S    |          |          |                |           |       |        |    | Analog gi                      | round                             |                                                      |

| 15     | -      | PB7/AIN7                           | I/O  | <u>X</u> | х        | х              |           | 01    | х      | х  | Port B7                        | Analog<br>input 7                 |                                                      |

| 16     | -      | PB6/AIN6                           | I/O  | X        | х        | Х              |           | 01    | х      | х  | Port B6                        | Analog<br>input 6                 |                                                      |

| 17     | 11     | PB5/AIN5<br>[I <sup>2</sup> C_SDA] | I/O  | X        | х        | Х              |           | 01    | х      | х  | Port B5                        | Analog<br>input 5                 | I <sup>2</sup> C_SDA<br>[AFR6]                       |

| 18     | 12     | PB4/AIN4<br>[I <sup>2</sup> C_SCL] | I/O  | X        | х        | Х              |           | 01    | х      | х  | Port B4                        | Analog<br>input 4                 | I <sup>2</sup> C_SCL<br>[AFR6]                       |

| 19     | 13     | PB3/AIN3<br>[TIM1_ETR]             | I/O  | X        | х        | Х              |           | 01    | х      | х  | Port B3                        | Analog<br>input 3                 | TIM1_ETR<br>[AFR5]                                   |

| 20     | 14     | PB2/AIN2<br>[TIM1_CH3N]            | I/O  | X        | x        | х              |           | 01    | Х      | х  | Port B2                        | Analog<br>input 2                 | TIM1_<br>CH3N<br>[AFR5]                              |

| 21     | 15     | PB1/AIN1<br>[TIM1_CH2N]            | I/O  | X        | Х        | Х              |           | O1    | х      | х  | Port B1                        | Analog<br>input 1                 | TIM1_<br>CH2N<br>[AFR5]                              |

Table 5. STM8S005C6 and STM8S005K6 pin descriptions

|                           |       |                          | e register map (continued)                | Reset  |  |  |

|---------------------------|-------|--------------------------|-------------------------------------------|--------|--|--|

| Address                   | Block | Register label           | Register name                             | status |  |  |

| 0x00 532B                 |       | TIM3_ARRH                | TIM3 auto-reload register high            | 0xFF   |  |  |

| 0x00 532C                 |       | TIM3_ARRL                | TIM3 auto-reload register low             | 0xFF   |  |  |

| 0x00 532D                 | ТІМЗ  | TIM3_CCR1H               | TIM3 capture/compare register 1 high      | 0x00   |  |  |

| 0x00 532E                 |       | TIM3_CCR1L               | TIM3 capture/compare register 1 low       | 0x00   |  |  |

| 0x00 532F                 |       | TIM3_CCR2H               | TIM3 capture/compare register 2 high      | 0x00   |  |  |

| 0x00 5330                 |       | TIM3_CCR2L               | TIM3 capture/compare register 2 low       | 0x00   |  |  |

| 0x00 5331 to<br>0x00 533F |       | Reserved area (15 bytes) |                                           |        |  |  |

| 0x00 5340                 |       | TIM4_CR1                 | TIM4 control register 1                   | 0x00   |  |  |

| 0x00 5341                 |       | TIM4_IER                 | TIM4 interrupt enable register            | 0x00   |  |  |

| 0x00 5342                 |       | TIM4_SR                  | TIM4 status register                      | 0x00   |  |  |

| 0x00 5343                 | TIM4  | TIM4_EGR                 | TIM4 event generation register            | 0x00   |  |  |

| 0x00 5344                 |       | TIM4_CNTR                | TIM4 counter                              | 0x00   |  |  |

| 0x00 5345                 |       | TIM4_PSCR                | TIM4 prescaler register                   | 0x00   |  |  |

| 0x00 5346                 |       | TIM4_ARR                 | TIM4 auto-reload register                 | 0xFF   |  |  |

| 0x00 5347 to<br>0x00 53FF |       | I                        | Reserved area (185 bytes)                 |        |  |  |

| 0x00 5400                 |       | ADC _CSR                 | ADC control/status register               | 0x00   |  |  |

| 0x00 5401                 |       | ADC_CR1                  | ADC configuration register 1              | 0x00   |  |  |

| 0x00 5402                 |       | ADC_CR2                  | ADC configuration register 2              | 0x00   |  |  |

| 0x00 5403                 |       | ADC_CR3                  | ADC configuration register 3              | 0x00   |  |  |

| 0x00 5404                 |       | ADC_DRH                  | ADC data register high                    | 0xXX   |  |  |

| 0x00 5405                 |       | ADC_DRL                  | ADC data register low                     | 0xXX   |  |  |

| 0x00 5406                 |       | ADC_TDRH                 | ADC Schmitt trigger disable register high | 0x00   |  |  |

| 0x00 5407                 | 4004  | ADC_TDRL                 | ADC Schmitt trigger disable register low  | 0x00   |  |  |

| 0x00 5408                 | ADC1  | ADC_HTRH                 | ADC high threshold register high          | 0x03   |  |  |

| 0x00 5409                 | 1     | ADC_HTRL                 | ADC high threshold register low           | 0xFF   |  |  |

| 0x00 540A                 | 1     | ADC_LTRH                 | ADC low threshold register high           | 0x00   |  |  |

| 0x00 540B                 | 1     | ADC_LTRL                 | ADC low threshold register low            | 0x00   |  |  |

| 0x00 540C                 | 1     | ADC_AWSRH                | ADC analog watchdog status register high  | 0x00   |  |  |

| 0x00 540D                 | 1     | ADC_AWSRL                | ADC analog watchdog status register low   | 0x00   |  |  |

| 0x00 540E                 | 1     | ADC_AWCRH                | ADC analog watchdog control register high | 0x00   |  |  |

| 0x00 540F                 | 1     | ADC_AWCRL                | ADC analog watchdog control register low  | 0x00   |  |  |

| 0x00 5410 to<br>0x00 57FF |       | R                        | Reserved area (1008 bytes)                |        |  |  |

| <b>T</b>    |                | • .           | / / N         |

|-------------|----------------|---------------|---------------|

| Table 8. Ge | neral hardware | e register ma | p (continued) |

34/97

# 7 Interrupt vector mapping

|            | Table 10. Interrupt mapping |                                                  |                          |                                 |                           |  |  |  |  |  |

|------------|-----------------------------|--------------------------------------------------|--------------------------|---------------------------------|---------------------------|--|--|--|--|--|

| IRQ<br>no. | Source<br>block             | Description                                      | Wakeup from<br>Halt mode | Wakeup from<br>Active-halt mode | Vector address            |  |  |  |  |  |

| -          | RESET                       | Reset                                            | Yes                      | Yes                             | 0x00 8000                 |  |  |  |  |  |

| -          | TRAP                        | Software interrupt                               | -                        | -                               | 0x00 8004                 |  |  |  |  |  |

| 0          | TLI                         | External top level interrupt                     | -                        | -                               | 0x00 8008                 |  |  |  |  |  |

| 1          | AWU                         | Auto wake up from halt                           | -                        | Yes                             | 0x00 800C                 |  |  |  |  |  |

| 2          | CLK                         | Clock controller                                 | -                        | -                               | 0x00 8010                 |  |  |  |  |  |

| 3          | EXTI0                       | Port A external interrupts                       | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>              | 0x00 8014                 |  |  |  |  |  |

| 4          | EXTI1                       | Port B external interrupts                       | Yes                      | Yes                             | 0x00 8018                 |  |  |  |  |  |

| 5          | EXTI2                       | Port C external interrupts                       | Yes                      | Yes                             | 0x00 801C                 |  |  |  |  |  |

| 6          | EXTI3                       | Port D external interrupts                       | Yes                      | Yes                             | 0x00 8020                 |  |  |  |  |  |

| 7          | EXTI4                       | Port E external interrupts                       | Yes                      | Yes                             | 0x00 8024                 |  |  |  |  |  |

| 8          |                             | Reserved                                         |                          | •                               | 0x00 8028                 |  |  |  |  |  |

| 9          |                             | Reserved                                         |                          |                                 | 0x00 802C                 |  |  |  |  |  |

| 10         | SPI                         | End of transfer                                  | Yes                      | Yes                             | 0x00 8030                 |  |  |  |  |  |

| 11         | TIM1                        | TIM1 update/overflow/underflow/<br>trigger/break | -                        | -                               | 0x00 8034                 |  |  |  |  |  |

| 12         | TIM1                        | TIM1 capture/compare                             | -                        | -                               | 0x00 8038                 |  |  |  |  |  |

| 13         | TIM2                        | TIM2 update /overflow                            | -                        | -                               | 0x00 803C                 |  |  |  |  |  |

| 14         | TIM2                        | TIM2 capture/compare                             | -                        | -                               | 0x00 8040                 |  |  |  |  |  |

| 15         | TIM3                        | Update/overflow                                  | -                        | -                               | 0x00 8044                 |  |  |  |  |  |

| 16         | TIM3                        | Capture/compare                                  | -                        | -                               | 0x00 8048                 |  |  |  |  |  |

| 17         | -                           | Reserved                                         | -                        | -                               | 0x00 804C                 |  |  |  |  |  |

| 18         | -                           | Reserved                                         | -                        | -                               | 0x00 8050                 |  |  |  |  |  |

| 19         | I <sup>2</sup> C            | I <sup>2</sup> C interrupt                       | Yes                      | Yes                             | 0x00 8054                 |  |  |  |  |  |

| 20         | UART2                       | Tx complete                                      | -                        | -                               | 0x00 8058                 |  |  |  |  |  |

| 21         | UART2                       | Receive register DATA FULL                       | -                        | -                               | 0x00 805C                 |  |  |  |  |  |

| 22         | ADC1                        | ADC1 end of conversion/analog watchdog interrupt | -                        | -                               | 0x00 8060                 |  |  |  |  |  |

| 23         | TIM4                        | TIM4 update/overflow                             | -                        | -                               | 0x00 8064                 |  |  |  |  |  |

| 24         | Flash                       | EOP/WR_PG_DIS                                    | -                        | -                               | 0x00 8068                 |  |  |  |  |  |

|            |                             | Reserved                                         | 1                        |                                 | 0x00 806C to<br>0x00 807C |  |  |  |  |  |

#### Table 10. Interrupt mapping

1. Except PA1

| Option byte number | Description <sup>(1)</sup>                                                                                                                                                                                                                             |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>AFR7Alternate function remapping option 7</li> <li>0: AFR7 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D4 alternate function = BEEP</li> <li>AFR6 Alternate function remapping option 6</li> </ul>   |

|                    | 0: AFR6 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port B5 alternate function = $I^2C\_SDA$ ; port B4 alternate function = $I^2C\_SCL$                                                                                 |

|                    | AFR5 Alternate function remapping option 5                                                                                                                                                                                                             |

|                    | 0: AFR5 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port B3 alternate function = TIM1_ETR, port B2 alternate function =<br>TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate<br>function = TIM1_CH1N |

|                    | AFR4 Alternate function remapping option 4                                                                                                                                                                                                             |

| OPT2               | <ul> <li>0: AFR4 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D alternate function = TIM1_CH4</li> </ul>                                                                                                       |

|                    | AFR3 Alternate function remapping option 3                                                                                                                                                                                                             |

|                    | <ul> <li>0: AFR3 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D0 alternate function = TIM1_BKIN</li> </ul>                                                                                                     |

|                    | AFR2 Alternate function remapping option 2                                                                                                                                                                                                             |

|                    | <ul> <li>0: AFR2 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D0 alternate function = CLK_CCO</li> </ul>                                                                                                       |

|                    | Note: AFR2 option has priority over AFR3 if both are activated                                                                                                                                                                                         |

|                    | AFR1 Alternate function remapping option 1                                                                                                                                                                                                             |

|                    | 0: AFR1 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port A3 alternate function = TIM3_CH1; port D2 alternate function<br>TIM2_CH3                                                                                       |

|                    | AFR0 Alternate function remapping option 0                                                                                                                                                                                                             |

|                    | <ul> <li>0: AFR0 remapping option inactive: default alternate function<sup>(2)</sup></li> <li>1: Port D3 alternate function = ADC_ETR</li> </ul>                                                                                                       |

1. Do not use more than one remapping option in the same port.

2. Refer to the pinout description.

# 9.2 Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                           | Min                   | Max                                     | Unit |

|------------------------------------|-------------------------------------------------------------------|-----------------------|-----------------------------------------|------|

| V <sub>DDx</sub> - V <sub>SS</sub> | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                  | 6.5                                     |      |

| V                                  | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3 | 6.5                                     | V    |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3                   |      |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           | -                     | 50                                      | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins                  | -                     | 50                                      | IIIV |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   | ratings (             | te maximum<br>´electrical<br>on page 83 | -    |

1. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

| Symbol   | Parameter            | Condi                                                       | Тур                                   | Max <sup>(1)</sup> | Unit |    |

|----------|----------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|----|

|          |                      |                                                             | HSE crystal osc. (16 MHz)             | 2.8                | -    |    |

|          |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz)          | 2.6                | 3.2  |    |

|          | Supply<br>current in |                                                             | HSI RC osc. (16 MHz)                  | 2.5                | 3.2  |    |

|          | run mode,            | un mode,                                                    | HSE user ext. clock (16 MHz)          | 1.6                | 2.2  |    |

|          | code<br>executed     | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.3                | 2.0  |    |

|          | from RAM             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16MHz/8)                 | 0.75               | -    |    |

| 1        |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.55               | -    | mA |

| IDD(RUN) |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 7.3                | -    |    |

|          |                      |                                                             | HSE user ext. clock (16 MHz)          | 7.0                | 8.0  |    |

|          | Supply<br>current in |                                                             | HSI RC osc. (16 MHz)                  | 7.0                | 8.0  |    |

|          | run mode,            | f <sub>CPU</sub> = f <sub>MASTER</sub> = 2 MHz              | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 1.5                | -    |    |

|          | code<br>executed     | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.35               | 2.0  | 1  |

|          | from Flash           | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)                | 0.75               | -    |    |

|          |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.6                | -    |    |

Table 20. Total current consumption with code execution in run mode at  $V_{DD}$  = 3.3 V

1. Data based on characterization results, not tested in production.

2. Default clock configuration.

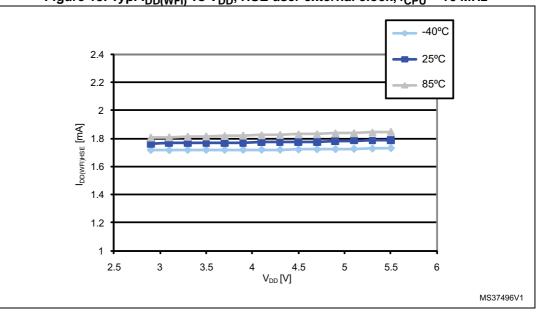

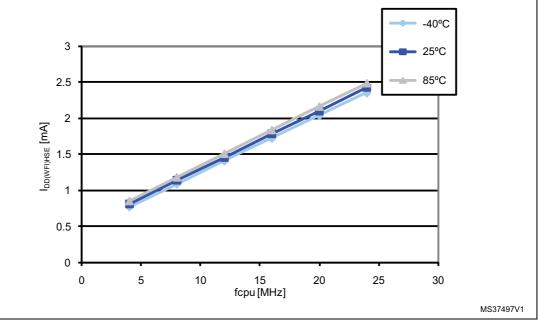

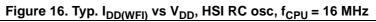

Figure 13. Typ.  $I_{DD(WFI)}$  vs V<sub>DD</sub>, HSE user external clock,  $f_{CPU}$  = 16 MHz

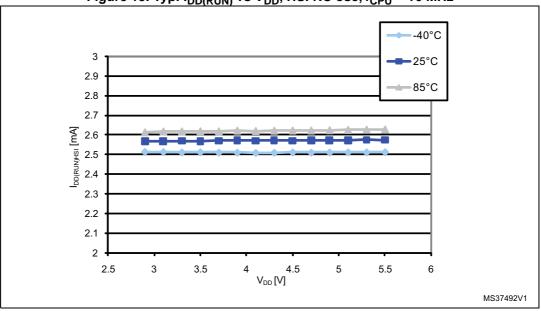

Figure 15. Typ.  $I_{DD(RUN)}$  vs  $V_{DD}$ , HSI RC osc,  $f_{CPU}$  = 16 MHz

### 9.3.4 Internal clock sources and timing characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.~f_{\text{HSE}}$

### High speed internal RC oscillator (HSI)

| Symbol               | Parameter                                          | Conditions                                                                                  | Min | Тур | Max                | Unit |

|----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|--------------------|------|

| f <sub>HSI</sub>     | Frequency                                          | -                                                                                           | -   | 16  | -                  | MHz  |

| ACC <sub>HSI</sub>   | Accuracy of HSI oscillator                         | Trimmed by the CLK_HSITRIMR register for given $V_{DD}$ and $T_A$ conditions <sup>(1)</sup> |     |     | 1.0 <sup>(2)</sup> | %    |

|                      | Accuracy of HSI oscillator<br>(factory calibrated) | V <sub>DD</sub> = 5 V, T <sub>A</sub> = 25 °C                                               | -   | 5   | - //               |      |

|                      |                                                    | $V_{DD} = 5 V,$<br>-40 °C $\leq T_A \leq 85 °C$                                             | -5  | -   | 5                  |      |

| t <sub>su(HSI)</sub> | HSI oscillator wakeup time including calibration   | -                                                                                           | -   | -   | 1.0 <sup>(2)</sup> | μs   |

| I <sub>DD(HSI)</sub> | HSI oscillator power<br>consumption                | -                                                                                           | -   | 170 | 250 <sup>(3)</sup> | μΑ   |

#### Table 32. HSI oscillator characteristics

1. See the application note.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production

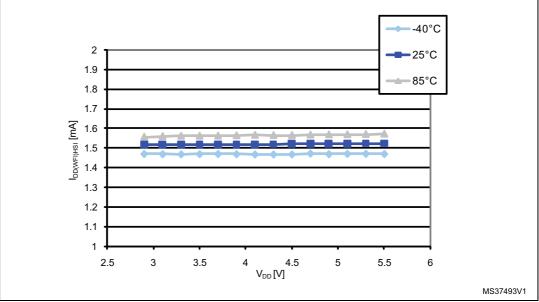

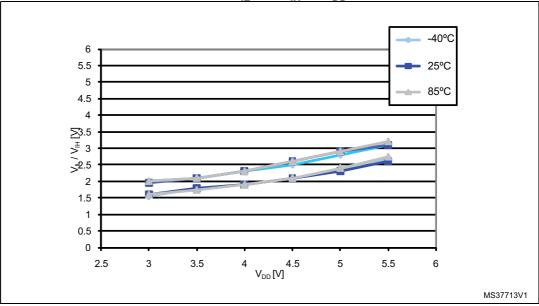

### Figure 19. Typical HSI frequency variation vs V<sub>DD</sub> at 3 temperatures

## 9.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions             | Min                         | <b>Typ</b> <sup>1)</sup> | Max                   | Unit |  |

|-------------------------|----------------------------------------------|------------------------|-----------------------------|--------------------------|-----------------------|------|--|

| V <sub>IL(NRST)</sub>   | NRST input low level voltage <sup>(1)</sup>  | -                      | -0.3 V                      | -                        | 0.3 x V <sub>DD</sub> |      |  |

| V <sub>IH(NRST)</sub>   | NRST input high level voltage <sup>(1)</sup> | -                      | $0.7 	ext{ x V}_{	ext{DD}}$ | -                        | V <sub>DD</sub> + 0.3 | V    |  |

| V <sub>OL(NRST)</sub>   | NRST output low level voltage <sup>(1)</sup> | I <sub>OL</sub> = 2 mA | -                           | -                        | 0.5                   |      |  |

| R <sub>PU(NRST)</sub>   | NRST pull-up resistor <sup>(2)</sup>         | -                      | 30                          | 55                       | 80                    | kΩ   |  |

| t <sub>IFP(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>     | -                      | -                           | -                        | 75                    | ns   |  |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse <sup>(3)</sup> | -                      | 500                         | -                        | -                     | ns   |  |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(1)</sup>             | -                      | 15                          | -                        | -                     | μs   |  |

#### Table 40. NRST pin characteristics

1. Data based on characterization results, not tested in production.

2. The  $\rm R_{PU}$  pull-up equivalent resistor is based on a resistive transistor

3. Data guaranteed by design, not tested in production.

### Figure 34. Typical NRST V<sub>IL</sub> and V<sub>IH</sub> vs V<sub>DD</sub> @ 3 temperatures

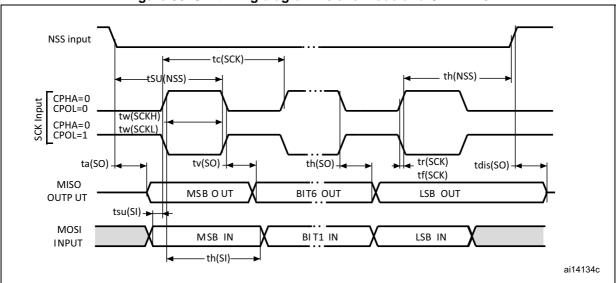

Figure 38. SPI timing diagram - slave mode and CPHA = 0

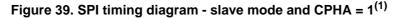

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

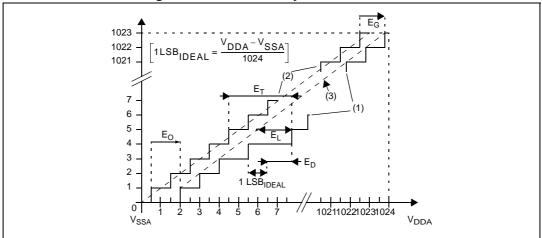

1. Example of an actual transfer curve.

- 2. The ideal transfer curve

- 3.

End point correlation line  $E_T$  = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.  $E_0$  = Offset error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: deviation between the last ideal transition and the last actual one.  $E_D$  = Differential linearity error: maximum deviation between actual steps and the ideal one.  $E_L$  = Integral linearity error: maximum deviation between any actual transition and the end point correlation between any actual transition and the end point correlation line.

### **Electromagnetic interference (EMI)**

Emission tests conform to the SAE IEC 61967-2 standard for test software, board layout and pin loading.

| Symbol           | Parameter        | Conditions                                                             |                             |                                                       |                  |      |

|------------------|------------------|------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------|------------------|------|

|                  |                  | General conditions                                                     | Monitored<br>frequency band | Max f <sub>HSE</sub> /f <sub>CPU</sub> <sup>(1)</sup> |                  | Unit |

|                  |                  |                                                                        |                             | 8 MHz/<br>8 MHz                                       | 8 MHz/<br>16 MHz |      |

| S <sub>EMI</sub> | Peak level       | $V_{DD} = 5 V$<br>$T_A = 25 °C$<br>LQFP48 package<br>conforming to SAE | 0.1 MHz to 30 MHz           | 13                                                    | 14               | dBµV |

|                  |                  |                                                                        | 30 MHz to 130 MHz           | 23                                                    | 19               |      |

|                  |                  |                                                                        | 130 MHz to 1 GHz            | -4.0                                                  | -4.0             |      |

|                  | SAE EMI<br>level | IEC 61967-2                                                            | -                           | 2.0                                                   | 1.5              |      |

1. Data based on characterization results, not tested in production.

### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### **Electrostatic discharge (ESD)**

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model) | $T_A = 25^{\circ}C$ , conforming to JESD22-A114  | А     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to JESD22-C101 | IV    | 1000                            | V    |

| Table 48 | . ESD | absolute | maximum | ratings |

|----------|-------|----------|---------|---------|

|----------|-------|----------|---------|---------|

1. Data based on characterization results, not tested in production.

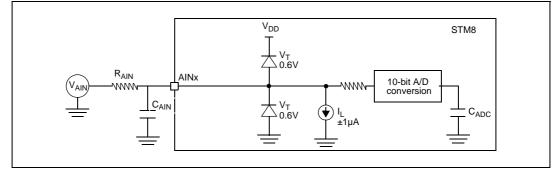

# 10 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at *www.st.com*. ECOPACK® is an ST trademark.

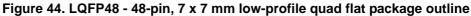

# 10.1 LQFP48 package information

1. Drawing is not to scale.

DocID022186 Rev 4

Figure 45. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

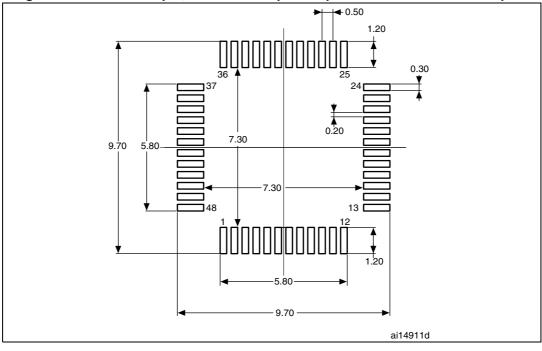

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 46. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

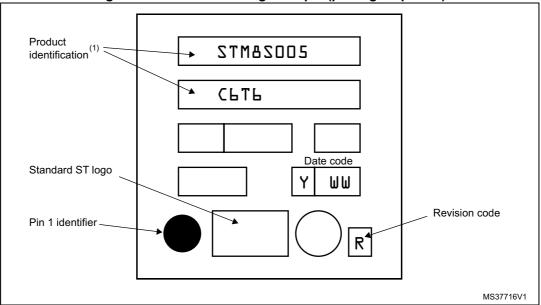

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

### **10.3** Thermal characteristics

The maximum chip junction temperature (T<sub>Jmax</sub>) must never exceed the values given in *Table 17: General operating conditions*.

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$

Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance in ° C/W

- P<sub>Dmax</sub> is the sum of P<sub>INTmax</sub> and P<sub>I/Omax</sub> (P<sub>Dmax</sub> = P<sub>INTmax</sub> + P<sub>I/Omax</sub>)

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins, where: P<sub>I/Omax</sub> = Σ (V<sub>OL</sub>\*I<sub>OL</sub>) + Σ((V<sub>DD</sub>-V<sub>OH</sub>)\*I<sub>OH</sub>), and taking account of the actual V<sub>OL</sub>/I<sub>OL</sub> and V<sub>OH</sub>/I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                 | Value | Unit |

|-----------------|-----------------------------------------------------------|-------|------|

| 0               | Thermal resistance junction-ambient<br>LQFP 48 - 7 x 7 mm | 57    | °C/W |

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP 32 - 7 x 7 mm | 60    | °C/W |

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

### 10.3.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.