Welcome to E-XFL.COM

### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

## Details

| Product Status                  | Obsolete                                                    |

|---------------------------------|-------------------------------------------------------------|

| Programmable Type               | In System Programmable                                      |

| Delay Time tpd(1) Max           | 10 ns                                                       |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                   |

| Number of Logic Elements/Blocks | 8                                                           |

| Number of Macrocells            | 128                                                         |

| Number of Gates                 | 2500                                                        |

| Number of I/O                   | 98                                                          |

| Operating Temperature           | 0°C ~ 70°C (TA)                                             |

| Mounting Type                   | Surface Mount                                               |

| Package / Case                  | 256-BGA                                                     |

| Supplier Device Package         | 256-FBGA (17x17)                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm3128afc256-10 |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Macrocells

MAX 3000A macrocells can be individually configured for either sequential or combinatorial logic oper ation. Macrocells consist of three functional blocks: logic array, product–term select matrix, and programmable register. Figure 2 shows a MAX 3000A macrocell.

Figure 2. MAX 3000A Macrocell

Combinatorial logic is implemented in the logic array, which provides five product terms per macrocell. The product–term select matrix allocates these product terms for use a wither primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as secondary inputs to the macrocell's register preset, clock, and clock enable control functions.

Two kinds of expander product terms ("expanders") are available to supplement macrocell logic resources:

- Shareable expanders, which are inverted product terms that are fed back into the logic array

- Parallel expanders, which are product terms borrowed from adjacent macrocells

The Altera development system automatically optimizes product–term allocation according to the logic requirements of the design.

#### Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 20 product terms to directly feed the macrocell OR logic, with five product term s provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB.

The Altera development system compiler can automatically allocate up to three sets of up to five parallel expanders to the macrocells that require additional product terms. Each set of five parallel expanders incurs a small, incremental timing delay ( $t_{PXP}$ ). For example, if a macrocell requires 14 product terms, the compiler uses the five dedicated product terms within the macrocell and allocate s two sets of parallel expanders; the first set includes five product terms, and the second set includes four product terms, increasing the total delay by  $2 \times t_{PXP}$ .

Two groups of eight macrocells within each LAB (e.g., macrocells 1 through 8 and 9 through 16) form tw o chains to lend or borrow parallel expanders. A macrocell borrows parallel expanders from lower– numbered macrocells. For example, macrocell 8 can borrow parallel expanders from macrocells 7, for macrocells 7 and 6, or from macrocells 7, 6, and 5. Within each group of eight, the lowest–numbered macrocell can only lend parallel expanders and the highest–numbered macrocell can only borrow them. Figure 4 shows how parallel expanders can be borrowed from a neighboring macrocell.

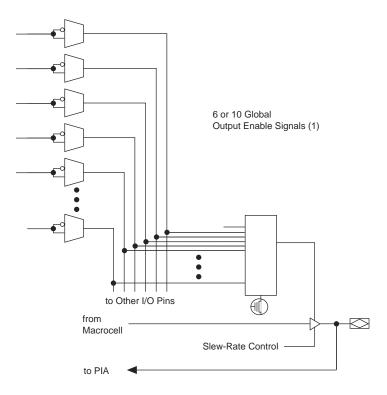

Figure 6. I/O Control Block of MAX 3000A Devices

Note:

(1) EPM3032A, EPM3064A, EPM3128A, and EPM3256A devices have six output enables. EPM3512A devices have 10 output enables.

When the tri–state buffer control is connected to ground, the output is tri-stated (high impedance), and the I/O pin can be used as a dedicated input. When the tri–state buffer control is connected to V  $_{CC}$ , the output is enabled.

The MAX 3000A architecture provid es dual I/O feedback, in which macrocell and pin feedbacks are independent. When an I/O pin is configured as an input, the associated macrocell can be used for buried logic.

## **Programming Sequence**

During in-system progra mming, instructions, addresses, and data are shifted into the MAX 3000A device through the TDI input pin. Data is shifted out through the TDO output pin and compared against the expected data.

Programming a pattern into the device requires the following six ISP stages. A stand-alone verification of a programmed pattern involves only stages 1, 2, 5, and 6.

- ter P . The enter ISP stage ensures that the I/O pins transition smoothly from user mode to ISP mode. The enter ISP stage requires 1 ms.

- 2. Chec . Before any program or verify process, the silicon ID is checked. The time required to read this silicon ID is relatively small compared to the overall programming time.

- 3. **1 rase** . Erasing the device in-system involves shifting in the instructions to erase the device and applying one erase pulse of 100 ms.

- 4. **Program** Programming the device in-system involves shifting in the address and data and then applying the programming pulse to program the EEPROM cells. This process is repeated for each EEPROM address.

- 5. **erif** . Verifying an Altera device in-system involves shifting in addresses, applying the read pulse to verify the EEPROM cells, and shifting out the data for comparis on. This process is repeated for each EEPROM address.

- it P . An exit ISP stage ensures that the I/O pins transition smoothly from ISP mode to user mode. The exit ISP stage requires 1 ms.

# **Programming Times**

The time required to implement each of the six programming stages can be broken into the following two elements:

- A pulse time to erase, program, or read the EEPROM cells.

- A shifting time based on the test clock (TCK) frequency and the number of TCK cycles to shift instructions, address, and data into the device.

By combining the pulse and shift ti mes for each of the programming stages, the program or verify time can be derived as a function of the TCK frequency, the number of devices, and specific target device(s). Because different ISP-capable devices have a different number of EEPROM cells, both the total fixed and total variable times are unique for a single device.

## Programming a Single MAX 3000A Device

The time required to program a single MAX 3000A device in-system can be calculated from the following formula:

| t <sub>P</sub> = | <sup>= t</sup> ppul                                             | $+\frac{Ccle_{PC}}{f_{C}}$                                                                                          |

|------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| where:           | t <sub>P</sub><br>t <sub>PPUL</sub>                             | <ul> <li>Programming time</li> <li>Sum of the fixed times to erase, program, and verify the EEPROM cells</li> </ul> |

|                  | $\begin{array}{l} \text{Ccle}_{PC} \\ \text{f}_{C} \end{array}$ | <ul> <li>Number of TCK cycles to program a device</li> <li>TCK frequency</li> </ul>                                 |

The ISP times for a stand-alone verification of a single MAX 3000A device can be calculated from the following formula:

| t = t <sub>PUL</sub>                              | $+\frac{C \operatorname{cle} C}{f_{C}}$                                                                                                     |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| where: t<br>t <sub>PUL</sub><br>Ccle <sub>C</sub> | <ul> <li>Verify time</li> <li>Sum of the fixed times to verify the EEPROM cells</li> <li>Number of TCK cycles to verify a device</li> </ul> |

The programming times described in Tables 4through 6 are associated with the worst-case method using the enhanced ISP algorithm.

| Table 4. MAX 3000A t <sub>PULSE</sub> & Cycle <sub>TCK</sub> Values |                         |                       |                          |                       |  |  |  |  |  |

|---------------------------------------------------------------------|-------------------------|-----------------------|--------------------------|-----------------------|--|--|--|--|--|

| Device                                                              | Programming             |                       | Stand-Alone Verification |                       |  |  |  |  |  |

|                                                                     | t <sub>PPULSE</sub> (s) | Cycle <sub>PTCK</sub> | t <sub>VPULSE</sub> (s)  | Cycle <sub>VTCK</sub> |  |  |  |  |  |

| EM3032A                                                             | 2.00                    | 55,000                | 0.002                    | 18,000                |  |  |  |  |  |

| EM3064A                                                             | 2.00                    | 105,000               | 0.002                    | 35,000                |  |  |  |  |  |

| EM3128A                                                             | 2.00                    | 205,000               | 0.002                    | 68,000                |  |  |  |  |  |

| <b>EM</b> 3256A                                                     | 2.00                    | 447,000               | 0.002                    | 149,000               |  |  |  |  |  |

| <b>EM</b> 3512A                                                     | 2.00                    | 890,000               | 0.002                    | 297,000               |  |  |  |  |  |

Tables 5 and 6 show the in-system programming and stand alone verification times for several common test clock frequencies.

| Device  |        | f <sub>TCK</sub> |       |       |         |         |         |        |   |  |

|---------|--------|------------------|-------|-------|---------|---------|---------|--------|---|--|

|         | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |   |  |

| EM3032A | 2.01   | 2.01             | 2.03  | 2.06  | 2.11    | 2.28    | 2.55    | 3.10   | s |  |

| EM3064A | 2.01   | 2.02             | 2.05  | 2.11  | 2.21    | 2.53    | 3.05    | 4.10   | s |  |

| EM3128A | 2.02   | 2.04             | 2.10  | 2.21  | 2.41    | 3.03    | 4.05    | 6.10   | s |  |

| EM3256A | 2.05   | 2.09             | 2.23  | 2.45  | 2.90    | 4.24    | 6.47    | 10.94  | s |  |

| EM3512A | 2.09   | 2.18             | 2.45  | 2.89  | 3.78    | 6.45    | 10.90   | 19.80  | s |  |

| Table 6. MAX 3000A Stand-Alone Verification Times for Different Test Clock Frequencies |        |                  |       |       |         |         |         |        |   |  |

|----------------------------------------------------------------------------------------|--------|------------------|-------|-------|---------|---------|---------|--------|---|--|

| Device                                                                                 |        | f <sub>TCK</sub> |       |       |         |         |         |        |   |  |

|                                                                                        | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |   |  |

| EM3032A                                                                                | 0.00   | 0.01             | 0.01  | 0.02  | 0.04    | 0.09    | 0.18    | 0.36   | s |  |

| EM3064A                                                                                | 0.01   | 0.01             | 0.02  | 0.04  | 0.07    | 0.18    | 0.35    | 0.70   | s |  |

| EM3128A                                                                                | 0.01   | 0.02             | 0.04  | 0.07  | 0.14    | 0.34    | 0.68    | 1.36   | s |  |

| EM3256A                                                                                | 0.02   | 0.03             | 0.08  | 0.15  | 0.30    | 0.75    | 1.49    | 2.98   | s |  |

| EM3512A                                                                                | 0.03   | 0.06             | 0.15  | 0.30  | 0.60    | 1.49    | 2.97    | 5.94   | s |  |

# Programming with External Hardware

MAX 3000A devices can be programmed on Windows–based PCs with an Altera Logic Programmer card, MPU, and the appropriate device adapter. The MPU performs continuity checking to ensure adequate electrical contact between the adapter and the device.

For more information, see the Altera Programmig Harware ata heet

The Altera software can use text- or waveform-format test vectors created with the Altera Text Editor or Wav eform Editor to test the programmed device. For added design verification, designers can perform functional testing to compare the functional device behavior with the results of simulation.

Data I/O, BP Microsystems, and other programming hardware manufacturers also provide programming support for Altera devices.

For more information, see Programmig Harwa re Mafactrers

# IEEE Std. 1149.1 (JTAG) Boundary–Scan Support

MAX 3000A devices include the JTAG BST circuitry defined by IEEE Std. 1149.1–1990Table 7 describes the JTAG instructions supported by MAX 3000A devices. The pin-out tables found on the Altera web site (http://www.altera.com) or the Altera igital Librar show the location of the JTAG control pins for each device. If the JTAG interface is not required, the JTAG pins are available as user I/O pins.

| JTAG Instructi  | on   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLEEOAD      | •    | Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Sectification<br>Se |

| <b>KTG</b> T    | AI   | lowine exernal circui try andboar Devel interconnection sto be tesedby forcing a tespattern at the output pinsandcapturing tes resits at the input pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BASS            | PI   | acesthe 1Đit bypas sregiter betwen the TDI and TDO pinstwich allowihe BT<br>dta to pasynchronoutly through a elect eddvice to apicent elvicesdring normal<br>elvice operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DCODE           | S    | electsthe DCODE egis er andplaces tbetwen the TDI and TDO pinsallowing the DCODE to be erially biftedout of TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| US <b>B</b> ODE | Sele | ectsche 32Dit USBCODEregiser andplacest betwen the TDI and TDO pins allowing the USBCODEralue to be biftedout of TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6P heructions   | Т    | hes instructionsare use when programming MAX 3000A elvices via the JTA Georts<br>wh the MaterBater, GateBaterMV, or BBBater cable, or when using a Jam STAPL<br>file, JB file, or SVF file via an embeeledproces ror test equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

The instruction register length of MAX 3000A devices is 10 bits. The IDCODE and USERCODE register length is 32 bits. Tables 8 and 9 show the boundary–scan register length and device IDCODE information for MAX 3000A devices.

| Table 8. MAX 3000A Boundary–Scan Register Length |                               |  |  |  |  |  |

|--------------------------------------------------|-------------------------------|--|--|--|--|--|

| Device                                           | Boundary–Scan Register Length |  |  |  |  |  |

| EM3032A                                          | 96                            |  |  |  |  |  |

| <b>EM</b> 3064A                                  | 192                           |  |  |  |  |  |

| <b>EM</b> 3128A                                  | 288                           |  |  |  |  |  |

| <b>EM</b> 3256A                                  | 480                           |  |  |  |  |  |

| EM3512A                                          | 624                           |  |  |  |  |  |

| Table 9. 32–Bit MAX 3000A Device IDCODE Value       Note (1) |                     |                       |                                      |                  |  |  |  |  |  |  |

|--------------------------------------------------------------|---------------------|-----------------------|--------------------------------------|------------------|--|--|--|--|--|--|

| Device                                                       |                     | IDCODE (32 bits)      |                                      |                  |  |  |  |  |  |  |

|                                                              | Version<br>(4 Bits) | Part Number (16 Bits) | Manufacturer's<br>Identity (11 Bits) | 1 (1 Bit)<br>(2) |  |  |  |  |  |  |

| <b>EM3032A</b>                                               | 0001                | 0111 0000 0011 0010   | 00001101110                          | 1                |  |  |  |  |  |  |

| EM3064A                                                      | 0001                | 0111 0000 0110 0100   | 00001101110                          | 1                |  |  |  |  |  |  |

| EM3128A                                                      | 0001                | 0111 0001 0010 1000   | 00001101110                          | 1                |  |  |  |  |  |  |

| EM3256A                                                      | 0001                | 0111 0010 0101 0110   | 00001101110                          | 1                |  |  |  |  |  |  |

| EM3512A                                                      | 0001                | 0111 0101 0001 0010   | 00001101110                          | 1                |  |  |  |  |  |  |

Notes:

(1) The most significant bit (MSB) is on the left.

(2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

...

SeeApplicatio ote . A oarca est ig i Altera evices for more information on JTAG BST.

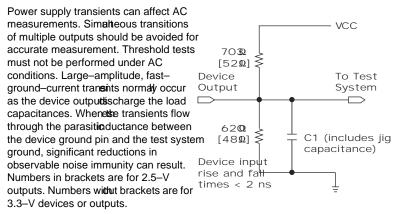

#### Figure 8. MAX 3000A AC Test Conditions

# Operating Conditions

Tables 12through 15 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for MAX 3000A devices.

| Table 1          | 2. MAX 3000A Device Absolu   | te Maximum Ratings Note (1)    |             |                   |    |  |  |

|------------------|------------------------------|--------------------------------|-------------|-------------------|----|--|--|

| Symbol           | Parameter Conditions Min Max |                                |             |                   |    |  |  |

| v <sub>cc</sub>  | Supply voltage               | With repect to groun(2)        | <b>Đ</b> .5 | 4.6               | v  |  |  |

| VI               | DC input voltage             |                                | Ð.0         | 5.75              | v  |  |  |

| I <sub>OUT</sub> | DC output current, per pin   |                                | <b>£</b> 5  | 25                | mA |  |  |

| T <sub>STG</sub> | Storage temperature          | No bias                        | 65          | 150               | iC |  |  |

| T <sub>A</sub>   | Ambient temperature          | Un <b>e</b> r bias             | 605         | 135               | ίC |  |  |

| Tj               | Junction temperature         | PGP and TGP packages undr bias | 13          | 35 i <sup>(</sup> | 2  |  |  |

# Tables 16through 23 show EPM3032A, EPM3064A, EPM3128A, EPM3256A, and EPM3512A timing information.

| Symbol            | Parameter                                                   | Conditions                     |       |     | Speed | Grade |       |     | Unit |

|-------------------|-------------------------------------------------------------|--------------------------------|-------|-----|-------|-------|-------|-----|------|

|                   |                                                             |                                | _     | 4   | -7    |       | -10   |     |      |

|                   |                                                             |                                | Min   | Max | Min   | Max   | Min   | Мах |      |

| t <sub>PD1</sub>  | hput to nonĐ<br>regiteredoutput                             | C1 <b>⊰</b> 5 pF<br><i>(2)</i> |       | 4.5 |       | 7.5   |       | 10  | ns   |

| t <sub>PD2</sub>  | D input to nonĐ<br>regiteredoutput                          | C1 <b>⊰</b> 5 pF<br>(2)        |       | 4.5 |       | 7.5   |       | 10  | ns   |

| t <sub>SU</sub>   | <b>lo</b> bal cloc <b>le</b> tup<br>time                    | (2)                            | 2.9   |     | 4.7   |       | 6.3   |     | ns   |

| t <sub>H</sub>    | Cobal clockholdime                                          | (2)                            | 0.0   |     | 0.0   |       | 0.0   |     | ns   |

| t <sub>CO1</sub>  | <b>lò</b> bal cloc <b>k</b> o output<br><b>e</b> lay        | C1 <b>⊰</b> 5 pF               | 1.0   | 3.0 | 1.0   | 5.0   | 1.0   | 6.7 | ns   |

| t <sub>CH</sub>   | Gbal clockhigh time                                         |                                | 2.0   |     | 3.0   |       | 4.0   |     | ns   |

| t <sub>CL</sub>   | Gobal clocklowime                                           |                                | 2.0   |     | 3.0   |       | 4.0   |     | ns   |

| t <sub>ASU</sub>  | Array clocketup time                                        | (2)                            | 1.6   |     | 2.5   |       | 3.6   |     | ns   |

| t <sub>AH</sub>   | Array clockholdime                                          | (2)                            | 0.3   |     | 0.5   |       | 0.5   |     | ns   |

| t <sub>ACO1</sub> | Array clocko output<br>ellay                                | C1 <b>⊰</b> 5 pF<br><i>(2)</i> | 1.0   | 4.3 | 1.0   | 7.2   | 1.0   | 9.4 | ns   |

| t <sub>ACH</sub>  | Array clockhigh time                                        |                                | 2.0   |     | 3.0   |       | 4.0   |     | ns   |

| t <sub>ACL</sub>  | Array clockowime                                            |                                | 2.0   |     | 3.0   |       | 4.0   |     | ns   |

| t <sub>CPPW</sub> | Minimum pul <b>e iw</b> h<br>for clear anфre <del>s</del> t | (3)                            | 2.0   |     | 3.0   |       | 4.0   |     | ns   |

| t <sub>CNT</sub>  | Minimum global clocl<br>period                              | ( <i>2</i> )                   |       | 4.4 |       | 7.2   |       | 9.7 | ns   |

| f <sub>CNT</sub>  | Maimum internal<br>global clockfreqency                     | (2), (4)                       | 227.3 |     | 138.9 |       | 103.1 |     | MHz  |

| t <sub>ACNT</sub> | Minimum array clock<br>period                               | (2)                            |       | 4.4 |       | 7.2   |       | 9.7 | ns   |

| f <sub>ACNT</sub> | Maimum internal<br>array clockfregency                      | (2), (4)                       | 227.3 |     | 138.9 |       | 103.1 |     | MHz  |

٦

Г

MAX 3000A Programmable Logic Device Family Data Sheet

| Symbol            | Parameter                                                                         | Conditions            | Speed Grade |     |     |     |     |      | Unit |  |

|-------------------|-----------------------------------------------------------------------------------|-----------------------|-------------|-----|-----|-----|-----|------|------|--|

|                   |                                                                                   |                       | -           | -4  | -7  |     | -10 |      |      |  |

|                   |                                                                                   |                       | Min         | Max | Min | Мах | Min | Мах  |      |  |

| t <sub>IN</sub>   | hput padandbuffer ellay                                                           |                       |             | 0.7 |     | 1.2 |     | 1.5  | ns   |  |

| tio               | D input padandbuffer<br>dlay                                                      |                       |             | 0.7 |     | 1.2 |     | 1.5  | ns   |  |

| t <sub>SEXP</sub> | Sharedeppanelr ellay                                                              |                       | 1           | 9   | 3   | .1  | 4   | .0   | ns   |  |

| t <sub>PEXP</sub> | Parallel epandr dlay                                                              |                       |             | 0.5 |     | 0.8 |     | 1.0  | ns   |  |

| t <sub>LAD</sub>  | Logic array <b>d</b> lay                                                          |                       |             | 1.5 |     | 2.5 |     | 3.3  | ns   |  |

| t <sub>LAC</sub>  | Logic control array dlay                                                          |                       |             | 0.6 |     | 1.0 |     | 1.2  | ns   |  |

| t <sub>IOE</sub>  | hternal output enable <b>d</b> lay                                                |                       |             | 0.0 |     | 0.0 |     | 0.0  | ns   |  |

| t <sub>OD1</sub>  | Output buffer anopad<br>ellay, bovbewrate =off<br>V <sub>CCD</sub> =3.3 V         | C1 <del>.3</del> 5 pF |             | 0.8 |     | 1.3 |     | 1.8  | ns   |  |

| t <sub>OD2</sub>  | Output buffer anopad<br>ellay, bowbewrate =off<br>V <sub>CCD</sub> =2.5 V         | C1 <b>⊰</b> 5 pF      |             | 1.3 |     | 1.8 |     | 2.3  | ns   |  |

| t <sub>OD3</sub>  | Output buffer andpad<br>ellay, bowbewrate =on<br>V <sub>CCD</sub> =2.5 V or 3.3 V | C1 <del>.3</del> 5 pF |             | 5.8 |     | 6.3 |     | 6.8  | ns   |  |

| t <sub>ZX1</sub>  | Output buffer enable ellay,<br>kowkewrate =off<br>V <sub>CCD</sub> =3.3 V         | C1 <b>⊰</b> 5 pF      |             | 4.0 |     | 4.0 |     | 5.0  | ns   |  |

| t <sub>ZX2</sub>  | Output buffer enable dlay,<br>townewrate =off<br>V <sub>CCD</sub> =2.5 V          | C1 <b>⊰</b> 5 pF      |             | 4.5 |     | 4.5 |     | 5.5  | ns   |  |

| t <sub>ZX3</sub>  | Output buffer enable dlay,<br>towtewrate =on<br>V <sub>CCD</sub> =2.5 V or 3.3 V  | C1 <del>.3</del> 5 pF |             | 9.0 |     | 9.0 |     | 10.0 | ns   |  |

| $t_{XZ}$          | Output buffer idsble ellay                                                        | :1 =5 pF              |             | 4.0 |     | 4.0 |     | 5.0  | ns   |  |

| t <sub>SU</sub>   | Rgiter etup time                                                                  |                       | 1.3         |     | 2.0 |     | 2.8 |      | ns   |  |

| t <sub>H</sub>    | ₿giter holdtime                                                                   |                       | 0.6         |     | 1.0 |     | 1.3 |      | ns   |  |

| t <sub>RD</sub>   | Rigiser ellay                                                                     |                       |             | 0.7 |     | 1.2 |     | 1.5  | ns   |  |

| t <sub>COMB</sub> | Combinatorial dlay                                                                |                       |             | 0.6 |     | 1.0 |     | 1.3  | ns   |  |

| t <sub>IC</sub>   | Array cloc <b>id</b> iay                                                          |                       |             | 1.2 |     | 2.0 |     | 2.5  | ns   |  |

| t <sub>EN</sub>   | Rgiter enable time                                                                |                       |             | 0.6 |     | 1.0 |     | 1.2  | ns   |  |

| t <sub>GLOB</sub> | Cobal control ellay                                                               |                       |             | 0.8 |     | 1.3 |     | 1.9  | ns   |  |

| t <sub>PRE</sub>  | Rigiser prest time                                                                |                       |             | 1.2 |     | 1.9 |     | 2.6  | ns   |  |

| t <sub>CLR</sub>  | Rigiter clear time                                                                |                       |             | 1.2 |     | 1.9 |     | 2.6  | ns   |  |

| Table 17. EPM3032A Internal Timing Parameters (Part 2 of 2)       Note (1) |                  |            |                       |     |     |     |     |      |    |

|----------------------------------------------------------------------------|------------------|------------|-----------------------|-----|-----|-----|-----|------|----|

| Symbol                                                                     | Parameter        | Conditions | onditions Speed Grade |     |     |     |     | Unit |    |

|                                                                            |                  |            | -4                    |     | -7  |     | -10 |      |    |

|                                                                            |                  |            | Min                   | Мах | Min | Max | Min | Max  |    |

| t <sub>PIA</sub>                                                           | <b>PIA di</b> ay | (2)        |                       | 0.9 |     | 1.5 |     | 2.1  | ns |

| t <sub>LPA</sub>                                                           | Loppoevraelr     | (5)        |                       | 2.5 |     | 4.0 |     | 5.0  | ns |

| Symbol            | Parameter                                        | Conditions            |     | Speed Grade |     |       |                  |       |      |     |

|-------------------|--------------------------------------------------|-----------------------|-----|-------------|-----|-------|------------------|-------|------|-----|

|                   |                                                  |                       |     | -4          |     | -7    |                  | -10   |      |     |

|                   |                                                  |                       |     | Min         | Мах | Min   | Мах              | Min   | Max  |     |

| t <sub>PD1</sub>  | hput to non£egisered<br>output                   | C1 <b>⊰</b> 5 pF      | (2) |             | 4.5 |       | 7.5              |       | 10.0 | ns  |

| t <sub>PD2</sub>  | D input to nonBegitered output                   | C1 <b>⊰</b> 5 pF      | (2) |             | 4.5 |       | 7.5              |       | 10.0 | ns  |

| t <sub>SU</sub>   | Cobal clocketup time                             | (2)                   |     | 2.8         |     | 4.7   |                  | 6.2   |      | ns  |

| t <sub>H</sub>    | Cobal clockholdime                               | (2)                   |     | 0.0         |     | 0.0   |                  | 0.0   |      | ns  |

| t <sub>CO1</sub>  | Cobal clockto output ellay C                     | :1 <del>.3</del> 5 pF |     | 1.0         | 3.1 | 1.0 5 | 5.1 <sup>·</sup> | 1.0   | 7.0  | ns  |

| t <sub>CH</sub>   | Cobal clockhigh time                             |                       |     | 2.0         |     | 3.0   |                  | 4.0   |      | ns  |

| t <sub>CL</sub>   | Cobal clocklowime                                |                       |     | 2.0         |     | 3.0   |                  | 4.0   |      | ns  |

| t <sub>ASU</sub>  | Array clocletup time                             | (2)                   |     | 1.6         |     | 2.6   |                  | 3.6   |      | ns  |

| t <sub>AH</sub>   | Array clockholdime                               | (2)                   |     | 0.3         |     | 0.4   |                  | 0.6   |      | ns  |

| t <sub>ACO1</sub> | Array clockto output ellay                       | C1 <b>⊰</b> 5 pF      | (2) | 1.0         | 4.3 | 1.0   | 7.2              | 1.0   | 9.6  | ns  |

| t <sub>ACH</sub>  | Array clockhigh time                             |                       |     | 2.0         |     | 3.0   |                  | 4.0   |      | ns  |

| t <sub>ACL</sub>  | Array clockowime                                 |                       |     | 2.0         |     | 3.0   |                  | 4.0   |      | ns  |

| t <sub>CPPW</sub> | Minimum pul <b>e itt</b> h for<br>clear andprest | (3)                   |     | 2.0         |     | 3.0   |                  | 4.0   |      | ns  |

| t <sub>CNT</sub>  | Minimum global clock<br>period                   | (2)                   |     |             | 4.5 |       | 7.4              |       | 10.0 | ns  |

| f <sub>CNT</sub>  | Maimum internal global<br>clocifreqency          | (2), (4)              |     | 222.2       |     | 135.1 |                  | 100.0 |      | MHz |

| t <sub>ACNT</sub> | Minimum array clockperiod                        | (2)                   |     |             | 4.5 |       | 7.4              |       | 10.0 | ns  |

| f <sub>ACNT</sub> | Maimum internal array<br>clockfreqency           | (2), (4)              |     | 222.2       |     | 135.1 |                  | 100.0 |      | MHz |

| Table 20. EPM3128A External Timing Parameters       Note (1) |                                        |            |                     |     |       |     |      |     |     |

|--------------------------------------------------------------|----------------------------------------|------------|---------------------|-----|-------|-----|------|-----|-----|

| Symbol                                                       | Parameter                              | Conditions | ns Speed Grade Unit |     |       |     |      |     |     |

|                                                              |                                        |            | _!                  | 5   | _     | 7   | -10  |     |     |

|                                                              |                                        |            | Min                 | Max | Min   | Max | Min  | Max |     |

| f <sub>ACNT</sub>                                            | Maimum internal<br>array clockfreqency | (2), (4)   | 192.3               |     | 129.9 |     | 98.0 |     | MHz |

| Symbol            | Parameter                                                                         | Conditions            | Speed Grade |     |     |     |     |      |    |

|-------------------|-----------------------------------------------------------------------------------|-----------------------|-------------|-----|-----|-----|-----|------|----|

|                   |                                                                                   |                       | -5          |     | -7  |     | -10 |      |    |

|                   |                                                                                   |                       | Min         | Мах | Min | Max | Min | Max  |    |

| t <sub>IN</sub>   | hput padandbuffer ellay                                                           |                       |             | 0.7 |     | 1.0 |     | 1.4  | ns |

| t <sub>IO</sub>   | D input padandbuffer<br>dlay                                                      |                       |             | 0.7 |     | 1.0 |     | 1.4  | ns |

| t <sub>SEXP</sub> | Sharedepeaneir eilay                                                              |                       | 2           | .0  | 2   | .9  | 3   | .8 I | ıs |

| t <sub>PEXP</sub> | Parallel epandr dlay                                                              |                       |             | 0.4 |     | 0.7 |     | 0.9  | ns |

| t <sub>LAD</sub>  | Logic array <b>d</b> lay                                                          |                       |             | 1.6 |     | 2.4 |     | 3.1  | ns |

| t <sub>LAC</sub>  | Logic control array dlay                                                          |                       |             | 0.7 |     | 1.0 |     | 1.3  | ns |

| t <sub>IOE</sub>  | hternal output enable <b>e</b> lay                                                |                       |             | 0.0 |     | 0.0 |     | 0.0  | ns |

| t <sub>OD1</sub>  | Output buffer anopad<br>ellay, bowbewrate =off<br>V <sub>CCD</sub> =3.3 V         | C1 <del>.3</del> 5 pF |             | 0.8 |     | 1.2 |     | 1.6  | ns |

| t <sub>OD2</sub>  | Output buffer andpad<br>ellay, bowbewrate =off<br>V <sub>CCD</sub> =2.5 V         | C1 <del>3</del> 5 pF  |             | 1.3 |     | 1.7 |     | 2.1  | ns |

| t <sub>OD3</sub>  | Output buffer andpad<br>ellay, bovbewrate =on<br>V <sub>CCD</sub> =2.5 V or 3.3 V | C1 <del>.3</del> 5 pF |             | 5.8 |     | 6.2 |     | 6.6  | ns |

| t <sub>ZX1</sub>  | Output buffer enable ellay,<br>bowbewrate =off<br>V <sub>CCD</sub> =3.3 V         | C1 <del>.3</del> 5 pF |             | 4.0 |     | 4.0 |     | 5.0  | ns |

| t <sub>ZX2</sub>  | Output buffer enable ellay,<br>bowbewrate =off<br>V <sub>CCD</sub> =2.5 V         | C1 <del>.3</del> 5 pF |             | 4.5 |     | 4.5 |     | 5.5  | ns |

| t <sub>ZX3</sub>  | Output buffer enable dlay,<br>bowbewrate =on<br>V <sub>CCD</sub> =2.5 V or 3.3 V  | C1 <del>.3</del> 5 pF |             | 9.0 |     | 9.0 |     | 10.0 | ns |

| t <sub>XZ</sub>   | Output buffer idsble ellay O                                                      | 1 –5 pF               |             | 4.0 |     | 4.0 |     | 5.0  | ns |

Г

٦

| Symbol           | Parameter                                                                         | Conditions        |     | Unit |     |      |    |

|------------------|-----------------------------------------------------------------------------------|-------------------|-----|------|-----|------|----|

|                  |                                                                                   |                   |     | -7   | -10 |      | -  |

|                  |                                                                                   |                   | Min | Max  | Min | Мах  | 1  |

| ОДЗ              | Output buffer anopbadellay,<br>bowbewaate ≠on<br>V <sub>CCD</sub> =2.5 V or 3.3 V | C1 <i>=</i> 35 pF |     | 6.0  |     | 6.5  | ns |

| tzx1             | Output buffer enable dlay,<br>bowbewrate ≠off<br>V <sub>CCD</sub> =3.3 V          | C1 <i>=</i> 35 pF |     | 4.0  |     | 5.0  | ns |

| t <sub>ZX2</sub> | Output buffer enable dlay,<br>kowkewrate =off<br>V <sub>CCD</sub> =2.5 V          | C1 <i>=</i> 35 pF |     | 4.5  |     | 5.5  | ns |

| t <sub>ZX3</sub> | Output buffer enable dlay,<br>bowbewrate ≈on<br>V <sub>CCD</sub> =3.3 V           | C1 <i>=</i> 35 pF |     | 9.0  |     | 10.0 | ns |

| t <sub>XZ</sub>  |                                                                                   | C1 =5 pF          |     | 4.0  |     | 5.0  | ns |

| รบ               | Rigiser etup time                                                                 |                   | 2.1 |      | 3.0 |      | ns |

| Н                | Bigiter holdtime                                                                  |                   | 0.6 |      | 0.8 |      | ns |

| FSU              | Egiter etup time of fatinput                                                      |                   | 1.6 |      | 1.6 |      | ns |

| t <sub>FH</sub>  | Regiser holdtime of fastinput                                                     |                   | 1.4 |      | 1.4 |      | ns |

| t <sub>RD</sub>  | Elgiteer ellay                                                                    |                   |     | 1.3  |     | 1.7  | ns |

| сомв             | Combinatorial dlay                                                                |                   |     | 0.6  |     | 0.8  | ns |

| lic              | Array clociday                                                                    |                   |     | 1.8  |     | 2.3  | ns |

| t <sub>EN</sub>  | Rgiter enable time                                                                |                   |     | 1.0  |     | 1.3  | ns |

| GLOB             | Cobal control diay                                                                |                   |     | 1.7  |     | 2.2  | ns |

| PRE              | Rigiter prest time                                                                |                   |     | 1.0  |     | 1.4  | ns |

| t <sub>CLR</sub> | Rigiter clear time                                                                |                   |     | 1.0  |     | 1.4  | ns |

| t <sub>PIA</sub> | PIA ellay                                                                         | (2)               |     | 3.0  |     | 4.0  | ns |

| t <sub>LPA</sub> | Lopeoneraetr                                                                      | (5)               |     | 4.5  |     | 5.0  | ns |

Notes to tables:

- (1) These values are specified under the recommended operating conditions, as shown in Table 13 on page 23 See Figure 11 on page 27 for more information on switching waveforms.

- (2) These values are specified for a PIA fan-out of one LAB(16 macrocells). For each additional LAB fan-out in these devices, add an additional 0.1 ns to the PIA timing value.

- (3) This minimum pulse width for preset and clear app lies for both global clear and array controls. The  $t_{LPA}$  parameter must be added to this minimum width if the clear or reset signal incorporates the  $t_{LA}$  parameter into the signal path.

- (4) These parameters are measured with a 16-bit loadableenabled, up/down counter programmed into each LAB.

- (5) The  $t_{LPA}$  parameter must be added to the  $t_{LA}$ ,  $t_{LAC}$ ,  $t_{C}$ ,  $t_{C}$ ,  $t_{ACL}$ , and  $t_{CPPW}$  parameters for macrocells running in low-power mode.

| Power<br>Consumption | Supply power (P) versus frequency (f $_{\rm MAX}$ , in MHz) for MAX 3000A devices is calculated with the following equation:                         |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|-------------------------------------------------------|---|--|--|--|

| eene ann prion       | $P = P_{INT} + P_{IO} = I_{CCINT} \times V_{CC} + P_{IO}$                                                                                            |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      |                                                                                                                                                      | ning                                                                                                                                        | frequency, c                                        |                  | ce output load o<br>d using the guic<br>Altera evices |   |  |  |  |

|                      | The $I_{CCINT}$ value depends on the switching frequency and the application logic. The $I_{CCINT}$ value is calculated with the following equation: |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | I <sub>CCINT</sub> =                                                                                                                                 |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | $(A \times MC_TON) + [B \times (MC_DEV - MC_TON)] + (C \times MC_USED \times f_MAX \times tog_LC)$                                                   |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | The parameters in the I <sub>CCINT</sub> equation are:                                                                                               |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | MC <sub>TON</sub>                                                                                                                                    | Number of macrocells with the Turbo Bit <sup>™</sup> option turned<br>on, as reported in the Quartus II or MAX+PLUS II Report<br>File (ret) |                                                     |                  |                                                       |   |  |  |  |

|                      | $MC_{DEV}$                                                                                                                                           | =                                                                                                                                           | File (.rpt)<br>= Number of macrocells in the device |                  |                                                       |   |  |  |  |

|                      | MC <sub>USED</sub> = Total number of macrocells in the design, as reported in the RPT File                                                           |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | $f_{MAX}$ = Highest clock frequency to the device                                                                                                    |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | $tog_{LC}$ = Average percentage of logic cells toggling at each clock                                                                                |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | (typically 12.5%)                                                                                                                                    |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | A, B, C = Constants (shown in Table 26)                                                                                                              |                                                                                                                                             |                                                     |                  |                                                       |   |  |  |  |

|                      | Table 26.                                                                                                                                            | MA                                                                                                                                          | X 3000A I <sub>CC</sub> Eq                          | quation Constant | s                                                     |   |  |  |  |

|                      |                                                                                                                                                      | Devi                                                                                                                                        | ice                                                 | А                | В                                                     | С |  |  |  |

| Device          | A    | В    | C     |

|-----------------|------|------|-------|

| EM3032A         | 0.71 | 0.30 | 0.014 |

| EM3064A         | 0.71 | 0.30 | 0.014 |

| <b>EM</b> 3128A | 0.71 | 0.30 | 0.014 |

| EM3256A         | 0.71 | 0.30 | 0.014 |

| <b>EM</b> 3512A | 0.71 | 0.30 | 0.014 |

The I<sub>CCINT</sub> calculation provides an I<sub>CC</sub> estimate based on typical conditions using a pattern of a 16–bit, loadable, enabled, up/down counter in each LAB with no output load. Actual I<sub>CC</sub> should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

Figures 12 and 13 show the typical supply cu rrent versus frequency for MAX 3000A devices.