Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 64MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 32KB (16K x 16)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k90-i-ptrsl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                    | 9   |

|-------|--------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with PIC18FXXKXX Microcontrollers   | 35  |

| 3.0   | Oscillator Configurations                                          |     |

| 4.0   | Power-Managed Modes                                                | 53  |

| 5.0   | Reset                                                              | 69  |

| 6.0   | Memory Organization                                                | 85  |

| 7.0   | Flash Program Memory                                               | 111 |

| 8.0   | Data EEPROM Memory                                                 | 121 |

| 9.0   | 8 x 8 Hardware Multiplier                                          | 127 |

| 10.0  | Interrupts                                                         | 129 |

| 11.0  | I/O Ports                                                          | 153 |

| 12.0  | Timer0 Module                                                      | 183 |

| 13.0  | Timer1 Module                                                      | 187 |

| 14.0  | Timer2 Module                                                      | 199 |

| 15.0  | Timer3/5/7 Modules                                                 | 201 |

| 16.0  | Timer4/6/8/10/12 Modules                                           | 213 |

|       | Real-Time Clock and Calendar (RTCC)                                |     |

| 18.0  | Capture/Compare/PWM (CCP) Modules                                  | 237 |

|       | Enhanced Capture/Compare/PWM (ECCP) Module                         |     |

| 20.0  | Liquid Crystal Display (LCD) Driver Module                         | 273 |

| 21.0  | Master Synchronous Serial Port (MSSP) Module                       |     |

| 22.0  |                                                                    |     |

| 23.0  | 12-Bit Analog-to-Digital Converter (A/D) Module                    | 373 |

|       | Comparator Module                                                  |     |

| 25.0  | Comparator Voltage Reference Module                                | 397 |

| 26.0  | High/Low-Voltage Detect (HLVD)                                     | 401 |

| 27.0  | Charge Time Measurement Unit (CTMU)                                | 407 |

| 28.0  | Special Features of the CPU                                        | 425 |

| 29.0  | Instruction Set Summary                                            | 451 |

| 30.0  | Development Support                                                | 501 |

| 31.0  | Electrical Characteristics                                         | 505 |

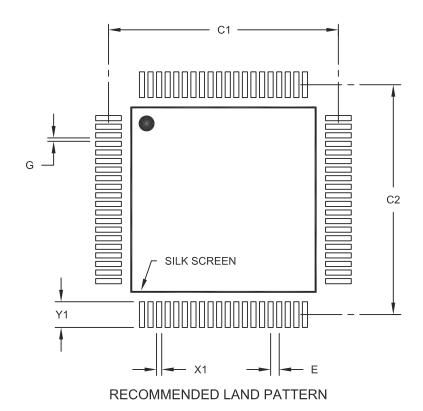

| 32.0  | Packaging Information                                              | 545 |

| Appe  | endix A: Revision History                                          | 553 |

| Appe  | endix B: Migration From PIC18F85J90 and PIC18F87J90 to PIC18F87K90 | 553 |

| Index | X                                                                  | 555 |

|       | Microchip Web Site                                                 |     |

|       | omer Change Notification Service                                   |     |

| Custo | omer Support                                                       | 567 |

| Read  | der Response                                                       | 568 |

| Prod  | uct Identification System                                          | 569 |

TABLE 1-3: PIC18F6XK90 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Nome                                                                            | Pin Number | Pin                         | Buffer                                        | Description                                                                                                                                    |

|-------------------------------------------------------------------------------------|------------|-----------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                            | QFN/TQFP   | Туре                        | Туре                                          | Description                                                                                                                                    |

|                                                                                     |            |                             |                                               | PORTA is a bidirectional I/O port.                                                                                                             |

| RA0/AN0/ULPWU<br>RA0<br>AN0<br>ULPWU                                                | 24         | I/O<br>I<br>I               | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 0.<br>Ultra Low-Power Wake-up (ULPW) input.                                                                       |

| RA1/AN1/SEG18<br>RA1<br>AN1<br>SEG18                                                | 23         | I/O<br>I<br>O               | TTL<br>Analog<br>Analog                       | Digital I/O. Analog Input 1. SEG18 output for LCD.                                                                                             |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF-                                                | 22         | I/O<br>I<br>I               | TTL<br>Analog<br>Analog                       | Digital I/O. Analog Input 2. A/D reference voltage (low) input.                                                                                |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                                                | 21         | I/O<br>I<br>I               | TTL<br>Analog<br>Analog                       | Digital I/O. Analog Input 3. A/D reference voltage (high) input.                                                                               |

| RA4/T0CKI/SEG14<br>RA4<br>T0CKI<br>SEG14                                            | 28         | I/O<br>I<br>O               | ST<br>ST<br>Analog                            | Digital I/O. Timer0 external clock input. SEG14 output for LCD.                                                                                |

| RA5/AN4/SEG15/T1CKI/<br>T3G/HLVDIN<br>RA5<br>AN4<br>SEG15<br>T1CKI<br>T3G<br>HLVDIN | 27         | I/O<br> <br>  O<br> <br>  I | TTL<br>Analog<br>Analog<br>ST<br>ST<br>Analog | Digital I/O. Analog Input 4. SEG15 output for LCD. Timer1 clock input. Timer3 external clock gate input. High/Low-Voltage Detect (HLVD) input. |

| RA6<br>RA7                                                                          |            |                             |                                               | See the OSC2/CLKO/RA6 pin. See the OSC1/CLKI/RA7 pin.                                                                                          |

**Legend:** TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open-Drain (no P diode to VDD)

$I^2C^{TM} = I^2C/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K90 and PIC18F85K90 devices.

# 3.0 OSCILLATOR CONFIGURATIONS

### 3.1 Oscillator Types

The PIC18F87K90 family of devices can be operated in the following oscillator modes:

| • EC                   | External Clock, RA6 available                                 |

|------------------------|---------------------------------------------------------------|

| • ECIO                 | External Clock, Clock Out RA6 (Fosc/4 on RA6)                 |

| • HS                   | High-Speed Crystal/Resonator                                  |

| <ul> <li>XT</li> </ul> | Crystal/Resonator                                             |

| • LP                   | Low-Power Crystal                                             |

| • RC                   | External Resistor/Capacitor, RA6 available                    |

| • RCIO                 | External Resistor/Capacitor, Clock<br>Out RA6 (Fosc/4 on RA6) |

| • INTIO2               | Internal Oscillator with I/O on RA6 and RA7                   |

| • INTIO1               | Internal Oscillator with Fosc/4 Output on RA6 and I/O on RA7  |

There is also an option for running the 4xPLL on any of the clock sources in the input frequency range of 4 to 16 MHz.

The PLL is enabled by setting the PLLCFG bit (CONFIG1H<4>) or the PLLEN bit (OSCTUNE<6>).

For the EC and HS mode, the PLLEN (software) or PLLCFG (CONFIG) bit can be used to enable the PLL.

For the INTIOx modes (HF-INTOSC):

- Only the PLLEN can enable the PLL (PLLCFG is ignored).

- When the oscillator is configured for the internal oscillator (OSC<3:0> = 100x), the PLL can be enabled only when the HF-INTOSC frequency is 8 or 16 MHz.

When the RA6 and RA7 pins are not used for an oscillator function or CLKOUT function, they are available as general purpose I/Os.

To optimize power consumption when using EC/HS/XT/LP/RC as the primary oscillator, the frequency input range can be configured to yield an optimized power bias:

- Low-Power Bias External frequency less than 160 kHz

- Medium Power Bias External frequency between 160 kHz and 16 MHz

- High-Power Bias External frequency greater than 16 MHz

All of these modes are selected by the user by programming the OSC<3:0> Configuration bits (CONFIG1H<3:0>). In addition, PIC18F87K90 family devices can switch between different clock sources, either under software control or under certain conditions, automatically. This allows for additional power savings by managing device clock speed in real time without resetting the application. The clock sources for the PIC18F87K90 family of devices are shown in Figure 3-1.

For the HS and EC mode, there are additional power modes of operation – depending on the frequency of operation.

HS1 is the Medium Power mode with a frequency range of 4 MHz to 16 MHz. HS2 is the High-Power mode where the oscillator frequency can go from 16 MHz to 25 MHz. HS1 and HS2 are achieved by setting the CONFIG1H<3:0> correctly. (For details, see Register 28-2 on page 428.)

EC mode has these modes of operation:

- EC1 For low power with a frequency range up to 160 kHz

- EC2 Medium power with a frequency range of 160 kHz to 16 MHz

- EC3 High power with a frequency range of 16 MHz to 64 MHz

EC1, EC2 and EC3 are achieved by setting the CONFIG1H<3:0> correctly. (For details, see Register 28-2 on page 428.)

Table 3-1 shows the HS and EC modes' frequency range and OSC<3:0> settings.

## REGISTER 4-4: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

| R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0 |

|--------|--------|--------|---------|---------|--------|--------|-------|

| CCP3MD | CCP2MD | CCP1MD | UART2MD | UART1MD | SSP2MD | SSP1MD | ADCMD |

| bit 7  |        |        |         |         |        |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 CCP3MD: PMD ECCP3 Enable/Disable bit

1 = Peripheral Module Disable (PMD) is enabled for ECCP3, disabling all of its clock sources

0 = PMD is disabled for ECCP3

bit 6 CCP2MD: PMD ECCP2 Enable/Disable bit

1 = PMD is enabled for ECCP2, disabling all of its clock sources

0 = PMD is disabled for ECCP2

bit 5 CCP1MD: PMD ECCP1 Enable/Disable bit

1 = PMD is enabled for ECCP1, disabling all of its clock sources

0 = PMD is disabled for ECCP1

bit 4 UART2MD: PMD UART2 Enable/Disable bit

1 = PMD is enabled for UART2, disabling all of its clock sources

0 = PMD is disabled for UART2

bit 3 UART1MD: PMD UART1 Enable/Disable bit

1 = PMD is enabled for UART1, disabling all of its clock sources

0 = PMD is disabled for UART1

bit 2 SSP2MD: PMD MSSP2 Enable/Disable bit

1 = PMD is enabled for MSSP2, disabling all of its clock sources

0 = PMD is disabled for MSSP2

bit 1 SSP1MD: PMD MSSP1 Enable/Disable bit

1 = PMD is enabled for MSSP1, disabling all of its clock sources

0 = PMD is disabled for MSSP1

bit 0 ADCMD: PMD Analog/Digital Converter PMD Enable/Disable bit

1 = PMD is enabled for Analog/Digital Converter, disabling all of its clock sources

0 = PMD is disabled for Analog/Digital Converter

TABLE 6-2: PIC18F87K90 FAMILY REGISTER FILE SUMMARY (CONTINUED)

| Address | File Name                | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3                | Bit 2                | Bit 1                | Bit 0          | Value on POR, BOR |

|---------|--------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------|-------------------|

| F50h    | CCPR2H                   | Capture/Com          | npare/PWM R          | egister 2 High       | Byte                 |                      |                      |                      |                | xxxx xxxx         |

| F51h    | ECCP2DEL                 | P2RSEN               | P2DC6                | P2DC5                | P2DC4                | P2DC3                | P2DC2                | P2DC1                | P2DC0          | 0000 0000         |

| F52h    | ECCP2AS                  | ECCP2ASE             | ECCP2AS2             | ECCP2AS1             | ECCP2AS0             | PSS2AC1              | PSS2AC0              | PSS2BD1              | PSS2BD0        | 0000 0000         |

| F53h    | PADCFG1                  | RDPU                 | REPU                 | RJPU <sup>(2)</sup>  | _                    | _                    | RTSECSEL1            | RTSECSEL0            | _              | 00000-            |

| F54h    | CM1CON                   | CON                  | COE                  | CPOL                 | EVPOL1               | EVPOL0               | CREF                 | CCH1                 | CCH0           | 0001 1111         |

| F55h    | CTMUICON                 | ITRIM5               | ITRIM4               | ITRIM3               | ITRIM2               | ITRIM1               | ITRIM0               | IRNG1                | IRNG1          | 0000 0000         |

| F56h    | CTMUCONL                 | EDG2POL              | EDG2SEL1             | EDG2SEL0             | EDG1POL              | EDG1SEL1             |                      | EDG2STAT             | EDG1STAT       | 0000 0000         |

| F57h    | CTMUCONH                 | CTMUEN               | _                    | CTMUSIDL             | TGEN                 | EDGEN                | EDGSEQEN             | IDISSEN              | CTTRIG         | 0-00 0000         |

| F58h    | ALRMVALL                 |                      | ı<br>Hiah Reaister   | Window base          |                      |                      |                      |                      |                | 0000 0000         |

| F59h    | ALRMVALH                 |                      |                      | Window base          |                      |                      |                      |                      |                | xxxx xxxx         |

| F5Ah    | ALRMRPT                  | ARPT7                | ARPT6                | ARPT5                | ARPT4                | ARPT3                | ARPT2                | ARPT1                | ARPT0          | 0000 0000         |

| F5Bh    | ALRMCFG                  | ALRMEN               | CHIME                | AMASK3               | AMASK2               | AMASK1               | AMASK0               | ALRMPTR1             | ALRMPTR0       | 0000 0000         |

| F5Ch    | RTCVALL                  |                      | l .                  | Window base          |                      |                      | 71171710110          | / LICINII II II      | / LI CONT TITO | 0000 0000         |

| F5Dh    | RTCVALH                  |                      |                      | Window base          |                      |                      |                      |                      |                | xxxx xxxx         |

| F5Eh    | RTCCAL                   | CAL7                 | CAL6                 | CAL5                 | CAL4                 | CAL3                 | CAL2                 | CAL1                 | CAL0           | XXXX XXXX         |

| F5Fh    | RTCCFG                   | RTCEN                |                      | RTCWREN              | RTCSYNC              | HALFSEC              | RTCOE                | RTCPTR1              | RTCPTR0        | 0-00 0000         |

| F60h    | PIE6                     | KICLIN               |                      | KICWKLN              | EEIE                 | TIALI SLC            | CMP3IE               | CMP2IE               | CMP1IE         | 0 -000            |

|         |                          | EEDDOM Do            | to Posistor          | _                    | EEIE                 | _                    | CIVIF3IE             | CIVIFZIE             | CIVIF IIE      | 0000 0000         |

| F61h    | EEDATA                   | EEPROM Da            |                      | ar Laur Durta        |                      |                      |                      |                      |                |                   |

| F62h    | EEADR                    |                      | Idress Registe       |                      |                      |                      |                      |                      |                | 0000 0000         |

| F63h    | EEADRH                   | EEPROM AO            | Idress Registe       | r High Byte          |                      | 000000               |                      | MEIOEO               | MEIOOFI        | 00                |

| F64h    | OSCCON2                  |                      | SOSCRUN              | - DVDTD              | TVOVD                | SOSCGO               | _                    | MFIOFS               | MFIOSEL        | -0 0-x0           |

| F65h    | BAUDCON1                 | ABDOVF               | RCIDL                | RXDTP                | TXCKP                | BRG16                | _                    | WUE                  | ABDEN          | 0000 0-x0         |

| F66h    | LCDDATA0                 | S07C0                | S06C0                | S05C0                | S04C0                | S03C0                | S02C0                | S01C0                | S00C0          | XXXX XXXX         |

| F67h    | LCDDATA1                 | S15C0                | S14C0                | S13C0                | S12C0                | S11C0                | S10C0                | S09C0                | S08C0          | XXXX XXXX         |

| F68h    | LCDDATA2                 | S23C0                | S22C0                | S21C0                | S20C0                | S19C0                | S18C0                | S17C0                | S16C0          | XXXX XXXX         |

| F69h    | LCDDATA3                 | S31C0                | S30C0                | S29C0                | S28C0                | S27C0                | S26C0                | S25C0                | S24C0          | XXXX XXXX         |

| F6Ah    | LCDDATA4                 | S39C0                | S38C0                | S37C0                | S36C0                | S35C0                | S34C0                | S33C0                | S32C0          | XXXX XXXX         |

| F6Bh    | LCDDATA5                 | S47C0                | S46C0                | S45C0                | S44C0                | S43C0                | S42C0                | S41C0                | S40C0          | XXXX XXXX         |

| F6Ch    | LCDDATA6                 | S07C1                | S06C1                | S05C1                | S04C1                | S03C1                | S02C1                | S01C1                | S00C1          | XXXX XXXX         |

| F6Dh    | LCDDATA7                 | S15C1                | S14C1                | S13C1                | S12C1                | S11C1                | S10C1                | S09C1                | S08C1          | XXXX XXXX         |

| F6Eh    | LCDDATA8                 | S23C1                | S22C1                | S21C1                | S20C1                | S19C1                | S18C1                | S17C1                | S16C1          | xxxxxxxx          |

| F6Fh    | LCDDATA9                 | S31C1                | S30C1                | S29C1                | S28C1                | S27C1                | S26C1                | S25C1                | S24C1          | xxxx xxxx         |

| F70h    | LCDDATA10 <sup>(2)</sup> | S39C1 <sup>(2)</sup> | S38C1 <sup>(2)</sup> | S37C1 <sup>(2)</sup> | S36C1 <sup>(2)</sup> | S35C1 <sup>(2)</sup> | S34C1 <sup>(2)</sup> | S33C1 <sup>(2)</sup> | S32C1          | xxxx xxxx         |

| F71h    | LCDDATA11 <sup>(2)</sup> | S47C1                | S46C1                | S45C1                | S44C1                | S43C1                | S42C1                | S41C1                | S40C1          | xxxx xxxx         |

| F72h    | LCDDATA12                | S07C2                | S06C2                | S05C2                | S04C2                | S03C2                | S02C2                | S01C2                | S00C2          | xxxx xxxx         |

| F73h    | LCDDATA13                | S15C2                | S14C2                | S13C2                | S12C2                | S11C2                | S10C2                | S09C2                | S08C2          | xxxx xxxx         |

| F74h    | LCDDATA14                | S23C2                | S22C2                | S21C2                | S20C2                | S19C2                | S18C2                | S17C2                | S16C2          | xxxx xxxx         |

| F75h    | LCDDATA15                | S31C2                | S30C2                | S29C2                | S28C2                | S27C2                | S26C2                | S25C2                | S24C2          | xxxx xxxx         |

| F76h    | LCDDATA16 <sup>(2)</sup> | S39C2 <sup>(2)</sup> | S38C2 <sup>(2)</sup> | S37C2 <sup>(2)</sup> | S36C2 <sup>(2)</sup> | S35C2 <sup>(2)</sup> | S34C2 <sup>(2)</sup> | S33C2 <sup>(2)</sup> | S32C2          | xxxx xxxx         |

| F77h    | LCDDATA17 <sup>(2)</sup> | S47C2                | S46C2                | S45C2                | S44C2                | S43C2                | S42C2                | S41C2                | S40C2          | xxxx xxxx         |

| F78h    | LCDDATA18                | S07C3                | S06C3                | S05C3                | S04C3                | S03C3                | S02C3                | S01C3                | S00C3          | xxxx xxxx         |

| F79h    | LCDDATA19                | S15C3                | S14C3                | S13C3                | S12C3                | S11C3                | S10C3                | S09C3                | S08C3          | xxxx xxxx         |

| F7Ah    | LCDDATA20                | S23C3                | S22C3                | S21C3                | S20C3                | S19C3                | S18C3                | S17C3                | S16C3          | xxxx xxxx         |

| F7Bh    | LCDDATA21                | S31C3                | S30C3                | S29C3                | S28C3                | S27C3                | S26C3                | S25C3                | S24C3          | xxxx xxxx         |

| F7Ch    | LCDDATA22                | S39C3 <sup>(2)</sup> | S38C3 <sup>(2)</sup> | S37C3 <sup>(2)</sup> | S36C3 <sup>(2)</sup> | S35C3 <sup>(2)</sup> | S34C3 <sup>(2)</sup> | S33C3 <sup>(2)</sup> | S32C3          | xxxx xxxx         |

| F7Dh    | LCDDATA23 <sup>(2)</sup> | S47C3                | S46C3                | S45C3                | S44C3                | S43C3                | S42C3                | S41C3                | S40C3          | xxxx xxxx         |

| F7Eh    | EECON2                   |                      | l .                  | 2 (not a phys        |                      |                      |                      |                      |                |                   |

| F7Fh    | EECON1                   | EEPGD                | CFGS                 | _                    | FREE                 | WRERR                | WREN                 | WR                   | RD             | xx-0 x000         |

| F80h    | PORTA                    | RA7                  | RA6                  | RA5                  | RA4                  | RA3                  | RA2                  | RA1                  | RA0            | xxxx xxxx         |

Note 1: This bit is available when Master Clear is disabled (MCLRE = 0). When MCLRE is set, the bit is unimplemented.

<sup>2:</sup> Unimplemented in 64-pin devices (PIC18F6XK90).

<sup>3:</sup> Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

TABLE 6-2: PIC18F87K90 FAMILY REGISTER FILE SUMMARY (CONTINUED)

| Address | File Name            | Bit 7      | Bit 6         | Bit 5              | Bit 4   | Bit 3            | Bit 2   | Bit 1  | Bit 0   | Value on POR, BOR |

|---------|----------------------|------------|---------------|--------------------|---------|------------------|---------|--------|---------|-------------------|

| F81h    | PORTB                | RB7        | RB6           | RB5                | RB4     | RB3              | RB2     | RB1    | RB0     | xxxx xxxx         |

| F82h    | PORTC                | RC7        | RC6           | RC5                | RC4     | RC3              | RC2     | RC1    | RC0     | xxxx xxxx         |

| F83h    | PORTD                | RD7        | RD6           | RD5                | RD4     | RD3              | RD2     | RD1    | RD0     | xxxx xxxx         |

| F84h    | PORTE                | RE7        | RE6           | RE5                | RE4     | RE3              | RE2     | RE1    | RE0     | xxxx xxxx         |

| F85h    | PORTF                | RF7        | RF6           | RF5                | RF4     | RF3              | RF2     | RF1    | _       | xxxx xxx-         |

| F86h    | PORTG                | _          | _             | RG5 <sup>(1)</sup> | RG4     | RG3              | RG2     | RG1    | RG0     | xx xxxx           |

| F87h    | PORTH <sup>(2)</sup> | RH7        | RH6           | RH5                | RH4     | RH3              | RH2     | RH1    | RH0     | xxxx xxxx         |

| F88h    | PORTJ <sup>(2)</sup> | RJ7        | RJ6           | RJ5                | RJ4     | RJ3              | RJ2     | RJ1    | RJ0     | xxxx xxxx         |

| F89h    | LATA                 | LATA7      | LATA6         | LATA5              | LATA4   | LATA3            | LATA2   | LATA1  | LATA0   | xxxx xxxx         |

| F8Ah    | LATB                 | LATB7      | LATB6         | LATB5              | LATB4   | LATB3            | LATB2   | LATB1  | LATB0   | xxxx xxxx         |

| F8Bh    | LATC                 | LATC7      | LATC6         | LATC5              | LATC4   | LATC3            | LATC2   | LATC1  | LATC0   | xxxx xxxx         |

| F8Ch    | LATD                 | LATD7      | LATD6         | LATD5              | LATD4   | LATD3            | LATD2   | LATD1  | LATD0   | xxxx xxxx         |

| F8Dh    | LATE                 | LATE7      | LATE6         | LATE5              | LATE4   | LATE3            | LATE2   | LATE1  | LATE0   | xxxx xxxx         |

| F8Eh    | LATF                 | LATF7      | LATF6         | LATF5              | LATF4   | LATF3            | LATF2   | LATF1  | _       | xxxx xxx-         |

| F8Fh    | LATG                 | _          | _             | _                  | LATG4   | LATG3            | LATG2   | LATG1  | LATG0   | x xxxx            |

| F90h    | LATH <sup>(2)</sup>  | LATH7      | LATH6         | LATH5              | LATH4   | LATH3            | LATH2   | LATH1  | LATH0   | xxxx xxxx         |

| F91h    | LATJ <sup>(2)</sup>  | LATJ7      | LATJ6         | LATJ5              | LATJ4   | LATJ3            | LATJ2   | LATJ1  | LATJ0   | xxxx xxxx         |

| F92h    | TRISA                | TRISA7     | TRISA6        | TRISA5             | TRISA4  | TRISA3           | TRISA2  | TRISA1 | TRISA0  | 1111 1111         |

| F93h    | TRISB                | TRISB7     | TRISB6        | TRISB5             | TRISB4  | TRISB3           | TRISB2  | TRISB1 | TRISB0  | 1111 1111         |

| F94h    | TRISC                | TRISC7     | TRISC6        | TRISC5             | TRISC4  | TRISC3           | TRISC2  | TRISC1 | TRISC0  | 1111 1111         |

| F95h    | TRISD                | TRISD7     | TRISD6        | TRISD5             | TRISD4  | TRISD3           | TRISD2  | TRISD1 | TRISD0  | 1111 1111         |

| F96h    | TRISE                | TRISE7     | TRISE6        | TRISE5             | TRISE4  | TRISE3           | TRISE2  | TRISE1 | TRISE0  | 1111 1111         |

| F97h    | TRISF                | TRISF7     | TRISF6        | TRISF5             | TRISF4  | TRISF3           | TRISF2  | TRISF1 | _       | 1111 111-         |

| F98h    | TRISG                | _          | _             | _                  | TRISG4  | TRISG3           | TRISG2  | TRISG1 | TRISG0  | 1 1111            |

| F99h    | TRISH <sup>(2)</sup> | TRISH7     | TRISH6        | TRISH5             | TRISH4  | TRISH3           | TRISH2  | TRISH1 | TRISH0  | 1111 1111         |

| F9Ah    | TRISJ <sup>(2)</sup> | TRISJ7     | TRISJ6        | TRISJ5             | TRISJ4  | TRISJ3           | TRISJ2  | TRISJ1 | TRISJ0  | 1111 1111         |

| F9Bh    | OSCTUNE              | INTSRC     | PLLEN         | TUN5               | TUN4    | TUN3             | TUN2    | TUN1   | TUN0    | 0000 0000         |

| F9Ch    | PSTR1CON             | CMPL1      | CMPL0         | _                  | STRSYNC | STRD             | STRC    | STRB   | STRA    | 00-0 0001         |

| F9Dh    | PIE1                 | _          | ADIE          | RC1IE              | TX1IE   | SSP1IE           | TMR1GIE | TMR2IE | TMR1IE  | -000 0000         |

| F9Eh    | PIR1                 | _          | ADIF          | RC1IF              | TX1IF   | SSP1IF           | TMR1GIF | TMR2IF | TMR1IF  | -000 0000         |

| F9Fh    | IPR1                 | _          | ADIP          | RC1IP              | TX1IP   | SSP1IP           | TMR1GIP | TMR2IP | TMR1IP  | -111 1111         |

| FA0h    | PIE2                 | OSCFIE     | _             | SSP2IE             | BCL2IE  | BCL1IE           | HLVDIE  | TMR3IE | TMR3GIE | 0-10 0000         |

| FA1h    | PIR2                 | OSCFIF     | _             | SSP2IF             | BCL2IF  | BCL1IF           | HLVDIF  | TMR3IF | TMR3GIF | 0-10 0000         |

| FA2h    | IPR2                 | OSCFIP     | _             | SSP2IP             | BCL2IP  | BCL1IP           | HLVDIP  | TMR3IP | TMR3GIP | 1-00 1110         |

|         | PIE3                 | TMR5GIE    | LCDIE         | RC2IE              | TX2IE   | CTMUIE           | CCP2IE  | CCP1IE | RTCCIE  | 0000 0000         |

| FA4h    | PIR3                 | TMR5GIF    | LCDIF         | RC2IF              | TX2IF   | CTMUIF           | CCP2IF  | CCP1IF | RTCCIF  | 0000 0000         |

| FA5h    | IPR3                 | TMR5GIP    | LCDIP         | RC2IP              | TX2IP   | CTMUIP           | CCP2IP  | CCP1IP | RTCCIP  | 1111 1111         |

| FA6h    | PIR6                 | _          | _             | _                  | EEIF    | _                | CMP3IF  | CMP2IF | CMP1IF  | 0 -000            |

| FA7h    | _                    | _          | _             | _                  | _       | _                | _       | _      | _       |                   |

| FA8h    | HLVDCON              | VDIRMAG    | BGVST         | IRVST              | HLVDEN  | HLVDL3           | HLVDL2  | HLVDL1 | HLVDL0  | 0000 0000         |

| FA9h    | IPR6                 | _          | _             | _                  | EEIP    | _                | CMP3IP  | CMP2IP | CMP1IP  | 1 -111            |

| FAAh    | T1GCON               | TMR1GE     | T1GPOL        | T1GTM              | T1GSPM  | T1GGO/<br>T1DONE | T1GVAL  | T1GSS1 | T1GSS0  | 0000 0x00         |

| FABh    | RCSTA1               | SPEN       | RX9           | SREN               | CREN    | ADDEN            | FERR    | OERR   | RX9D    | 0000 000x         |

| FACh    | TXSTA1               | CSRC       | TX9           | TXEN               | SYNC    | SENDB            | BRGH    | TRMT   | TX9D    | 0000 0010         |

| FADh    | TXREG1               |            | nsmit Registe |                    | 1       | 1                | 1       | 1      | 1       | xxxx xxxx         |

| FAEh    | RCREG1               | USART1 Red | eive Register |                    |         |                  |         |        |         | 0000 0000         |

| FAFh    | SPBRG1               |            | ıd Rate Gene  |                    |         |                  |         |        |         | 0000 0000         |

Note 1: This bit is available when Master Clear is disabled (MCLRE = 0). When MCLRE is set, the bit is unimplemented.

<sup>2:</sup> Unimplemented in 64-pin devices (PIC18F6XK90).

<sup>3:</sup> Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

TABLE 10-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name    | Bit 7                  | Bit 6                  | Bit 5                  | Bit 4   | Bit 3                 | Bit 2   | Bit 1  | Bit 0   | Reset<br>Values<br>on Page: |

|---------|------------------------|------------------------|------------------------|---------|-----------------------|---------|--------|---------|-----------------------------|

| INTCON  | GIE/GIEH               | PEIE/GIEL              | TMR0IE                 | INT0IE  | RBIE                  | TMR0IF  | INT0IF | RBIF    | 75                          |

| INTCON2 | RBPU                   | INTEDG0                | INTEDG1                | INTEDG2 | INTEDG3               | TMR0IP  | INT3IP | RBIP    | 75                          |

| INTCON3 | INT2IP                 | INT1IP                 | INT3IE                 | INT2IE  | INT1IE                | INT3IF  | INT2IF | INT1IF  | 75                          |

| PIR1    | _                      | ADIF                   | RC1IF                  | TX1IF   | SSP1IF                | TMR1GIF | TMR2IF | TMR1IF  | 77                          |

| PIR2    | OSCFIF                 | _                      | SSP2IF                 | BCL2IF  | BCL1IF                | HLVDIF  | TMR3IF | TMR3GIF | 77                          |

| PIR3    | TMR5GIF                | LCDIF                  | RC2IF                  | TX2IF   | CTMUIF                | CCP2IF  | CCP1IF | RTCCIF  | 77                          |

| PIR4    | CCP10IF <sup>(1)</sup> | CCP9IF <sup>(1)</sup>  | CCP8IF                 | CCP7IF  | CCP6IF                | CCP5IF  | CCP4IF | CCP3IF  | 77                          |

| PIR5    | TMR7GIF <sup>(1)</sup> | TMR12IF <sup>(1)</sup> | TMR10IF <sup>(1)</sup> | TMR8IF  | TMR7IF <sup>(1)</sup> | TMR6IF  | TMR5IF | TMR4IF  | 77                          |

| PIR6    | _                      | _                      |                        | EEIF    | _                     | CMP3IF  | CMP2IF | CMP1IF  | 77                          |

| PIE1    | _                      | ADIE                   | RC1IE                  | TX1IE   | SSP1IE                | TMR1GIE | TMR2IE | TMR1IE  | 77                          |

| PIE2    | OSCFIE                 | _                      | SSP2IE                 | BCL2IE  | BCL1IE                | HLVDIE  | TMR3IE | TMR3GIE | 77                          |

| PIE3    | TMR5GIE                | LCDIE                  | RC2IE                  | TX2IE   | CTMUIE                | CCP2IE  | CCP1IE | RTCCIE  | 77                          |

| PIE4    | CCP10IE <sup>(1)</sup> | CCP9IE <sup>(1)</sup>  | CCP8IE                 | CCP7IE  | CCP6IE                | CCP5IE  | CCP4IE | CCP3IE  | 77                          |

| PIE5    | TMR7GIE <sup>(1)</sup> | TMR12IE <sup>(1)</sup> | TMR10IE <sup>(1)</sup> | TMR8IE  | TMR7IE <sup>(1)</sup> | TMR6IE  | TMR5IE | TMR4IE  | 77                          |

| PIE6    | _                      |                        | 1                      | EEIE    |                       | CMP3IE  | CMP2IE | CMP1IE  | 80                          |

| IPR1    | _                      | ADIP                   | RC1IP                  | TX1IP   | SSP1IP                | TMR1GIP | TMR2IP | TMR1IP  | 77                          |

| IPR2    | OSCFIP                 | _                      | SSP2IP                 | BCL2IP  | BCL1IP                | HLVDIP  | TMR3IP | TMR3GIP | 77                          |

| IPR3    | TMR5GIP                | LCDIP                  | RC2IP                  | TX2IP   | CTMUIP                | CCP2IP  | CCP1IP | RTCCIP  | 77                          |

| IPR4    | CCP10IP <sup>(1)</sup> | CCP9IP <sup>(1)</sup>  | CCP8IP                 | CCP7IP  | CCP6IP                | CCP5IP  | CCP4IP | CCP3IP  | 77                          |

| IPR5    | TMR7GIP <sup>(1)</sup> | TMR12IP <sup>(1)</sup> | TMR10IP <sup>(1)</sup> | TMR8IP  | TMR7IP <sup>(1)</sup> | TMR6IP  | TMR5IP | TMR4IP  | 76                          |

| IPR6    | _                      | _                      | _                      | EEIP    |                       | CMP3IP  | CMP2IP | CMP1IP  | 77                          |

| RCON    | IPEN                   | SBOREN                 | CM                     | RI      | TO                    | PD      | POR    | BOR     | 76                          |

**Legend:** Shaded cells are not used by the interrupts.

Note 1: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

### REGISTER 11-2: ODCON2: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 2

| R/W-0                  | R/W-0                 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|------------------------|-----------------------|--------|--------|--------|--------|--------|--------|

| CCP10OD <sup>(1)</sup> | CCP9OD <sup>(1)</sup> | CCP8OD | CCP7OD | CCP6OD | CCP5OD | CCP4OD | CCP3OD |

| bit 7                  |                       |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | CCP10OD: CCP10 Open-Drain Output Enable bit <sup>(1)</sup>                                           |

|-------|------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 6 | CCP9OD: CCP9 Open-Drain Output Enable bit(1)                                                         |

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 5 | CCP8OD: CCP8 Open-Drain Output Enable bit                                                            |

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 4 | CCP7OD: CCP7 Open-Drain Output Enable bit                                                            |

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 3 | CCP6OD: CCP6 Open-Drain Output Enable bit                                                            |

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 2 | CCP5OD: CCP5 Open-Drain Output Enable bit                                                            |

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 1 | CCP4OD: CCP4 Open-Drain Output Enable bit                                                            |

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 0 | CCP3OD: ECCP3 Open-Drain Output Enable bit                                                           |

|       | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

Note 1: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

# 11.5 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISD and LATD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

**Note:** These pins are configured as digital inputs on any device Reset.

Each of the PORTD pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by clearing bit, RDPU (PADCFG1<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

All of the PORTD pins are multiplexed with LCD segment drives that are controlled by bits in the LCDSE0 register. RD0 is multiplexed with the CTMU pulse generator output.

I/O port functionality is only available when the LCD segments are disabled.

The PORTD also has the I<sup>2</sup>C and SPI functionality on RD4, RD5 and RD6. The pins for SPI are also configurable for open-drain output. Open-drain configuration is selected by setting the SSPxOD control bits in the ODCON1 register.

RD0 has a CTMU functionality. RD1 has the functionality for a Timer5 clock input and also Timer7 has functionality for an external clock gate input.

### **EXAMPLE 11-4: INITIALIZING PORTD**

| CLRF  | PORTD | ; Initialize PORTD by ; clearing output |

|-------|-------|-----------------------------------------|

|       |       | ; data latches                          |

|       |       | / data factites                         |

| CLRF  | LATD  | ; Alternate method                      |

|       |       | ; to clear output                       |

|       |       | ; data latches                          |

| MOVLW | 0CFh  | ; Value used to                         |

|       |       | ; initialize data                       |

|       |       | ; direction                             |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                 |

|       |       | ; RD<5:4> as outputs                    |

|       |       | ; RD<7:6> as inputs                     |

|       |       | _                                       |

**TABLE 18-5:** REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1/3/5/7 (CONTINUED)

| Name                    | Bit 7   | Bit 6   | Bit 5  | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|-------------------------|---------|---------|--------|----------|---------|---------|---------|---------|-----------------------------|

| CCP6CON                 | _       | _       | DC6B1  | DC6B0    | CCP6M3  | CCP6M2  | CCP6M1  | CCP6M0  | 82                          |

| CCP7CON                 | _       | _       | DC7B1  | DC7B0    | CCP7M3  | CCP7M2  | CCP7M1  | CCP7M0  | 82                          |

| CCP8CON                 | _       | _       | DC8B1  | DC8B0    | CCP8M3  | CCP8M2  | CCP8M1  | CCP8M0  | 80                          |

| CCP9CON <sup>(1)</sup>  | _       | _       | DC9B1  | DC9B0    | ССР9М3  | CCP9M2  | CCP9M1  | ССР9М0  | 80                          |

| CCP10CON <sup>(1)</sup> | _       | _       | DC10B1 | DC10B0   | CCP10M3 | CCP10M2 | CCP10M1 | CCP10M0 | 81                          |

| CCPTMRS1                | C7TSEL1 | C7TSEL0 | _      | C6TSEL0  | _       | C5TSEL0 | C4TSEL1 | C4TSEL0 | 81                          |

| CCPTMRS2                |         | _       | _      | C10TSEL0 | _       | C9TSEL0 | C8TSEL1 | C8TSEL0 | 81                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare or Timer1/3/5/7.

Note 1: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

2: Unimplemented in 64-pin devices.

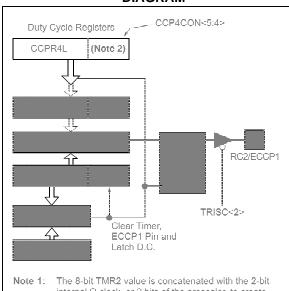

#### 18.4 **PWM Mode**

In Pulse-Width Modulation (PWM) mode, the CCP4 pin produces up to a 10-bit resolution PWM output. Since the CCP4 pin is multiplexed with a PORTC or PORTE data latch, the appropriate TRIS bit must be cleared to make the CCP4 pin an output.

Clearing the CCP4CON register will force Note: the RC1 or RE7 output latch (depending on device configuration) to the default low level. This is not the PORTC or PORTE I/O data latch.

Figure 18-3 shows a simplified block diagram of the ECCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 18.4.3 "Setup for PWM Operation".

**FIGURE 18-3:** SIMPLIFIED PWM BLOCK **DIAGRAM**

- internal O clock, or 2 bits of the prescaler, to create the 10-bit time base.

- 2: CCP4 and its appropriate timers are used as an example. For details on all of the CCP modules and their timer assignments, see Table 18-2 and Table 18-3.

#### 21.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Status Register (SSPxSTAT)

- · Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPxSR and SSPxBUF together create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

transmission, the SSPxBUF double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

The SSPxBUF register cannot be used with read-modify-write instructions, such as BCF, COMF, etc.

> To avoid lost data in Master mode, a read of the SSPxBUF must be performed to clear the Buffer Full (BF) detect bit (SSPxSTAT<0>) between each transmission.

### REGISTER 21-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

| R/W-0 | R/W-0              | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|--------------------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE <sup>(1)</sup> | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |                    |     |     |     |     |     | bit 0 |

| R = Readable bit |

|------------------|

|------------------|

Legend:

W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 7 SMP: Sample bit

### SPI Master mode:

1 = Input data sampled at the end of data output time

0 = Input data sampled at the middle of data output time

### SPI Slave mode:

SMP must be cleared when SPI is used in Slave mode.

#### CKE: SPI Clock Select bit(1) bit 6

1 = Transmit occurs on transition from active to Idle clock state

0 = Transmit occurs on transition from Idle to active clock state

#### bit 5 D/A: Data/Address bit

Used in  $I^2C^{TM}$  mode only.

## bit 4

Used in I<sup>2</sup>C mode only. This bit is cleared when the MSSPx module is disabled; SSPEN is cleared.

#### bit 3 S: Start bit

Used in I<sup>2</sup>C mode only.

#### R/W: Read/Write Information bit bit 2

Used in I<sup>2</sup>C mode only.

#### **UA:** Update Address bit bit 1

Used in I<sup>2</sup>C mode only.

#### bit 0 BF: Buffer Full Status bit (Receive mode only)

1 = Receive complete. SSPxBUF is full

0 = Receive not complete, SSPxBUF is empty

**Note 1:** Polarity of the clock state is set by the CKP bit (SSPxCON1<4>).

## 21.3.9 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full-power mode; in the case of the Sleep mode, all clocks are halted.

In Idle modes, a clock is provided to the peripherals. That clock can be from the primary clock source, the secondary clock (SOSC oscillator) or the INTOSC source. See **Section 3.3 "Clock Sources and Oscillator Switching"** for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set, and if enabled, will wake the device.

### 21.3.10 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 21.3.11 BUS MODE COMPATIBILITY

Table 21-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKF control bits

TABLE 21-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also an SMP bit which controls when the data is sampled.

## 21.3.12 SPI CLOCK SPEED AND MODULE INTERACTIONS

Because MSSP1 and MSSP2 are independent modules, they can operate simultaneously at different data rates. Setting the SSPM<3:0> bits of the SSPxCON1 register determines the rate for the corresponding module.

An exception is when both modules use Timer2 as a time base in Master mode. In this instance, any changes to the Timer2 module's operation will affect both MSSP modules equally. If different bit rates are required for each module, the user should select one of the other three time base options for one of the modules.

TABLE 21-2: REGISTERS ASSOCIATED WITH SPI OPERATION

| Name     | Bit 7     | Bit 6           | Bit 5        | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0   | Reset<br>Values<br>on Page: |

|----------|-----------|-----------------|--------------|--------|--------|---------|--------|---------|-----------------------------|

| INTCON   | GIE/GIEH  | PEIE/GIEL       | TMR0IE       | INT0IE | RBIE   | TMR0IF  | INT0IF | RBIF    | 75                          |

| PIR1     | _         | ADIF            | RC1IF        | TX1IF  | SSP1IF | TMR1GIF | TMR2IF | TMR1IF  | 77                          |

| PIE1     | _         | ADIE            | RC1IE        | TX1IE  | SSP1IE | TMR1GIE | TMR2IE | TMR1IE  | 77                          |

| IPR1     | _         | ADIP            | RC1IP        | TX1IP  | SSP1IP | TMR1GIP | TMR2IP | TMR1IP  | 77                          |

| PIR2     | OSCFIF    | _               | SSP2IF       | BCL2IF | BCL1IF | HLVDIF  | TMR3IF | TMR3GIF | 77                          |

| PIE2     | OSCFIE    | _               | SSP2IE       | BCL2IE | BCL1IE | HLVDIE  | TMR3IE | TMR3GIE | 77                          |

| IPR2     | OSCFIP    | _               | SSP2IP       | BCL2IP | BCL1IP | HLVDIP  | TMR3IP | TMR3GIP | 77                          |

| TRISC    | TRISC7    | TRISC6          | TRISC5       | TRISC4 | TRISC3 | TRISC2  | TRISC1 | TRISC0  | 78                          |

| TRISD    | TRISD7    | TRISD6          | TRISD5       | TRISD4 | TRISD3 | TRISD2  | TRISD1 | TRISD0  | 78                          |

| TRISF    | TRISF7    | TRISF6          | TRISF5       | TRISF4 | TRISF3 | TRISF2  | TRISF1 | _       | 78                          |

| SSP1BUF  | MSSP1 Rec | eive Buffer/Tra | ansmit Regis | ster   |        |         |        |         | 82                          |

| SSP1CON1 | WCOL      | SSPOV           | SSPEN        | CKP    | SSPM3  | SSPM2   | SSPM1  | SSPM0   | 76                          |

| SSP1CON2 | GCEN      | ACKSTAT         | ACKDT        | ACKEN  | RCEN   | PEN     | RSEN   | SEN     | 76                          |

| SSP1STAT | SMP       | CKE             | D/A          | Р      | S      | R/W     | UA     | BF      | 76                          |

| SSP2CON1 | WCOL      | SSPOV           | SSPEN        | CKP    | SSPM3  | SSPM2   | SSPM1  | SSPM0   | 82                          |

| SSP2CON2 | GCEN      | ACKSTAT         | ACKDT        | ACKEN  | RCEN   | PEN     | RSEN   | SEN     | 83                          |

| SSP2STAT | SMP       | CKE             | D/Ā          | Р      | S      | R/W     | UA     | BF      | 82                          |

| SSP2BUF  | MSSP2 Rec | eive Buffer/Tra | ansmit Regis | ster   |        |         |        |         | 82                          |

| ODCON3   | U2OD      | U1OD            | _            | _      | _      | _       | _      | CTMUDS  | 81                          |

**Legend:** Shaded cells are not used by the MSSP module in SPI mode.

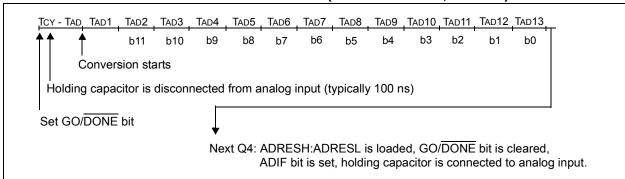

### 23.7 A/D Conversions

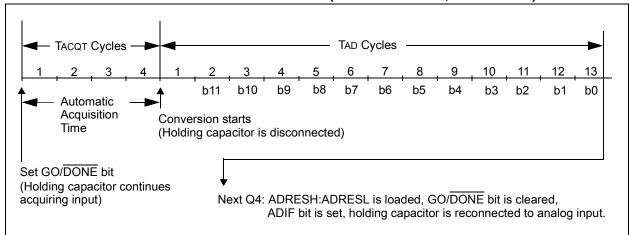

Figure 23-6 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 23-7 shows the operation of the A/D Converter after the GO/DONE bit has been set, the ACQT<2:0> bits set to '010' and a 4 TAD acquisition time selected.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the

ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD Wait is required before the next acquisition can be started. After this Wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

### FIGURE 23-6: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

### FIGURE 23-7: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

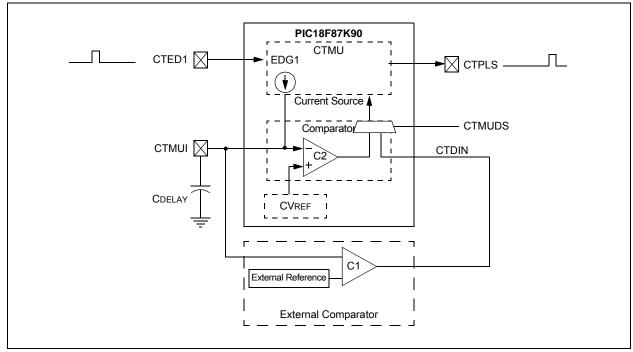

## 27.7 Creating a Delay with the CTMU Module

A unique feature on board the CTMU module is its ability to generate system clock independent output pulses, based on either an internal voltage or an external capacitor value. When using an external voltage, this is accomplished using the CTDIN input pin as a trigger for the pulse delay. When using an internal capacitor value, this is accomplished using the internal comparator voltage reference module and Comparator 2 input pin. The pulse is output onto the CTPLS pin. To enable this mode, set the TGEN bit.

See Figure 27-4 for an example circuit. When CTMUDS (ODCON3<0>) is cleared, the pulse delay is determined by the output of Comparator 2, and when it is set, the pulse delay is determined by the input of CTDIN. CDELAY is chosen by the user to determine the output pulse width on CTPLS. The pulse width is calculated by T = (CDELAY/I) \* V, where I is known from the current source measurement step (Section 27.4.1 "Current Source Calibration") and V is the internal reference voltage (CVREF).

An example use of the external capacitor feature is interfacing with variable capacitive-based sensors, such as a humidity sensor. As the humidity varies, the pulse-width output on CTPLS will vary. An example use of the CTDIN feature is interfacing with a digital sensor. The CTPLS output pin can be connected to an input capture pin and the varying pulse width measured to determine the humidity in the application.

### To use this feature:

- 1. If CTMUDS is cleared, initialize Comparator 2.

- If CTMUDS is cleared, initialize the comparator voltage reference.

- 3. Initialize the CTMU and enable time delay generation by setting the TGEN bit.

- 4. Set EDG1STAT.

When CTMUDS is cleared, as soon as CDELAY charges to the value of the voltage reference trip point, an output pulse is generated on CTPLS. When CTMUDS is set, as soon as CTDIN is set, an output pulse is generated on CTPLS.

FIGURE 27-4: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

**NEGF** Negate f NEGF f {,a} Syntax: Operands:  $0 \le f \le 255$  $a \in [0,1]$ Operation:  $(\overline{f}) + 1 \rightarrow f$ N, OV, C, DC, Z Status Affected: Encoding: 0110 110a ffff ffff Description: Location 'f' is negated using two's complement. The result is placed in the data memory location 'f'.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 29.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed

Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: NEGF REG, 1

Before Instruction

REG = 0011 1010 [3Ah]

After Instruction

REG = 1100 0110 [C6h]

| NOP   |                | No Operation |               |      |    |         |  |  |  |

|-------|----------------|--------------|---------------|------|----|---------|--|--|--|

| Synta | ax:            | NOP          |               |      |    |         |  |  |  |

| Oper  | ands:          | None         | None          |      |    |         |  |  |  |

| Oper  | ation:         | No operati   | on            |      |    |         |  |  |  |

| Statu | s Affected:    | None         |               |      |    |         |  |  |  |

| Enco  | oding:         | 0000         | 0000          | 000  | 0  | 0000    |  |  |  |

|       |                | 1111         | xxxx          | XXX  | ΧX | xxxx    |  |  |  |

| Desc  | ription:       | No operati   | No operation. |      |    |         |  |  |  |

| Word  | ds:            | 1            | 1             |      |    |         |  |  |  |

| Cycle | es:            | 1            | 1             |      |    |         |  |  |  |

| QC    | ycle Activity: |              |               |      |    |         |  |  |  |

|       | Q1             | Q2           | Q             | 3    |    | Q4      |  |  |  |

|       | Decode         | No           | No            | No   |    | No      |  |  |  |

|       |                | operation    | opera         | tion | op | eration |  |  |  |

Example:

None.

# 31.2 DC Characteristics: Power-Down and Supply Current PIC18F87K90 Family (Industrial/Extended) (Continued)

| PIC18F87K90 Family |                                       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |      |       |            |                                       |                                        |  |  |

|--------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|---------------------------------------|----------------------------------------|--|--|

| Param<br>No.       | Device                                | Тур                                                                                                                                                                                                                                   | Max  | Units | Conditions |                                       |                                        |  |  |

|                    | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                                                                                                                       |      |       |            |                                       |                                        |  |  |

|                    | All devices                           | 5.3                                                                                                                                                                                                                                   | 10   | μА    | -40°C      |                                       |                                        |  |  |

|                    |                                       | 5.5                                                                                                                                                                                                                                   | 10   | μА    | +25°C      | V <sub>DD</sub> = 1.8V <sup>(4)</sup> |                                        |  |  |

|                    |                                       | 5.5                                                                                                                                                                                                                                   | 10   | μА    | +85°C      | Regulator Disabled                    |                                        |  |  |

|                    |                                       | 12                                                                                                                                                                                                                                    | 24   | μА    | +125°C     |                                       |                                        |  |  |

|                    | All devices                           | 10                                                                                                                                                                                                                                    | 15   | μΑ    | -40°C      |                                       | F 04111                                |  |  |

|                    |                                       | 10                                                                                                                                                                                                                                    | 16   | μΑ    | +25°C      | 1  VDD = 3.3  V/(3)                   | Fosc = 31 kHz<br>( <b>RC_RUN</b> mode, |  |  |

|                    |                                       | 11                                                                                                                                                                                                                                    | 17   | μΑ    | +85°C      | Regulator Disabled                    | LF-INTOSC)                             |  |  |

|                    |                                       | 15                                                                                                                                                                                                                                    | 35   | μА    | +125°C     |                                       | 2                                      |  |  |

|                    | All devices                           | 70                                                                                                                                                                                                                                    | 180  | μА    | -40°C      |                                       |                                        |  |  |

|                    |                                       | 80                                                                                                                                                                                                                                    | 185  | μА    | +25°C      | $V_{DD} = 5V^{(5)}$                   |                                        |  |  |

|                    |                                       | 90                                                                                                                                                                                                                                    | 190  | μА    | +85°C      | Regulator Enabled                     |                                        |  |  |

|                    |                                       | 200                                                                                                                                                                                                                                   | 500  | μА    | +125°C     |                                       |                                        |  |  |

|                    | All devices                           | 410                                                                                                                                                                                                                                   | 850  | μА    | -40°C      |                                       |                                        |  |  |

|                    |                                       | 410                                                                                                                                                                                                                                   | 800  | μА    | +25°C      | V <sub>DD</sub> = 1.8V <sup>(4)</sup> |                                        |  |  |

|                    |                                       | 410                                                                                                                                                                                                                                   | 830  | μА    | +85°C      | Regulator Disabled                    |                                        |  |  |

|                    |                                       | 700                                                                                                                                                                                                                                   | 1500 | μА    | +125°C     |                                       |                                        |  |  |

|                    | All devices                           | 680                                                                                                                                                                                                                                   | 990  | μА    | -40°C      |                                       | F000 - 4 MUI-                          |  |  |

|                    |                                       | 680                                                                                                                                                                                                                                   | 960  | μА    | +25°C      | $V_{DD} = 3.3V^{(4)}$                 | Fosc = 1 MHz<br>( <b>RC_RUN</b> mode,  |  |  |

|                    |                                       | 670                                                                                                                                                                                                                                   | 950  | μА    | +85°C      | Regulator Disabled                    | HF-INTOSC)                             |  |  |

|                    |                                       | 800                                                                                                                                                                                                                                   | 1700 | μА    | +125°C     |                                       |                                        |  |  |

|                    | All devices                           | 760                                                                                                                                                                                                                                   | 1400 | μА    | -40°C      |                                       |                                        |  |  |

|                    |                                       | 780                                                                                                                                                                                                                                   | 1400 | μА    | +25°C      | V <sub>DD</sub> = 5V <sup>(5)</sup>   |                                        |  |  |

|                    |                                       | 800                                                                                                                                                                                                                                   | 1500 | μА    | +85°C      | Regulator Enabled                     |                                        |  |  |

|                    |                                       | 1200                                                                                                                                                                                                                                  | 2400 | μΑ    | +125°C     |                                       |                                        |  |  |

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in a high-impedance state and tied to VDD or Vss, and all features that add delta current are disabled (such as WDT, SOSC oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

$\underline{\mathsf{OSC1}}$  = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;  $\overline{\mathsf{MCLR}}$  = VDD; WDT enabled/disabled as specified.

- 3: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

- 4: Voltage regulator disabled (ENVREG = 0, tied to Vss, RETEN (CONFIG1L<0>) = 1).

- 5: Voltage regulator enabled (ENVREG = 1, tied to VDD, SRETEN (WDTCON<4>) = 1 and RETEN (CONFIG1L<0>) = 0).

- 6: LCD glass is not connected; resistor current is not included.

- 7: 48 MHz maximum frequency at 125°C.

## 31.5 AC (Timing) Characteristics

## 31.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS            |                                            | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|------------------------|--------------------------------------------|-----------|----------------------------------------|

| 2. TppS                |                                            | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                      |                                            |           |                                        |

| F                      | Frequency                                  | Т         | Time                                   |

| Lowercas               | Lowercase letters (pp) and their meanings: |           |                                        |

| рр                     |                                            |           |                                        |