Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 53                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

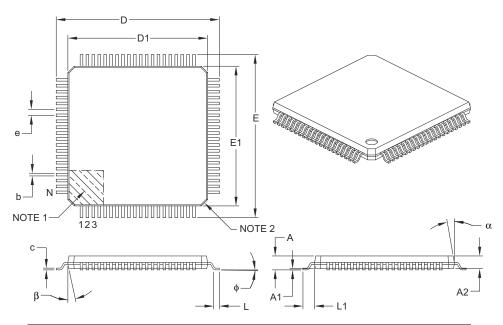

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                            | Pin Number      | Pin                            | Buffer                                | Description                                                                                                                                                      |

|-------------------------------------------------------------------------------------|-----------------|--------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                            | TQFP            | Туре                           | Туре                                  | Description                                                                                                                                                      |

|                                                                                     |                 |                                |                                       | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                                                    |

| RB0/INT0/SEG30/FLT0<br>RB0<br>INT0<br>SEG30<br>FLT0                                 | 58              | I/O<br>I<br>O<br>I             | TTL<br>ST<br>Analog<br>ST             | Digital I/O.<br>External Interrupt 0.<br>SEG30 output for LCD.<br>Enhanced PWM Fault input for ECCP1/2/3.                                                        |

| RB1/INT1/SEG8<br>RB1<br>INT1<br>SEG8                                                | 57              | I/O<br>I<br>O                  | TTL<br>ST<br>Analog                   | Digital I/O.<br>External Interrupt 1.<br>SEG8 output for LCD.                                                                                                    |

| RB2/INT2/SEG9/CTED1<br>RB2<br>INT2<br>SEG9<br>CTED1                                 | 56              | I/O<br>I<br>O<br>I             | TTL<br>ST<br>Analog<br>ST             | Digital I/O.<br>External Interrupt 2.<br>SEG9 output for LCD.<br>CTMU Edge 1 input.                                                                              |

| RB3/INT3/SEG10/<br>CTED2/ECCP2/P2A<br>RB3<br>INT3<br>SEG10<br>CTED2<br>ECCP2<br>P2A | 55              | I/O<br>I<br>0<br>I<br>I/O<br>0 | TTL<br>ST<br>Analog<br>ST<br>ST<br>ST | Digital I/O.<br>External Interrupt 3.<br>SEG10 output for LCD.<br>CTMU Edge 2 input.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>Enhanced PWM2 Output A. |

| RB4/KBI0/SEG11<br>RB4<br>KBI0<br>SEG11                                              | 54              | I/O<br>I<br>O                  | TTL<br>TTL<br>Analog                  | Digital I/O.<br>Interrupt-on-change pin.<br>SEG11 output for LCD.                                                                                                |

| RB5/KBI1/SEG29/T3CKI/<br>T1G<br>RB5<br>KBI1<br>SEG29<br>T3CKI<br>T1G                | 53              | I/O<br>I<br>O<br>I             | TTL<br>TTL<br>Analog<br>ST<br>ST      | Digital I/O.<br>Interrupt-on-change pin.<br>SEG29 output for LCD.<br>Timer3 clock input.<br>Timer1 external clock gate input.                                    |

| Legend: TTL = TTL cc<br>ST = Schmit<br>I = Input<br>P = Power                       | t Trigger input | with C                         | MOS leve                              | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)                                             |

## TABLE 1-4: PIC18F8XK90 PINOUT I/O DESCRIPTIONS (CONTINUED)

P = Power $I^2C^{TM} = I^2C/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K90 and PIC18F85K90 devices.

4: The CCP6, CCP7, CCP8 and CCP9 pin placement depends on the ECCPMX Configuration bit setting.

## REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 HFIOFS: INTOSC Frequency Stable bit

- 1 = HF-INTOSC oscillator frequency is stable

0 = HF-INTOSC oscillator frequency is not stable

- bit 1-0 SCS<1:0>: System Clock Select bits<sup>(4)</sup>

- 1x = Internal oscillator block (LF-INTOSC, MF-INTOSC or HF-INTOSC)

- 01 = SOSC oscillator

- 00 = Default primary oscillator (OSC1/OSC2 or HF-INTOSC with or without PLL; defined by the OSC<3:0> Configuration bits, CONFIG1H<3:0>.)

- **Note 1:** Reset state depends on the state of the IESO Configuration bit (CONFIG1H<7>).

- 2: Modifying these bits will cause an immediate clock frequency switch if the internal oscillator is providing the device clocks.

- 3: Source selected by the INTSRC bit (OSCTUNE<7>).

- 4: Modifying these bits will cause an immediate clock source switch.

- 5: INTSRC = OSCTUNE<7> and MFIOSEL = OSCCON2<0>.

## REGISTER 3-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-0     | U-0 | U-0 | R/W-0  | U-0 | R-x    | R/W-0   |

|-------|---------|-----|-----|--------|-----|--------|---------|

| —     | SOSCRUN | —   |     | SOSCGO |     | MFIOFS | MFIOSEL |

| bit 7 |         |     |     |        |     |        | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOSCRUN: SOSC Run Status bit                                                                                                                                                                                                                                                                    |

| <ul> <li>1 = System clock comes from a secondary SOSC</li> <li>0 = System clock comes from an oscillator other than SOSC</li> </ul>                                                                                                                                                             |

| Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

| SOSCGO: Oscillator Start Control bit                                                                                                                                                                                                                                                            |

| <ul> <li>1 = Oscillator is running, even if no other sources are requesting it</li> <li>0 = Oscillator is shut off if no other sources are requesting it (When the SOSC is selected to run from<br/>a digital clock input, rather than an external crystal, this bit has no effect.)</li> </ul> |

| Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

| MFIOFS: MF-INTOSC Frequency Stable bit                                                                                                                                                                                                                                                          |

| 1 = MF-INTOSC is stable<br>0 = MF-INTOSC is not stable                                                                                                                                                                                                                                          |

| MFIOSEL: MF-INTOSC Select bit                                                                                                                                                                                                                                                                   |

| <ul> <li>1 = MF-INTOSC is used in place of HF-INTOSC frequencies of 500 kHz, 250 kHz and 31.25 kHz</li> <li>0 = MF-INTOSC is not used</li> </ul>                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                 |

## 4.0 POWER-MANAGED MODES

The PIC18F87K90 family of devices offers a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (such as battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- · Sleep mode

There is an Ultra Low-Power Wake-up (ULPWU) for waking from the Sleep mode.

These categories define which portions of the device are clocked, and sometimes, at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block). The Sleep mode does not use a clock source.

The ULPWU mode, on the RA0 pin, enables a slow falling voltage to generate a wake-up, even from Sleep, without excess current consumption. (See **Section 4.7 "Ultra Low-Power Wake-up"**.)

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices. This feature allows the controller to use the SOSC oscillator instead of the primary one. Another power-saving feature is Sleep mode, offered by all PIC devices, where all device clocks are stopped.

## 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions:

- · Will the CPU be clocked or not

- · What will be the clock source

The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

## 4.1.1 CLOCK SOURCES

The SCS<1:0> bits select one of three clock sources for power-managed modes. Those sources are:

- The primary clock, as defined by the OSC<3:0> Configuration bits

- The secondary clock (the SOSC oscillator)

- The internal oscillator block (for LF-INTOSC modes)

### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These considerations are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entering the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current and impending mode, a change to a power-managed mode does not always require setting all of the previously discussed bits. Many transitions can be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured as desired, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mode     | oscco                   | ON Bits  | Module          | Clocking |                                                                                               |  |  |  |  |

|----------|-------------------------|----------|-----------------|----------|-----------------------------------------------------------------------------------------------|--|--|--|--|

|          | IDLEN<7> <sup>(1)</sup> | SCS<1:0> | CPU Peripherals |          | Available Clock and Oscillator Source                                                         |  |  |  |  |

| Sleep    | 0                       | N/A      | Off             | Off      | None – All clocks are disabled                                                                |  |  |  |  |

| PRI_RUN  | N/A                     | 00       |                 |          | Primary – XT, LP, HS, EC, RC and PLL modes.<br>This is the normal, Full-Power Execution mode. |  |  |  |  |

| SEC_RUN  | N/A                     | 01       | Clocked         | Clocked  | Secondary – SOSC Oscillator                                                                   |  |  |  |  |

| RC_RUN   | N/A                     | 1x       | Clocked         | Clocked  | Internal oscillator block <sup>(2)</sup>                                                      |  |  |  |  |

| PRI_IDLE | 1                       | 00       | Off             | Clocked  | Primary – LP, XT, HS, RC, EC                                                                  |  |  |  |  |

| SEC_IDLE | 1                       | 01       | Off Clocked Se  |          | Secondary – SOSC oscillator                                                                   |  |  |  |  |

| RC_IDLE  | 1                       | 1x       | Off             | Clocked  | Internal oscillator block <sup>(2)</sup>                                                      |  |  |  |  |

## TABLE 4-1:POWER-MANAGED MODES

**Note 1:** IDLEN reflects its value when the **SLEEP** instruction is executed.

2: Includes INTOSC (HF-INTOSC and MG-INTOSC) and INTOSC postscaler, as well as the LF-INTISC source.

NOTES:

## 6.3 Data Memory Organization

| Note: | The operation of some aspects of data    |

|-------|------------------------------------------|

|       | memory are changed when the PIC18        |

|       | extended instruction set is enabled. See |

|       | Section 6.6 "Data Memory and the         |

|       | Extended Instruction Set" for more       |

|       | information.                             |

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4,096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. PIC18FX6K90 and PIC18FX7K90 devices implement all 16 complete banks, for a total of 4 Kbytes. PIC18FX5K90 devices implement only the first eight complete banks, for a total of 2 Kbytes.

Figure 6-6 and Figure 6-7 show the data memory organization for the devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this section.

To ensure that commonly used registers (select SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to select SFRs and the lower portion of GPR Bank 0 without using the Bank Select Register. For details on the Access RAM, see **Section 6.3.2 "Access Bank"**.

## 6.3.1 BANK SELECT REGISTER

Large areas of data memory require an efficient addressing scheme to make possible rapid access to any address. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit, low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the four Most Significant bits of a location's address. The instruction itself includes the eight Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused, always read as '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The eight bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 6-7.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh, will end up resetting the Program Counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 6-6 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. When this instruction executes, it ignores the BSR completely. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

## 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value.

These operands are:

- POSTDEC Accesses the FSR value, then automatically decrements it by '1' afterwards

- POSTINC Accesses the FSR value, then automatically increments it by '1' afterwards

- PREINC Increments the FSR value by '1', then uses it in the operation

- PLUSW Adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value, offset by the value in the W register – with neither value actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair. Rollovers of the FSRnL register, from FFh to 00h, carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (for example, Z, N and OV bits).

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

## 6.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations.

As a specific case, assume that the FSR0H:FSR0L registers contain FE7h, the address of INDF1. Attempts to read the value of the INDF1, using INDF0 as an operand, will return 00h. Attempts to write to INDF1, using INDF0 as the operand, will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair, but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, however, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution, so that they do not inadvertently change settings that might affect the operation of the device.

## 6.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds five additional two-word commands to the existing PIC18 instruction set: ADDFSR, CALLW, MOVSF, MOVSS and SUBFSR. These instructions are executed as described in **Section 6.2.4 "Two-Word Instructions"**.

| Pin Name  | Function | TRIS<br>Setting | I/O | I/O Type         | Description                                                                                   |

|-----------|----------|-----------------|-----|------------------|-----------------------------------------------------------------------------------------------|

| RD0/SEG0/ | RD0      | 0               | 0   | DIG              | LATD<0> data output.                                                                          |

| CTPLS     |          | 1               | I   | ST               | PORTD<0> data input.                                                                          |

|           | SEG0     | 1               | 0   | ANA              | LCD Segment 0 output; disables all other pin functions.                                       |

|           | CTPLS    | x               | 0   | DIG              | CTMU pulse generator output.                                                                  |

| RD1/SEG1/ | RD1      | 0               | 0   | DIG              | LATD<1> data output.                                                                          |

| T5CKI/T7G |          | 1               | Ι   | ST               | PORTD<1> data input.                                                                          |

|           | SEG1     | 1               | 0   | ANA              | LCD Segment 1 output; disables all other pin functions.                                       |

|           | T5CKI    | x               | Ι   | ST               | Timer5 clock input.                                                                           |

|           | T7G      | x               | Ι   | ST               | Timer7 external clock gate input.                                                             |

| RD2/SEG2  | RD2      | 0               | 0   | DIG              | LATD<2> data output.                                                                          |

|           |          | 1               | I   | ST               | PORTD<2> data input.                                                                          |

|           | SEG2     | 1               | 0   | ANA              | LCD Segment 2 output; disables all other pin functions.                                       |

| RD3/SEG3  | RD3      | 0               | 0   | DIG              | LATD<3> data output.                                                                          |

|           |          | 1               | I   | ST               | PORTD<3> data input.                                                                          |

|           | SEG3     | 1               | 0   | ANA              | LCD Segment 3 output; disables all other pin functions.                                       |

| RD4/SEG4/ | RD4      | 0               | 0   | DIG              | LATD<4> data output.                                                                          |

| SDO2      |          | 1               | I   | ST               | PORTD<4> data input.                                                                          |

|           | SEG4     | 1               | 0   | ANA              | LCD Segment 4 output; disables all other pin functions.                                       |

|           | SDO2     | 0               | Р   | DOG              | SPI data output (MSSP module).                                                                |

| RD5/SEG5/ | RD5 0    |                 | 0   | DIG              | LATD<5> data output.                                                                          |

| SDI2/SDA2 |          | 1               | I   | ST               | PORTD<5> data input.                                                                          |

|           | SEG5     | 1               | 0   | ANA              | LCD Segment 5 output; disables all other pin functions.                                       |

|           | SDI2     | 1               | I   | ST               | SPI data input (MSSP module).                                                                 |

|           | SDA2     | 0               | 0   | l <sup>2</sup> C | I <sup>2</sup> C <sup>™</sup> data input (MSSP module). Input type depends on module setting. |

|           |          | 1               | I   | ANA              | LCD Segment 5 output; disables all other pin functions.                                       |

| RD6/SEG6/ | RD6      | 0               | 0   | DIG              | LATD<6> data output.                                                                          |

| SCK2/SCL2 |          | 1               | I   | ST               | PORTD<6> data input.                                                                          |

|           | SEG6     | 1               | 0   | ANA              | LCD Segment 6 output; disables all other pin functions.                                       |

|           | SCK2     | 0               | 0   | DIG              | SPI clock output (MSSP module); takes priority over port data.                                |

|           |          | 1               | I   | ST               | SPI clock input (MSSP module).                                                                |

|           | SCL2     | 0               | 0   | DIG              | I <sup>2</sup> C clock output (MSSP module); takes priority over port data.                   |

|           |          | 1               | I   | l <sup>2</sup> C | I <sup>2</sup> C clock input (MSSP module). Input type depends on module setting.             |

| RD7/SEG7/ | RD7      | 0               | 0   | DIG              | LATD<7> data output.                                                                          |

| SS2       |          | 1               | I   | ST               | PORTD<7> data input.                                                                          |

|           | SEG7     | 1               | I   | ANA              | LCD Segment 7 output; disables all other pin functions.                                       |

|           | SS2      | 1               | I   | TTL              | Slave select input for MSSP module.                                                           |

TABLE 11-7: PORTD FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,  $I^2C = I^2C$  Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| TABLE 11-8: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0  | Reset<br>Values on<br>Page: |

|---------|--------|--------|---------------------|--------|--------|-----------|-----------|--------|-----------------------------|

| PORTD   | RD7    | RD6    | RD5                 | RD4    | RD3    | RD2       | RD1       | RD0    | 78                          |

| LATD    | LATD7  | LATD6  | LATD5               | LATD4  | LATD3  | LATD2     | LATD1     | LATD0  | 78                          |

| TRISD   | TRISD7 | TRISD6 | TRISD5              | TRISD4 | TRISD3 | TRISD2    | TRISD1    | TRISD0 | 78                          |

| LCDSE0  | SE07   | SE06   | SE05                | SE04   | SE03   | SE02      | SE01      | SE00   | 83                          |

| PADCFG1 | RDPU   | REPU   | RJPU <sup>(1)</sup> | _      | _      | RTSECSEL1 | RTSECSEL0 | _      | 80                          |

Legend: Shaded cells are not used by PORTD.

Note 1: This bit is not available in 64-pin devices.

## 11.10 PORTJ, TRISJ and LATJ Registers

Note: PORTJ is available only on 80-pin devices.

PORTJ is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISJ and LATJ.

All pins on PORTJ are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Note: These pins are configured as digital inputs on any device Reset.

All PORTJ pins, except RJ0, are multiplexed with LCD segment drives controlled by the LCDSE4 register. I/O port functions are only available on these pins when the segments are disabled.

Each of the PORTJ pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by clearing bit RJPU (PADCFG1<5>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on any device Reset.

| CLRF  | PORTJ | ; Initialize PORTJ by     |

|-------|-------|---------------------------|

|       |       | ; clearing output latches |

| CLRF  | LATJ  | ; Alternate method        |

|       |       | ; to clear output latches |

| MOVLW | 0CFh  | ; Value used to           |

|       |       | ; initialize data         |

|       |       | ; direction               |

| MOVWF | TRISJ | ; Set RJ3:RJ0 as inputs   |

|       |       | ; RJ5:RJ4 as output       |

|       |       | ; RJ7:RJ6 as inputs       |

|       |       |                           |

## 13.1 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), displayed in Register 13-2, is used to control the Timer1 gate.

## REGISTER 13-2: T1GCON: TIMER1 GATE CONTROL REGISTER<sup>(1)</sup>

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 7       TMR1GE: Timer1 Gate Enable bit       If TMR1ON = 0:       This bit is ignored.         If TMR1ON = 1:       1 = Timer1 counting is controlled by the Timer1 gate function       0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit       1 = Timer1 gate is active-high (Timer1 counts when gate is high)         0 = Timer1 gate is active-low (Timer1 counts when gate is low)       bit 5         bit 5       T1GTM: Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled       0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.       bit 4         t1GSPM: Timer1 Gate Single Pulse Mode bit       1 = Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate       0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                               | T1GSS0<br>bit 0<br>wn                                                                                                                    |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 7       TMR1GE: Timer1 Gate Enable bit       If TMR1ON = 0:       This bit is ignored.         If TMR1ON = 1:       1 = Timer1 counting is controlled by the Timer1 gate function       0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit       1 = Timer1 gate is active-high (Timer1 counts when gate is high)         0 = Timer1 gate is active-low (Timer1 counts when gate is low)       0 = Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled       0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.       bit 4         t1GSPM: Timer1 Gate Single Pulse Mode bit       1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate       0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/TIDONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                    |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 7       TMR1GE: Timer1 Gate Enable bit       If TMR1ON = 0:       This bit is ignored.         If TMR1ON = 1:       1 = Timer1 counting is controlled by the Timer1 gate function       0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit       1 = Timer1 gate is active-high (Timer1 counts when gate is high)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit       1 = Timer1 Gate Toggle mode is enabled         0 = Timer1 gate flip-flop toggles on every rising edge.       bit 4         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled <td< td=""><td>wn</td></td<> | wn                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 7       TMR1GE: Timer1 Gate Enable bit       If TMR1ON = 0:       This bit is ignored.         If TMR1ON = 1:       1 = Timer1 counting is controlled by the Timer1 gate function       0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit       1 = Timer1 gate is active-high (Timer1 counts when gate is high)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit       1 = Timer1 Gate Toggle mode is enabled         0 = Timer1 gate flip-flop toggles on every rising edge.       bit 4         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled <td< td=""><td>wn</td></td<> | wn                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 7 <b>TMR1GE:</b> Timer1 Gate Enable bit       If <u>TMR1ON = 0</u> :<br>This bit is ignored.       If <u>TMR1ON = 1</u> :<br>1 = Timer1 counting is controlled by the Timer1 gate function<br>0 = Timer1 counts regardless of the Timer1 gate function       0 = Timer1 counts regardless of the Timer1 gate function         bit 6 <b>T1GPOL:</b> Timer1 Gate Polarity bit       1 = Timer1 gate is active-high (Timer1 counts when gate is high)       0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5 <b>T1GTM:</b> Timer1 Gate Toggle Mode bit       1 = Timer1 Gate Toggle mode is enabled       0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared<br>Timer1 gate flip-flop toggles on every rising edge.         bit 4 <b>T1GSPM:</b> Timer1 Gate Single Pulse Mode bit       1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         bit 3 <b>T1GGO/T1DONE:</b> Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                    | wn                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| bit 7 <b>TMR1GE:</b> Timer1 Gate Enable bit         If <u>TMR1ON = 0</u> :         This bit is ignored.         If <u>TMR1ON = 1</u> :         1 = Timer1 counting is controlled by the Timer1 gate function         0 = Timer1 counts regardless of the Timer1 gate function         0 = Timer1 counts regardless of the Timer1 gate function         bit 6 <b>T1GPOL:</b> Timer1 Gate Polarity bit         1 = Timer1 gate is active-high (Timer1 counts when gate is high)         0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5 <b>T1GTM:</b> Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled       0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.       bit 4         bit 4 <b>T1GSPM:</b> Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is disabled </td <td>wn</td>             | wn                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| If TMR1ON = 0:<br>This bit is ignored.         If TMR1ON = 1:<br>1 = Timer1 counting is controlled by the Timer1 gate function<br>0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit<br>1 = Timer1 gate is active-high (Timer1 counts when gate is high)<br>0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit<br>1 = Timer1 Gate Toggle mode is enabled<br>0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared<br>Timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit<br>1 = Timer1 Gate Single Pulse mode is enabled on the timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit<br>1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate<br>0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| This bit is ignored.If TMR1ON = 1:1 = Timer1 counting is controlled by the Timer1 gate function0 = Timer1 counts regardless of the Timer1 gate functionbit 6T1GPOL: Timer1 Gate Polarity bit1 = Timer1 gate is active-high (Timer1 counts when gate is high)0 = Timer1 gate is active-low (Timer1 counts when gate is low)bit 5T1GTM: Timer1 Gate Toggle Mode bit1 = Timer1 Gate Toggle mode is enabled0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is clearedTimer1 gate flip-flop toggles on every rising edge.bit 4T1GSPM: Timer1 Gate Single Pulse Mode bit1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate0 = Timer1 Gate Single Pulse mode is disabledbit 3T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| If TMR1ON = 1:         1 = Timer1 counting is controlled by the Timer1 gate function         0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit         1 = Timer1 gate is active-high (Timer1 counts when gate is high)         0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled         0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 4       T1GSPM: Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 1 = Timer1 counting is controlled by the Timer1 gate function         0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit         1 = Timer1 gate is active-high (Timer1 counts when gate is high)         0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled         0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled or is enabled       Timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 0 = Timer1 counts regardless of the Timer1 gate function         bit 6       T1GPOL: Timer1 Gate Polarity bit         1 = Timer1 gate is active-high (Timer1 counts when gate is high)       0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled       0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         0 = Timer1 Gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled         0 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is disabled         1 = Timer1 Gate Single Pulse mode is disabled         0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| bit 6       T1GPOL: Timer1 Gate Polarity bit         1 = Timer1 gate is active-high (Timer1 counts when gate is high)       0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled       0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled and bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 1 = Timer1 gate is active-high (Timer1 counts when gate is high)         0 = Timer1 gate is active-low (Timer1 counts when gate is low)         bit 5       T1GTM: Timer1 Gate Toggle Mode bit         1 = Timer1 Gate Toggle mode is enabled         0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| <ul> <li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li> <li>bit 5 T1GTM: Timer1 Gate Toggle Mode bit         <ol> <li>1 = Timer1 Gate Toggle mode is enabled</li> <li>0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared Timer1 gate flip-flop toggles on every rising edge.</li> </ol> </li> <li>bit 4 T1GSPM: Timer1 Gate Single Pulse Mode bit         <ol> <li>1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate</li> <li>0 = Timer1 Gate Single Pulse mode is disabled</li> </ol> </li> <li>bit 3 T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 1 = Timer1 Gate Toggle mode is enabled         0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.         bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared         Timer1 gate flip-flop toggles on every rising edge.         bit 4 <b>T1GSPM:</b> Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Timer1 gate flip-flop toggles on every rising edge.         bit 4         T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3         T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| bit 4       T1GSPM: Timer1 Gate Single Pulse Mode bit         1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 1 = Timer1 Gate Single Pulse mode is enabled and is controlling Timer1 gate         0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 0 = Timer1 Gate Single Pulse mode is disabled         bit 3       T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| bit 3 T1GGO/T1DONE: Timer1 Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 1 = Timer1 gate single pulse acquisition is ready, waiting for an edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 0 = Timer1 gate single pulse acquisition has completed or has not been started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 = Timer1 gate single pulse acquisition has completed or has not been started                                                           |  |  |  |  |  |  |  |  |  |

| This bit is automatically cleared when T1GSPM is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| bit 2 T1GVAL: Timer1 Gate Current State bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |  |  |  |  |  |  |  |  |  |