Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betails                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66k90-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Special Microcontroller Features:**

- Operating Voltage Range: 1.8V to 5.5V

- On-Chip 3.3V Regulator

- Operating Speed up to 64 MHz

- Up to 128 Kbytes On-Chip Flash Program Memory

- Data EEPROM of 1,024 Bytes

- 4K x 8 General Purpose Registers (SRAM)

- 10,000 Erase/Write Cycle Flash Program Memory, Minimum

- 1,000,000 Erase/write Cycle Data EEPROM Memory, Typical

- Flash Retention 40 Years, Minimum

- Three Internal Oscillators: LF-INTRC (31 kHz), MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 4,194s (about 70 minutes)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- · In-Circuit Debug via Two Pins

- Programmable:

- BOR

- LVD

- Two Enhanced Addressable USART modules:

- LIN/J2602 support

- Auto-Baud Detect (ABD)

- 12-Bit A/D Converter with up to 24 Channels:

- Auto-acquisition and Sleep operation

- Differential Input mode of operation

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18FXXKXX MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18F87K90 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG (if implemented) and VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

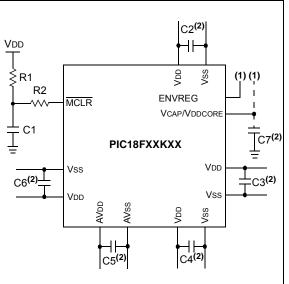

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED

#### MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic R1: 10 k $\Omega$

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)" for explanation of ENVREG pin connections.

- 2: The example shown is for a PIC18F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

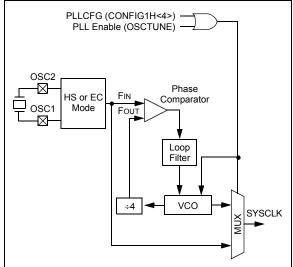

#### FIGURE 3-7: PLL BLOCK DIAGRAM

### 3.5.2.2 PLL and HF-INTOSC

The PLL is available to the internal oscillator block when the internal oscillator block is configured as the primary clock source. In this configuration, the PLL is enabled in software and generates a clock output of up to 64 MHz.

The operation of INTOSC with the PLL is described in **Section 3.6.2 "INTPLL Modes**". Care should be taken that the PLL is enabled only if the HF-INTOSC postscaler is configured for 8 MHz or 16 MHz.

# 3.6 Internal Oscillator Block

The PIC18F87K90 family of devices includes an internal oscillator block which generates two different clock signals. Either clock can be used as the micro-controller's clock source, which may eliminate the need for an external oscillator circuit on the OSC1 and/or OSC2 pins.

The internal oscillator consists of three blocks, depending on the frequency of operation. They are HF-INTOSC, MF-INTOSC and LF-INTRC.

In HF-INTOSC mode, the internal oscillator can provide a frequency, ranging from 31 kHz to 16 MHz, with the postscaler deciding the selected frequency (IRCF<2:0>).

The INTSRC bit (OSCTUNE<7>) and MFIOSEL bit (OSCCON2<0>) also decide which INTOSC provides the lower frequency (500 kHz to 31 kHz). For the HF-INTOSC to provide these frequencies, INTSRC = 1 and MFIOSEL = 0.

In HF-INTOSC, the postscaler (IRCF<2:0>) provides the frequency range of 31 kHz to 16 MHz. If HF-INTOSC is used with the PLL, the input frequency to the PLL should be 8 MHz or 16 MHz (IRCF<2:0> = 111, 110).

For MF-INTOSC mode to provide a frequency range of 500 kHz to 31 kHz, INTSRC = 1 and MFIOSEL = 1. The postscaler (IRCF<2:0>), in this mode, provides the frequency range of 31 kHz to 500 kHz.

The LF-INTRC can provide only 31 kHz if INTSRC = 0.

The LF-INTRC provides 31 kHz and is enabled if it is selected as the device clock source. The mode is enabled automatically when any of the following is enabled:

- Power-up Timer

- · Fail-Safe Clock Monitor

- · Watchdog Timer

- · Two-Speed Start-up

These features are discussed in greater detail in **Section 28.0 "Special Features of the CPU"**.

The clock source frequency (HF-INTOSC, MF-INTOSC or LF-INTRC direct) is selected by configuring the IRCF bits of the OSCCON register, as well the INTSRC and MFIOSEL bits. The default frequency on device Resets is 8 MHz.

#### 3.6.1 INTIO MODES

Using the internal oscillator as the clock source eliminates the need for up to two external oscillator pins, which can then be used for digital I/O. Two distinct oscillator configurations, which are determined by the OSC Configuration bits, are available:

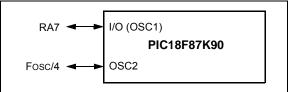

- In INTIO1 mode, the OSC2 pin (RA6) outputs Fosc/4, while OSC1 functions as RA7 (see Figure 3-8) for digital input and output.

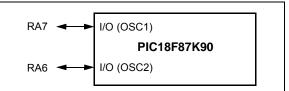

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6 (see Figure 3-9). Both are available as digital input and output ports.

#### FIGURE 3-8: INTIO1 OSCILLATOR MODE

#### FIGURE 3-9: INTIO2 OSCILLATOR MODE

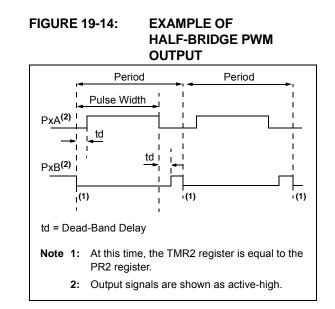

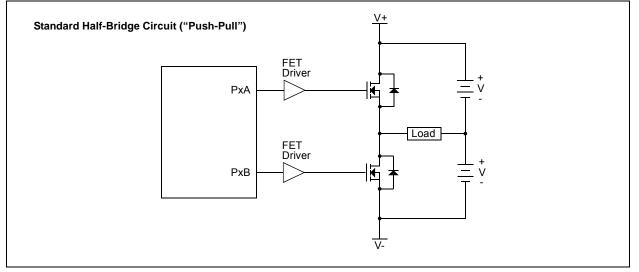

#### 19.4.6 PROGRAMMABLE DEAD-BAND DELAY MODE

In half-bridge applications, where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period until one switch completely turns off. During this brief interval, a very high current (shoot-through current) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. For an illustration, see Figure 19-14. The lower seven bits of the associated ECCPxDEL register (Register 19-4) set the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

# FIGURE 19-15: EXAMPLE OF HALF-BRIDGE APPLICATIONS

# PIC18F87K90 FAMILY

The LCDSE5:LCDSE0 registers configure the functions of the port pins. Setting the segment enable bit for a particular segment configures that pin as an LCD driver. There are six LCD Segment Enable registers, as shown in Table 20-1. The prototype LCDSEx register is shown in Register 20-5.

# TABLE 20-1:LCDSE REGISTERS AND<br/>ASSOCIATED SEGMENTS

| Register | Segments                                        |

|----------|-------------------------------------------------|

| LCDSE0   | 7:0 (RD<7:0>)                                   |

| LCDSE1   | 15:8 (RA<5:4>, RC2, RC5,<br>RB<4:1>)            |

| LCDSE2   | 23:16 (RF<5:1>, RA1,<br>RC<4:3>)                |

| LCDSE3   | 31:24 (RE7, RB0, RB5,<br>RC<7:6>, RG4, RF<7:6>) |

| LCDSE4   | 39:32 (RJ<4:7>, RJ<3:1>, RC1)                   |

| LCDSE5   | 47:40 (RH<0:3>, RH<7:4>)                        |

| Note: | The LCDSE5:LCDSE4 registers are not |

|-------|-------------------------------------|

|       | implemented in PIC18F6XK90 devices. |

Once the module is initialized for the LCD panel, the individual bits of the LCDDATA23:LCDDATA0 registers are cleared or set to represent a clear or dark pixel, respectively.

Specific sets of LCDDATA registers are used with specific segments and common signals. Each bit represents a unique combination of a specific segment connected to a specific common.

Individual LCDDATA bits are named by the convention, "SxxCy", with "xx" as the segment number and "y" as the common number. The relationship is summarized in Table 20-2. The prototype LCDDATAx register is shown in Register 20-6.

| Note: | In PIC18F6XK90 devices, writing into the  |

|-------|-------------------------------------------|

|       | registers, LCDDATA4, LCDDATA5,            |

|       | LCDDATA10, LCDDATA11, LCDDATA16,          |

|       | LCDDATA17, LCDDATA22 and                  |

|       | LCDDATA23, will not affect the status of  |

|       | any pixel. These registers can be used as |

|       | general purpose registers.                |

## REGISTER 20-5: LCDSEx: LCD SEGMENTx ENABLE REGISTER

| R/W-0       | R/W-0 R/W-0 |                     | W-0 R/W-0 R/V |           | R/W-0     | R/W-0     | R/W-0 |  |  |

|-------------|-------------|---------------------|---------------|-----------|-----------|-----------|-------|--|--|

| SE(n + 7)   | SE(n + 6)   | SE(n + 5) SE(n + 4) |               | SE(n + 3) | SE(n + 2) | SE(n + 1) | SE(n) |  |  |

| bit 7 bit 0 |             |                     |               |           |           |           |       |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| SE(n + 7):SE(n): Segment Enable bits |

|--------------------------------------|

| For LCDSE0: $n = 0$                  |

| For LCDSE1: n = 8                    |

| <u>For LCDSE2: n = 16</u>            |

| For LCDSE3: n = 24                   |

| For LCDSE4: n = 32                   |

| <u>For LCDSE5: n = 40</u>            |

|                                      |

1 = Segment function of the pin is enabled, digital I/O is disabled

0 = I/O function of the pin is enabled

# 20.7 LCD Frame Frequency

The rate at which the COM and SEG outputs change is called the LCD frame frequency.

#### TABLE 20-5: FRAME FREQUENCY FORMULAS

| Multiplex | Frame Frequency =                    |  |  |  |  |  |  |  |

|-----------|--------------------------------------|--|--|--|--|--|--|--|

| Static    | Clock Source/(4 x 1 x (LP<3:0> + 1)) |  |  |  |  |  |  |  |

| 1/2       | Clock Source/(2 x 2 x (LP<3:0> + 1)) |  |  |  |  |  |  |  |

| 1/3       | Clock Source/(1 x 3 x (LP<3:0> + 1)) |  |  |  |  |  |  |  |

| 1/4       | Clock Source/(1 x 4 x (LP<3:0> + 1)) |  |  |  |  |  |  |  |

Note: Clock source is (Fosc/4)/8192, Timer1 Osc/32 or INTRC/32.

#### TABLE 20-6: APPROXIMATE FRAME FREQUENCY (IN Hz) USING Fosc AT 32 MHz, TIMER1 AT 32.768 kHz OR INTRC OSC

| LP<3:0> | Static | 1/2 | 1/3 | 1/4 |

|---------|--------|-----|-----|-----|

| 1       | 125    | 125 | 167 | 125 |

| 2       | 83     | 83  | 111 | 83  |

| 3       | 62     | 62  | 83  | 62  |

| 4       | 50     | 50  | 67  | 50  |

| 5       | 42     | 42  | 56  | 42  |

| 6       | 36     | 36  | 48  | 36  |

| 7       | 31     | 31  | 42  | 31  |

# 20.8 LCD Waveform Generation

LCD waveform generation is based on the philosophy that the net AC voltage across the dark pixel should be maximized and the net AC voltage across the clear pixel should be minimized. The net DC voltage across any pixel should be zero.

The COM signal represents the time slice for each common, while the SEG contains the pixel data.

The pixel signal (COM-SEG) will have no DC component and can take only one of the two rms values. The higher rms value will create a dark pixel and a lower rms value will create a clear pixel.

As the number of commons increases, the delta between the two rms values decreases. The delta represents the maximum contrast that the display can have.

The LCDs can be driven by two types of waveforms: Type-A and Type-B. In a Type-A waveform, the phase changes within each common type, whereas a Type-B waveform's phase changes on each frame boundary. Thus, Type-A waveforms maintain 0 VDc over a single frame, whereas Type-B waveforms take two frames.

| Note 1: | If Sleep has to be executed with       |  |  |  |  |  |  |  |

|---------|----------------------------------------|--|--|--|--|--|--|--|

|         | LCD Sleep enabled (SLPEN               |  |  |  |  |  |  |  |

|         | (LCDCON<6>) = 1), care must be taken   |  |  |  |  |  |  |  |

|         | to execute Sleep only when VDC on all  |  |  |  |  |  |  |  |

|         | the pixels is '0'.                     |  |  |  |  |  |  |  |

| 2:      | When the LCD clock source is (Fosc/4)/ |  |  |  |  |  |  |  |

2: When the LCD clock source is (FOSC/4)/ 8192, if Sleep is executed irrespective of the LCDCON<SLPEN> setting, the LCD goes into Sleep. Thus, take care to see that VDC on all pixels is '0' when Sleep is executed.

Figure 20-7 through Figure 20-17 provide waveforms for static, half-multiplex, one-third multiplex and quarter multiplex drives for Type-A and Type-B waveforms.

# 21.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Each MSSP module consists of a Transmit/Receive Shift register (SSPxSR) and a Serial Receive Transmit Buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full detect bit, BF (SSPxSTAT<0>), and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL (SSPxCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPxBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF (SSPxSTAT<0>), indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 21-1 shows the loading of the SSPxBUF (SSPxSR) for data transmission.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various status conditions.

## 21.3.3 OPEN-DRAIN OUTPUT OPTION

The drivers for the SDOx output and SCKx clock pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor, and allows the output to communicate with external circuits without the need for additional level shifters. For more information, see **Section 11.1.3 "Open-Drain Outputs"**.

The open-drain output option is controlled by the SSP2OD (ODCON1<0>) and SSP1OD bits (ODCON1<7>). Setting an SSPxOD bit configures the SDOx and SCKx pins for the corresponding module for open-drain operation.

Note: To avoid lost data in Master mode, a read of the SSPxBUF must be performed to clear the Buffer Full (BF) detect bit (SSPxSTAT<0>) between each transmission.

#### EXAMPLE 21-1: LOADING THE SSP1BUF (SSP1SR) REGISTER

| LOOP | BTFSS | SSP1STAT, BF | ;Has data been received (transmit complete)? |

|------|-------|--------------|----------------------------------------------|

|      | BRA   | LOOP         | ;No                                          |

|      | MOVF  | SSP1BUF, W   | ;WREG reg = contents of SSP1BUF              |

|      | MOVWF | RXDATA       | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W    | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSP1BUF      | ;New data to xmit                            |

#### 21.4.3.2 Address Masking Modes

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which greatly expands the number of addresses Acknowledged.

The  $l^2C$  slave behaves the same way whether address masking is used or not. However, when address masking is used, the  $l^2C$  slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking the SSPxBUF.

The PIC18F87K90 family of devices is capable of using two different Address Masking modes in I<sup>2</sup>C slave operation: 5-Bit Address Masking and 7-Bit Address Masking. The Masking mode is selected at device configuration using the MSSPMSK Configuration bit. The default device configuration is 7-Bit Address Masking.

Both Masking modes, in turn, support address masking of 7-bit and 10-bit addresses. The combination of Masking modes and addresses provide different ranges of Acknowledgable addresses for each combination.

While both Masking modes function in roughly the same manner, the way they use address masks are different.

#### 21.4.3.3 5-Bit Address Masking Mode

As the name implies, 5-Bit Address Masking mode uses an address mask of up to 5 bits to create a range of addresses to be Acknowledged, using bits, 5 through 1, of the incoming address. This allows the module to Acknowledge up to 31 addresses when using 7-bit addressing, or 63 addresses with 10-bit addressing (see Example 21-2). This Masking mode is selected when the MSSPMSK Configuration bit is programmed ('0').

The address mask in this mode is stored in the SSPxCON2 register, which stops functioning as a control register in  $l^2C$  Slave mode (Register 21-6). In 7-Bit Address Masking mode, address mask bits, ADMSK<5:1> (SSPxCON2<5:1>), mask the corresponding address bits in the SSPxADD register. For any ADMSK bits that are set (ADMSK<n> = 1), the corresponding address bit is ignored (SSPxADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

In 10-Bit Address Masking mode, bits, ADMSK<5:2>, mask the corresponding address bits in the SSPxADD register. In addition, ADMSK1 simultaneously masks the two LSbs of the address (SSPxADD<1:0>). For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (SPxADD<n> = x). Also note, that although in 10-Bit Address Masking mode, the upper address bits reuse part of the SSPxADD register bits. The address mask bits do not interact with those bits; they only affect the lower address bits.

- **Note 1:** ADMSK1 masks the two Least Significant bits of the address.

- The two Most Significant bits of the address are not affected by address masking.

#### EXAMPLE 21-2: ADDRESS MASKING EXAMPLES IN 5-BIT MASKING MODE

#### 7-Bit Addressing:

SSPxADD<7:1>= A0h (1010000) (SSPxADD<0> is assumed to be '0')

```

ADMSK<5:1> = 00111

```

Addresses Acknowledged: A0h, A2h, A4h, A6h, A8h, AAh, ACh, AEh

#### 10-Bit Addressing:

SSPxADD<7:0> = A0h (10100000) (The two MSb of the address are ignored in this example, since they are not affected by masking)

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A1h, A2h, A3h, A4h, A5h, A6h, A7h, A8h, A9h, AAh, ABh, ACh, ADh, AEh, AFh

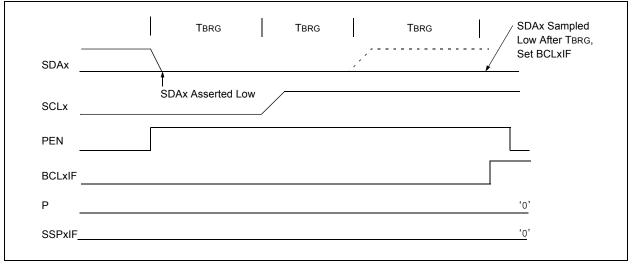

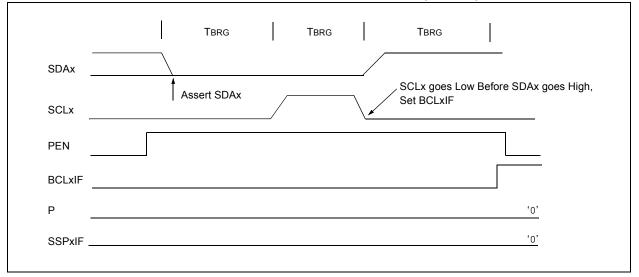

#### 21.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD<6:0> and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 21-33). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 21-34).

#### FIGURE 21-33: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 21-34: BUS COLLISION DURING A STOP CONDITION (CASE 2)

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | l = 0, BRG            | 16 = 1     |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            | Fosc = 10.000 MHz           |                       |            | Fosc = 8.000 MHz            |                       |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                 | 0.00       | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |

| 1.2         | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |

| 2.4         | 2.402                 | 0.06       | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |

| 9.6         | 9.615                 | 0.16       | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2        | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6        | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2       | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | _                     | —          | —                           |

# TABLE 22-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|       |                       |            | S                           | YNC = 0, E            | BRGH = (   | ), BRG16 =                  | 1                     |            |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Foso                  | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.04       | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16      | 207                         |

| 1.2   | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4   | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6   | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |

| 19.2  | 19.231                | 0.16       | 12                          | —                     | _          | _                           | —                     | _          | _                           |

| 57.6  | 62.500                | 8.51       | 3                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2 | 125.000               | 8.51       | 1                           | _                     | _          | —                           | _                     | _          | _                           |

|              |                       |            |                             | SYNC = 0,             | , BRGH =   | = 1, BRG16                  | = 1 or SY             | NC = 1,    | BRG16 = 1                   |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | ) MHz                       | Fosc                  | = 10.000   | ) MHz                       | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                 | 0.00       | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                 | 0.02       | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                 | 0.06       | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                | -0.03      | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                | 0.35       | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943               | -0.22      | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

|       |                       | SYN        | IC = 0, BR(                 | GH = 1, BF            | <b>RG16 =</b> 1 | or SYNC =                   | = 1, BRG1             | 6 = 1      |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|-----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fost                  | c = 4.000  | MHz                         | Fos                   | c = 2.000       | MHz                         | Fos                   | c = 1.000  | MHz                         |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error      | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.01       | 3332                        | 0.300                 | -0.04           | 1665                        | 0.300                 | -0.04      | 832                         |

| 1.2   | 1.200                 | 0.04       | 832                         | 1.201                 | -0.16           | 415                         | 1.201                 | -0.16      | 207                         |

| 2.4   | 2.404                 | 0.16       | 415                         | 2.403                 | -0.16           | 207                         | 2.403                 | -0.16      | 103                         |

| 9.6   | 9.615                 | 0.16       | 103                         | 9.615                 | -0.16           | 51                          | 9.615                 | -0.16      | 25                          |

| 19.2  | 19.231                | 0.16       | 51                          | 19.230                | -0.16           | 25                          | 19.230                | -0.16      | 12                          |

| 57.6  | 58.824                | 2.12       | 16                          | 55.555                | 3.55            | 8                           | —                     | _          | —                           |

| 115.2 | 111.111               | -3.55      | 8                           | —                     | _               | —                           | —                     | _          | —                           |

# 22.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCxIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared after this when a rising edge is seen on RXx/DTx. The interrupt condition is then cleared by reading the RCREGx register. Ordinarily, the data in RCREGx will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCxIF flag is set should not be used as an indicator of the integrity of the data in RCREGx. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering Sleep mode.

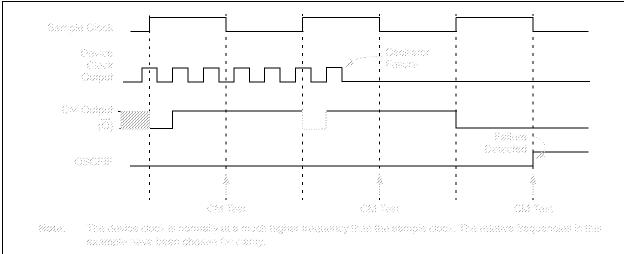

## FIGURE 22-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

| 0366                  | 승규는 다 다 다      | ટું આ આ આવે પ                         | pununun.                                   | ટ્રે ચેટ પ     | 7 3.2 3.2 3. | ઝ દેકે દેકે દે. | ( N.C. N.C. N.C. N | હતું દેવને દાતે દેવ                     | 옷 다섯 다가 다가                            | 3.2 S.Z | [ 1년 1년 1년 1년 1년                                 | [12] 12] 12 |

|-----------------------|----------------|---------------------------------------|--------------------------------------------|----------------|--------------|-----------------|--------------------|-----------------------------------------|---------------------------------------|---------|--------------------------------------------------|-------------|

|                       | ) – 85 Set byg | Yeast                                 | 5                                          |                |              | 1               |                    |                                         |                                       |         | a garren hadal                                   | YSaaaas -   |

| 9403 B8 <sup>99</sup> | S              |                                       | 2                                          |                |              | ······          | ·····              |                                         | •••••••                               |         |                                                  |             |

|                       | 5              | ;                                     | ·<br>·                                     | 4 - 1<br>4 - 1 | ÷            | 5               | 1                  | 5                                       |                                       | 1       |                                                  | (<br>(      |

| ozie Skieber          | 3              | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·      | 111            |              |                 |                    |                                         | :776277777777                         | an i    |                                                  | ·····       |

|                       | 2              | ·                                     |                                            | < 2<br>        |              | 1. N.           | :                  |                                         | · · · · · · · · · · · · · · · · · · · |         | (<br>                                            | (           |

| 800a9                 | \$             | ,<br>;                                | ;<br>; · · · · · · · · · · · · · · · · · · | ÷              | ·····        | ••••••          |                    |                                         | . 44                                  |         | Varia and an | Z           |

|                       | /              | ·                                     | ł                                          |                |              |                 | . S                | effect cas                              | an Marian                             | 00 OCJ  | žorec –                                          |             |

|                       | 2 C            | ·                                     | ·                                          |                |              |                 |                    | 1 A A A A A A A A A A A A A A A A A A A | · · · · · · · · · · · · · · · · · · · |         |                                                  |             |

## FIGURE 22-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

|                       | <ol> <li>BR Star BV</li> </ol> | (NUAUAUA).<br>%*******                | innunni.       |                | mununun.<br>İ                          | anagaguna.               | LAUAUAUAUAU<br>Jauk      |  |

|-----------------------|--------------------------------|---------------------------------------|----------------|----------------|----------------------------------------|--------------------------|--------------------------|--|

| VYDE 58 <sup>63</sup> |                                | - 4<br>                               | 2/             |                | ······································ |                          |                          |  |

|                       | 6.<br>6.<br>9.                 | · · · · · · · · · · · · · · · · · · · | · · · · ·      |                |                                        |                          |                          |  |

| 8026                  |                                | 9<br>                                 | e<br>Esocatori | <br>Sosap Sods | à Ciean                                | i<br>sé due la User Real | e el ACRECE <sup>2</sup> |  |

2: The HURARY comens in the write the WOH of it eat.

#### 22.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>), or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREGx register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# FIGURE 22-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

| .C7/RX1/DT1/<br>SEG28 Pin                 | 1                | bit 0       | bit 1       | bit 2       | bit 3 | bit 4 | bit 5       | bit 6       | X' <u>.                                    </u> | bit 7            |

|-------------------------------------------|------------------|-------------|-------------|-------------|-------|-------|-------------|-------------|-------------------------------------------------|------------------|

| C6/TX1/CK1/<br>SEG27 Pin<br>(TXCKP = 0)   | 1<br>1<br>1<br>1 |             |             |             |       | J÷    | J.          | J; L        |                                                 | 1<br>1<br>1<br>1 |

| C6/TX1/CK1/<br>SEG27 Pin -<br>(TXCKP = 1) | ,<br>,<br>,<br>, |             |             |             |       |       |             |             |                                                 | 1<br>1<br>1<br>1 |

| Write to _<br>bit, SREN                   | - <u> </u>       |             |             |             |       |       |             |             |                                                 |                  |

| SREN bit                                  |                  | 1           |             | 1           | 1     |       | 1           |             |                                                 | 1                |

| CREN bit                                  | '0'              | 1           |             | 1<br>1      | 1     | 1     | 1<br>1      | 1           | î<br>L                                          | ʻ0               |

| RC1IF bit<br>(Interrupt) –                | 1<br>1<br>1      | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1 |       |       | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1                                     |                  |

| Read<br>RCREG1 -                          | ,<br>,<br>,      | 1           | 1           |             |       |       |             |             | 1<br>1<br>1                                     | :_f              |

# PIC18F87K90 FAMILY

| R/W-0        | U-0                                                                                                                                                                                      | R/W-0                     | R/W-0         | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------|--------------------------|------------------|-----------------|-------|

| ADFM         | _                                                                                                                                                                                        | ACQT2                     | ACQT1         | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |

| bit 7        |                                                                                                                                                                                          |                           |               |                          |                  |                 | bit   |

|              |                                                                                                                                                                                          |                           |               |                          |                  |                 |       |

| Legend:      |                                                                                                                                                                                          |                           |               |                          |                  |                 |       |

| R = Readat   |                                                                                                                                                                                          | W = Writable              |               |                          | nented bit, read |                 |       |

| -n = Value a | at POR                                                                                                                                                                                   | '1' = Bit is set          |               | '0' = Bit is cle         | ared             | x = Bit is unkr | nown  |

| bit 7        | ADFM: A/D R                                                                                                                                                                              | Result Format S           | elect bit     |                          |                  |                 |       |

|              | 1 = Right justi<br>0 = Left justifie                                                                                                                                                     |                           |               |                          |                  |                 |       |

| bit 6        | Unimplement                                                                                                                                                                              | ted: Read as '            | כ'            |                          |                  |                 |       |

| bit 5-3      | ACQT<2:0>:                                                                                                                                                                               | A/D Acquisition           | n Time Select | bits                     |                  |                 |       |

|              | $111 = 20 \text{ TAD}$ $110 = 16 \text{ TAD}$ $101 = 12 \text{ TAD}$ $100 = 8 \text{ TAD}$ $011 = 6 \text{ TAD}$ $010 = 4 \text{ TAD}$ $001 = 2 \text{ TAD}$ $000 = 0 \text{ TAD}^{(1)}$ |                           |               |                          |                  |                 |       |

| bit 2-0      | 111 = FRC (cl<br>110 = FOSC/6<br>101 = FOSC/1<br>100 = FOSC/4                                                                                                                            | 6<br>ock derived frc<br>2 | m A/D RC oso  | cillator) <sup>(1)</sup> |                  |                 |       |

#### REGISTER 23-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

# 23.2.2 A/D RESULT REGISTERS

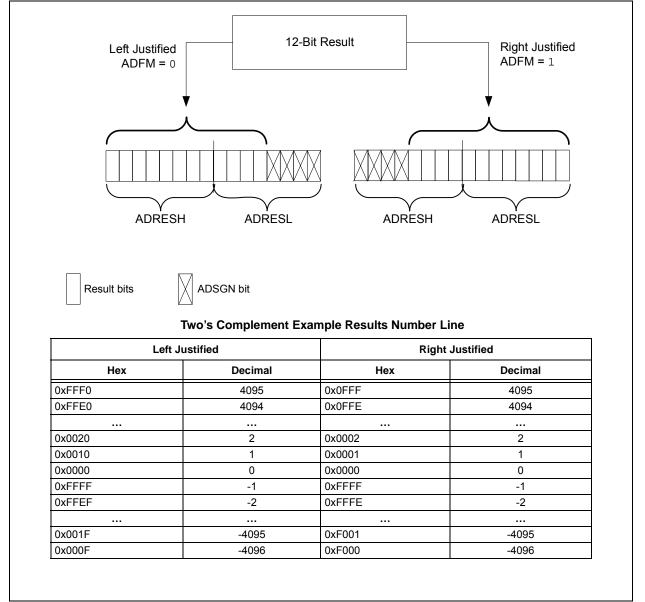

The ADRESH:ADRESL register pair is where the 12-bit A/D result and extended sign bits (ADSGN) are loaded at the completion of a conversion. This register pair is 16 bits wide. The A/D module gives the flexibility of left or right justifying the 12-bit result in the 16-Bit Result register. The A/D Format Select bit (ADFM) controls this justification.

Figure 23-3 shows the operation of the A/D result justification and location of the sign bit (ADSGN). The extended sign bits allow for easier 16-bit math to be

performed on the result. The results are represented as a two's compliment binary value. This means that when sign bits and magnitude bits are considered together in right justification, the ADRESH and ADRESL can be read as a single signed integer value.

When the A/D Converter is disabled, these 8-bit registers can be used as two general purpose registers.

# FIGURE 23-3: A/D RESULT JUSTIFICATION

# 23.7 A/D Conversions

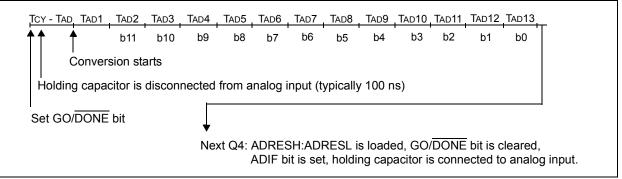

Figure 23-6 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

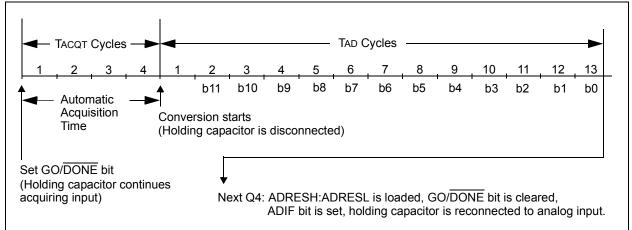

Figure 23-7 shows the operation of the A/D Converter after the GO/DONE bit has been set, the ACQT<2:0> bits set to '010' and a 4 TAD acquisition time selected.

Clearing the  $GO/\overline{DONE}$  bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD Wait is required before the next acquisition can be started. After this Wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

## FIGURE 23-6: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 23-7: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

# PIC18F87K90 FAMILY

#### 28.5.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Monitoring of the powermanaged clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the Oscillator Failure Interrupt Flag is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTOSC source.

#### 28.5.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is EC, RC or INTRC modes, monitoring can begin immediately following these events. For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (when the OST and PLL timers have timed out).

This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTOSC returns to its role as the FSCM source.

Note: The same logic that prevents false oscillator failure interrupts on POR, or wake from Sleep, also prevents the detection of the oscillator's failure to start at all following these events. This can be avoided by monitoring the OSTS bit and using a timing routine to determine if the oscillator is taking too long to start. Even so, no oscillator failure interrupt will be flagged.

As noted in **Section 28.4.1 "Special Considerations for Using Two-Speed Start-up"**, it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new powermanaged mode is selected, the primary clock is disabled.

# 31.3 DC Characteristics: PIC18F87K90 Family (Industrial/Extended) (Continued)

| DC CHA       | ARACTE | RISTICS                                     |           | erature -40° | $C \leq TA \leq$ | unless otherwise stated)<br>≤ +85°C for industrial<br>≤ +125°C for extended |

|--------------|--------|---------------------------------------------|-----------|--------------|------------------|-----------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                              | Min       | Max          | Units            | Conditions                                                                  |

|              | Vol    | Output Low Voltage                          |           |              |                  |                                                                             |

| D080         |        | I/O Ports:                                  |           |              |                  |                                                                             |

|              |        | PORTA,PORTB,PORTC                           | _         | 0.6          | V                | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                |

|              |        | PORTD, PORTE, PORTF,<br>PORTG, PORTH, PORTJ | _         | 0.6          | V                | IOL = 3.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                |

| D083         |        | OSC2/CLKO<br>(EC modes)                     | _         | 0.6          | V                | IOL = 1.6 mA, VDD = 5.5V,<br>-40°C to +125°C                                |

|              | Vон    | Output High Voltage <sup>(1)</sup>          |           |              |                  |                                                                             |

| D090         |        | I/O Ports:                                  |           |              |                  |                                                                             |

|              |        | PORTA,PORTB,PORTC                           | VDD - 0.7 | —            | V                | ІОн = -3 mA, VDD = 4.5V,<br>-40°C to +125°C                                 |

|              |        | PORTD, PORTE, PORTF,<br>PORTG, PORTH, PORTJ | VDD - 0.7 | —            | V                | ІОн = -2 mA, VDD = 4.5V,<br>-40°C to +125°C                                 |

| D092         |        | OSC2/CLKO<br>(INTOSC, EC modes)             | Vdd - 0.7 | —            | V                | ІОн = -1 mA, VDD = 5.5V,<br>-40°C to +125°C                                 |

|              |        | Capacitive Loading Specs<br>on Output Pins  |           |              |                  |                                                                             |

| D100         | COSC2  | OSC2 Pin                                    | _         | 20           | pF               | In HS mode when external<br>clock is used to drive OSC1                     |

| D101         | Сю     | All I/O Pins and OSC2                       | _         | 50           | pF               | To meet the AC Timing<br>Specifications                                     |

| D102         | Св     | SCLx, SDAx                                  | _         | 400          | pF               | I <sup>2</sup> C™ Specification                                             |

**Note 1:** Negative current is defined as current sourced by the pin.

# 31.4 DC Characteristics: CTMU Current Source Specifications

| DC CH        | ARACT | ERISTICS                           |     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |       |                    |  |  |

|--------------|-------|------------------------------------|-----|------------------------------------------------------|-----|-------|--------------------|--|--|

| Param<br>No. | Sym   | Characteristic                     | Min | Typ <sup>(1)</sup>                                   | Max | Units | Conditions         |  |  |

|              | IOUT1 | CTMU Current Source,<br>Base Range | _   | 550                                                  |     | nA    | CTMUICON<1:0> = 01 |  |  |

|              | IOUT2 | CTMU Current Source,<br>10x Range  | —   | 5.5                                                  | _   | μA    | CTMUICON<1:0> = 10 |  |  |

|              | IOUT3 | CTMU Current Source,<br>100x Range | —   | 55                                                   | _   | μA    | CTMUICON<1:0> = 11 |  |  |

**Note 1:** Nominal value at center point of current trim range (CTMUICON<7:2> = 000000).

# TABLE 31-25: A/D CONVERTER CHARACTERISTICS: PIC18F87K90 FAMILY (INDUSTRIAL/EXTENDED)

| Param<br>No. | Sym           | Characteristic                                       | Min        | Тур | Мах        | Units    | Conditions                                               |

|--------------|---------------|------------------------------------------------------|------------|-----|------------|----------|----------------------------------------------------------|

| A01          | NR            | Resolution                                           | -          |     | 12         | bit      | $\Delta V \text{REF} \ge 5.0 V$                          |

| A03          | EIL           | Integral Linearity Error                             | _          | ±1  | ±6.0       | LSB      | ΔVREF = 5.0V                                             |

| A04          | Edl           | Differential Linearity Error                         | _          | ±1  | +3.0/-1.0  | LSB      | ΔVREF = 5.0V                                             |

| A06          | EOFF          | Offset Error                                         | _          | ±1  | ±9.0       | LSB      | ΔVREF = 5.0V                                             |

| A07          | Egn           | Gain Error                                           | _          | ±1  | ±8.0       | LSB      | ΔVREF = 5.0V                                             |

| A10          | _             | Monotonicity <sup>(1)</sup>                          | _          | _   | _          | _        | $VSS \le VAIN \le VREF$                                  |

| A20          | $\Delta VREF$ | Reference Voltage Range<br>(VREFH – VREFL)           | 3          | _   | Vdd - Vss  | V        |                                                          |

| A21          | Vrefh         | Reference Voltage High                               | Vss + 3.0V | _   | VDD + 0.3V | V        |                                                          |

| A22          | Vrefl         | Reference Voltage Low                                | Vss – 0.3V | _   | Vdd - 3.0V | V        |                                                          |

| A25          | VAIN          | Analog Input Voltage                                 | VREFL      | _   | VREFH      | V        |                                                          |

| A30          | Zain          | Recommended<br>Impedance of Analog<br>Voltage Source | _          | _   | 2.5        | kΩ       |                                                          |

| A50          | IREF          | VREF Input Current <sup>(2)</sup>                    |            | _   | 5<br>150   | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D conversion cycle. |

Note 1: The A/D conversion result never decreases with an increase in the input voltage.

2: VREFH current is from the RA3/AN3/VREF+ pin or VDD, whichever is selected as the VREFH source. VREFL current is from the RA2/AN2/VREF-/CVREF pin or VSs, whichever is selected as the VREFL source.

#### TABLE B-1: NOTABLE DIFFERENCES BETWEEN PIC18F87K90, PIC18F87J90 AND PIC18F85J90 FAMILIES

| FAMILIES                             |                                                                         | r                                       |                                         |

|--------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|

| Characteristic                       | PIC18F87K90 Family                                                      | PIC18F87J90 Family                      | PIC18F85J90 Family                      |

| Max Operating Frequency              | 64 MHz                                                                  | 48 MHz                                  | 40 MHz                                  |

| Max Program Memory                   | 128 Kbytes                                                              | 128 Kbytes                              | 32 Kbytes                               |

| Data Memory                          | 4 Kbytes                                                                | 4 Kbytes                                | 2 Kbytes                                |

| Program Memory Endurance             | 10,000 Write/Erase<br>(minimum)                                         | 10,000 Write/Erase<br>(minimum)         | 1,000 Write/Erase<br>(minimum)          |

| Single-Word Write for Flash          | Yes                                                                     | Yes                                     | No                                      |

| Oscillator Options                   | PLL can be used with<br>INTOSC                                          | Yes                                     | PLL cannot be used with<br>INTOSC       |

| СТМИ                                 | Yes                                                                     | Yes                                     | No                                      |

| RTCC                                 | Yes                                                                     | Yes                                     | No                                      |

| SOSC Oscillator Options              | Low-power oscillator option<br>for SOSC                                 | Low-power oscillator option<br>for SOSC | No                                      |

| TICKI Clock                          | T1CKI can be used as a<br>clock without enabling the<br>SOSC oscillator | No                                      | No                                      |

| INTOSC                               | Up to 16 MHz                                                            | 8 MHz                                   | 8 MHz                                   |

| SPI/I <sup>2</sup> C™                | 2                                                                       | 1                                       | 1                                       |

| Timers                               | 11                                                                      | 4                                       | 4                                       |

| ECCP                                 | 3                                                                       | No                                      | No                                      |

| ССР                                  | 7                                                                       | 2                                       | 2                                       |

| Data EEPROM                          | Yes                                                                     | No                                      | No                                      |

| Programmable BOR                     | Multiple level of BOR                                                   | No                                      | No                                      |

| WDT Prescale Options                 | 22                                                                      | 16                                      | 16                                      |

| 5V Operation                         | Yes                                                                     | No                                      | No                                      |

| nanoWatt XLP                         | Yes                                                                     | No                                      | No                                      |

| Regulator                            | Yes                                                                     | Yes                                     | Yes                                     |

| Low-Power BOR                        | Yes                                                                     | No                                      | No                                      |

| ADC                                  | 24-Channel<br>Differential (12-bit)                                     | 12-Channel<br>Not differential (10-bit) | 12-Channel<br>Not Differential (10-bit) |

| Internal Temperature Sensor          | Yes                                                                     | No                                      | No                                      |

| Programmable HLVD                    | Yes                                                                     | No                                      | No                                      |

| EUSART                               | 2 EUSARTs                                                               | 1 EUSART, 1 AUSART                      | 1 EUSART, 1 AUSART                      |

| Comparators                          | 3                                                                       | 2                                       | 2                                       |

| Oscillator Options                   | 14 options by OSC<3:0>                                                  | 8 options by OSC<3:0>                   | 8 options by OSC<3:0>                   |

| Ultra Low-Power Wake-up<br>(ULPW)    | Yes                                                                     | No                                      | No                                      |

| Power-up Timer                       | Yes                                                                     | No                                      | No                                      |

| MCLR Pin as Input Port               | Yes                                                                     | No                                      | No                                      |

| LCD Charge Pump                      | No                                                                      | Yes                                     | Yes                                     |

| Internal Resistor Ladder for Biasing | Yes                                                                     | No                                      | No                                      |

# PIC18F87K90 FAMILY

| Core Features                              |     |

|--------------------------------------------|-----|

| Easy Migration                             | 9   |

| Extended Instruction Set                   | 9   |

| Memory Options                             | 9   |

| nanoWatt Technology                        | 9   |

| Oscillator Options and Features            | 9   |

| CPFSEQ                                     |     |

| CPFSGT                                     |     |

| CPFSLT                                     |     |

| Crystal Oscillator/Ceramic Resonators (HS) |     |

| Customer Change Notification Service       | 566 |

| Customer Notification Service              | 566 |

| Customer Support                           |     |

|                                            |     |

# D

| Data Addressing Modes                     | 104 |

|-------------------------------------------|-----|

| Comparing Addressing Modes (Bit-Oriented, |     |

| Byte Oriented) with the Extended          |     |

| Instruction Set Enabled                   |     |

| Direct                                    | 104 |

| Indexed Literal Offset                    |     |

| BSR                                       |     |

| Mapping Access Bank                       |     |

| Indirect                                  |     |

| Inherent and Literal                      | 104 |

| Data EEPROM Memory                        |     |

| Associated Registers                      |     |

| EEADR and EEADRH Registers                |     |

| EECON1 and EECON2 Registers               |     |

| Operation During Code-Protect             |     |

| Overview                                  |     |

| Protection, Spurious Writes               | 124 |

| Reading                                   |     |

| Usage                                     |     |

| Write Verify                              |     |

| Writing To                                |     |

| Data Memory                               |     |

| Access Bank<br>Bank Select Register (BSR) |     |

| Extended Instruction Set                  |     |

| General Purpose Registers                 |     |

| Memory Maps                               |     |

| PIC18FX5K90/X7K90 Devices                 | 03  |

| Special Function Registers                |     |

| Special Function Registers                |     |

| Data Memory Modes                         |     |

| Indexed Literal Offset                    | 107 |

| Affected Instructions                     |     |

| DAW                                       |     |

| DC Characteristics                        |     |

| CTMU Current Source                       | 520 |

| PIC18F87K90 Family, Industrial            |     |

| Power-Down and Supply Current             | 508 |

| Supply Voltage                            |     |

| DCFSNZ                                    | 471 |

| DECF                                      |     |

| DECFSZ                                    |     |

| Default System Clock                      |     |

| Details on Individual Family Members      | 10  |

| Development Support                       | 501 |

| Device Overview                           |     |

| Features (64-Pin Devices)                 |     |

| Features (80-Pin Devices)                 |     |

| Direct Addressing                         | 105 |

#### Е

| Effect on Standard PIC18 Instructions                | 100 |

|------------------------------------------------------|-----|

| Effects of Power-Managed Modes on Various            | 490 |

| Clock Sources                                        | 52  |

| Electrical Characteristics                           |     |

| Enhanced Capture/Compare/PWM (ECCP)                  |     |

| Capture Mode. See Capture.                           |     |

| Compare Mode. See Compare.                           |     |

| ECCP Mode and Timer Resources                        |     |

| Enhanced PWM Mode                                    |     |

| Auto-Restart                                         |     |

| Auto-Shutdown                                        | 264 |

| Direction Change in Full-Bridge                      | 262 |

| Output Mode                                          |     |

| Full-Bridge Application<br>Full-Bridge Mode          |     |

| Half-Bridge Application                              |     |

| Half-Bridge Application Examples                     |     |

| Half-Bridge Mode                                     |     |

| Output Relationships (Active-High and                | 200 |

| Active-Low)                                          | 258 |

| Output Relationships Diagram                         |     |

| Programmable Dead-Band Delay                         |     |

| Shoot-Through Current                                |     |

| Start-up Considerations                              | 264 |

| Outputs and Configuration                            |     |

| Enhanced Capture/Compare/PWM (ECCP1/2/3)             |     |

| Associated Registers                                 | 272 |

| Enhanced Universal Synchronous Asynchronous Received | er  |

| Transmitter (EUSART). See EUSART.                    |     |

| Equations                                            |     |

| 16 x 16 Signed Multiplication Algorithm              |     |

| 16 x 16 Unsigned Multiplication Algorithm            |     |

| A/D Acquisition Time                                 |     |

| A/D Minimum Charging Time                            | 384 |

| Calculating the Minimum Required                     |     |

| Acquisition Time                                     |     |

| Converting Error Pulses                              | 232 |

| Asynchronous Mode                                    | 350 |

| 12-Bit Break Transmit and Receive                    | 000 |

| Sequence                                             | 366 |

| Associated Registers, Receive                        |     |

| Associated Registers, Transmit                       |     |

| Auto-Wake-up on Sync Break                           |     |

| Receiver                                             |     |

| Setting Up 9-Bit Mode with Address Detect            | 362 |

| Transmitter                                          |     |

| Baud Rate Generator                                  |     |

| Operation in Power-Managed Modes                     |     |

| Baud Rate Generator (BRG)                            |     |

| Associated Registers                                 |     |

| Auto-Baud Rate Detect                                |     |

| Baud Rate Error, Calculating                         |     |

| Baud Rates, Asynchronous Modes                       |     |

| High Baud Rate Select (BRGH Bit)                     |     |

| Sampling                                             |     |

| Synchronous Master Mode                              |     |

| Associated Registers, Receive                        |     |

| Associated Registers, Transmit                       |     |

| Reception<br>Transmission                            |     |

| 1101151111551011                                     | 307 |