Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k90-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2009

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009-2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-61341-351-7

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

| Din Nama                                            | Pin Number | Pin                    | Buffer                                 | Description                                                                                                                                                       |

|-----------------------------------------------------|------------|------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | QFN/TQFP   | Туре                   | Туре                                   | Description                                                                                                                                                       |

|                                                     |            |                        |                                        | PORTC is a bidirectional I/O port.                                                                                                                                |

| RC0/SOSCO/SCLKI<br>RC0<br>SOSCO<br>SCLKI            | 30         | I/O<br>O<br>I          | ST<br>—<br>ST                          | Digital I/O.<br>SOSC oscillator output.<br>Digital SOSC input.                                                                                                    |

| RC1/SOSCI/ECCP2/P2A/<br>SEG32<br>RC1                | 29         | I/O                    | ST                                     | Digital I/O.                                                                                                                                                      |

| SOSCI<br>ECCP2 <sup>(1)</sup><br>P2A<br>SEG32       |            | I<br>I/O<br>O<br>O     | CMOS<br>ST<br>—<br>Analog              | SOSC oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>Enhanced PWM2 Output A.<br>SEG32 output for LCD.                                       |

| RC2/ECCP1/P1A/SEG13<br>RC2<br>ECCP1<br>P1A<br>SEG13 | 33         | I/O<br>I/O<br>O<br>O   | ST<br>ST<br>—<br>Analog                | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Enhanced PWM1 Output A.<br>SEG13 output for LCD.                                                 |

| RC3/SCK1/SCL1/SEG17<br>RC3<br>SCK1<br>SCL1<br>SEG17 | 34         | I/O<br>I/O<br>I/O<br>O | ST<br>ST<br>I <sup>2</sup> C<br>Analog | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode.<br>SEG17 output for LCD. |

| RC4/SDI1/SDA1/SEG16<br>RC4<br>SDI1<br>SDA1<br>SEG16 | 35         | I/O<br>I<br>I/O<br>O   | ST<br>ST<br>I <sup>2</sup> C<br>Analog | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.<br>SEG16 output for LCD.                                                                               |

| RC5/SDO1/SEG12<br>RC5<br>SDO1<br>SEG12              | 36         | I/O<br>O<br>O          | ST<br><br>Analog                       | Digital I/O.<br>SPI data out.<br>SEG12 output for LCD.                                                                                                            |

| RC6/TX1/CK1/SEG27<br>RC6<br>TX1<br>CK1<br>SEG27     | 31         | I/O<br>O<br>I/O<br>O   | ST<br>—<br>ST<br>Analog                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX1/DT1).<br>SEG27 output for LCD.                                         |

| RC7/RX1/DT1/SEG28<br>RC7<br>RX1<br>DT1<br>SEG28     | 32         | I/O<br>I<br>I/O<br>O   | ST<br>ST<br>ST<br>Analog               | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX1/CK1).<br>SEG28 output for LCD.                                           |

| -                                                   |            |                        |                                        | CMOS = CMOS compatible input or output                                                                                                                            |

#### TABLE 1-3: PIC18F6XK90 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

**2:** Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K90 and PIC18F85K90 devices.

| R/W-0        | R/W-0                                                           | R/W-0             | R/W-0                     | R/W-0             | R/W-0            | R/W-0           | R/W-0         |  |  |

|--------------|-----------------------------------------------------------------|-------------------|---------------------------|-------------------|------------------|-----------------|---------------|--|--|

| INTSRC       | PLLEN                                                           | TUN5              | TUN4                      | TUN3              | TUN2             | TUN1            | TUN0          |  |  |

| bit 7        |                                                                 |                   |                           |                   |                  |                 | bit 0         |  |  |

|              |                                                                 |                   |                           |                   |                  |                 |               |  |  |

| Legend:      |                                                                 |                   |                           |                   |                  |                 |               |  |  |

| R = Readab   | le bit                                                          | W = Writable      | bit                       | U = Unimplen      | nented bit, rea  | d as '0'        |               |  |  |

| -n = Value a | t POR                                                           | '1' = Bit is set  |                           | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |  |  |

|              |                                                                 |                   |                           |                   |                  |                 |               |  |  |

| bit 7        | t 7 INTSRC: Internal Oscillator Low-Frequency Source Select bit |                   |                           |                   |                  |                 |               |  |  |

|              | 1 = 31.25 kHz                                                   | z device clock is | derived from <sup>2</sup> | 16 MHz INTOSC     | source (divide   | -by-512 enabled | d, HF-INTOSC) |  |  |

|              | 0 = 31 kHz de                                                   | evice clock is d  | lerived from IN           | ITRC 31 kHz os    | cillator (LF-IN  | TOSC)           |               |  |  |

| bit 6        | PLLEN: Freq                                                     | uency Multiplie   | r PLL Enable              | bit               |                  |                 |               |  |  |

|              | 1 = PLL is en                                                   | abled             |                           |                   |                  |                 |               |  |  |

|              | 0 = PLL is dis                                                  | sabled            |                           |                   |                  |                 |               |  |  |

| bit 5-0      | TUN<5:0>: Fa                                                    | ast RC Oscillat   | or (INTOSC) F             | Frequency Tunir   | ng bits          |                 |               |  |  |

|              | 011111 <b>= Ma</b>                                              | ximum frequer     | псу                       |                   |                  |                 |               |  |  |

|              | •                                                               |                   |                           |                   |                  |                 |               |  |  |

|              | •                                                               |                   |                           |                   |                  |                 |               |  |  |

|              | 000001                                                          |                   |                           |                   |                  |                 |               |  |  |

|              | 000000 = Ce<br>111111                                           | nter frequency.   | Fast RC osci              | llator is running | at the calibrate | ed frequency.   |               |  |  |

|              | •                                                               |                   |                           |                   |                  |                 |               |  |  |

|              | •                                                               |                   |                           |                   |                  |                 |               |  |  |

|              | 100000 <b>= M</b> ir                                            | nimum frequen     | су                        |                   |                  |                 |               |  |  |

#### REGISTER 3-3: OSCTUNE: OSCILLATOR TUNING REGISTER

#### 3.3 Clock Sources and Oscillator Switching

Essentially, PIC18F87K90 family devices have these independent clock sources:

- Primary oscillators

- · Secondary oscillators

- Internal oscillator

The **primary oscillators** can be thought of as the main device oscillators. These are any external oscillators connected to the OSC1 and OSC2 pins, and include the External Crystal and Resonator modes and the External Clock modes. If selected by the OSC<3:0> Configuration bits (CONFIG1H<3:0>), the internal oscillator block may be considered a primary oscillator. The internal oscillator block can be one of the following:

- 31 kHz LF-INTRC source

- 31 kHz to 500 kHz MF-INTOSC source

- · 31 kHz to 16 MHz HF-INTOSC source

The particular mode is defined by the OSC Configuration bits. The details of these modes are covered in Section 3.4 "External Oscillator Modes".

The **secondary oscillators** are external clock sources that are not connected to the OSC1 or OSC2 pin. These sources may continue to operate, even after the controller is placed in a power-managed mode. PIC18F87K90 family devices offer the SOSC (Timer1/3/5/7) oscillator as a secondary oscillator source. This oscillator, in all power-managed modes, is often the time base for functions, such as a Real-Time Clock (RTC).

The SOSCEN bit in the corresponding timer should be set correctly for the enabled SOSC. The SOSCEL<1:0> bits (CONFIG1L<4:3>) decide the SOSC mode of operation:

- 11 = High-power SOSC circuit

- 10 = Digital (SCLKI) mode

- 01 = Low-power SOSC circuit

In addition to being a primary clock source in some circumstances, the **internal oscillator** is available as a power-managed mode clock source. The LF-INTOSC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor. The internal oscillator block is discussed in more detail in Section 3.6 "Internal Oscillator Block".

The PIC18F87K90 family includes features that allow the device clock source to be switched from the main oscillator, chosen by device configuration, to one of the alternate clock sources. When an alternate clock source is enabled, various power-managed operating modes are available.

### 4.6 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

#### 4.6.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle or Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCONx or PIEx registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/ GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see **Section 10.0 "Interrupts"**).

#### 4.6.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 28.2 "Watchdog Timer (WDT)").

Executing a SLEEP or CLRWDT instruction clears the WDT timer and postscaler, loses the currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifies the IRCF bits in the OSCCON register (if the internal oscillator block is the device clock source).

#### 4.6.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the HFIOFS/MFIOFS bits are set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up, and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 4-4.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 28.4 "Two-Speed Start-up") or Fail-Safe Clock Monitor (see Section 28.5 "Fail-Safe Clock Monitor") is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer, driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

#### 4.6.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. The two cases are:

- When in PRI\_IDLE mode, where the primary clock source is not stopped

- When the primary clock source is not any of the LP, XT, HS or HSPLL modes

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval, TCSD, following the wake event, is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

# TABLE 6-1: PIC18F87K90 FAMILY SPECIAL FUNCTION REGISTER MAP<sup>(5)</sup> (CONTINUED)

| Addr. | Name                  | Addr. | Name                  | Addr. | Name     | Addr. | Name    | Addr. | Name     | Addr. | Name                  |

|-------|-----------------------|-------|-----------------------|-------|----------|-------|---------|-------|----------|-------|-----------------------|

| F3Eh  | TMR7L <sup>(4)</sup>  | F31h  | PR12 <sup>(4)</sup>   | F24h  | ANCON1   | F17h  | PMD2    | F0Ah  | CCPR6L   | EFDh  | LCDREF                |

| F3Dh  | T7CON <sup>(4)</sup>  | F30h  | T12CON <sup>(4)</sup> | F23h  | ANCON2   | F16h  | PMD3    | F09h  | CCP6CON  | EFCh  | LCDRL                 |

| F3Ch  | T7GCON <sup>(4)</sup> | F2Fh  | CM2CON                | F22h  | RCSTA2   | F15h  | TMR5H   | F08h  | CCPR7H   | EFBh  | LCDSE5 <sup>(3)</sup> |

| F3Bh  | TMR6                  | F2Eh  | CM3CON                | F21h  | TXSTA2   | F14h  | TMR5L   | F07h  | CCPR7L   | EFAh  | LCDSE4                |

| F3Ah  | PR6                   | F2Dh  | CCPTMRS0              | F20h  | BAUDCON2 | F13h  | T5CON   | F06h  | CCP7CON  | EF9h  | LCDSE3                |

| F39H  | T6CON                 | F2Ch  | CCPTMRS1              | F1Fh  | SPBRGH2  | F12h  | T5GCON  | F05h  | TMR4     | EF8h  | LCDSE2                |

| F38h  | TMR8                  | F2Bh  | CCPTMRS2              | F1Eh  | SPBRG2   | F11h  | CCPR4H  | F04h  | PR4      | EF7h  | LCDSE1                |

| F37h  | PR8                   | F2Ah  | REFOCON               | F1Dh  | RCREG2   | F10h  | CCPR4L  | F03h  | T4CON    | EF6h  | LCDSE0                |

| F36h  | T8CON                 | F29H  | ODCON1                | F1Ch  | TXREG2   | F0Fh  | CCP4CON | F02h  | SSP2BUF  | EF5h  | LCDPS                 |

| F35h  | TMR10 <sup>(4)</sup>  | F28h  | ODCON2                | F1Bh  | PSTR2CON | F0Eh  | CCPR5H  | F01h  | SSP2ADD  | EF4h  | LCDCON                |

| F34h  | PR10 <sup>(4)</sup>   | F27h  | ODCON3                | F1Ah  | PSTR3CON | F0Dh  | CCPR5L  | F00h  | SSP2STAT |       |                       |

| F33h  | T10CON <sup>(4)</sup> | F26h  |                       | F19h  | PMD0     | F0Ch  | CCP5CON | EFFh  | SSP2CON1 | ]     |                       |

**Note 1:** This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available in 64-pin devices (PIC18F6XK90).

4: This register is not available in devices with a program memory of 32 Kbytes (PIC18FX5K90).

5: Addresses, EF4h through F5Fh, are also used by SFRs, but are not part of the Access RAM. Users must always load the proper BSR value to access these registers.

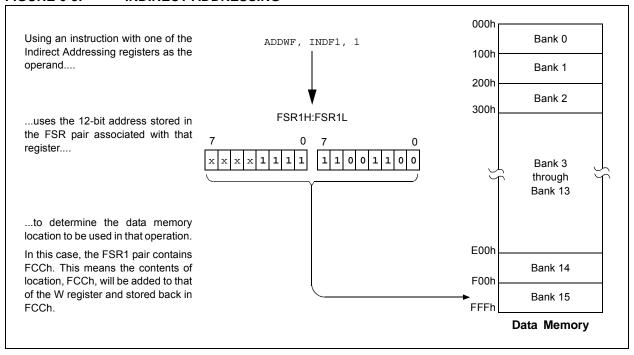

# 6.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers: FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers. The operands

# FIGURE 6-8: INDIRECT ADDRESSING

are mapped in the SFR space, but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L.

Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

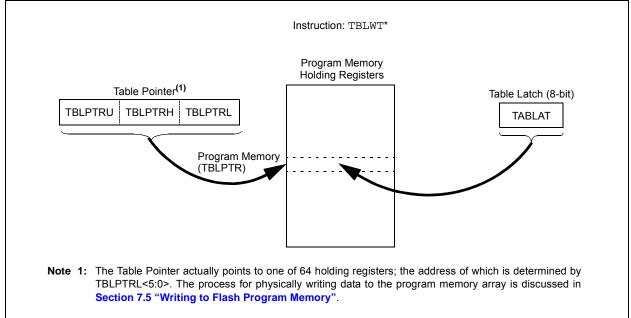

### FIGURE 7-2: TABLE WRITE OPERATION

## 7.2 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- · EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register, not a physical register, is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access is a program or data EEPROM memory access. When clear, any subsequent operations operate on the data EEPROM memory. When set, any subsequent operations operate on the program memory.

The CFGS control bit determines if the access is to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations operate on Configuration registers regardless of EEPGD (see Section 28.0 "Special Features of the CPU"). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, allows a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, allows a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit (PIR6<4>) is set when the write is complete. It must be cleared in software.

| FIGURE 13-7:               | TIMER1 GATE SINGLE                                         | E PULSE AND TOGGLE COMBI                       | NED MODE                                         |

|----------------------------|------------------------------------------------------------|------------------------------------------------|--------------------------------------------------|

| TMR1GE                     |                                                            |                                                |                                                  |

| T1GPOL                     |                                                            |                                                |                                                  |

| T1GSPM                     |                                                            |                                                |                                                  |

| T1GT <u>M</u>              |                                                            |                                                |                                                  |

| T1GGO/<br>T1DONE<br>T1G_IN | ✓ Set by Software<br>Counting Enabled<br>Rising Edge of T1 | on<br>G                                        | Cleared by Hardware on<br>Falling Edge of T1GVAL |

| Т1СКІ                      |                                                            |                                                |                                                  |

| T1GVAL                     |                                                            |                                                |                                                  |

| Timer1                     | Ν                                                          | N + 1 N + 2 N + 3                              | N + 4                                            |

| RTCCIF                     | — Cleared by Software                                      | Set by Hardware on<br>Falling Edge of T1GVAL — | Cleared by Software                              |

### TABLE 13-5: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name     | Bit 7                       | Bit 6         | Bit 5   | Bit 4    | Bit 3            | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|----------|-----------------------------|---------------|---------|----------|------------------|---------|---------|---------|-----------------------------|

| INTCON   | GIE/GIEH                    | PEIE/GIEL     | TMR0IE  | INT0IE   | RBIE             | TMR0IF  | INT0IF  | RBIF    | 75                          |

| PIR1     | _                           | ADIF          | RC1IF   | TX1IF    | SSP1IF           | TMR1GIF | TMR2IF  | TMR1IF  | 77                          |

| PIE1     | _                           | ADIE          | RC1IE   | TX1IE    | SSP1IE           | TMR1GIE | TMR2IE  | TMR1IE  | 77                          |

| IPR1     | _                           | ADIP          | RC1IP   | TX1IP    | SSP1IP           | TMR1GIP | TMR2IP  | TMR1IP  | 77                          |

| TMR1L    | 1L Timer1 Register Low Byte |               |         |          |                  |         |         |         |                             |

| TMR1H    | Timer1 Reg                  | gister High B | yte     |          |                  |         |         |         | 76                          |

| T1CON    | TMR1CS1                     | TMR1CS0       | T1CKPS1 | T1CKPS0  | SOSCEN           | T1SYNC  | RD16    | TMR10N  | 76                          |

| T1GCON   | TMR1GE                      | T1GPOL        | T1GTM   | T1GSPM   | T1GGO/<br>T1DONE | T1GVAL  | T1GSS1  | T1GSS0  | 77                          |

| OSCCON2  | —                           | SOSCRUN       | _       | —        | SOSCGO           | —       | MFIOFS  | MFIOSEL | 79                          |

| CCPTMRS0 | C3TSEL1                     | C3TSEL0       | C2TSEL2 | C2TSEL1  | C2TSEL0          | C1TSEL2 | C1TSEL1 | C1TSEL0 | 81                          |

| CCPTMRS1 | C7TSEL1                     | C7TSEL0       | _       | C6TSEL0  | _                | C5TSEL0 | C4TSEL1 | C4TSEL0 | 81                          |

| CCPTMRS2 |                             | _             | _       | C10TSEL0 | _                | C9TSEL0 | C8TSEL1 | C8TSEL0 | 81                          |

Legend: Shaded cells are not used by the Timer1 module.

$<sup>\</sup>ensuremath{\textcircled{}^\circ}$  2009-2011 Microchip Technology Inc.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 TMRxCS1 TMRxCS0 TxCKPS1 TxCKPS0 SOSCEN TxSYNC **RD16 TMRxON** bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 7-6 TMRxCS<1:0>: Timerx Clock Source Select bits 10 = The Timer1 clock source is either a pin or an oscillator depending on the SOSCEN bit. SOSCEN = 0: External clock is from the T1CKI pin (on the rising edge). SOSCEN = 1: Crystal oscillator is on the SOSCI/SOSCO pins. 01 = Timerx clock source is the system clock (Fosc)<sup>(1)</sup> 00 = Timerx clock source is the instruction clock (Fosc/4) bit 5-4 TxCKPS<1:0>: Timerx Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value SOSCEN: SOSC Oscillator Enable bit bit 3 1 = SOSC is enabled for Timerx (based on SOSCSEL fuses) 0 = SOSC is disabled for Timerx bit 2 TxSYNC: Timerx External Clock Input Synchronization Control bit (Not usable if the device clock comes from Timer1/Timer3.) When TMRxCS<1:0> = 10: 1 = Do not synchronize external clock input 0 = Synchronize external clock input When TMRxCS<1:0> = 0x: This bit is ignored; Timer3 uses the internal clock. bit 1 RD16: 16-Bit Read/Write Mode Enable bit 1 = Enables register read/write of Timerx in one 16-bit operation 0 = Enables register read/write of Timerx in two 8-bit operations bit 0 TMRxON: Timerx On bit 1 =Enables Timerx 0 = Stops Timerx

#### REGISTER 15-1: TxCON: TIMER3/5/7 CONTROL REGISTER

**Note 1:** The Fosc clock source should not be selected if the timer will be used with the ECCP capture/compare features.

# 18.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F87K90 family devices have seven CCP (Capture/Compare/PWM) modules, designated CCP4 through CCP10. All the modules implement standard Capture, Compare and Pulse-Width Modulation (PWM) modes.

**Note:** Throughout this section, generic references are used for register and bit names that are the same, except for an 'x' variable that indicates the item's association with the specific CCP module. For example, the control register is named CCPxCON and refers to CCP4CON through CCP10CON.

Each CCP module contains a 16-bit register that can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operation in the following sections is described with respect to CCP4, but is equally applicable to CCP5 through CCP10.

Note: The CCP9 and CCP10 modules are disabled on the devices with 32 Kbytes of program memory (PIC18FX5K90).

# REGISTER 18-1: CCPxCON: CCPx CONTROL REGISTER (CCP4-CCP10 MODULES)<sup>(1)</sup>

| U-0        | U-0                              | R/W-0                    | R/W-0           | R/W-0                                   | R/W-0            | R/W-0           | R/W-0                    |

|------------|----------------------------------|--------------------------|-----------------|-----------------------------------------|------------------|-----------------|--------------------------|

| _          | —                                | DCxB1                    | DCxB0           | CCPxM3                                  | CCPxM2           | CCPxM1          | CCPxM0                   |

| bit 7      |                                  |                          |                 |                                         |                  | ·               | bit 0                    |

| Legend:    |                                  |                          |                 |                                         |                  |                 |                          |

| R = Read   | able bit                         | W = Writable             | bit             | U = Unimplen                            | nented bit, rea  | d as '0'        |                          |

| -n = Value | e at POR                         | '1' = Bit is set         |                 | '0' = Bit is clea                       | ared             | x = Bit is unkr | nown                     |

| bit 7-6    | Unimplemen                       | ted: Read as '           | )'              |                                         |                  |                 |                          |

| bit 5-4    | DCxB<1:0>:                       | PWM Duty Cyc             | le for CCPx N   | lodule bits (bit 1                      | , bit 0)         |                 |                          |

|            | Capture mod                      | <u>e:</u>                |                 |                                         |                  |                 |                          |

|            | Unused.                          |                          |                 |                                         |                  |                 |                          |

|            | Compare mo                       | <u>de</u> :              |                 |                                         |                  |                 |                          |

|            | Unused.                          |                          |                 |                                         |                  |                 |                          |

|            | <u>PWM mode:</u>                 | a tha two I agat         | Cignificant bit | o (hit 1 and hit (                      | )) of the 10 bit | DW/M duty ava   | la Tha aight             |

|            |                                  |                          |                 | s (bit 1 and bit (<br>uty cycle are for |                  |                 | ie. The eight            |

| bit 3-0    | •                                | : CCPx Module            |                 |                                         |                  |                 |                          |

|            | 0000 = Cap                       | ture/Compare/F           | WM disabled     | (resets CCPx n                          | nodule)          |                 |                          |

|            | 0001 = Rese                      |                          |                 |                                         |                  |                 |                          |

|            |                                  |                          | gle output on   | match (CCPxIF                           | bit is set)      |                 |                          |

|            | 0011 = Res                       | ervea<br>ture mode: evei | a, falling adga |                                         |                  |                 |                          |

|            |                                  | ture mode: even          |                 |                                         |                  |                 |                          |

|            |                                  | ture mode: ever          |                 | lae                                     |                  |                 |                          |

|            |                                  | ture mode: ever          |                 |                                         |                  |                 |                          |

|            | 1000 = Com<br>is se              | ·                        | ialize CCPx p   | in low; on comp                         | are match, for   | ce CCPx pin hi  | gh (CCPxIF bit           |

|            | 1001 = Com<br>is se              | •                        | ialize CCPx p   | in high; on com                         | pare match, fo   | rce CCPx pin lo | ow (CCPxIF bit           |

|            | 1010 = Com                       | ,                        | nerate softwa   | re interrupt on c                       | ompare match     | (CCPxIF bit is  | set, CCPx pin            |

|            |                                  | npare mode: Sp           | ecial Event Tr  | igger; reset time                       | er on CCPx ma    | atch (CCPxIF bi | t is set) <sup>(2)</sup> |

| Note 1:    | The CCP9 and C<br>(PIC18FX5K90). |                          | are not availa  | ble on devices                          | with 32 Kbytes   | of program me   | emory                    |

2: CCPxM<3:0> = 1011 will only reset the timer and not start the A/D conversion on a CCPx match.

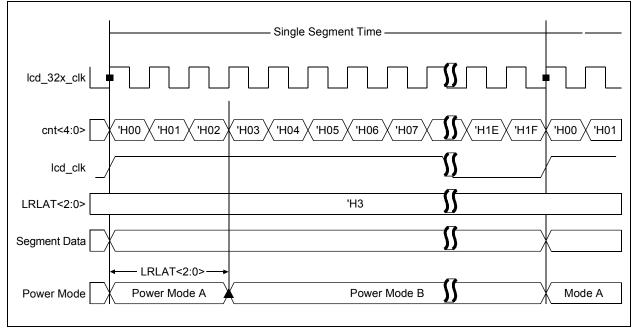

There are two power modes designated as "Mode A" and "Mode B". Mode A is set by the bits, LRLAP<1:0> and Mode B by LRLB<1:0>. The resistor ladder to use for Modes A and B are selected by the bits, LRLAP<1:0> and LRLBP<1:0>, respectively

Each ladder has a matching contrast control ladder, tuned to the nominal resistance of the reference ladder. This contrast control resistor can be controlled by LCDREF<5:3> (LCDCST<2:0>). Disabling the internal reference ladder results in all of the ladders being disconnected, allowing external voltages to be supplied.

To get additional current in High-Power mode, when LCDRL<7:6> (LRLAP<1:0>) = 11, both the medium and high-power resistor ladders are activated.

Whenever the LCD module is inactive (LCDA (LCDPS < 5>) = 0), the reference ladder will be turned off.

#### 20.3.2.1 Automatic Power Mode Switching

As an LCD segment is electrically only a capacitor, current is drawn only during the interval when the voltage is switching. To minimize total device current, the LCD reference ladder can be operated in a different power mode for the transition portion of the duration. This is controlled by the LCDRL register.

Mode A Power mode is active for a programmable time, beginning at the time when the LCD segment waveform is transitioning. The LCDRL<2:1> (LRLAT<2:0>) bits select how long, or if the Mode A is active. Mode B Power mode is active for the remaining time before the segments or commons change again.

As shown in Figure 20-5, there are 32 counts in a single segment time. Type-A can be chosen during the time when the wave form is in transition. Type-B can be used when the clock is stable or not in transition.

By using this feature of automatic power switching, using Type-A/Type-B, the power consumption can be optimized for a given contrast.

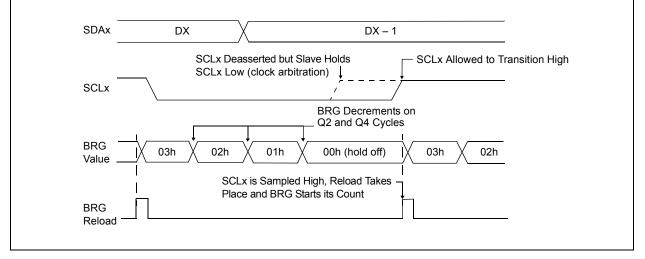

#### 21.4.7.2 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the

SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 21-20).

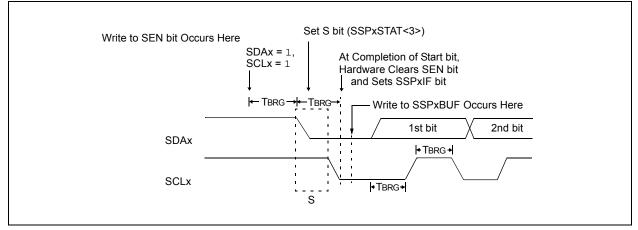

### 21.4.8 I<sup>2</sup>C<sup>™</sup> MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPxCON2<0>). If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit (SSPxSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPxCON2<0>) will be automatically cleared by hardware. The Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

Note: If, at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

### 21.4.8.1 WCOL Status Flag

If the user writes the SSPxBUF when a Start sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPxCON2 is disabled until the Start condition is complete.

### FIGURE 21-21: FIRST START BIT TIMING

| Name     | Bit 7    | Bit 6       | Bit 5       | Bit 4        | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------|----------|-------------|-------------|--------------|--------|---------|--------|--------|-----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE   | TMR0IF  | INT0IF | RBIF   | 75                          |

| PIR1     | _        | ADIF        | RC1IF       | TX1IF        | SSP1IF | TMR1GIF | TMR2IF | TMR1IF | 77                          |

| PIE1     | _        | ADIE        | RC1IE       | TX1IE        | SSP1IE | TMR1GIE | TMR2IE | TMR1IE | 77                          |

| IPR1     | _        | ADIP        | RC1IP       | TX1IP        | SSP1IP | TMR1GIP | TMR2IP | TMR1IP | 77                          |

| PIR3     | TMR5GIF  | LCDIF       | RC2IF       | TX2IF        | CTMUIF | CCP2IF  | CCP1IF | RTCCIF | 77                          |

| PIE3     | TMR5GIE  | LCDIE       | RC2IE       | TX2IE        | CTMUIE | CCP2IE  | CCP1IE | RTCCIE | 77                          |

| IPR3     | TMR5GIP  | LCDIP       | RC2IP       | TX2IP        | CTMUIP | CCP2IP  | CCP1IP | RTCCIP | 77                          |

| RCSTA1   | SPEN     | RX9         | SREN        | CREN         | ADDEN  | FERR    | OERR   | RX9D   | 77                          |

| TXREG1   | EUSART1  | Transmit Re | gister      |              |        |         |        |        | 77                          |

| TXSTA1   | CSRC     | TX9         | TXEN        | SYNC         | SENDB  | BRGH    | TRMT   | TX9D   | 77                          |

| BAUDCON1 | ABDOVF   | RCIDL       | RXDTP       | TXCKP        | BRG16  | —       | WUE    | ABDEN  | 79                          |

| SPBRGH1  | EUSART1  | Baud Rate ( | Generator R | egister Higl | n Byte |         |        |        | 76                          |

| SPBRG1   | EUSART1  | Baud Rate ( | Generator R | egister Low  | v Byte |         |        |        | 77                          |

| RCSTA2   | SPEN     | RX9         | SREN        | CREN         | ADDEN  | FERR    | OERR   | RX9D   | 81                          |

| TXREG2   | EUSART2  | Transmit Re | gister      |              |        |         |        |        | 82                          |

| TXSTA2   | CSRC     | TX9         | TXEN        | SYNC         | SENDB  | BRGH    | TRMT   | TX9D   | 81                          |

| BAUDCON2 | ABDOVF   | RCIDL       | RXDTP       | TXCKP        | BRG16  | —       | WUE    | ABDEN  | 81                          |

| SPBRGH2  | EUSART2  | Baud Rate ( | Generator R | egister Higl | n Byte |         |        | •      | 82                          |

| SPBRG2   | EUSART2  | Baud Rate ( | Generator R | egister Low  | v Byte |         |        |        | 82                          |

#### TABLE 22-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

## 27.4.2 CAPACITANCE CALIBRATION

There is a small amount of capacitance from the internal A/D Converter sample capacitor, as well as stray capacitance from the circuit board traces and pads that affect the precision of capacitance measurements. A measurement of the stray capacitance can be taken by making sure the desired capacitance to be measured has been removed.

After removing the capacitance to be measured:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT (= 1).

- 3. Wait for a fixed delay of time, *t*.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

- 6. Calculate the stray and A/D sample capacitances:

```

COFFSET = CSTRAY + CAD = (I \cdot t)/V

```

Where:

- I is known from the current source measurement step

- t is a fixed delay

- $\rm V$  is measured by performing an A/D conversion

This measured value is then stored and used for calculations of time measurement or subtracted for capacitance measurement. For calibration, it is expected that the capacitance of CSTRAY + CAD is approximately known; CAD is approximately 4 pF.

An iterative process may be required to adjust the time, t, that the circuit is charged to obtain a reasonable voltage reading from the A/D Converter. The value of t may be determined by setting *C*OFFSET to a theoretical value and solving for t. For example, if *C*STRAY is theoretically calculated to be 11 pF, and V is expected to be 70% of VDD or 2.31V, t would be:

or 63 µs.

See Example 27-3 for a typical routine for CTMU capacitance calibration.

#### REGISTER 28-5: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/P-1  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | —   | _   | —   | —   | _   | RTCOSC |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:           | P = Programmable bit | P = Programmable bit       |                    |  |  |  |

|-------------------|----------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, rea | ad as '0'          |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

bit 7-1 Unimplemented: Read as '0'

bit 0

RTCOSC: RTCC Reference Clock Select bit

1 = RTCC uses SOSC as a reference clock

0 = RTCC uses LF-INTOSC as a reference clock

#### REGISTER 28-6: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| R/P-1 | U-0 | U-0 | U-0 | R/P-1   | U-0 | R/P-1                 | R/P-1  |

|-------|-----|-----|-----|---------|-----|-----------------------|--------|

| MCLRE | —   | —   | _   | MSSPMSK | —   | ECCPMX <sup>(1)</sup> | CCP2MX |

| bit 7 |     |     |     |         |     |                       | bit 0  |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | MCLRE: MCLR Pin Enable bit                                                                    |

|---------|-----------------------------------------------------------------------------------------------|

|         | 1 = MCLR pin is enabled; RG5 input pin is disabled                                            |

|         | 0 = RG5 input pin is enabled; MCLR is disabled                                                |

| bit 6-4 | Unimplemented: Read as '0'                                                                    |

| bit 3   | MSSPMSK: MSSP V3 7-Bit Address Masking Mode Enable bit                                        |

|         | 1 = 7-Bit Address Masking mode is enabled                                                     |

|         | 0 = 5-Bit Address Masking mode is enabled                                                     |

| bit 2   | Unimplemented: Read as '0'                                                                    |

| bit 1   | ECCPMX: ECCP MUX bit <sup>(1)</sup>                                                           |

|         | 1 = Enhanced ECCP1 (P1B/P1C) is multiplexed onto RE6 and RE5, CCP6 onto RE6 and CCP7 onto RE5 |

|         | Enhanced ECCP3 (P3B/P3C) is multiplexed onto RE4 and RE3, CCP8 onto RE4 and CCP9 onto RE3     |

|         | 0 = Enhanced ECCP1 (P1B/P1C) is multiplexed onto RH7 and RH6, CCP6 onto RH7 and CCP7 onto RH6 |

|         | Enhanced ECCP3 (P3B/P3C) is multiplexed onto RH5 and RH4, CCP8 onto RH5 and CCP9 onto RH4     |

| bit 0   | CCP2MX: ECCP2 MUX bit                                                                         |

|         | 1 = ECCP2 is multiplexed with RC1                                                             |

|         | 0 = ECCP2 input/output is multiplexed with RE7 <sup>(1)</sup>                                 |

|         |                                                                                               |

Note 1: This feature is only available on 80-pin devices.

# REGISTER 28-10: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)<sup>(2)</sup>

| R/C-1               | R/C-1               | R/C-1                                 | R/C-1               | R/C-1            | R/C-1 | R/C-1          | R/C-1 |

|---------------------|---------------------|---------------------------------------|---------------------|------------------|-------|----------------|-------|

| WRT7 <sup>(1)</sup> | WRT6 <sup>(1)</sup> | WRT5 <sup>(1)</sup>                   | WRT4 <sup>(1)</sup> | WRT3             | WRT2  | WRT1           | WRT0  |

| bit 7               |                     |                                       |                     |                  |       |                | bit ( |

|                     |                     |                                       |                     |                  |       |                |       |

| Legend:             |                     | C = Clearable                         |                     |                  |       |                |       |

| R = Readable        |                     | W = Writable                          |                     | U = Unimpler     |       |                |       |

| -n = Value at       | POR                 | '1' = Bit is set                      |                     | '0' = Bit is cle | ared  | x = Bit is unk | nown  |

| bit 7               | WRT7: Write         | Protection bit <sup>(1</sup>          | )                   |                  |       |                |       |

|                     |                     | s not write-prote<br>s write-protecte |                     |                  |       |                |       |

| bit 6               | WRT6: Write         | Protection bit <sup>(1</sup>          | )                   |                  |       |                |       |

|                     |                     | s not write-prote                     |                     |                  |       |                |       |

|                     |                     | s write-protecte                      |                     |                  |       |                |       |

| bit 5               |                     | Protection bit <sup>(1</sup>          |                     |                  |       |                |       |

|                     |                     | s not write-prote<br>s write-protecte |                     |                  |       |                |       |

| bit 4               |                     | Protection bit <sup>(1</sup>          |                     |                  |       |                |       |

| Dit 4               |                     | not write-prote                       |                     |                  |       |                |       |

|                     |                     | s write-protecte                      |                     |                  |       |                |       |

| bit 3               | WRT3: Write         | Protection bit                        |                     |                  |       |                |       |

|                     | 1 = Block 3 is      | s not write-prote                     | ected               |                  |       |                |       |

|                     | 0 = Block 3 is      | s write-protecte                      | d                   |                  |       |                |       |

| bit 2               | WRT2: Write         | Protection bit                        |                     |                  |       |                |       |

|                     |                     | s not write-prote<br>s write-protecte |                     |                  |       |                |       |

| bit 1               | WRT1: Write         | Protection bit                        |                     |                  |       |                |       |

|                     |                     | s not write-prote<br>s write-protecte |                     |                  |       |                |       |

| bit 0               | WRT0: Write         | Protection bit                        |                     |                  |       |                |       |

|                     |                     | s not write-prote<br>s write-protecte |                     |                  |       |                |       |

|                     |                     |                                       |                     |                  |       |                |       |

| Note 1: Th          | is bit is only ava  | allable on PIC1                       | 8F67K90 and         | PIC18F87K90.     |       |                |       |

2: For the memory size of the blocks, refer to Figure 28-6.

| SLEEP Enter Sleep Mode                                               |                                                                                                                                             |                |      |                |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|----------------|--|--|

| Syntax:                                                              | SLEEP                                                                                                                                       |                |      |                |  |  |

| Operands:                                                            | None                                                                                                                                        | None           |      |                |  |  |

| Operation:                                                           |                                                                                                                                             |                |      |                |  |  |

| Status Affected:                                                     | TO, PD                                                                                                                                      |                |      |                |  |  |

| Encoding:                                                            | 0000                                                                                                                                        | 0000           | 0000 | 0011           |  |  |

| Description:                                                         | The Power-Down status bit (PD) is<br>cleared. The Time-out status bit (TO)<br>is set. The Watchdog Timer and its<br>postscaler are cleared. |                |      |                |  |  |

| The processor is put into Sleep mode<br>with the oscillator stopped. |                                                                                                                                             |                |      | ep mode        |  |  |

| Words:                                                               | 1                                                                                                                                           |                |      |                |  |  |

| Cycles:                                                              | 1                                                                                                                                           |                |      |                |  |  |

| Q Cycle Activity:                                                    |                                                                                                                                             |                |      |                |  |  |

| Q1                                                                   | Q2                                                                                                                                          | Q3             |      | Q4             |  |  |

| Decode                                                               | No<br>operation                                                                                                                             | Proces<br>Data |      | Go to<br>Sleep |  |  |

| Example: SLEEP                                                       |                                                                                                                                             |                |      |                |  |  |

| Before Instruction<br>TO = ?<br>PD = ?<br>After Instruction          |                                                                                                                                             |                |      |                |  |  |

| $\frac{TO}{PD} = 1 \dagger$ $\frac{TO}{PD} = 0$                      |                                                                                                                                             |                |      |                |  |  |

| † If WDT causes                                                      | wake-up, this l                                                                                                                             | bit is clear   | ed.  |                |  |  |

| W. If 'd' is '1', the result is stored in register 'f'.         If 'a' is '0', the Access Bank is selected 'a' is '1', the BSR is used to select the GPR bank.         If 'a' is '0' and the extended instruction set is enabled, this instruction operates Indexed Literal Offset Addressing mod whenever f ≤ 95 (5Fh). See         Section 29.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.         Words:       1         Cycles:       1         Q Cycle Activity:       Q1       Q2       Q3       Q4         Decode       Read       Process       Write to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SUBFWB             | Subtract f fr                                                                                                                   | om W with Bo                                            | orrow                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|--|

| $\begin{array}{ccccc} d \in [0,1] \\ a \in [0,1] \\ a \in [0,1] \\ c \in [0,1] \\ c \in [0,1] \\ \hline \\ c \in$ | Syntax:            | SUBFWB f                                                                                                                        | {,d {,a}}                                               |                               |  |

| $a \in [0, 1]$ Operation: (W) - (f) - (C) $\rightarrow$ dest Status Affected: N, OV, C, DC, Z Encoding: 0101 01da ffff ffff Description: Subtract register 'f and Carry flag (borrow) from W (2's complement method). If 'd' is '0', the result is stored in register 'f. If 'a' is '0', the Access Bank is selected 'a' is '1', the BSR is used to select the GPR bank. If 'a' is '0' and the extended instruction set is enabled, this instruction operates Indexed Literal Offset Addressing mod whenever f $\leq$ 95 (5Fh). See Section 29.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. Words: 1 Cycles: 1 Q Cycle Activity: Q1 Q2 Q3 Q4 Decode Read Process Write to Detata Virite to Decode Read Process Virite to Detata VV V V V V V V V V V V V V V V V V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Operands:          |                                                                                                                                 |                                                         |                               |  |

| Operation:       (W) - (f) - (C) → dest         Status Affected:       N, OV, C, DC, Z         Encoding:       0101       01da       ffff         Description:       Subtract register 'f and Carry flag<br>(borrow) from W (2's complement<br>method). If 'd' is '0', the result is stored in<br>register 'f.         If 'a' is '0', the Access Bank is selected<br>'a' is '1', the BSR is used to select the<br>GPR bank.         If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>indexed Literal Offset Addressing mod<br>whenever f ≤ 95 (5Fh). See         Section 29.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.         Words:       1         Cycles :       1         Q cycle Activity:       Q1       Q2       Q3       Q4         Decode       Read       Process       Write to<br>destinatio         Example 1:       SUBFWB       REG, 1, 0         Before Instruction       REG       3         REG       =       3         W       =       2       C       2         C       =       0       7         SUBFWB       REG, 0, 0       0       Before Instruction         REG       =       1       ; result is negative         Example 2:       SUBFWB       REG, 0, 0 <t< td=""><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |                                                                                                                                 |                                                         |                               |  |