Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

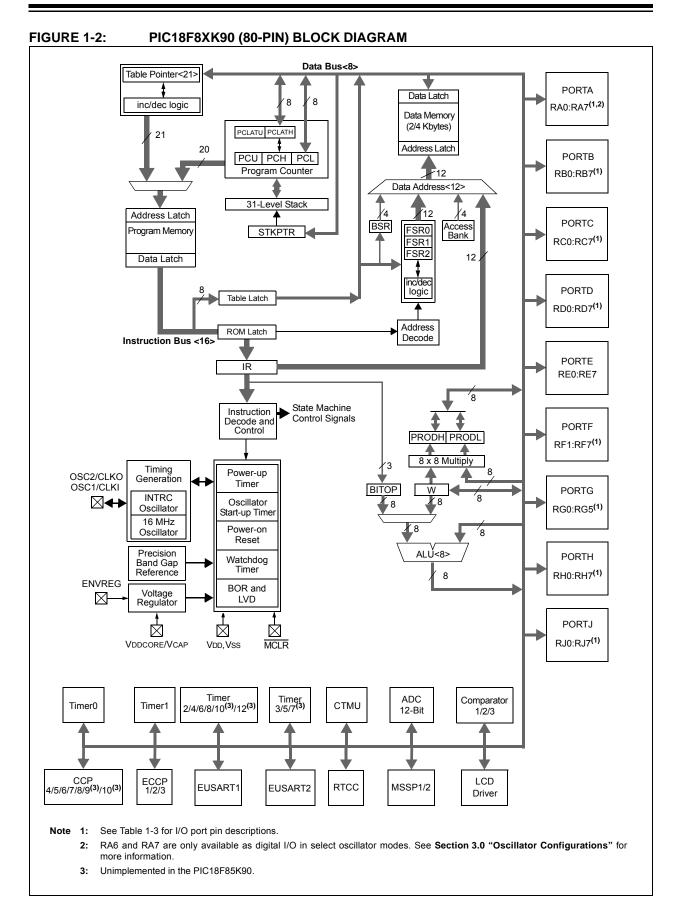

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

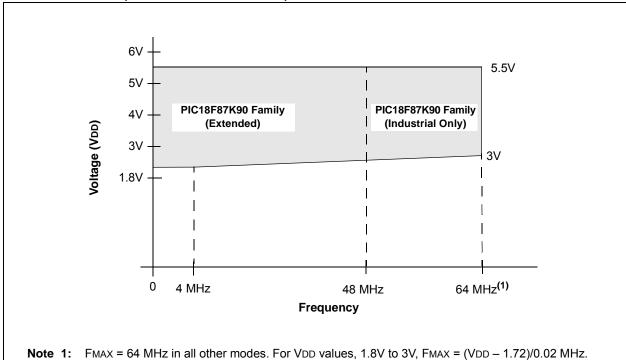

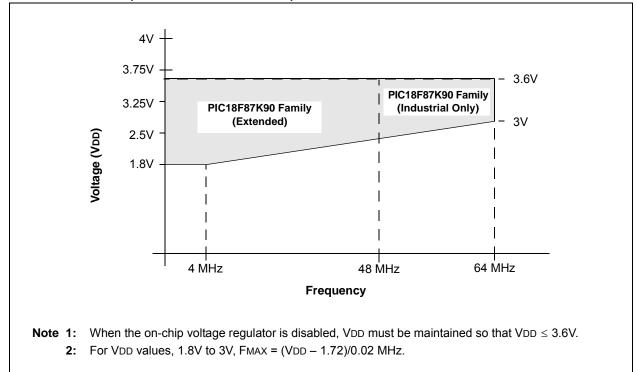

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

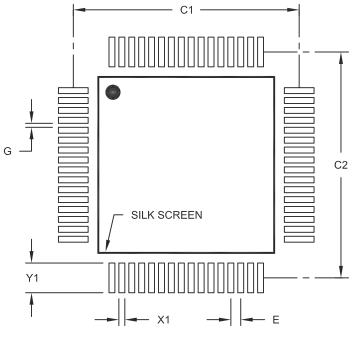

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k90-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

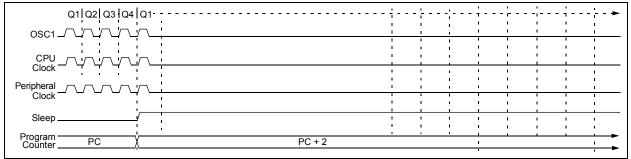

## 4.3 Sleep Mode

The power-managed Sleep mode in the PIC18F87K90 family of devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the LF-INTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

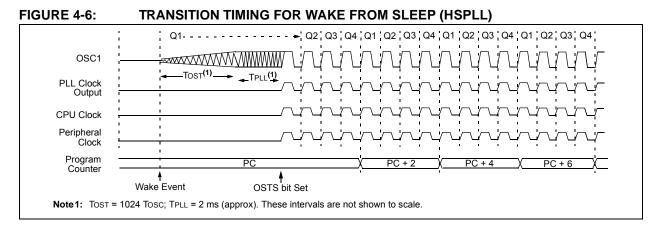

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 4-6). Alternately, the device will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor is enabled (see **Section 28.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

### 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits. The CPU, however, will not be clocked. The clock source status bits are not affected. This approach is a quick method to switch from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the LF-INTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (Parameter 38, Table 31-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or Sleep mode, a WDT timeout will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

#### FIGURE 4-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

Example 9-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 9-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 9-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| = | into intentional into zna into za                                               |

|---|---------------------------------------------------------------------------------|

| = | $(ARG1H \bullet ARG2H \bullet 2^{16}) + (ARG1H \bullet ARG2L \bullet 2^{8}) + $ |

|   | $(ARG1L \bullet ARG2H \bullet 2^8) + (ARG1L \bullet ARG2L)$                     |

|   | =                                                                               |

#### EXAMPLE 9-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

| - |        |             | 1                 |

|---|--------|-------------|-------------------|

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     |                   |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

|   |        |             |                   |

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = ARG1H:ARG1L • ARG2H:ARG2L                                      |

|-----------|------------------------------------------------------------------|

|           | $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                       |

|           | $(ARG1H \bullet ARG2L \bullet 2^8) +$                            |

|           | $(ARG1L \bullet ARG2H \bullet 2^8) +$                            |

|           | $(ARG1L \bullet ARG2L) +$                                        |

|           | $(-1 \bullet ARG2H < 7 > \bullet ARG1H: ARG1L \bullet 2^{16}) +$ |

|           | $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$   |

#### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     |         | ARG1L, W    |   |                  |

|-----|---------|-------------|---|------------------|

|     | MULWF   | ARG2L       | ; | ARG1L * ARG2L -> |

|     |         |             | ; | PRODH:PRODL      |

|     | MOVFF   | PRODH, RES1 | ; |                  |

|     |         | PRODL, RESO |   |                  |

| ;   |         |             |   |                  |

|     | MOVF    | ARG1H, W    |   |                  |

|     | MULWF   | ARG2H       | ; | ARG1H * ARG2H -> |

|     |         |             | ; | PRODH:PRODL      |

|     | MOVFF   | PRODH, RES3 | ; |                  |

|     | MOVFF   | PRODL, RES2 | ; |                  |

| ;   |         |             |   |                  |

|     | MOVF    | ARG1L, W    |   |                  |

|     | MULWF   | ARG2H       | ; | ARG1L * ARG2H -> |

|     |         |             | ; | PRODH:PRODL      |

|     | MOVF    | PRODL, W    | ; |                  |

|     |         | RES1, F     | ; | Add cross        |

|     | MOVF    | PRODH, W    | ; | products         |

|     |         | RES2, F     | ; |                  |

|     | CLRF    | WREG        | ; |                  |

|     | ADDWFC  | RES3, F     | ; |                  |

| ;   |         |             |   |                  |

|     |         | ARG1H, W    | ; |                  |

|     | MULWF   | ARG2L       | ; | ARG1H * ARG2L -> |

|     |         |             | ; | PRODH:PRODL      |

|     | MOVF    | PRODL, W    | ; |                  |

|     | ADDWF   | RES1, F     | ; | Add cross        |

|     | MOVF    | PRODH, W    | ; | products         |

|     | ADDWFC  | RES2, F     | ; |                  |

|     |         | WREG        | ; |                  |

|     | ADDWFC  | RES3, F     | ; |                  |

| ;   |         |             |   |                  |

|     | BTFSS   | ARG2H, 7    | ; | ARG2H:ARG2L neg? |

|     | BRA     | SIGN_ARG1   | ; | no, check ARG1   |

|     | MOVF    | ARG1L, W    | ; |                  |

|     |         | RES2        | ; |                  |

|     | MOVF    | ARG1H, W    | ; |                  |

|     | SUBWFB  | RES3        | ; |                  |

| SIC | GN_ARG1 |             |   |                  |

|     | BTFSS   | ARG1H, 7    | ; | ARG1H:ARG1L neg? |

|     | BRA     | CONT_CODE   | ; | no, done         |

|     | MOVF    | ARG2L, W    | ; |                  |

|     | SUBWF   | RES2        | ; |                  |

|     | MOVF    | ARG2H, W    | ; |                  |

|     | SUBWFB  | RES3        |   |                  |

| ;   |         |             |   |                  |

| CON | NT_CODE |             |   |                  |

|     | :       |             |   |                  |

| L   |         |             |   |                  |

### 10.1 INTCON Registers

The INTCON registers are readable and writable registers that contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

### REGISTER 10-1: INTCON: INTERRUPT CONTROL REGISTER

| GIE/GIEH         PEIE/GIEL         TMR0IE         INT0IE         RBIE         TMR0IF         INT0IF         RBIF <sup>(1)</sup> bit 7         bit 0 | R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| bit 7 bit 0                                                                                                                                         | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

|                                                                                                                                                     | bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | GIE/GIEH: Global Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts<br>When IPEN = 1:                    |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables all high-priority interrupts</li> <li>0 = Disables all interrupts</li> </ul>                                                                         |

| bit 6   | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                                                                |

|         | When IPEN = $0$ :                                                                                                                                                         |

|         | <ol> <li>Enables all unmasked peripheral interrupts</li> <li>Disables all peripheral interrupts</li> </ol>                                                                |

|         | When IPEN = 1:                                                                                                                                                            |

|         | <ul> <li>1 = Enables all low-priority peripheral interrupts</li> <li>0 = Disables all low-priority peripheral interrupts</li> </ul>                                       |

| bit 5   | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                                                                                |

|         | <ul> <li>1 = Enables the TMR0 overflow interrupt</li> <li>0 = Disables the TMR0 overflow interrupt</li> </ul>                                                             |

| bit 4   | INTOIE: INTO External Interrupt Enable bit                                                                                                                                |

|         | <ul> <li>1 = Enables the INT0 external interrupt</li> <li>0 = Disables the INT0 external interrupt</li> </ul>                                                             |

| bit 3   | RBIE: RB Port Change Interrupt Enable bit                                                                                                                                 |

|         | <ul> <li>1 = Enables the RB port change interrupt</li> <li>0 = Disables the RB port change interrupt</li> </ul>                                                           |

| bit 2   | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                                  |

|         | <ul> <li>1 = TMR0 register has overflowed (must be cleared in software)</li> <li>0 = TMR0 register did not overflow</li> </ul>                                            |

| bit 1   | INT0IF: INT0 External Interrupt Flag bit                                                                                                                                  |

|         | <ul> <li>1 = The INT0 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT0 external interrupt did not occur</li> </ul>                         |

| bit 0   | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                                                                             |

|         | <ul> <li>1 = At least one of the RB&lt;7:4&gt; pins changed state (must be cleared in software)</li> <li>0 = None of the RB&lt;7:4&gt; pins have changed state</li> </ul> |

| Note 1: | A mismatch condition will continue to set this bit. Reading PORTB, and then waiting one additional instruction                                                            |

cycle, will end the mismatch condition and allow the bit to be cleared.

## 13.2 Timer1 Operation

The Timer1 module is an 8 or 16-bit incrementing counter that is accessed through the TMR1H:TMR1L register pair.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter. It increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively.

When SOSC is selected as a Crystal mode (by SOSCEL), the RC1/SOSCI/ECCP2/P2A/SEG32 and RC0/SOSCO/SCLKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

## 13.3 Clock Source Selection

The TMR1CS<1:0> and SOSCEN bits of the T1CON register are used to select the clock source for Timer1. Register 13-1 displays the clock source selections.

#### 13.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc, as determined by the Timer1 prescaler.

## 13.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input, T1CKI. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external, 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

• Timer1 is enabled after a POR Reset

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0)

When T1CKI is high, Timer1 is enabled (TMR1ON = 1) when T1CKI is low.

| TABLE 13-1: TIMER | 1 CLOCK SOURCE SELECTION |

|-------------------|--------------------------|

|-------------------|--------------------------|

| TMR1CS1 | TMR1CS0 | SOSCEN | Clock Source                           |

|---------|---------|--------|----------------------------------------|

| 0       | 1       | x      | Clock Source (Fosc)                    |

| 0       | 0       | x      | Instruction Clock (Fosc/4)             |

| 1       | 0       | 0      | External Clock on T1CKI Pin            |

| 1       | 0       | 1      | Oscillator Circuit on SOSCI/SOSCO Pins |

### **REGISTER 17-16:** ALRMWD: ALARM WEEKDAY VALUE REGISTER<sup>(1)</sup>

| U-0         | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|-------------|-----|-----|-----|-----|-------|-------|-------|

| —           | —   | —   | _   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 7 bit 0 |     |     |     |     |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 2-0 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## REGISTER 17-17: ALRMHR: ALARM HOURS VALUE REGISTER<sup>(1)</sup>

| U-0        | -0 U-0 R/W-x |        | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x |

|------------|--------------|--------|--------|--------|--------|--------|-------|

| — — HRTEN1 |              | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |       |

| bit 7      |              |        |        |        |        |        | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                       |

|---------|------------------------------------------------------------------|

| bit 5-4 | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|         | Contains a value from 0 to 2.                                    |

| bit 3-0 | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

|         | Contains a value from 0 to 9.                                    |

|         |                                                                  |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### 18.4.3 SETUP FOR PWM OPERATION

To configure the CCP module for PWM operation (with CCP4 as an example):

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR4L register and CCP4CON<5:4> bits.

- 3. Make the CCP4 pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCP4 module for PWM operation.

| Name                   | Bit 7                                    | Bit 6                 | Bit 5          | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|------------------------|------------------------------------------|-----------------------|----------------|----------|----------|--------|---------|---------|-----------------------------|

| INTCON                 | GIE/GIEH                                 | PEIE/GIEL             | TMR0IE         | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 75                          |

| RCON                   | IPEN                                     | SBOREN                | CM             | RI       | TO       | PD     | POR     | BOR     | 76                          |

| PIR4                   | CCP10IF <sup>(1)</sup>                   | CCP9IF <sup>(1)</sup> | CCP8IF         | CCP7IF   | CCP6IF   | CCP5IF | CCP4IF  | CCP3IF  | 77                          |

| PIE4                   | CCP10IE <sup>(1)</sup>                   | CCP9IE <sup>(1)</sup> | CCP8IE         | CCP7IE   | CCP6IE   | CCP5IE | CCP4IE  | CCP3IE  | 77                          |

| IPR4                   | CCP10IP <sup>(1)</sup>                   | CCP9IP <sup>(1)</sup> | CCP8IP         | CCP7IP   | CCP6IP   | CCP5IP | CCP4IP  | CCP3IP  | 77                          |

| TRISB                  | TRISB7                                   | TRISB6                | TRISB5         | TRISB4   | TRISB3   | TRISB2 | TRISB1  | TRISB0  | 78                          |

| TRISC                  | TRISC7                                   | TRISC6                | TRISC5         | TRISC4   | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 78                          |

| TRISE                  | TRISE7                                   | TRISE6                | TRISE5         | TRISE4   | TRISE3   | TRISE2 | TRISE1  | TRISE0  | 78                          |

| TRISH                  | TRISH7                                   | TRISH6                | TRISH5         | TRISH4   | TRISH3   | TRISH2 | TRISH1  | TRISH0  | 78                          |

| TMR2                   | Timer2 Regis                             | ster                  |                |          |          |        |         |         | 76                          |

| TMR4                   | Timer4 Regis                             | ster                  |                |          |          |        |         |         | 82                          |

| TMR6                   | Timer6 Regis                             | ster                  |                |          |          |        |         |         | 81                          |

| TMR8                   | Timer8 Register                          |                       |                |          |          |        |         |         | 81                          |

| PR2                    | Timer2 Period Register                   |                       |                |          |          |        |         |         | 76                          |

| PR4                    | Timer4 Period Register                   |                       |                |          |          |        |         |         | 82                          |

| PR6                    | Timer6 Perio                             | d Register            |                |          |          |        |         |         | 81                          |

| PR8                    | Timer8 Perio                             | d Register            |                |          |          |        |         |         | 81                          |

| T2CON                  | —                                        | T2OUTPS3              | T2OUTPS2       | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 76                          |

| T4CON                  | _                                        | T4OUTPS3              | T4OUTPS2       | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | 82                          |

| T6CON                  | _                                        | T6OUTPS3              | T6OUTPS2       | T6OUTPS1 | T6OUTPS0 | TMR6ON | T6CKPS1 | T6CKPS0 | 81                          |

| T8CON                  | _                                        | T8OUTPS3              | T8OUTPS2       | T8OUTPS1 | T8OUTPS0 | TMR8ON | T8CKPS1 | T8CKPS0 | 81                          |

| CCPR4L                 | Capture/Corr                             | npare/PWM F           | egister 4 Low  | / Byte   |          |        |         |         | 82                          |

| CCPR4H                 | Capture/Corr                             | npare/PWM F           | legister 4 Hig | h Byte   |          |        |         |         | 82                          |

| CCPR5L                 | Capture/Corr                             | npare/PWM R           | egister 5 Low  | / Byte   |          |        |         |         | 82                          |

| CCPR5H                 | Capture/Corr                             | npare/PWM F           | legister 5 Hig | n Byte   |          |        |         |         | 82                          |

| CCPR6L                 | Capture/Corr                             | npare/PWM R           | legister 6 Low | / Byte   |          |        |         |         | 82                          |

| CCPR6H                 | Capture/Corr                             | npare/PWM F           | legister 6 Hig | n Byte   |          |        |         |         | 82                          |

| CCPR7L                 | Capture/Corr                             | npare/PWM F           | legister 7 Low | / Byte   |          |        |         |         | 82                          |

| CCPR7H                 | Capture/Compare/PWM Register 7 High Byte |                       |                |          |          |        |         |         | 82                          |

| CCPR8L                 | Capture/Com                              | npare/PWM F           | legister 8 Low | / Byte   |          |        |         |         | 80                          |

| CCPR8H                 | Capture/Corr                             | npare/PWM F           | legister 8 Hig | n Byte   |          |        |         |         | 80                          |

| CCPR9L <sup>(1)</sup>  | Capture/Corr                             | npare/PWM F           | Register 9 Low | / Byte   |          |        |         |         | 80                          |

| CCPR9H <sup>(1)</sup>  | Capture/Corr                             | npare/PWM F           | legister 9 Hig | n Byte   |          |        |         |         | 80                          |

| CCPR10L <sup>(1)</sup> | Capture/Corr                             | npare/PWM F           | egister 10 Lo  | w Byte   |          |        |         |         | 81                          |

#### TABLE 18-7: REGISTERS ASSOCIATED WITH PWM AND TIMERS

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2/4/6/8.

Note 1: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

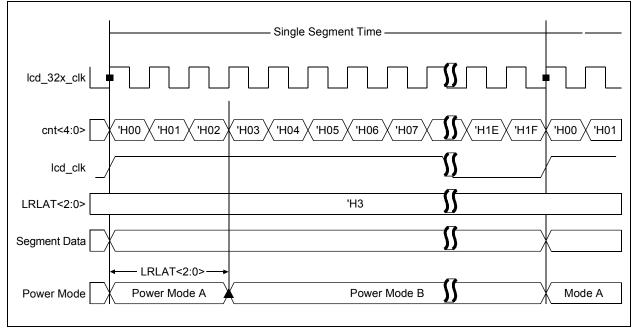

There are two power modes designated as "Mode A" and "Mode B". Mode A is set by the bits, LRLAP<1:0> and Mode B by LRLB<1:0>. The resistor ladder to use for Modes A and B are selected by the bits, LRLAP<1:0> and LRLBP<1:0>, respectively

Each ladder has a matching contrast control ladder, tuned to the nominal resistance of the reference ladder. This contrast control resistor can be controlled by LCDREF<5:3> (LCDCST<2:0>). Disabling the internal reference ladder results in all of the ladders being disconnected, allowing external voltages to be supplied.

To get additional current in High-Power mode, when LCDRL<7:6> (LRLAP<1:0>) = 11, both the medium and high-power resistor ladders are activated.

Whenever the LCD module is inactive (LCDA (LCDPS<5>) = 0), the reference ladder will be turned off.

### 20.3.2.1 Automatic Power Mode Switching

As an LCD segment is electrically only a capacitor, current is drawn only during the interval when the voltage is switching. To minimize total device current, the LCD reference ladder can be operated in a different power mode for the transition portion of the duration. This is controlled by the LCDRL register.

Mode A Power mode is active for a programmable time, beginning at the time when the LCD segment waveform is transitioning. The LCDRL<2:1> (LRLAT<2:0>) bits select how long, or if the Mode A is active. Mode B Power mode is active for the remaining time before the segments or commons change again.

As shown in Figure 20-5, there are 32 counts in a single segment time. Type-A can be chosen during the time when the wave form is in transition. Type-B can be used when the clock is stable or not in transition.

By using this feature of automatic power switching, using Type-A/Type-B, the power consumption can be optimized for a given contrast.

## 20.7 LCD Frame Frequency

The rate at which the COM and SEG outputs change is called the LCD frame frequency.

#### TABLE 20-5: FRAME FREQUENCY FORMULAS

| Multiplex | Frame Frequency =                    |

|-----------|--------------------------------------|

| Static    | Clock Source/(4 x 1 x (LP<3:0> + 1)) |

| 1/2       | Clock Source/(2 x 2 x (LP<3:0> + 1)) |

| 1/3       | Clock Source/(1 x 3 x (LP<3:0> + 1)) |

| 1/4       | Clock Source/(1 x 4 x (LP<3:0> + 1)) |

Note: Clock source is (Fosc/4)/8192, Timer1 Osc/32 or INTRC/32.

#### TABLE 20-6: APPROXIMATE FRAME FREQUENCY (IN Hz) USING Fosc AT 32 MHz, TIMER1 AT 32.768 kHz OR INTRC OSC

| LP<3:0> | Static | 1/2 | 1/3 | 1/4 |

|---------|--------|-----|-----|-----|

| 1       | 125    | 125 | 167 | 125 |

| 2       | 83     | 83  | 111 | 83  |

| 3       | 62     | 62  | 83  | 62  |

| 4       | 50     | 50  | 67  | 50  |

| 5       | 42     | 42  | 56  | 42  |

| 6       | 36     | 36  | 48  | 36  |

| 7       | 31     | 31  | 42  | 31  |

## 20.8 LCD Waveform Generation

LCD waveform generation is based on the philosophy that the net AC voltage across the dark pixel should be maximized and the net AC voltage across the clear pixel should be minimized. The net DC voltage across any pixel should be zero.

The COM signal represents the time slice for each common, while the SEG contains the pixel data.

The pixel signal (COM-SEG) will have no DC component and can take only one of the two rms values. The higher rms value will create a dark pixel and a lower rms value will create a clear pixel.

As the number of commons increases, the delta between the two rms values decreases. The delta represents the maximum contrast that the display can have.

The LCDs can be driven by two types of waveforms: Type-A and Type-B. In a Type-A waveform, the phase changes within each common type, whereas a Type-B waveform's phase changes on each frame boundary. Thus, Type-A waveforms maintain 0 VDc over a single frame, whereas Type-B waveforms take two frames.

| Note 1: | If Sleep has to be executed with       |  |  |  |  |  |

|---------|----------------------------------------|--|--|--|--|--|

|         | LCD Sleep enabled (SLPEN               |  |  |  |  |  |

|         | (LCDCON<6>) = 1), care must be taken   |  |  |  |  |  |

|         | to execute Sleep only when VDC on all  |  |  |  |  |  |

|         | the pixels is '0'.                     |  |  |  |  |  |

| 2:      | When the LCD clock source is (Fosc/4)/ |  |  |  |  |  |

2: When the LCD clock source is (FOSC/4)/ 8192, if Sleep is executed irrespective of the LCDCON<SLPEN> setting, the LCD goes into Sleep. Thus, take care to see that VDC on all pixels is '0' when Sleep is executed.

Figure 20-7 through Figure 20-17 provide waveforms for static, half-multiplex, one-third multiplex and quarter multiplex drives for Type-A and Type-B waveforms.

## 27.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

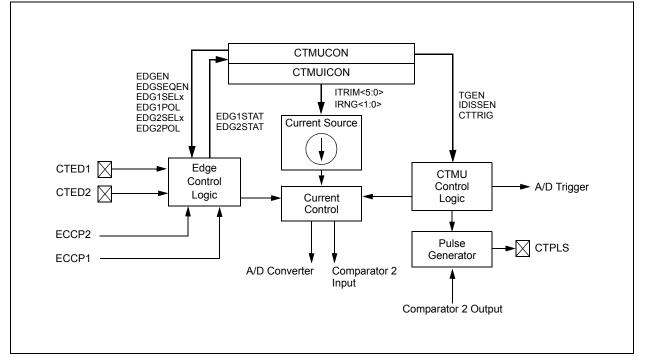

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. By working with other on-chip analog modules, the CTMU can precisely measure time, capacitance and relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The module includes these key features:

- Up to 24 channels available for capacitive or time measurement input

- · On-chip precision current source

- · Four-edge input trigger sources

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · Time measurement resolution of 1 nanosecond

- · High-precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- Accurate current source suitable for capacitive measurement

The CTMU works in conjunction with the A/D Converter to provide up to 24 channels for time or charge measurement, depending on the specific device and the number of A/D channels available. When configured for time delay, the CTMU is connected to one of the analog comparators. The level-sensitive input edge sources can be selected from four sources: two external inputs or the ECCP1/ECCP2 Special Event Triggers.

The CTMU special event can trigger the Analog-to-Digital Converter module.

Figure 27-1 provides a block diagram of the CTMU.

## 27.1 CTMU Registers

The control registers for the CTMU are:

- CTMUCONH

- CTMUCONL

- CTMUICON

The CTMUCONH and CTMUCONL registers (Register 27-1 and Register 27-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 27-3) has bits for selecting the current source range and current source trim.

#### REGISTER 27-1: CTMUCONH: CTMU CONTROL HIGH REGISTER

| R/W-0  | U-0                  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0  |

|--------|----------------------|-------|-------|-------|----------|---------|--------|

| CTMUEN | CTMUEN — CTMUSIDL TG |       | TGEN  | EDGEN | EDGSEQEN | IDISSEN | CTTRIG |

| bit 7  |                      |       |       |       |          |         | bit 0  |

|        |                      |       |       |       |          |         |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | CTMUEN: CTMU Enable bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Module is enabled</li><li>0 = Module is disabled</li></ul>                                                             |

| bit 6 | Unimplemented: Read as '0'                                                                                                         |

| bit 5 | CTMUSIDL: Stop in Idle Mode bit                                                                                                    |

|       | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul> |

| bit 4 | TGEN: Time Generation Enable bit                                                                                                   |

|       | <ul><li>1 = Enables edge delay generation</li><li>0 = Disables edge delay generation</li></ul>                                     |

| bit 3 | EDGEN: Edge Enable bit                                                                                                             |

|       | 1 = Edges are not blocked                                                                                                          |

|       | 0 = Edges are blocked                                                                                                              |

| bit 2 | EDGSEQEN: Edge Sequence Enable bit                                                                                                 |

|       | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>              |

| bit 1 | IDISSEN: Analog Current Source Control bit                                                                                         |

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul>            |

| bit 0 | <b>CTTRIG:</b> Trigger Control bit<br>1 = Trigger output is enabled<br>0 = Trigger output is disabled                              |

## 27.2 CTMU Operation

The CTMU works by using a fixed current source to charge a circuit. The type of circuit depends on the type of measurement being made.

In the case of charge measurement, the current is fixed and the amount of time the current is applied to the circuit is fixed. The amount of voltage read by the A/D becomes a measurement of the circuit's capacitance.

In the case of time measurement, the current, as well as the capacitance of the circuit, is fixed. In this case, the voltage read by the A/D is representative of the amount of time elapsed from the time the current source starts and stops charging the circuit.

If the CTMU is being used as a time delay, both capacitance and current source are fixed, as well as the voltage supplied to the comparator circuit. The delay of a signal is determined by the amount of time it takes the voltage to charge to the comparator threshold voltage.

### 27.2.1 THEORY OF OPERATION

The operation of the CTMU is based on the equation for charge:

$C = I \bullet \frac{dV}{dT}$

More simply, the amount of charge measured in coulombs in a circuit is defined as current in amperes (I) multiplied by the amount of time in seconds that the current flows (t). Charge is also defined as the capacitance in farads (C) multiplied by the voltage of the circuit (V). It follows that:

$I \bullet t = C \bullet V$

The CTMU module provides a constant, known current source. The A/D Converter is used to measure (V) in the equation, leaving two unknowns: capacitance (C) and time (t). The above equation can be used to calculate capacitance or time, by either the relationship using the known fixed capacitance of the circuit:

$t = (C \bullet V)/I$

or by:

$\mathbf{C} = (\mathbf{I} \bullet \mathbf{t}) / \mathbf{V}$

using a fixed time that the current source is applied to the circuit.

## 27.2.2 CURRENT SOURCE

At the heart of the CTMU is a precision current source, designed to provide a constant reference for measurements. The level of current is user-selectable across three ranges or a total of two orders of magnitude, with the ability to trim the output in  $\pm 2\%$  increments (nominal). The current range is selected by the IRNG<1:0> bits (CTMUICON<1:0>), with a value of '00' representing the lowest range.

Current trim is provided by the ITRIM<5:0> bits (CTMUICON<7:2>). These six bits allow trimming of the current source in steps of approximately 2% per step. Half of the range adjusts the current source positively and the other half reduces the current source. A value of '000000' is the neutral position (no change). A value of '100000' is the maximum negative adjustment (approximately -62%) and '011111' is the maximum positive adjustment (approximately +62%).

## 27.2.3 EDGE SELECTION AND CONTROL

CTMU measurements are controlled by edge events occurring on the module's two input channels. Each channel, referred to as Edge 1 and Edge 2, can be configured to receive input pulses from one of the edge input pins (CTED1 and CTED2) or CCPx Special Event Triggers. The input channels are level-sensitive, responding to the instantaneous level on the channel rather than a transition between levels. The inputs are selected using the EDG1SEL and EDG2SEL bit pairs (CTMUCONL<3:2, 6:5>).

In addition to source, each channel can be configured for event polarity using the EDGE2POL and EDGE1POL bits (CTMUCONL<7,4>). The input channels can also be filtered for an edge event sequence (Edge 1 occurring before Edge 2) by setting the EDGSEQEN bit (CTMUCONH<2>).

## 27.2.4 EDGE STATUS

The CTMUCON register also contains two status bits, EDG2STAT and EDG1STAT (CTMUCONL<1:0>). Their primary function is to show if an edge response has occurred on the corresponding channel. The CTMU automatically sets a particular bit when an edge response is detected on its channel. The level-sensitive nature of the input channels also means that the status bits become set immediately if the channel's configuration is changed and matches the channel's current state.

The module uses the edge status bits to control the current source output to external analog modules (such as the A/D Converter). Current is only supplied to external modules when only one (not both) of the status bits is set. Current is shut off when both bits are either set or cleared. This allows the CTMU to measure current only during the interval between edges. After both status bits are set, it is necessary to clear them before another measurement is taken. Both bits should be cleared simultaneously, if possible, to avoid re-enabling the CTMU current source.

In addition to being set by the CTMU hardware, the edge status bits can also be set by software. This permits a user application to manually enable or disable the current source. Setting either (but not both) of the bits enables the current source. Setting or clearing both bits at once disables the source.

| DEC                                                                                                                                                                                                        | FSZ                                                                                                                                                                                                                                                                                  | Decrement                                                                      | f, Skip if 0                     |                            | DCF                                                                                                                                                                                                                                             | SNZ                      | Decremen                                              | t f, Skip if Not                    | 0               |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------|-------------------------------------|-----------------|--|

| Synta                                                                                                                                                                                                      | ax:                                                                                                                                                                                                                                                                                  | DECFSZ f                                                                       | {,d {,a}}                        |                            | Synta                                                                                                                                                                                                                                           | ax:                      | DCFSNZ                                                | f {,d {,a}}                         |                 |  |

| Oper                                                                                                                                                                                                       | ands:                                                                                                                                                                                                                                                                                | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$ |                                  |                            | Oper                                                                                                                                                                                                                                            | ands:                    | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$ | d ∈ [0,1]                           |                 |  |

| Oper                                                                                                                                                                                                       | ation:                                                                                                                                                                                                                                                                               | (f) – $1 \rightarrow de$<br>skip if result                                     |                                  |                            | Oper                                                                                                                                                                                                                                            | ation:                   | (f) – $1 \rightarrow de$ skip if resul                |                                     |                 |  |

| Statu                                                                                                                                                                                                      | s Affected:                                                                                                                                                                                                                                                                          | None                                                                           |                                  |                            | Statu                                                                                                                                                                                                                                           | s Affected:              | None                                                  |                                     |                 |  |

| Enco                                                                                                                                                                                                       | ding:                                                                                                                                                                                                                                                                                | 0010                                                                           | 11da ff:                         | ff ffff                    | Enco                                                                                                                                                                                                                                            | ding:                    | 0100                                                  | 11da fff                            | f ffff          |  |

| Desc                                                                                                                                                                                                       | Description: The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'.                                                                                                              |                                                                                | Desc                             | ription:                   | The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'.                                                                                      |                          |                                                       |                                     |                 |  |

| If the result is '0', the next instruction<br>which is already fetched is discarded<br>and a NOP is executed instead, making<br>it a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected. |                                                                                                                                                                                                                                                                                      |                                                                                |                                  | instruction<br>discarded a | is not '0', the<br>which is alread<br>and a NOP is ex<br>aking it a two-c                                                                                                                                                                       | ly fetched is<br>cecuted |                                                       |                                     |                 |  |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                      | lf 'a' is '1', th<br>GPR bank.                                                 | ne BSR is use                    | d to select the            |                                                                                                                                                                                                                                                 |                          |                                                       | he Access Bar<br>he BSR is use      |                 |  |

|                                                                                                                                                                                                            | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 29.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                                                |                                  |                            | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 29.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                          |                                                       |                                     |                 |  |

| Word                                                                                                                                                                                                       | ls:                                                                                                                                                                                                                                                                                  | 1                                                                              |                                  |                            |                                                                                                                                                                                                                                                 |                          | Literal Off                                           | set Mode" for                       | details.        |  |

| Cycle                                                                                                                                                                                                      | es:                                                                                                                                                                                                                                                                                  | 1(2)                                                                           |                                  |                            | Word                                                                                                                                                                                                                                            | s:                       | 1                                                     |                                     |                 |  |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                      |                                                                                | cles if skip an<br>2-word instru |                            | Cycle                                                                                                                                                                                                                                           | es:                      |                                                       | ycles if skip ar<br>a 2-word instru |                 |  |

| QC                                                                                                                                                                                                         | ycle Activity:<br>Q1                                                                                                                                                                                                                                                                 | Q2                                                                             | Q3                               | Q4                         | QC                                                                                                                                                                                                                                              | cle Activity:            | - )                                                   |                                     |                 |  |

|                                                                                                                                                                                                            | Decode                                                                                                                                                                                                                                                                               | Read                                                                           | Process                          | Write to                   |                                                                                                                                                                                                                                                 | Q1                       | Q2                                                    | Q3                                  | Q4              |  |

|                                                                                                                                                                                                            | 200000                                                                                                                                                                                                                                                                               | register 'f'                                                                   | Data                             | destination                |                                                                                                                                                                                                                                                 | Decode                   | Read                                                  | Process                             | Write to        |  |

| lf sk                                                                                                                                                                                                      | ip:                                                                                                                                                                                                                                                                                  |                                                                                |                                  |                            |                                                                                                                                                                                                                                                 |                          | register 'f'                                          | Data                                | destination     |  |

|                                                                                                                                                                                                            | Q1                                                                                                                                                                                                                                                                                   | Q2                                                                             | Q3                               | Q4                         | lf sk                                                                                                                                                                                                                                           | •                        |                                                       |                                     |                 |  |

|                                                                                                                                                                                                            | No                                                                                                                                                                                                                                                                                   | No                                                                             | No                               | No                         |                                                                                                                                                                                                                                                 | Q1                       | Q2                                                    | Q3                                  | Q4              |  |

| lf old                                                                                                                                                                                                     | operation                                                                                                                                                                                                                                                                            | operation                                                                      | operation                        | operation                  |                                                                                                                                                                                                                                                 | No<br>operation          | No<br>operation                                       | No<br>operation                     | No<br>operation |  |

| 11 56                                                                                                                                                                                                      | Q1                                                                                                                                                                                                                                                                                   | d by 2-word ins<br>Q2                                                          | Q3                               | Q4                         | lf sk                                                                                                                                                                                                                                           |                          | d by 2-word in                                        |                                     | oporation       |  |

|                                                                                                                                                                                                            | No                                                                                                                                                                                                                                                                                   | No                                                                             | No                               | No                         |                                                                                                                                                                                                                                                 | Q1                       | Q2                                                    | Q3                                  | Q4              |  |

|                                                                                                                                                                                                            | operation                                                                                                                                                                                                                                                                            | operation                                                                      | operation                        | operation                  |                                                                                                                                                                                                                                                 | No                       | No                                                    | No                                  | No              |  |

|                                                                                                                                                                                                            | No                                                                                                                                                                                                                                                                                   | No                                                                             | No                               | No                         |                                                                                                                                                                                                                                                 | operation                | operation                                             | operation                           | operation       |  |

|                                                                                                                                                                                                            | operation                                                                                                                                                                                                                                                                            | operation                                                                      | operation                        | operation                  |                                                                                                                                                                                                                                                 | No                       | No                                                    | No                                  | No              |  |

| <u>Exan</u>                                                                                                                                                                                                | nple:                                                                                                                                                                                                                                                                                | HERE                                                                           | DECFSZ<br>GOTO                   | CNT, 1, 1<br>LOOP          | Exan                                                                                                                                                                                                                                            | operation                |                                                       | OPERATION                           | operation       |  |

|                                                                                                                                                                                                            | Doforo Instruct                                                                                                                                                                                                                                                                      | CONTINUE                                                                       |                                  |                            |                                                                                                                                                                                                                                                 |                          |                                                       | :                                   |                 |  |

|                                                                                                                                                                                                            | Before Instruc<br>PC                                                                                                                                                                                                                                                                 |                                                                                | (HERE)                           |                            |                                                                                                                                                                                                                                                 | Before Instruc           | tion                                                  |                                     |                 |  |

|                                                                                                                                                                                                            | After Instruction                                                                                                                                                                                                                                                                    |                                                                                | . ( ם אם אום און                 |                            |                                                                                                                                                                                                                                                 | TEMP                     | =                                                     | ?                                   |                 |  |

|                                                                                                                                                                                                            | CNT                                                                                                                                                                                                                                                                                  | = CNT – 1                                                                      |                                  |                            |                                                                                                                                                                                                                                                 | After Instructio         |                                                       |                                     |                 |  |

|                                                                                                                                                                                                            | If CNT<br>PC                                                                                                                                                                                                                                                                         |                                                                                | (CONTINUE                        | :)                         |                                                                                                                                                                                                                                                 | TEMP<br>If TEMP          | =                                                     | TEMP – 1,<br>0;                     |                 |  |