Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 53                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k90t-i-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                            | Pin Number | Pin                     |                                               | Description                                                                                                                                                   |  |

|-------------------------------------------------------------------------------------|------------|-------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                                                            | QFN/TQFP   | Туре                    |                                               | Description                                                                                                                                                   |  |

|                                                                                     |            |                         |                                               | PORTA is a bidirectional I/O port.                                                                                                                            |  |

| RA0/AN0/ULPWU<br>RA0<br>AN0<br>ULPWU                                                | 24         | I/O<br>I<br>I           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 0.<br>Ultra Low-Power Wake-up (ULPW) input.                                                                                      |  |

| RA1/AN1/SEG18<br>RA1<br>AN1<br>SEG18                                                | 23         | I/O<br>I<br>O           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 1.<br>SEG18 output for LCD.                                                                                                      |  |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF-                                                | 22         | I/O<br>I<br>I           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.                                                                                         |  |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                                                | 21         | I/O<br>I<br>I           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input.                                                                                        |  |

| RA4/T0CKI/SEG14<br>RA4<br>T0CKI<br>SEG14                                            | 28         | I/O<br>I<br>O           | ST<br>ST<br>Analog                            | Digital I/O.<br>Timer0 external clock input.<br>SEG14 output for LCD.                                                                                         |  |

| RA5/AN4/SEG15/T1CKI/<br>T3G/HLVDIN<br>RA5<br>AN4<br>SEG15<br>T1CKI<br>T3G<br>HLVDIN | 27         | I/O<br>I<br>O<br>I<br>I | TTL<br>Analog<br>Analog<br>ST<br>ST<br>Analog | Digital I/O.<br>Analog Input 4.<br>SEG15 output for LCD.<br>Timer1 clock input.<br>Timer3 external clock gate input.<br>High/Low-Voltage Detect (HLVD) input. |  |

| RA6                                                                                 |            |                         |                                               | See the OSC2/CLKO/RA6 pin.                                                                                                                                    |  |

| RA7                                                                                 |            |                         |                                               | See the OSC1/CLKI/RA7 pin.                                                                                                                                    |  |

| $ST = Schm$ $I = Input$ $P = Powe$ $I^{2}C^{TM} = I^{2}C/SI$                        | MBus       | : with C                |                                               | CMOS = CMOS compatible input or output<br>els Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)<br>2MX Configuration bit is set.     |  |

### TABLE 1-3: PIC18F6XK90 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K90 and PIC18F85K90 devices.

## TABLE 6-1: PIC18F87K90 FAMILY SPECIAL FUNCTION REGISTER MAP<sup>(5)</sup> (CONTINUED)

| Addr. | Name                  | Addr. | Name                  | Addr. | Name     | Addr. | Name    | Addr. | Name     | Addr. | Name                  |

|-------|-----------------------|-------|-----------------------|-------|----------|-------|---------|-------|----------|-------|-----------------------|

| F3Eh  | TMR7L <sup>(4)</sup>  | F31h  | PR12 <sup>(4)</sup>   | F24h  | ANCON1   | F17h  | PMD2    | F0Ah  | CCPR6L   | EFDh  | LCDREF                |

| F3Dh  | T7CON <sup>(4)</sup>  | F30h  | T12CON <sup>(4)</sup> | F23h  | ANCON2   | F16h  | PMD3    | F09h  | CCP6CON  | EFCh  | LCDRL                 |

| F3Ch  | T7GCON <sup>(4)</sup> | F2Fh  | CM2CON                | F22h  | RCSTA2   | F15h  | TMR5H   | F08h  | CCPR7H   | EFBh  | LCDSE5 <sup>(3)</sup> |

| F3Bh  | TMR6                  | F2Eh  | CM3CON                | F21h  | TXSTA2   | F14h  | TMR5L   | F07h  | CCPR7L   | EFAh  | LCDSE4                |

| F3Ah  | PR6                   | F2Dh  | CCPTMRS0              | F20h  | BAUDCON2 | F13h  | T5CON   | F06h  | CCP7CON  | EF9h  | LCDSE3                |

| F39H  | T6CON                 | F2Ch  | CCPTMRS1              | F1Fh  | SPBRGH2  | F12h  | T5GCON  | F05h  | TMR4     | EF8h  | LCDSE2                |

| F38h  | TMR8                  | F2Bh  | CCPTMRS2              | F1Eh  | SPBRG2   | F11h  | CCPR4H  | F04h  | PR4      | EF7h  | LCDSE1                |

| F37h  | PR8                   | F2Ah  | REFOCON               | F1Dh  | RCREG2   | F10h  | CCPR4L  | F03h  | T4CON    | EF6h  | LCDSE0                |

| F36h  | T8CON                 | F29H  | ODCON1                | F1Ch  | TXREG2   | F0Fh  | CCP4CON | F02h  | SSP2BUF  | EF5h  | LCDPS                 |

| F35h  | TMR10 <sup>(4)</sup>  | F28h  | ODCON2                | F1Bh  | PSTR2CON | F0Eh  | CCPR5H  | F01h  | SSP2ADD  | EF4h  | LCDCON                |

| F34h  | PR10 <sup>(4)</sup>   | F27h  | ODCON3                | F1Ah  | PSTR3CON | F0Dh  | CCPR5L  | F00h  | SSP2STAT |       |                       |

| F33h  | T10CON <sup>(4)</sup> | F26h  |                       | F19h  | PMD0     | F0Ch  | CCP5CON | EFFh  | SSP2CON1 | ]     |                       |

**Note 1:** This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available in 64-pin devices (PIC18F6XK90).

4: This register is not available in devices with a program memory of 32 Kbytes (PIC18FX5K90).

5: Addresses, EF4h through F5Fh, are also used by SFRs, but are not part of the Access RAM. Users must always load the proper BSR value to access these registers.

| Address | File Name                | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3                | Bit 2                | Bit 1                | Bit 0    | Value on<br>POR, BOR |

|---------|--------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------|----------------------|

| F50h    | CCPR2H                   | Capture/Com          | pare/PWM R           | egister 2 High       | Byte                 |                      |                      |                      |          | xxxx xxxx            |

| F51h    | ECCP2DEL                 | P2RSEN               | P2DC6                | P2DC5                | P2DC4                | P2DC3                | P2DC2                | P2DC1                | P2DC0    | 0000 0000            |

| F52h    | ECCP2AS                  | ECCP2ASE             | ECCP2AS2             | ECCP2AS1             | ECCP2AS0             | PSS2AC1              | PSS2AC0              | PSS2BD1              | PSS2BD0  | 0000 0000            |

| F53h    | PADCFG1                  | RDPU                 | REPU                 | RJPU <sup>(2)</sup>  | _                    | _                    | RTSECSEL1            | RTSECSEL0            | _        | 00000-               |

| F54h    | CM1CON                   | CON                  | COE                  | CPOL                 | EVPOL1               | EVPOL0               | CREF                 | CCH1                 | CCH0     | 0001 1111            |

| F55h    | CTMUICON                 | ITRIM5               | ITRIM4               | ITRIM3               | ITRIM2               | ITRIM1               | ITRIM0               | IRNG1                | IRNG1    | 0000 0000            |

| F56h    | CTMUCONL                 | EDG2POL              | EDG2SEL1             | EDG2SEL0             | EDG1POL              | EDG1SEL1             | EDG1SEL0             | EDG2STAT             | EDG1STAT | 0000 0000            |

| F57h    | CTMUCONH                 | CTMUEN               | _                    | CTMUSIDL             | TGEN                 | EDGEN                | EDGSEQEN             | IDISSEN              | CTTRIG   | 0-00 0000            |

| F58h    | ALRMVALL                 | Alarm Value          | High Register        | Window base          | ed on APTR<1         | :0>                  |                      |                      |          | 0000 0000            |

| F59h    | ALRMVALH                 | Alarm Value          | High Register        | Window base          | ed on APTR<1         | :0>                  |                      |                      |          | xxxx xxxx            |

| F5Ah    | ALRMRPT                  | ARPT7                | ARPT6                | ARPT5                | ARPT4                | ARPT3                | ARPT2                | ARPT1                | ARPT0    | 0000 0000            |

| F5Bh    | ALRMCFG                  | ALRMEN               | CHIME                | AMASK3               | AMASK2               | AMASK1               | AMASK0               | ALRMPTR1             | ALRMPTR0 | 0000 0000            |

| F5Ch    | RTCVALL                  |                      | Low Register         | Window base          | d on RTCPTF          | R<1:0>               |                      |                      |          | 0000 0000            |

| F5Dh    | RTCVALH                  |                      | High Register        |                      |                      |                      |                      |                      |          | xxxx xxxx            |

| F5Eh    | RTCCAL                   | CAL7                 | CAL6                 | CAL5                 | CAL4                 | CAL3                 | CAL2                 | CAL1                 | CAL0     | xxxx xxxx            |

| F5Fh    | RTCCFG                   | RTCEN                | _                    | RTCWREN              | RTCSYNC              | HALFSEC              | RTCOE                | RTCPTR1              | RTCPTR0  | 0-00 0000            |

| F60h    | PIE6                     | _                    | _                    | _                    | EEIE                 | _                    | CMP3IE               | CMP2IE               | CMP1IE   | 0 -000               |

| F61h    | EEDATA                   | EEPROM Da            | ata Register         |                      |                      |                      | 0                    | 0                    | 0        | 0000 0000            |

| F62h    | EEADR                    |                      | Idress Registe       | er Low Byte          |                      |                      |                      |                      |          | 0000 0000            |

| F63h    | EEADRH                   |                      | Idress Registe       |                      |                      |                      |                      |                      |          | 00                   |

| F64h    | OSCCON2                  |                      | SOSCRUN              |                      | _                    | SOSCGO               |                      | MFIOFS               | MFIOSEL  | -0 0-x0              |

| F65h    | BAUDCON1                 | ABDOVF               | RCIDL                | RXDTP                | ТХСКР                | BRG16                |                      | WUE                  | ABDEN    | 0000 0-x0            |

| F66h    | LCDDATA0                 | S07C0                | S06C0                | S05C0                | S04C0                | S03C0                | S02C0                | S01C0                | S00C0    | xxxx xxxx            |

| F67h    | LCDDATA0                 | S15C0                | S14C0                | S13C0                | S12C0                | S11C0                | S10C0                | S09C0                | S08C0    |                      |

| F68h    | LCDDATA1                 | S23C0                | S22C0                | S21C0                | S20C0                | S19C0                | S18C0                | S17C0                | S16C0    | xxxx xxxx            |

| F69h    | LCDDATA2                 | S31C0                | S30C0                | S29C0                | S28C0                | S19C0                | S26C0                | S25C0                | S24C0    | xxxx xxxx            |

|         |                          | S39C0                |                      |                      |                      |                      |                      |                      |          | xxxx xxxx            |

| F6Ah    | LCDDATA4                 |                      | S38C0                | S37C0                | S36C0                | S35C0                | S34C0                | S33C0                | S32C0    | XXXX XXXX            |

| F6Bh    | LCDDATA5                 | S47C0                | S46C0                | S45C0                | S44C0                | S43C0                | S42C0                | S41C0                | S40C0    | XXXX XXXX            |

| F6Ch    | LCDDATA6                 | S07C1                | S06C1                | S05C1                | S04C1                | S03C1                | S02C1                | S01C1                | S00C1    | XXXX XXXX            |

| F6Dh    | LCDDATA7                 | S15C1                | S14C1                | S13C1                | S12C1                | S11C1                | S10C1                | S09C1                | S08C1    | XXXX XXXX            |

| F6Eh    | LCDDATA8                 | S23C1                | S22C1                | S21C1                | S20C1                | S19C1                | S18C1                | S17C1                | S16C1    | XXXXXXXX             |

| F6Fh    | LCDDATA9                 | S31C1                | S30C1                | S29C1                | S28C1                | S27C1                | S26C1                | S25C1                | S24C1    | XXXX XXXX            |

| F70h    | LCDDATA10 <sup>(2)</sup> | S39C1 <sup>(2)</sup> | S38C1 <sup>(2)</sup> | S37C1 <sup>(2)</sup> | S36C1 <sup>(2)</sup> | S35C1 <sup>(2)</sup> | S34C1 <sup>(2)</sup> | S33C1 <sup>(2)</sup> | S32C1    | XXXX XXXX            |

| F71h    | LCDDATA11 <sup>(2)</sup> | S47C1                | S46C1                | S45C1                | S44C1                | S43C1                | S42C1                | S41C1                | S40C1    | XXXX XXXX            |

|         | LCDDATA12                | S07C2                | S06C2                | S05C2                | S04C2                | S03C2                | S02C2                | S01C2                | S00C2    | XXXX XXXX            |

| F73h    | LCDDATA13                | S15C2                | S14C2                | S13C2                | S12C2                | S11C2                | S10C2                | S09C2                | S08C2    | XXXX XXXX            |

| F74h    | LCDDATA14                | S23C2                | S22C2                | S21C2                | S20C2                | S19C2                | S18C2                | S17C2                | S16C2    | XXXX XXXX            |

| F75h    | LCDDATA15                | S31C2                | S30C2                | S29C2                | S28C2                | S27C2                | S26C2                | S25C2                | S24C2    | XXXX XXXX            |

| F76h    | LCDDATA16 <sup>(2)</sup> | S39C2 <sup>(2)</sup> | S38C2 <sup>(2)</sup> | S37C2 <sup>(2)</sup> | S36C2 <sup>(2)</sup> | S35C2 <sup>(2)</sup> | S34C2 <sup>(2)</sup> | S33C2 <sup>(2)</sup> | S32C2    | XXXX XXXX            |

| F77h    | LCDDATA17 <sup>(2)</sup> | S47C2                | S46C2                | S45C2                | S44C2                | S43C2                | S42C2                | S41C2                | S40C2    | XXXX XXXX            |

| F78h    | LCDDATA18                | S07C3                | S06C3                | S05C3                | S04C3                | S03C3                | S02C3                | S01C3                | S00C3    | XXXX XXXX            |

| F79h    | LCDDATA19                | S15C3                | S14C3                | S13C3                | S12C3                | S11C3                | S10C3                | S09C3                | S08C3    | XXXX XXXX            |

| F7Ah    | LCDDATA20                | S23C3                | S22C3                | S21C3                | S20C3                | S19C3                | S18C3                | S17C3                | S16C3    | XXXX XXXX            |

| F7Bh    | LCDDATA21                | S31C3                | S30C3                | S29C3                | S28C3                | S27C3                | S26C3                | S25C3                | S24C3    | XXXX XXXX            |

| F7Ch    | LCDDATA22                | S39C3 <sup>(2)</sup> | S38C3 <sup>(2)</sup> | S37C3 <sup>(2)</sup> | S36C3 <sup>(2)</sup> | S35C3 <sup>(2)</sup> | S34C3 <sup>(2)</sup> | S33C3 <sup>(2)</sup> | S32C3    | XXXX XXXX            |

| F7Dh    | LCDDATA23 <sup>(2)</sup> | S47C3                | S46C3                | S45C3                | S44C3                | S43C3                | S42C3                | S41C3                | S40C3    | XXXX XXXX            |

| F7Eh    | EECON2                   | EEPROM Co            | ontrol Register      | 2 (not a phys        | ical register)       | r                    | 1                    | r                    | 1        |                      |

| F7Fh    | EECON1                   | EEPGD                | CFGS                 | —                    | FREE                 | WRERR                | WREN                 | WR                   | RD       | xx-0 x000            |

| F80h    | PORTA                    | RA7                  | RA6                  | RA5                  | RA4                  | RA3                  | RA2                  | RA1                  | RA0      | xxxx xxxx            |

2: Unimplemented in 64-pin devices (PIC18F6XK90).

3: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

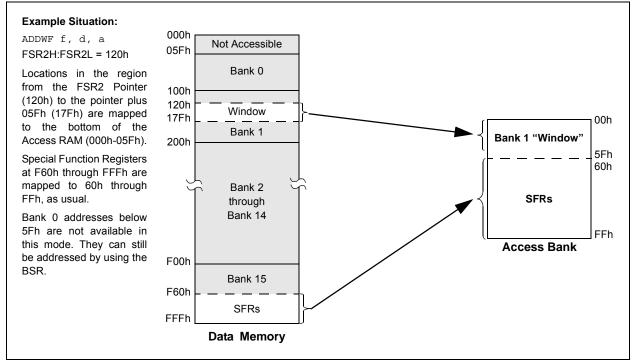

## 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space.

The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described. (See **Section 6.3.2 "Access Bank**".) An example of Access Bank remapping in this addressing mode is shown in Figure 6-10. Remapping the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit = 1) will continue to use Direct Addressing as before. Any Indirect or Indexed Addressing operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

## 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

## FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

### REGISTER 11-2: ODCON2: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 2

| R/W-0                  | R/W-0                 | R/W-0                                | R/W-0          | R/W-0                    | R/W-0            | R/W-0           | R/W-0  |

|------------------------|-----------------------|--------------------------------------|----------------|--------------------------|------------------|-----------------|--------|

| CCP100D <sup>(1)</sup> | CCP90D <sup>(1)</sup> | CCP8OD                               | CCP7OD         | CCP6OD                   | CCP5OD           | CCP4OD          | CCP3OD |

| oit 7                  |                       |                                      | I              |                          |                  |                 | bit C  |

|                        |                       |                                      |                |                          |                  |                 |        |

| Legend:                |                       |                                      |                |                          |                  |                 |        |

| R = Readable           | bit                   | W = Writable                         | bit            | U = Unimpler             | nented bit, read | l as '0'        |        |

| -n = Value at P        | OR                    | '1' = Bit is set                     |                | '0' = Bit is cle         | ared             | x = Bit is unkr | nown   |

|                        |                       |                                      |                |                          |                  |                 |        |

| bit 7                  | <b>CCP100D:</b> C     | CP10 Open-D                          | ain Output Er  | nable bit <sup>(1)</sup> |                  |                 |        |

|                        |                       | in capability is                     |                |                          |                  |                 |        |

|                        | -                     | in capability is                     |                | (4)                      |                  |                 |        |

| bit 6                  |                       | P9 Open-Drai                         | -              | ble bit <sup>(1)</sup>   |                  |                 |        |

|                        |                       | in capability is<br>in capability is |                |                          |                  |                 |        |

| bit 5                  | •                     | P8 Open-Drai                         |                | ole hit                  |                  |                 |        |

| bit 5                  |                       | in capability is                     | •              |                          |                  |                 |        |

|                        |                       | in capability is                     |                |                          |                  |                 |        |

| bit 4                  | CCP70D: CC            | P7 Open-Drai                         | n Output Enat  | ole bit                  |                  |                 |        |

|                        | 1 = Open-dra          | in capability is                     | enabled        |                          |                  |                 |        |

|                        | 0 = Open-dra          | in capability is                     | disabled       |                          |                  |                 |        |

| bit 3                  |                       | P6 Open-Drai                         | •              | ole bit                  |                  |                 |        |

|                        |                       | in capability is                     |                |                          |                  |                 |        |

|                        | •                     | in capability is                     |                |                          |                  |                 |        |

| bit 2                  |                       | P5 Open-Drai                         | •              | de bit                   |                  |                 |        |

|                        |                       | in capability is<br>in capability is |                |                          |                  |                 |        |

| bit 1                  | •                     | P4 Open-Drai                         |                | ole hit                  |                  |                 |        |

|                        |                       | in capability is                     | •              |                          |                  |                 |        |

|                        |                       | in capability is                     |                |                          |                  |                 |        |

| bit 0                  | CCP3OD: EC            | CP3 Open-Dra                         | ain Output Ena | able bit                 |                  |                 |        |

|                        | 1 = Open-dra          | in capability is                     | enabled        |                          |                  |                 |        |

|                        | 0 = Open-dra          | in capability is                     | disabled       |                          |                  |                 |        |

Note 1: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

## 11.6 PORTE, TRISE and LATE Registers

PORTE is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISE and LATE.

All pins on PORTE are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. The RE7 pin is also configurable for open-drain output when ECCP2 is active on this pin. Open-drain configuration is selected by setting the CCP2OD control bit (ODCON1<6>)

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

Each of the PORTE pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by clearing bit, REPU (PADCFG1<6>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on any device Reset.

Pins, RE<6:3>, are multiplexed with the LCD common drives. I/O port functions are available only on those PORTE pins according to which commons are active. The configuration is determined by the LMUX<1:0> control bits (LCDCON<1:0>). The availability is summarized in Table 11-9.

# TABLE 11-9:PORTE PINS AVAILABLE IN<br/>DIFFERENT LCD DRIVE<br/>CONFIGURATIONS<sup>(1)</sup>

| LCDCON<br><1:0> | Active LCD<br>Commons      | PORTE Pins<br>Available for I/O |

|-----------------|----------------------------|---------------------------------|

| 00              | COM0                       | RE6, RE5, RE4                   |

| 01              | COM0, COM1                 | RE6, RE5                        |

| 10              | COM0, COM1<br>and COM2     | RE6                             |

| 11              | All (COM0<br>through COM3) | None                            |

Note 1: If the LCD bias voltages are generated using the internal resistor ladder, the LCDBIASx pins are also available as I/O ports (RE0, RE1 and RE2). Pins, RE2, RE1 and RE0, are multiplexed with the functions of LCDBIAS3, LCDBIAS2 and LCDBIAS1. When LCD bias generation is required (in any application where the device is connected to an external LCD), these pins cannot be used as digital I/O. These pins can be used as digital I/O, however, when the internal resistor ladder is used for bias generation.

PORTE is also multiplexed with the Enhanced PWM Outputs B and C for ECCP1 and ECCP3, and Outputs B, C and D for ECCP2. For all devices, their default assignments are on PORTE<6:0>. On 80-pin devices, the multiplexing for the outputs of ECCP1 and ECCP3 is controlled by the ECCPMX Configuration bit. Clearing this bit reassigns the P1B/P1C and P3B/P3C outputs to PORTH.

RE7 is multiplexed with the LCD segment drive (SEG31) that is controlled by the LCDSE3<7> bit. I/O port function is only available when the segment is disabled. RE7 can also be configured as the alternate peripheral pin for the ECCP2 module. This is done by clearing the CCP2MX Configuration bit.

RE3 can also be configured as the Reference Clock Output (REFO) from the system clock. For further details, refer to **Section 3.7 "Reference Clock Output"**.

| EXAMPLE 11-5: | INITIALIZING PORTE |

|---------------|--------------------|

|               |                    |

| CLRF  | PORTE | ; Initialize PORTE by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATE  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 03h   | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISE | ; Set RE<1:0> as inputs |

|       |       | ; RE<7:2> as outputs    |

|       |       | -                       |

## 14.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- · Both registers are readable and writable

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

This module is controlled through the T2CON register (Register 14-1) that enables or disables the timer, and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 14-1.

## 14.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A 4-bit counter/prescaler on the clock input gives the prescale options of direct input, divide-by-4 or divide-by-16. These are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>).

The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/ postscaler. (See **Section 14.2 "Timer2 Interrupt**".)

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset (Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset [BOR])

TMR2 is not cleared when T2CON is written.

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 18-2, Register 18-3 and Register 19-2.

### REGISTER 14-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

### bit 7 Unimplemented: Read as '0'

| bit 6-3 | <b>T2OUTPS&lt;3:0&gt;:</b> Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale |

|---------|----------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                              |

|         | •                                                                                                              |

|         | 1111 = 1:16 Postscale                                                                                          |

| bit 2   | TMR2ON: Timer2 On bit                                                                                          |

|         | 1 = Timer2 is on                                                                                               |

|         | 0 = Timer2 is off                                                                                              |

| bit 1-0 | T2CKPS<1:0>: Timer2 Clock Prescale Select bits                                                                 |

|         | 00 = Prescaler is 1                                                                                            |

|         | 01 = Prescaler is 4                                                                                            |

|         | 1x = Prescaler is 16                                                                                           |

© 2009-2011 Microchip Technology Inc.

## 15.0 TIMER3/5/7 MODULES

The Timer3/5/7 timer/counter modules incorporate these features:

- Software-selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMRxH and TMRxL)

- Selectable clock source (internal or external) with device clock or SOSC oscillator internal options

- Interrupt-on-overflow

- · Module Reset on ECCP Special Event Trigger

Timer7 is unimplemented for devices with a program memory of 32 Kbytes (PIC18FX5K90).

**Note:** Throughout this section, generic references are used for register and bit names that are the same, except for an 'x' variable that indicates the item's association with the Timer3, Timer5 or Timer7 module. For example, the control register is named TxCON and refers to T3CON, T5CON and T7CON.

A simplified block diagram of the Timer3/5/7 module is shown in Figure 15-1.

The Timer3/5/7 module is controlled through the TxCON register (Register 15-1). It also selects the clock source options for the ECCP modules. (For more information, see **Section 19.1.1 "ECCP Module and Timer Resources"**.)

The Fosc clock source should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

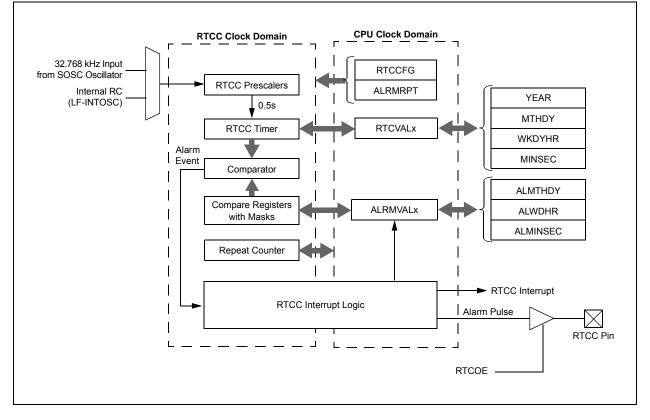

## 17.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

The key features of the Real-Time Clock and Calendar (RTCC) module are:

- Time: hours, minutes and seconds

- Twenty-four hour format (military time)

- Calendar: weekday, date, month and year

- · Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- · BCD format for compact firmware

- Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for an extended period with minimum to no intervention from the CPU. The module is optimized for low-power usage in order to provide extended battery life while keeping track of time.

The module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

Hours are measured in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

### FIGURE 17-1: RTCC BLOCK DIAGRAM

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ALRMEN CHIME AMASK3 AMASK2 AMASK1 AMASK0 ALRMPTR1 ALRMPTR0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 7 ALRMEN: Alarm Enable bit 1 = Alarm is enabled (cleared automatically after an alarm event whenever ALRMPTR<1:0> = 00 and CHIME = 0) 0 = Alarm is disabled bit 6 CHIME: Chime Enable bit 1 = Chime is enabled; ALRMPTR<1:0> bits are allowed to roll over from 00h to FFh 0 = Chime is disabled; ALRMPTR<1:0> bits stop once they reach 00h bit 5-2 AMASK<3:0>: Alarm Mask Configuration bits 0000 = Every half second 0001 = Every second 0010 = Every 10 seconds 0011 = Every minute 0100 = Every 10 minutes 0101 = Every hour 0110 = Once a day 0111 = Once a week 1000 = Once a month 1001 = Once a year (except when configured for February 29<sup>th</sup>, once every four years) 101x = Reserved – Do not use 11xx = Reserved – Do not use bit 1-0 ALRMPTR<1:0>: Alarm Value Register Window Pointer bits Points to the corresponding Alarm Value registers when reading the ALRMVALH and ALRMVALL registers. The ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches '00'. ALRMVALH: 00 = ALRMMIN 01 = ALRMWD 10 = ALRMMNTH 11 = Unimplemented ALRMVALL: 00 = ALRMSEC 01 = ALRMHR 10 = ALRMDAY 11 = Unimplemented

### **REGISTER 17-4: ALRMCFG: ALARM CONFIGURATION REGISTER**

NOTES:

### REGISTER 18-4: CCPRxL: CCPx PERIOD LOW BYTE REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxL7 | CCPRxL6 | CCPRxL5 | CCPRxL4 | CCPRxL3 | CCPRxL2 | CCPRxL1 | CCPRxL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 CCPRxL<7:0>: CCPx Period Register Low Byte bits <u>Capture Mode:</u> Capture register low byte. <u>Compare Mode:</u> Compare register low byte. <u>PWM Mode:</u> Duty Cycle register low byte.

### REGISTER 18-5: CCPRxH: CCPx PERIOD HIGH BYTE REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxH7 | CCPRxH6 | CCPRxH5 | CCPRxH4 | CCPRxH3 | CCPRxH2 | CCPRxH1 | CCPRxH0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 CCPRxH<7:0>: CCPx Period Register High Byte bits <u>Capture Mode:</u> Capture register high byte. <u>Compare Mode:</u> Compare register high byte. <u>PWM Mode:</u> Duty Cycle Buffer register high byte.

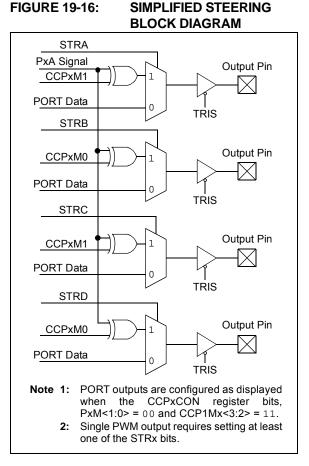

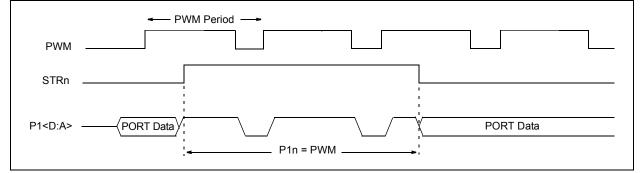

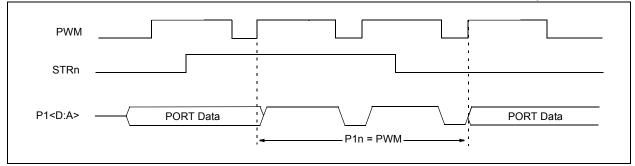

### 19.4.7.1 Steering Synchronization

The STRSYNC bit of the PSTRxCON register gives the user two choices for when the steering event will happen. When the STRSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the Px<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 19-17 and 19-18 illustrate the timing diagrams of the PWM steering depending on the STRSYNC setting.

### FIGURE 19-17: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRSYNC = 0)

#### FIGURE 19-18: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRSYNC = 1)

### 21.3.9 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full-power mode; in the case of the Sleep mode, all clocks are halted.

In Idle modes, a clock is provided to the peripherals. That clock can be from the primary clock source, the secondary clock (SOSC oscillator) or the INTOSC source. See **Section 3.3** "**Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set, and if enabled, will wake the device.

### 21.3.10 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 21.3.11 BUS MODE COMPATIBILITY

Table 21-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |

|-------------------|--------------------|-----|--|

| Terminology       | СКР                | CKE |  |

| 0, 0              | 0                  | 1   |  |

| 0, 1              | 0                  | 0   |  |

| 1, 0              | 1                  | 1   |  |

| 1, 1              | 1                  | 0   |  |

There is also an SMP bit which controls when the data is sampled.

## 21.3.12 SPI CLOCK SPEED AND MODULE INTERACTIONS

Because MSSP1 and MSSP2 are independent modules, they can operate simultaneously at different data rates. Setting the SSPM<3:0> bits of the SSPxCON1 register determines the rate for the corresponding module.

An exception is when both modules use Timer2 as a time base in Master mode. In this instance, any changes to the Timer2 module's operation will affect both MSSP modules equally. If different bit rates are required for each module, the user should select one of the other three time base options for one of the modules.

| DAW                           | Decimal A                     | djust W Regis                                                           | ter                           | DECF              | Decrement                                                            | f                                                                                      |                                           |

|-------------------------------|-------------------------------|-------------------------------------------------------------------------|-------------------------------|-------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------|

| Syntax:                       | DAW                           |                                                                         |                               | Syntax:           | DECF f{,c                                                            | 1 {,a}}                                                                                |                                           |

| Operands:                     | None                          |                                                                         |                               | Operands:         | $0 \leq f \leq 255$                                                  |                                                                                        |                                           |

| Operation:                    | •                             | > 9] or [DC = 1<br>6 → W<3:0>;                                          | ], then                       |                   | d ∈ [0,1]<br>a ∈ [0,1]                                               |                                                                                        |                                           |

|                               | else,                         | o , ele ,                                                               |                               | Operation:        | (f) – 1 $\rightarrow$ de                                             | est                                                                                    |                                           |

|                               | (W<3:0>) –                    | → W<3:0>;                                                               |                               | Status Affected:  | C, DC, N, 0                                                          | DV, Z                                                                                  |                                           |

|                               | lf [W<7:4>                    | > 9] or [C = 1],                                                        | then                          | Encoding:         | 0000                                                                 | 01da ff                                                                                | ff ffff                                   |

|                               | (W<7:4>) +<br>C = 1;<br>else, | $6 \rightarrow W < 7:4>;$                                               |                               | Description:      | result is sto                                                        | register 'f'. If<br>red in W. If 'c<br>red back in re                                  | l' is '1', the                            |

| Statua Affaatad               | (W<7:4>) –                    | → W<7:4>                                                                |                               |                   | ,                                                                    |                                                                                        | ank is selected.                          |

| Status Affected:<br>Encoding: | C                             | 0000 000                                                                | 0 0111                        |                   | lf 'a' is '1', t<br>GPR bank.                                        |                                                                                        | ed to select the                          |

| Description:<br>Words:        | resulting fro<br>variables (e | the 8-bit valu<br>om the earlier a<br>each in packed<br>es a correct pa | ddition of two<br>BCD format) |                   | set is enabl<br>in Indexed<br>mode wher<br>Section 29<br>Bit-Oriente | ed, this instru<br>Literal Offset<br>never f ≤ 95 (5<br>.2.3 "Byte-O<br>ed Instruction | 5Fh). See<br>riented and<br>ns in Indexed |

|                               | 1                             |                                                                         |                               |                   |                                                                      | set Mode" fo                                                                           | r details.                                |

| Cycles:                       | I                             |                                                                         |                               | Words:            | 1                                                                    |                                                                                        |                                           |

| Q Cycle Activity:<br>Q1       | Q2                            | Q3                                                                      | Q4                            | Cycles:           | 1                                                                    |                                                                                        |                                           |

| Decode                        | Read                          | Process                                                                 | Write                         | Q Cycle Activity: |                                                                      |                                                                                        |                                           |

|                               | register W                    | Data                                                                    | W                             | Q1                | Q2                                                                   | Q3                                                                                     | Q4                                        |

| Example 1:                    | DAW                           |                                                                         |                               | Decode            | Read<br>register 'f'                                                 | Process<br>Data                                                                        | Write to destination                      |

| Before Instruc                | ction                         |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

| W                             | = A5h                         |                                                                         |                               | Example:          | DECF (                                                               | CNT, 1, (                                                                              | 0                                         |

| C<br>DC                       | = 0<br>= 0                    |                                                                         |                               | Before Instruc    |                                                                      |                                                                                        |                                           |

| After Instructi               | on                            |                                                                         |                               | CNT<br>Z          | = 01h<br>= 0                                                         |                                                                                        |                                           |

| W                             | = 05h                         |                                                                         |                               | After Instruction | 0                                                                    |                                                                                        |                                           |

| C<br>DC                       | = 1<br>= 0                    |                                                                         |                               | CNT<br>Z          | = 00h<br>= 1                                                         |                                                                                        |                                           |

| Example 2:                    |                               |                                                                         |                               | L                 | - 1                                                                  |                                                                                        |                                           |

| Before Instruc                | ction                         |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

| W                             | = CEh                         |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

| C<br>DC                       | = 0<br>= 0                    |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

| After Instruction             | 0                             |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

| W                             | = 34h                         |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

| C<br>DC                       | = 1<br>= 0                    |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

|                               | = 0                           |                                                                         |                               |                   |                                                                      |                                                                                        |                                           |

| RRN                         | CF                                                                                                                                        | Rotate Rig                                                                                         | ght f (No                                                        | Carry                       | )                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|---------------------------------------------------|

| Synta                       | ax:                                                                                                                                       | RRNCF                                                                                              | f {,d {,a}}                                                      |                             |                                                   |

| Oper                        | ands:                                                                                                                                     | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                              | 5                                                                |                             |                                                   |

| Oper                        | ation:                                                                                                                                    | $(f \le n >) \rightarrow c$<br>$(f \le 0 >) \rightarrow c$                                         |                                                                  | .>,                         |                                                   |

| Statu                       | is Affected:                                                                                                                              | N, Z                                                                                               |                                                                  |                             |                                                   |

| Enco                        | oding:                                                                                                                                    | 0100                                                                                               | 00da                                                             | fff                         | f ffff                                            |

| Desc                        | ription:                                                                                                                                  | one bit to                                                                                         | the right. I<br>n W. If 'd'                                      | f 'd' is<br>is '1',         | ' are rotated<br>'0', the result<br>the result is |

|                             |                                                                                                                                           |                                                                                                    | overriding<br>the bank                                           | the BS                      | nk will be<br>SR value. If 'a'<br>e selected as   |

|                             |                                                                                                                                           | set is enal<br>in Indexed<br>mode whe<br><b>Section 2</b>                                          | bled, this i<br>Literal O<br>never f ≤<br>9.2.3 "By<br>ed Instru | ffset A<br>95 (5F<br>te-Ori | h). See<br>ented and<br>s in Indexed              |

|                             |                                                                                                                                           |                                                                                                    |                                                                  |                             | uetalis.                                          |

|                             |                                                                                                                                           | Г                                                                                                  |                                                                  | egister                     |                                                   |

| Word                        | is:                                                                                                                                       | 1                                                                                                  |                                                                  |                             |                                                   |

|                             |                                                                                                                                           | 1                                                                                                  |                                                                  |                             |                                                   |

| Cycle                       | es:                                                                                                                                       |                                                                                                    |                                                                  |                             |                                                   |

| Cycle                       |                                                                                                                                           |                                                                                                    |                                                                  | egister                     |                                                   |

| Cycle                       | es:<br>ycle Activity:                                                                                                                     | 1                                                                                                  | ► re                                                             | egister                     | f                                                 |

| Cycle                       | es:<br>ycle Activity:<br>Q1                                                                                                               | 1<br>Q2                                                                                            | ► re<br>Q3                                                       | egister                     | f A                                               |

| Cycle<br>Q C<br><u>Exan</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:                                                                                          | 1<br>Q2<br>Read<br>register 'f'                                                                    | Q3<br>Proce                                                      | egister                     | f<br>Q4<br>Write to                               |

| Cycle<br>Q C<br><u>Exan</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruc<br>REG                                                                 | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101                                         | Q3<br>Proce<br>Data<br>REG, 1,                                   | egister                     | f<br>Q4<br>Write to                               |

| Cycle<br>Q C<br><u>Exan</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruc                                                                        | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101                                         | ► re<br>Q3<br>Proce<br>Data<br>REG, 1,<br>0111                   | egister                     | f<br>Q4<br>Write to                               |

| Cycle<br>Q C<br><u>Exan</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruct<br>REG<br>After Instruction                                           | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on                                   | Q3<br>Proce<br>Data<br>REG, 1,<br>0111                           | egister<br>3<br>ess<br>a    | f<br>Q4<br>Write to                               |

| Cycle<br>Q C<br><u>Exan</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG<br>nple 2:<br>Before Instruct<br>W | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on<br>= 1110<br>RRNCF<br>tion<br>= ? | Q3<br>Proce<br>Data<br>REG, 1,<br>0111<br>1011<br>REG, 0,        | egister<br>3<br>ess<br>a    | f<br>Q4<br>Write to                               |

| Cycle<br>Q C<br><u>Exan</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG<br>nple 2:<br>Before Instruc       | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>RRNCF<br>tion<br>= ?<br>= 1101       | Q3<br>Proce<br>Data<br>REG, 1,<br>0111<br>1011<br>REG, 0,        | egister<br>3<br>ess<br>a    | f<br>Q4<br>Write to                               |

| SETF                                                           | Set f                                                                                                   |                                                                |                                                                   |                                                |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------|

| Syntax:                                                        | SETF f{,;                                                                                               | a}                                                             |                                                                   |                                                |

| Operands:                                                      | $0 \leq f \leq 255$                                                                                     |                                                                |                                                                   |                                                |

|                                                                | <b>a</b> ∈ [0,1]                                                                                        |                                                                |                                                                   |                                                |

| Operation:                                                     | $FFh\tof$                                                                                               |                                                                |                                                                   |                                                |

| Status Affected:                                               | None                                                                                                    |                                                                |                                                                   |                                                |

| Encoding:                                                      | 0110                                                                                                    | 100a                                                           | ffff                                                              | ffff                                           |

| Description:                                                   | The conten are set to F                                                                                 |                                                                | specified                                                         | register                                       |

|                                                                | lf 'a' is '0', t<br>lf 'a' is '1', t<br>GPR bank.                                                       |                                                                |                                                                   |                                                |

|                                                                | If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offs | led, this i<br>Literal O<br>never f ≤<br>.2.3 "By<br>ed Instru | nstruction<br>ffset Addre<br>95 (5Fh).<br>te-Oriente<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |

| Words:                                                         | 1                                                                                                       |                                                                |                                                                   |                                                |

| Cycles:                                                        | 1                                                                                                       |                                                                |                                                                   |                                                |

| Q Cycle Activity:                                              |                                                                                                         |                                                                |                                                                   |                                                |

| Q1                                                             | Q2                                                                                                      | Q3                                                             | 1                                                                 | Q4                                             |

| Decode                                                         | Read<br>register 'f'                                                                                    | Proce<br>Data                                                  |                                                                   | Write<br>gister 'f'                            |

| Example:<br>Before Instruct<br>REG<br>After Instruction<br>REG | = 5A                                                                                                    | h                                                              | G,1                                                               |                                                |

| MOVSS                                              | Move Indexed to Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|