Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 69                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f85k90-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                            | Pin Number | Pin                     | Buffer                                        | Description                                                                                                                                                   |  |  |

|-------------------------------------------------------------------------------------|------------|-------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                            | QFN/TQFP   | Туре                    | Туре                                          | Description                                                                                                                                                   |  |  |

|                                                                                     |            |                         |                                               | PORTA is a bidirectional I/O port.                                                                                                                            |  |  |

| RA0/AN0/ULPWU<br>RA0<br>AN0<br>ULPWU                                                | 24         | I/O<br>I<br>I           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 0.<br>Ultra Low-Power Wake-up (ULPW) input.                                                                                      |  |  |

| RA1/AN1/SEG18<br>RA1<br>AN1<br>SEG18                                                | 23         | I/O<br>I<br>O           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 1.<br>SEG18 output for LCD.                                                                                                      |  |  |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF-                                                | 22         | I/O<br>I<br>I           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.                                                                                         |  |  |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                                                | 21         | I/O<br>I<br>I           | TTL<br>Analog<br>Analog                       | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input.                                                                                        |  |  |

| RA4/T0CKI/SEG14<br>RA4<br>T0CKI<br>SEG14                                            | 28         | I/O<br>I<br>O           | ST<br>ST<br>Analog                            | Digital I/O.<br>Timer0 external clock input.<br>SEG14 output for LCD.                                                                                         |  |  |

| RA5/AN4/SEG15/T1CKI/<br>T3G/HLVDIN<br>RA5<br>AN4<br>SEG15<br>T1CKI<br>T3G<br>HLVDIN | 27         | I/O<br>I<br>O<br>I<br>I | TTL<br>Analog<br>Analog<br>ST<br>ST<br>Analog | Digital I/O.<br>Analog Input 4.<br>SEG15 output for LCD.<br>Timer1 clock input.<br>Timer3 external clock gate input.<br>High/Low-Voltage Detect (HLVD) input. |  |  |

| RA6                                                                                 |            |                         |                                               | See the OSC2/CLKO/RA6 pin.                                                                                                                                    |  |  |

| RA7                                                                                 |            |                         |                                               | See the OSC1/CLKI/RA7 pin.                                                                                                                                    |  |  |

| $ST = Schm$ $I = Input$ $P = Powe$ $I^{2}C^{TM} = I^{2}C/SI$                        | MBus       | : with C                |                                               | CMOS = CMOS compatible input or output<br>els Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)<br>2MX Configuration bit is set.     |  |  |

## TABLE 1-3: PIC18F6XK90 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K90 and PIC18F85K90 devices.

| Pin Name  | Function | TRIS<br>Setting | I/O | I/O Type         | Description                                                                                   |

|-----------|----------|-----------------|-----|------------------|-----------------------------------------------------------------------------------------------|

| RD0/SEG0/ | RD0      | 0               | 0   | DIG              | LATD<0> data output.                                                                          |

| CTPLS     |          | 1               | I   | ST               | PORTD<0> data input.                                                                          |

|           | SEG0     | 1               | 0   | ANA              | LCD Segment 0 output; disables all other pin functions.                                       |

|           | CTPLS    | x               | 0   | DIG              | CTMU pulse generator output.                                                                  |

| RD1/SEG1/ | RD1      | 0               | 0   | DIG              | LATD<1> data output.                                                                          |

| T5CKI/T7G |          | 1               | Ι   | ST               | PORTD<1> data input.                                                                          |

|           | SEG1     | 1               | 0   | ANA              | LCD Segment 1 output; disables all other pin functions.                                       |

|           | T5CKI    | x               | Ι   | ST               | Timer5 clock input.                                                                           |

|           | T7G      | x               | Ι   | ST               | Timer7 external clock gate input.                                                             |

| RD2/SEG2  | RD2      | 0               | 0   | DIG              | LATD<2> data output.                                                                          |

|           |          | 1               | I   | ST               | PORTD<2> data input.                                                                          |

|           | SEG2     | 1               | 0   | ANA              | LCD Segment 2 output; disables all other pin functions.                                       |

| RD3/SEG3  | RD3      | 0               | 0   | DIG              | LATD<3> data output.                                                                          |

|           |          | 1               | I   | ST               | PORTD<3> data input.                                                                          |

|           | SEG3     | 1               | 0   | ANA              | LCD Segment 3 output; disables all other pin functions.                                       |

| RD4/SEG4/ | RD4      | 0               | 0   | DIG              | LATD<4> data output.                                                                          |

| SDO2      |          | 1               | I   | ST               | PORTD<4> data input.                                                                          |

|           | SEG4     | 1               | 0   | ANA              | LCD Segment 4 output; disables all other pin functions.                                       |

|           | SDO2     | 0               | Р   | DOG              | SPI data output (MSSP module).                                                                |

| RD5/SEG5/ | RD5      | 0               | 0   | DIG              | LATD<5> data output.                                                                          |

| SDI2/SDA2 |          | 1               | I   | ST               | PORTD<5> data input.                                                                          |

|           | SEG5     | 1               | 0   | ANA              | LCD Segment 5 output; disables all other pin functions.                                       |

|           | SDI2     | 1               | I   | ST               | SPI data input (MSSP module).                                                                 |

|           | SDA2     | 0               | 0   | l <sup>2</sup> C | I <sup>2</sup> C <sup>™</sup> data input (MSSP module). Input type depends on module setting. |

|           |          | 1               | I   | ANA              | LCD Segment 5 output; disables all other pin functions.                                       |

| RD6/SEG6/ | RD6      | 0               | 0   | DIG              | LATD<6> data output.                                                                          |

| SCK2/SCL2 |          | 1               | I   | ST               | PORTD<6> data input.                                                                          |

|           | SEG6     | 1               | 0   | ANA              | LCD Segment 6 output; disables all other pin functions.                                       |

|           | SCK2     | 0               | 0   | DIG              | SPI clock output (MSSP module); takes priority over port data.                                |

|           |          | 1               | I   | ST               | SPI clock input (MSSP module).                                                                |

|           | SCL2     | 0               | 0   | DIG              | I <sup>2</sup> C clock output (MSSP module); takes priority over port data.                   |

|           |          | 1               | I   | l <sup>2</sup> C | I <sup>2</sup> C clock input (MSSP module). Input type depends on module setting.             |

| RD7/SEG7/ | RD7      | 0               | 0   | DIG              | LATD<7> data output.                                                                          |

| SS2       |          | 1               | I   | ST               | PORTD<7> data input.                                                                          |

|           | SEG7     | 1               | I   | ANA              | LCD Segment 7 output; disables all other pin functions.                                       |

|           | SS2      | 1               | I   | TTL              | Slave select input for MSSP module.                                                           |

TABLE 11-7: PORTD FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,  $I^2C = I^2C$  Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

### 13.8.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. (For timing details, see Figure 13-5.)

The T1GVAL bit (T1GCON<2>) indicates when the Toggled mode is active and the timer is counting.

The Timer1 Gate Toggle mode is enabled by setting the T1GTM bit (T1GCON<5>). When T1GTM is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| TMR1GE |                                                                                                           |

|--------|-----------------------------------------------------------------------------------------------------------|

| T1GPOL | [                                                                                                         |

| T1GTM  |                                                                                                           |

| T1G_IN |                                                                                                           |

| T1CKI  |                                                                                                           |

| T1GVAL |                                                                                                           |

| Timer1 | $N = \frac{1}{2} \sqrt{N+1} \sqrt{N+2} \sqrt{N+3} \sqrt{N+4} \sqrt{N+5} \sqrt{N+6} \sqrt{N+7} \sqrt{N+8}$ |

|        |                                                                                                           |

#### FIGURE 13-5: TIMER1 GATE TOGGLE MODE

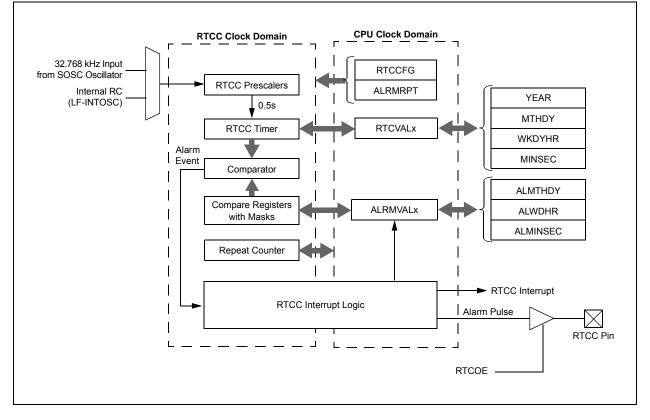

# 17.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

The key features of the Real-Time Clock and Calendar (RTCC) module are:

- Time: hours, minutes and seconds

- Twenty-four hour format (military time)

- Calendar: weekday, date, month and year

- · Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- · BCD format for compact firmware

- Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for an extended period with minimum to no intervention from the CPU. The module is optimized for low-power usage in order to provide extended battery life while keeping track of time.

The module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

Hours are measured in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

#### FIGURE 17-1: RTCC BLOCK DIAGRAM

NOTES:

### REGISTER 18-4: CCPRxL: CCPx PERIOD LOW BYTE REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxL7 | CCPRxL6 | CCPRxL5 | CCPRxL4 | CCPRxL3 | CCPRxL2 | CCPRxL1 | CCPRxL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 CCPRxL<7:0>: CCPx Period Register Low Byte bits <u>Capture Mode:</u> Capture register low byte. <u>Compare Mode:</u> Compare register low byte. <u>PWM Mode:</u> Duty Cycle register low byte.

### REGISTER 18-5: CCPRxH: CCPx PERIOD HIGH BYTE REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxH7 | CCPRxH6 | CCPRxH5 | CCPRxH4 | CCPRxH3 | CCPRxH2 | CCPRxH1 | CCPRxH0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 CCPRxH<7:0>: CCPx Period Register High Byte bits <u>Capture Mode:</u> Capture register high byte. <u>Compare Mode:</u> Compare register high byte. <u>PWM Mode:</u> Duty Cycle Buffer register high byte.

| R/W-0                 | R/W-0                                                | R/W-0                                                                                                                                                                                                      | R/W-0                      | R/W-0                     | R/W-0            | R/W-0                 | R/W-0          |  |  |  |  |

|-----------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|------------------|-----------------------|----------------|--|--|--|--|

| PxM1                  | PxM0                                                 | DCxB1                                                                                                                                                                                                      | DCxB0                      | CCPxM3                    | CCPxM2           | CCPxM1                | CCPxM0         |  |  |  |  |

| bit 7                 | •                                                    |                                                                                                                                                                                                            |                            | ·                         | •                | •                     | bit            |  |  |  |  |

|                       |                                                      |                                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

| Legend:<br>R = Readab | le hit                                               | W = Writable                                                                                                                                                                                               | hit                        | II = I Inimpler           | mented bit, read | d as 'O'              |                |  |  |  |  |

| -n = Value at         |                                                      | '1' = Bit is set                                                                                                                                                                                           |                            | '0' = Bit is cle          |                  | x = Bit is unk        | nown           |  |  |  |  |

|                       |                                                      |                                                                                                                                                                                                            | •                          |                           | arcu             |                       |                |  |  |  |  |

| bit 7-6               | <b>PxM&lt;1:0&gt;:</b> E                             | Enhanced PWM                                                                                                                                                                                               | l Output Confi             | guration bits             |                  |                       |                |  |  |  |  |

|                       | If CCPxM<3:                                          | 2> = 00, 01, 10                                                                                                                                                                                            | <u>):</u>                  | -                         |                  |                       |                |  |  |  |  |

|                       | xx = PxA is                                          | assigned as a c                                                                                                                                                                                            | apture/compar              | e input/output; I         | PxB, PxC and P   | xD are assigned       | d as PORT pin  |  |  |  |  |

|                       | If CCPxM<3:                                          |                                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | output: PxA, P                                                                                                                                                                                             | xB, PxC and                | PxD are contro            | olled by steerin | g (see <b>Section</b> | 19.4.7 "Puls   |  |  |  |  |

|                       |                                                      | n <b>g Mode"</b> )<br>idae output forv                                                                                                                                                                     | vard <sup>.</sup> PxD is n | odulated <sup>.</sup> PxA | is active: PxB   | PxC are inactiv       | /e             |  |  |  |  |

|                       |                                                      | <ul> <li>1 = Full-bridge output forward: PxD is modulated; PxA is active; PxB, PxC are inactive</li> <li>0 = Half-bridge output: PxA, PxB are modulated with dead-band control; PxC and PxD are</li> </ul> |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | ied as PORT pi                                                                                                                                                                                             |                            |                           |                  |                       |                |  |  |  |  |

|                       | 11 = Full-br                                         | idge output revo                                                                                                                                                                                           | erse: PxB is m             | nodulated; PxC            | is active; PxA   | and PxD are in        | active         |  |  |  |  |

| bit 5-4               | DCxB<1:0>:                                           | DCxB<1:0>: PWM Duty Cycle Bit 1 and Bit 0                                                                                                                                                                  |                            |                           |                  |                       |                |  |  |  |  |

|                       | Capture mode:                                        |                                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       | Unused.                                              |                                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       | <u>Compare mo</u><br>Unused.                         | <u>de:</u>                                                                                                                                                                                                 |                            |                           |                  |                       |                |  |  |  |  |

|                       | PWM mode:                                            |                                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | e the two LSbs                                                                                                                                                                                             | of the 10-bit F            | WM duty cycle             | e. The eight MS  | bs of the duty c      | ycle are found |  |  |  |  |

|                       | in CCPRxL.                                           |                                                                                                                                                                                                            |                            |                           | C C              | -                     | -              |  |  |  |  |

| bit 3-0               | CCPxM<3:0                                            | >: ECCPx Mode                                                                                                                                                                                              | e Select bits              |                           |                  |                       |                |  |  |  |  |

|                       | 0000 = Capture/Compare/PWM off (resets ECCPx module) |                                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | 0001 = Reserved                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | npare mode: to                                                                                                                                                                                             | ggle output or             | match                     |                  |                       |                |  |  |  |  |

|                       |                                                      | 0011 = Capture mode<br>0100 = Capture mode: every falling edge                                                                                                                                             |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | oture mode: eve                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       | 0110 = Cap                                           | oture mode: eve                                                                                                                                                                                            | ry fourth rising           | g edge                    |                  |                       |                |  |  |  |  |

|                       |                                                      | 111 = Capture mode: every 16 <sup>th</sup> rising edge<br>.000 = Compare mode: initialize the ECCPx pin low; set the output on a compare match (set CCPxIF)                                                |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      |                                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | npare mode: init<br>npare mode: ge                                                                                                                                                                         |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | npare mode: tri                                                                                                                                                                                            |                            |                           |                  |                       |                |  |  |  |  |

|                       | sets                                                 | CCxIF bit)                                                                                                                                                                                                 |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | M mode: PxA a                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |  |

|                       |                                                      | M mode: PxA a                                                                                                                                                                                              |                            | •                         |                  |                       |                |  |  |  |  |

|                       | 1110 = PW                                            | M mode: PxA a                                                                                                                                                                                              | nd PxC are a               | ctive-low; PxB a          | and PXD are ac   | tive-nigh             |                |  |  |  |  |

## REGISTER 19-1: CCPxCON: ENHANCED CAPTURE/COMPARE/PWM x CONTROL

1110 = PWM mode: PxA and PxC are active-low; PxB and PxD are active-high 1111 = PWM mode: PxA and PxC are active-low; PxB and PxD are active-low

# 20.1 LCD Registers

The LCD driver module has 32 registers:

- LCD Control Register (LCDCON)

- LCD Phase Register (LCDPS)

- LCD Reference Ladder Register (LCDRL)

- LCD Reference Voltage Control Register (LCDREF)

- Six LCD Segment Enable Registers (LCDSE5:LCDSE0)

- 24 LCD Data Registers (LCDDATA23:LCDDATA0)

The LCDCON register, shown in Register 20-1, controls the overall operation of the module. Once the module is configured, the LCDEN (LCDCON<7>) bit is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN (LCDCON<6>) bit.

The LCDPS register, shown in Register 20-2, configures the LCD clock source prescaler and the type of waveform, Type-A or Type-B. For details on these features, see Section 20.2 "LCD Clock Source Selection", Section 20.3 "LCD Bias Types" and Section 20.8 "LCD Waveform Generation".

| R/W-0 | R/W-0 | R/C-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-------|-------|-------|-------|

| LCDEN | SLPEN | WERR  | —   | CS1   | CS0   | LMUX1 | LMUX0 |

| bit 7 |       |       |     |       |       |       | bit 0 |

### REGISTER 20-1: LCDCON: LCD CONTROL REGISTER

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | LCDEN: LCD Driver Enable bit<br>1 = LCD driver module is enabled<br>0 = LCD driver module is disabled                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>SLPEN:</b> LCD Driver Enable in Sleep mode bit<br>1 = LCD driver module is disabled in Sleep mode<br>0 = LCD driver module is enabled in Sleep mode |

| bit 5   | WERR: LCD Write Failed Error bit<br>1 = LCDDATAx register is written while WA (LCDPS<4>) = 0 (must be cleared in software)<br>0 = No LCD write error   |

| bit 4   | Unimplemented: Read as '0'                                                                                                                             |

| bit 3-2 | <b>CS&lt;1:0&gt;:</b> Clock Source Select bits<br>00 = (Fosc/4)/8192<br>01 = SOSC oscillator/32<br>1x = INTRC (31.25 kHz)/32                           |

| bit 1-0 | LMUX<1:0>: Commons Select bits                                                                                                                         |

| LMUX<1:0> | Multiplex      | Maximum<br>Number of Pixels<br>(PIC18F6X90) | Maximum<br>Number of Pixels<br>(PIC18F8X90) | Bias       |

|-----------|----------------|---------------------------------------------|---------------------------------------------|------------|

| 00        | Static (COM0)  | 33                                          | 48                                          | Static     |

| 01        | 1/2 (COM<1:0>) | 66                                          | 96                                          | 1/2 or 1/3 |

| 10        | 1/3 (COM<2:0>) | 99                                          | 144                                         | 1/2 or 1/3 |

| 11        | 1/4 (COM<3:0>) | 132                                         | 192                                         | 1/3        |

| REGISTER 2    | 21-6: SSPx                                              | CON2: MSSF                                             | Px CONTRO        | L REGISTER                                             | 2 (I <sup>2</sup> C™ SLA | VE MODE)        |                    |

|---------------|---------------------------------------------------------|--------------------------------------------------------|------------------|--------------------------------------------------------|--------------------------|-----------------|--------------------|

| R/W-0         | R/W-0                                                   | R/W-0                                                  | R/W-0            | R/W-0                                                  | R/W-0                    | R/W-0           | R/W-0              |

| GCEN          | ACKSTAT                                                 | ADMSK5                                                 | ADMSK4           | ADMSK3                                                 | ADMSK2                   | ADMSK1          | SEN <sup>(1)</sup> |

| bit 7         |                                                         |                                                        |                  |                                                        |                          |                 | bit 0              |

| Legend:       |                                                         |                                                        |                  |                                                        |                          |                 |                    |

| R = Readable  | e bit                                                   | W = Writable                                           | bit              | U = Unimplem                                           | nented bit, read         | 1 as '0'        |                    |

| -n = Value at | POR                                                     | '1' = Bit is set                                       |                  | '0' = Bit is clea                                      | ared                     | x = Bit is unkn | own                |

| bit 7         | 1 = Enables ir                                          | ral Call Enable<br>nterrupt when a<br>all address is c | a general call a | ddress (0000h)                                         | ) is received in         | the SSPxSR      |                    |

| bit 6         | ACKSTAT: Ac<br>Unused in Sla                            | knowledge Sta                                          | atus bit         |                                                        |                          |                 |                    |

| bit 5-2       | 1 = Masking c                                           | of correspondin                                        | g bits of SSPx   | t bits (5-Bit Add<br>ADD is enableo<br>ADD is disableo | j t                      | mode)           |                    |

| bit 1         | <u>In 7-Bit Addre</u><br>1 = Masking c<br>0 = Masking c | <u>ssing mode:</u><br>of SSPxADD<1<br>of SSPxADD<1     | > only is enab   |                                                        | lect bit                 |                 |                    |

| bit 0         | 0                                                       | of SSPxADD<1<br>of SSPxADD<1                           |                  |                                                        |                          |                 |                    |

**Note 1:** If the I<sup>2</sup>C module is active, this bit may not be set (no spooling) and the SSPxBUF may not be written to (or writes to the SSPxBUF are disabled).

| REGISTER 21-7: SSPxM | SK: $I^2 C^{TM}$ SLAVE ADDRESS MASK REGISTER (7-BIT MASKING MODE) <sup>(1)</sup> |

|----------------------|----------------------------------------------------------------------------------|

|----------------------|----------------------------------------------------------------------------------|

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(2)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 MSK<7:0>: Slave Address Mask Select bit

1 = Masking of the corresponding bit of SSPxADD is enabled

0 = Masking of the corresponding bit of SSPxADD is disabled

Note 1: This register shares the same SFR address as SSPxADD and is only addressable in select MSSPx operating modes. See Section 21.4.3.4 "7-Bit Address Masking Mode" for more details.

2: MSK0 is not used as a mask bit in 7-bit addressing.

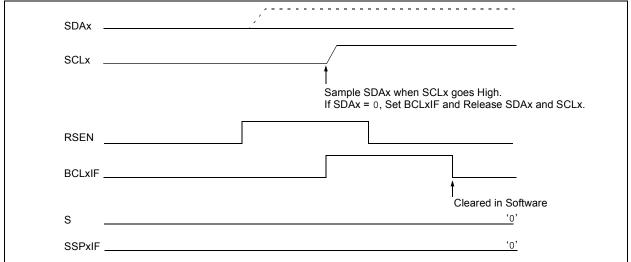

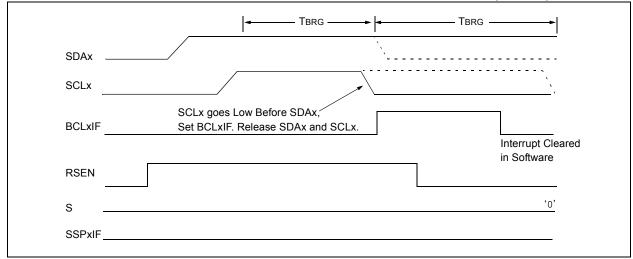

# 21.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from a low level to a high level.

- b) SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD<6:0> and counts down to 0. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled.

If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 21-31). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 21-32).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

### FIGURE 21-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 21-32: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

| R/W-0                         | R-1                                | R/W-0                                                   | R/W-0            | R/W-0                             | U-0             | R/W-0           | R/W-0          |

|-------------------------------|------------------------------------|---------------------------------------------------------|------------------|-----------------------------------|-----------------|-----------------|----------------|

| ABDOVF                        | RCIDL                              | RXDTP                                                   | TXCKP            | BRG16                             |                 | WUE             | ABDEN          |

| bit 7                         | •                                  |                                                         | •                |                                   |                 |                 | bit            |

| <u> </u>                      |                                    |                                                         |                  |                                   |                 |                 |                |

| <b>Legend:</b><br>R = Readabl | o hit                              | M = Mritabla                                            | hit              | II – Unimplom                     | onted hit read  | L a a 'O'       |                |

| -n = Value at                 |                                    | W = Writable<br>'1' = Bit is set                        |                  | U = Unimplem<br>'0' = Bit is clea |                 |                 | 2014/2         |

|                               | PUR                                | I = DILIS SEL                                           |                  | U = BILIS CIER                    | reu             | x = Bit is unki | IOWI           |

| bit 7                         | ABDOVF: A                          | uto-Baud Acqui                                          | sition Rollover  | Status bit                        |                 |                 |                |

|                               |                                    | ollover has occ<br>rollover has oc                      | •                | uto-Baud Rate [                   | Detect mode (n  | nust be cleare  | d in software) |

| bit 6                         | RCIDL: Rece                        | eive Operation I                                        | dle Status bit   |                                   |                 |                 |                |

|                               |                                    | operation is Idle operation is act                      |                  |                                   |                 |                 |                |

| bit 5                         | RXDTP: Dat                         | a/Receive Polar                                         | ity Select bit   |                                   |                 |                 |                |

|                               |                                    | <u>ıs mode:</u><br>data (RXx) is in<br>data (RXx) is no |                  |                                   |                 |                 |                |

|                               | <u>Synchronous</u><br>1 = Data (DT |                                                         | ctive-low)       |                                   |                 |                 |                |

| bit 4                         | -                                  | chronous Clock                                          |                  |                                   |                 |                 |                |

|                               | Asynchronou                        |                                                         |                  |                                   |                 |                 |                |

|                               | 1 = Idle state                     | e for transmit (T)<br>e for transmit (T)                | ,                |                                   |                 |                 |                |

|                               | Synchronous                        |                                                         | , ,              |                                   |                 |                 |                |

|                               |                                    | e for clock (CKx)<br>e for clock (CKx)                  |                  |                                   |                 |                 |                |

| bit 3                         | BRG16: 16-                         | Bit Baud Rate R                                         | egister Enable   | bit                               |                 |                 |                |

|                               |                                    |                                                         |                  | Hx and SPBRG> only (Compatibl     |                 | RGHx value is   | ignored        |

| bit 2                         | Unimpleme                          | nted: Read as '                                         | כי               |                                   |                 |                 |                |

| bit 1                         | WUE: Wake                          | -up Enable bit                                          |                  |                                   |                 |                 |                |

|                               | cleared                            |                                                         | the following ri |                                   | rupt is generat | ed on the falli | ng edge; bit   |

|                               | Synchronous<br>Unused in th        |                                                         |                  |                                   |                 |                 |                |

| bit 0                         | ABDEN: Aut                         | o-Baud Detect                                           | Enable bit       |                                   |                 |                 |                |

|                               | cleared                            |                                                         | on completion.   | e next characte                   | r. Requires rec | ception of a Sy | vnc field (55h |

|                               | Synchronous                        |                                                         |                  | compicted                         |                 |                 |                |

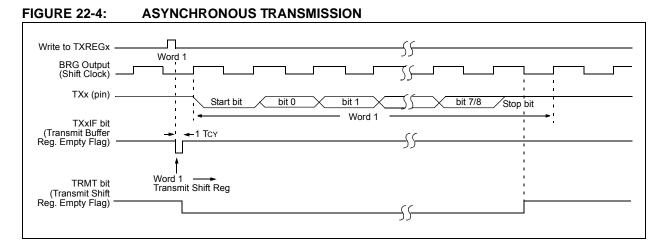

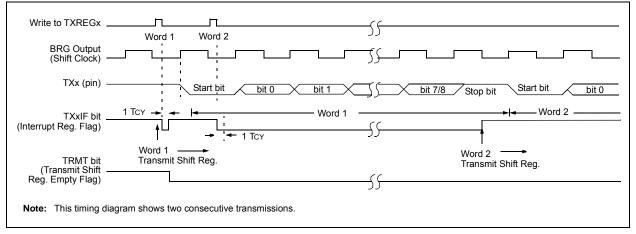

## FIGURE 22-5: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

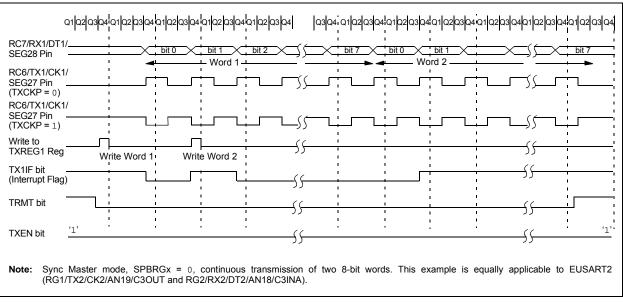

### 22.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTAx<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTAx<4>). In addition, enable bit, SPEN (RCSTAx<7>), is set in order to configure the TXx and RXx pins to CKx (clock) and DTx (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CKx line. Clock polarity is selected with the TXCKP bit (BAUDCONx<4>). Setting TXCKP sets the Idle state on CKx as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 22.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 22-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The TSR register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREGx (if available).

Once the TXREGx register transfers the data to the TSR register (occurs in one TcY), the TXREGx is empty and the TXxIF flag bit is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF is set regardless of the state of enable bit, TXxIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREGx register.

While flag bit, TXxIF, indicates the status of the TXREGx register, another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user must poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### FIGURE 22-11: SYNCHRONOUS TRANSMISSION

# 27.2 CTMU Operation

The CTMU works by using a fixed current source to charge a circuit. The type of circuit depends on the type of measurement being made.

In the case of charge measurement, the current is fixed and the amount of time the current is applied to the circuit is fixed. The amount of voltage read by the A/D becomes a measurement of the circuit's capacitance.

In the case of time measurement, the current, as well as the capacitance of the circuit, is fixed. In this case, the voltage read by the A/D is representative of the amount of time elapsed from the time the current source starts and stops charging the circuit.

If the CTMU is being used as a time delay, both capacitance and current source are fixed, as well as the voltage supplied to the comparator circuit. The delay of a signal is determined by the amount of time it takes the voltage to charge to the comparator threshold voltage.

### 27.2.1 THEORY OF OPERATION

The operation of the CTMU is based on the equation for charge:

$C = I \bullet \frac{dV}{dT}$

More simply, the amount of charge measured in coulombs in a circuit is defined as current in amperes (I) multiplied by the amount of time in seconds that the current flows (t). Charge is also defined as the capacitance in farads (C) multiplied by the voltage of the circuit (V). It follows that:

$I \bullet t = C \bullet V$

The CTMU module provides a constant, known current source. The A/D Converter is used to measure (V) in the equation, leaving two unknowns: capacitance (C) and time (t). The above equation can be used to calculate capacitance or time, by either the relationship using the known fixed capacitance of the circuit:

$t = (C \bullet V)/I$

or by:

$\mathbf{C} = (\mathbf{I} \bullet \mathbf{t}) / \mathbf{V}$

using a fixed time that the current source is applied to the circuit.

## 27.2.2 CURRENT SOURCE

At the heart of the CTMU is a precision current source, designed to provide a constant reference for measurements. The level of current is user-selectable across three ranges or a total of two orders of magnitude, with the ability to trim the output in  $\pm 2\%$  increments (nominal). The current range is selected by the IRNG<1:0> bits (CTMUICON<1:0>), with a value of '00' representing the lowest range.

Current trim is provided by the ITRIM<5:0> bits (CTMUICON<7:2>). These six bits allow trimming of the current source in steps of approximately 2% per step. Half of the range adjusts the current source positively and the other half reduces the current source. A value of '000000' is the neutral position (no change). A value of '100000' is the maximum negative adjustment (approximately -62%) and '011111' is the maximum positive adjustment (approximately +62%).

# 27.2.3 EDGE SELECTION AND CONTROL

CTMU measurements are controlled by edge events occurring on the module's two input channels. Each channel, referred to as Edge 1 and Edge 2, can be configured to receive input pulses from one of the edge input pins (CTED1 and CTED2) or CCPx Special Event Triggers. The input channels are level-sensitive, responding to the instantaneous level on the channel rather than a transition between levels. The inputs are selected using the EDG1SEL and EDG2SEL bit pairs (CTMUCONL<3:2, 6:5>).

In addition to source, each channel can be configured for event polarity using the EDGE2POL and EDGE1POL bits (CTMUCONL<7,4>). The input channels can also be filtered for an edge event sequence (Edge 1 occurring before Edge 2) by setting the EDGSEQEN bit (CTMUCONH<2>).

# 27.2.4 EDGE STATUS

The CTMUCON register also contains two status bits, EDG2STAT and EDG1STAT (CTMUCONL<1:0>). Their primary function is to show if an edge response has occurred on the corresponding channel. The CTMU automatically sets a particular bit when an edge response is detected on its channel. The level-sensitive nature of the input channels also means that the status bits become set immediately if the channel's configuration is changed and matches the channel's current state.

The module uses the edge status bits to control the current source output to external analog modules (such as the A/D Converter). Current is only supplied to external modules when only one (not both) of the status bits is set. Current is shut off when both bits are either set or cleared. This allows the CTMU to measure current only during the interval between edges. After both status bits are set, it is necessary to clear them before another measurement is taken. Both bits should be cleared simultaneously, if possible, to avoid re-enabling the CTMU current source.

In addition to being set by the CTMU hardware, the edge status bits can also be set by software. This permits a user application to manually enable or disable the current source. Setting either (but not both) of the bits enables the current source. Setting or clearing both bits at once disables the source.

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <u>15 10 9 8 7 0</u>                                                                                                                                                                                                                                  |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| 15 12 11 9 8 7 0                                                                                                                                                                                                                                      |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

|                                                                                                                                                                                                                                                       |                      |

| CALL, GOTO and Branch operations<br>15 8 7 0                                                                                                                                                                                                          |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | BRA MYFUNC           |

|                                                                                                                                                                                                                                                       |                      |

| 15 8 7 0                                                                                                                                                                                                                                              | BC MYFUNC            |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               |                      |

| LFSF                                                      | र              | Load FSR                                                            |                                                                                   |                            |                                        |  |  |

|-----------------------------------------------------------|----------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------|----------------------------------------|--|--|

| Synta                                                     | ax:            | LFSR f, k                                                           |                                                                                   |                            |                                        |  |  |

| Oper                                                      | ands:          | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 409 \end{array}$ | 95                                                                                |                            |                                        |  |  |

| Oper                                                      | ation:         | $k\toFSRf$                                                          |                                                                                   |                            |                                        |  |  |

| Statu                                                     | s Affected:    | None                                                                |                                                                                   |                            |                                        |  |  |

| Enco                                                      | ding:          | 1110<br>1111                                                        | 1110<br>0000                                                                      | 00ff<br>k <sub>7</sub> kkk | k <sub>11</sub> kkk<br>kkkk            |  |  |

| Desc                                                      | ription:       |                                                                     | The 12-bit literal 'k' is loaded into the file select register pointed to by 'f'. |                            |                                        |  |  |

| Word                                                      | ls:            | 2                                                                   |                                                                                   |                            |                                        |  |  |

| Cycle                                                     | es:            | 2                                                                   |                                                                                   |                            |                                        |  |  |

| QC                                                        | ycle Activity: |                                                                     |                                                                                   |                            |                                        |  |  |

|                                                           | Q1             | Q2                                                                  | Q3                                                                                |                            | Q4                                     |  |  |

|                                                           | Decode         | Read literal<br>'k' MSB                                             | Proce:<br>Data                                                                    | a                          | Write<br>iteral 'k'<br>MSB to<br>FSRfH |  |  |

|                                                           | Decode         | Read literal                                                        | Proce                                                                             |                            | rite literal                           |  |  |

|                                                           |                | ʻk' LSB                                                             | Data                                                                              | a 'k'                      | to FSRfL                               |  |  |

| Example: LFSR 2, 3ABh<br>After Instruction<br>FSR2H = 03h |                |                                                                     |                                                                                   |                            |                                        |  |  |

|                                                           | FSR2L          | = AE                                                                |                                                                                   |                            |                                        |  |  |

| MOV   | ΥF                | Move f                                                                                                  |                                                                          |                                                            |                                                |  |  |

|-------|-------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|--|--|

| Synta | ax:               | MOVF f{                                                                                                 | ,d {,a}}                                                                 |                                                            |                                                |  |  |

| Oper  | ands:             | $0 \leq f \leq 255$                                                                                     |                                                                          |                                                            |                                                |  |  |

|       |                   | d ∈ [0,1]<br>a ∈ [0,1]                                                                                  |                                                                          |                                                            |                                                |  |  |

| Oper  | ation:            | $f \rightarrow dest$                                                                                    |                                                                          |                                                            |                                                |  |  |

| •     | is Affected:      | N, Z                                                                                                    |                                                                          |                                                            |                                                |  |  |