Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 69                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f85k90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name   | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                              |

|------------|----------|-----------------|-----|-------------|------------------------------------------------------------------------------------------|

| RH6/SEG42/ | RH6      | 0               | 0   | DIG         | LATH<6> data output.                                                                     |

| CCP7/P1C/  |          | 1               | Ι   | ST          | PORTH<6> data input.                                                                     |

| AN14/C1INC | SEG42    | 1               | 0   | ANA         | LCD Segment 42 output; disables all other pin functions.                                 |

|            | CCP7     | 0               | 0   | DIG         | CCP7 compare/PWM output; takes priority over port data.                                  |

|            |          | 1               | Ι   | ST          | CCP7 capture input.                                                                      |

|            | P1C      | 0               | 0   |             | ECCP1 PWM Output C. May be configured for tri-state during<br>Enhanced PWM.              |

|            | AN14     | 1               | I   | ANA         | A/D Input Channel 14. Default input configuration on POR; does not affect digital input. |

|            | C1INC    | x               | Ι   | ANA         | Comparator 1 Input C.                                                                    |

| RH7/SEG43/ | RH7      | 0               | 0   | DIG         | LATH<7> data output.                                                                     |

| CCP6/P1B/  |          | 1               | Ι   | ST          | PORTH<7> data input.                                                                     |

| AN15       | SEG43    | 1               | 0   | ANA         | LCD Segment 43 output; disables all other pin functions.                                 |

|            | CCP6     | 0               | 0   | DIG         | CCP6 compare/PWM output; takes priority over port data.                                  |

|            |          | 1               | Ι   | ST          | CCP6 capture input.                                                                      |

|            | P1B      | 0               | 0   | _           | ECCP1 PWM Output B. May be configured for tri-state during<br>Enhanced PWM.              |

|            | AN15     | 1               | Ι   | ANA         | A/D Input Channel 15. Default input configuration on POR; does not affect digital input. |

#### TABLE 11-16: PORTH FUNCTIONS (CONTINUED)

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

#### TABLE 11-17: SUMMARY OF REGISTERS ASSOCIATED WITH PORTH

| Name   | Bit 7                  | Bit 6                 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|--------|------------------------|-----------------------|---------|---------|---------|---------|---------|---------|-----------------------------|

| PORTH  | RH7                    | RH6                   | RH5     | RH4     | RH3     | RH2     | RH1     | RH0     | 78                          |

| LATH   | LATH7                  | LATH6                 | LATH5   | LATH4   | LATH3   | LATH2   | LATH1   | LATH0   | 78                          |

| TRISH  | TRISH7                 | TRISH6                | TRISH5  | TRISH4  | TRISH3  | TRISH2  | TRISH1  | TRISH0  | 78                          |

| LCDSE5 | SE47                   | SE46                  | SE45    | SE44    | SE43    | SE42    | SE41    | SE40    | 83                          |

| ANCON1 | ANSEL15                | ANSEL14               | ANSEL13 | ANSEL12 | ANSEL11 | ANSEL10 | ANSEL9  | ANSEL8  | 81                          |

| ANCON2 | ANSEL23                | ANSEL22               | ANSEL21 | ANSEL20 | ANSEL19 | ANSEL18 | ANSEL17 | ANSEL16 | 81                          |

| ODCON2 | CCP100D <sup>(1)</sup> | CCP9OD <sup>(1)</sup> | CCP8OD  | CCP7OD  | CCP6OD  | CCP5OD  | CCP4OD  | CCP3OD  | 81                          |

Note 1: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

| FIGURE 13-7:               | TIMER1 GATE SINGLE                                         | E PULSE AND TOGGLE COMBI                       | NED MODE                                         |

|----------------------------|------------------------------------------------------------|------------------------------------------------|--------------------------------------------------|

| TMR1GE                     |                                                            |                                                |                                                  |

| T1GPOL                     |                                                            |                                                |                                                  |

| T1GSPM                     |                                                            |                                                |                                                  |

| T1GTM                      |                                                            |                                                |                                                  |

| T1GGO/<br>T1DONE<br>T1G_IN | ✓ Set by Software<br>Counting Enabled<br>Rising Edge of T1 | on<br>G                                        | Cleared by Hardware on<br>Falling Edge of T1GVAL |

| Т1СКІ                      |                                                            |                                                |                                                  |

| T1GVAL                     |                                                            |                                                |                                                  |

| Timer1                     | Ν                                                          | N + 1 N + 2 N + 3                              | N + 4                                            |

| RTCCIF                     | — Cleared by Software                                      | Set by Hardware on<br>Falling Edge of T1GVAL — | Cleared by Software                              |

### TABLE 13-5: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name     | Bit 7                    | Bit 6         | Bit 5   | Bit 4    | Bit 3            | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|----------|--------------------------|---------------|---------|----------|------------------|---------|---------|---------|-----------------------------|

| INTCON   | GIE/GIEH                 | PEIE/GIEL     | TMR0IE  | INT0IE   | RBIE             | TMR0IF  | INT0IF  | RBIF    | 75                          |

| PIR1     |                          | ADIF          | RC1IF   | TX1IF    | SSP1IF           | TMR1GIF | TMR2IF  | TMR1IF  | 77                          |

| PIE1     |                          | ADIE          | RC1IE   | TX1IE    | SSP1IE           | TMR1GIE | TMR2IE  | TMR1IE  | 77                          |

| IPR1     | —                        | ADIP          | RC1IP   | TX1IP    | SSP1IP           | TMR1GIP | TMR2IP  | TMR1IP  | 77                          |

| TMR1L    | Timer1 Register Low Byte |               |         |          |                  |         |         | 76      |                             |

| TMR1H    | Timer1 Reg               | gister High B | yte     |          |                  |         |         |         | 76                          |

| T1CON    | TMR1CS1                  | TMR1CS0       | T1CKPS1 | T1CKPS0  | SOSCEN           | T1SYNC  | RD16    | TMR10N  | 76                          |

| T1GCON   | TMR1GE                   | T1GPOL        | T1GTM   | T1GSPM   | T1GGO/<br>T1DONE | T1GVAL  | T1GSS1  | T1GSS0  | 77                          |

| OSCCON2  |                          | SOSCRUN       | _       | —        | SOSCGO           | _       | MFIOFS  | MFIOSEL | 79                          |

| CCPTMRS0 | C3TSEL1                  | C3TSEL0       | C2TSEL2 | C2TSEL1  | C2TSEL0          | C1TSEL2 | C1TSEL1 | C1TSEL0 | 81                          |

| CCPTMRS1 | C7TSEL1                  | C7TSEL0       | _       | C6TSEL0  | _                | C5TSEL0 | C4TSEL1 | C4TSEL0 | 81                          |

| CCPTMRS2 |                          | —             | _       | C10TSEL0 | _                | C9TSEL0 | C8TSEL1 | C8TSEL0 | 81                          |

Legend: Shaded cells are not used by the Timer1 module.

$<sup>\</sup>ensuremath{\textcircled{}^\circ}$  2009-2011 Microchip Technology Inc.

### REGISTER 18-4: CCPRxL: CCPx PERIOD LOW BYTE REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxL7 | CCPRxL6 | CCPRxL5 | CCPRxL4 | CCPRxL3 | CCPRxL2 | CCPRxL1 | CCPRxL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 CCPRxL<7:0>: CCPx Period Register Low Byte bits <u>Capture Mode:</u> Capture register low byte. <u>Compare Mode:</u> Compare register low byte. <u>PWM Mode:</u> Duty Cycle register low byte.

### REGISTER 18-5: CCPRxH: CCPx PERIOD HIGH BYTE REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxH7 | CCPRxH6 | CCPRxH5 | CCPRxH4 | CCPRxH3 | CCPRxH2 | CCPRxH1 | CCPRxH0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 CCPRxH<7:0>: CCPx Period Register High Byte bits <u>Capture Mode:</u> Capture register high byte. <u>Compare Mode:</u> Compare register high byte. <u>PWM Mode:</u> Duty Cycle Buffer register high byte.

### 18.3 Compare Mode

In Compare mode, the 16-bit CCPR4 register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCP4 pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP4M<3:0>). At the same time, the interrupt flag bit, CCP4IF, is set.

Figure 18-2 shows the Compare mode block diagram

#### 18.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP4CON register will force    |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | the RC1 or RE7 compare output latch         |  |  |  |  |

|       | (depending on device configuration) to the  |  |  |  |  |

|       | default low level. This is not the PORTC or |  |  |  |  |

|       | PORTE I/O data latch.                       |  |  |  |  |

### 18.3.2 TIMER1/3/5/7 MODE SELECTION

If the CCP module is using the compare feature in conjunction with any of the Timer1/3/5/7 timers, the timers must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the compare operation may not work.

**Note:** Details of the timer assignments for the CCP modules are given in Table 18-2 and Table 18-3.

### 18.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP4M<3:0> = 1010), the CCP4 pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCP4IE bit is set.

#### 18.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP4M<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP4 cannot start an A/D conversion.

Note: The Special Event Trigger of ECCP1 can start an A/D conversion, but the A/D Converter needs to be enabled. For more information, see Section 19.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

### 21.3.4 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPxCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPxCON registers and then set the SSPEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDIx must have TRISC<4> or TRISD<5> bit set

- SDOx must have the TRISC<5> or TRISD<4> bit cleared

- SCKx (Master mode) must have the TRISC<3> or TRISD<6>bit cleared

- SCKx (Slave mode) must have the TRISC<3> or TRISD<6> bit set

- SSx must have the TRISF<7> or TRISD<7> bit set

Any serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value.

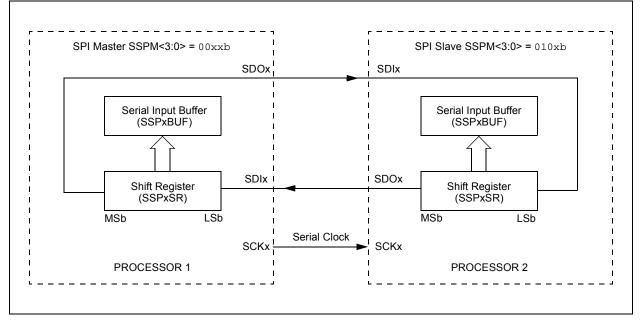

### 21.3.5 TYPICAL CONNECTION

Figure 21-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCKx signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

### FIGURE 21-2: SPI MASTER/SLAVE CONNECTION

| REGISTER 2    | 21-6: SSPx                                                                                                                                                                                                                                               | CON2: MSSF                                                                                                                                                                                                                                                                                                 | Px CONTRO        | L REGISTER        | 2 (I <sup>2</sup> C™ SLA | VE MODE)        |                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|--------------------------|-----------------|--------------------|

| R/W-0         | R/W-0                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                      | R/W-0            | R/W-0             | R/W-0                    | R/W-0           | R/W-0              |

| GCEN          | ACKSTAT                                                                                                                                                                                                                                                  | ADMSK5                                                                                                                                                                                                                                                                                                     | ADMSK4           | ADMSK3            | ADMSK2                   | ADMSK1          | SEN <sup>(1)</sup> |

| bit 7         |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |                  |                   |                          |                 | bit 0              |

| Legend:       |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |                  |                   |                          |                 |                    |

| R = Readable  | e bit                                                                                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                                                                                                               | bit              | U = Unimplem      | nented bit, read         | 1 as '0'        |                    |

| -n = Value at | POR                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                           |                  | '0' = Bit is clea | ared                     | x = Bit is unkn | own                |

| bit 7         | 1 = Enables ir                                                                                                                                                                                                                                           | ral Call Enable<br>nterrupt when a<br>all address is c                                                                                                                                                                                                                                                     | a general call a | ddress (0000h)    | ) is received in         | the SSPxSR      |                    |

| bit 6         | ACKSTAT: Ac<br>Unused in Sla                                                                                                                                                                                                                             | knowledge Sta                                                                                                                                                                                                                                                                                              | atus bit         |                   |                          |                 |                    |

| bit 5-2       | ADMSK<5:2>: Slave Address Mask Select bits (5-Bit Address Masking mode)<br>1 = Masking of corresponding bits of SSPxADD is enabled<br>0 = Masking of corresponding bits of SSPxADD is disabled                                                           |                                                                                                                                                                                                                                                                                                            |                  |                   |                          |                 |                    |

| bit 1         | <u>In 7-Bit Addre</u><br>1 = Masking c<br>0 = Masking c                                                                                                                                                                                                  | <ul> <li>0 = Masking of corresponding bits of SSPxADD is disabled</li> <li>ADMSK1: Slave Address Least Significant bit(s) Mask Select bit</li> <li>In 7-Bit Addressing mode:</li> <li>1 = Masking of SSPxADD&lt;1&gt; only is enabled</li> <li>0 = Masking of SSPxADD&lt;1&gt; only is disabled</li> </ul> |                  |                   |                          |                 |                    |

| bit 0         | In 10-Bit Addressing mode:<br>1 = Masking of SSPxADD<1:0> is enabled<br>0 = Masking of SSPxADD<1:0> is disabled<br>SEN: Stretch Enable bit <sup>(1)</sup><br>1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled) |                                                                                                                                                                                                                                                                                                            |                  |                   |                          |                 |                    |

**Note 1:** If the I<sup>2</sup>C module is active, this bit may not be set (no spooling) and the SSPxBUF may not be written to (or writes to the SSPxBUF are disabled).

| REGISTER 21-7: SSPxM | SK: $I^2 C^{TM}$ SLAVE ADDRESS MASK REGISTER (7-BIT MASKING MODE) <sup>(1)</sup> |

|----------------------|----------------------------------------------------------------------------------|

|----------------------|----------------------------------------------------------------------------------|

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(2)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 MSK<7:0>: Slave Address Mask Select bit

1 = Masking of the corresponding bit of SSPxADD is enabled

0 = Masking of the corresponding bit of SSPxADD is disabled

Note 1: This register shares the same SFR address as SSPxADD and is only addressable in select MSSPx operating modes. See Section 21.4.3.4 "7-Bit Address Masking Mode" for more details.

2: MSK0 is not used as a mask bit in 7-bit addressing.

### 22.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex, asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

All members of the PIC18F87K90 family are equipped with two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/TX1/CK1/ SEG27 and RC7/RX1/DT1/SEG28) and PORTG (RG1/TX2/CK2/AN19/C3OUT and RG2/RX2/DT2/ AN18/C3INA), respectively. In order to configure these pins as an EUSART:

- For EUSART1:

- SPEN (RCSTA1<7>) bit must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

- For EUSART2:

- SPEN (RCSTA2<7>) bit must be set (= 1)

- TRISG<2> bit must be set (= 1)

- TRISG<1> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively, on the following pages.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

Note: The EUSART control will automatically reconfigure the pin from input to output as needed.

| R/W-0                         | R-1                                | R/W-0                                                   | R/W-0            | R/W-0                             | U-0             | R/W-0           | R/W-0          |

|-------------------------------|------------------------------------|---------------------------------------------------------|------------------|-----------------------------------|-----------------|-----------------|----------------|

| ABDOVF                        | RCIDL                              | RXDTP                                                   | TXCKP            | BRG16                             |                 | WUE             | ABDEN          |

| bit 7                         | •                                  |                                                         | •                |                                   |                 |                 | bit            |

| <u> </u>                      |                                    |                                                         |                  |                                   |                 |                 |                |

| <b>Legend:</b><br>R = Readabl | o hit                              | M = Mritabla                                            | hit              | II – Unimplom                     | onted hit read  | L a a 'O'       |                |

| -n = Value at                 |                                    | W = Writable<br>'1' = Bit is set                        |                  | U = Unimplem<br>'0' = Bit is clea |                 |                 | 2014/2         |

|                               | PUR                                | I = DILIS SEL                                           |                  | U = BILIS CIEA                    | reu             | x = Bit is unki | IOWI           |

| bit 7                         | ABDOVF: A                          | uto-Baud Acqui                                          | sition Rollover  | Status bit                        |                 |                 |                |

|                               |                                    | ollover has occ<br>rollover has oc                      | •                | uto-Baud Rate [                   | Detect mode (n  | nust be cleare  | d in software) |

| bit 6                         | RCIDL: Rece                        | eive Operation I                                        | dle Status bit   |                                   |                 |                 |                |

|                               |                                    | operation is Idle operation is act                      |                  |                                   |                 |                 |                |

| bit 5                         | RXDTP: Dat                         | a/Receive Polar                                         | ity Select bit   |                                   |                 |                 |                |

|                               |                                    | <u>ıs mode:</u><br>data (RXx) is in<br>data (RXx) is no |                  |                                   |                 |                 |                |

|                               | <u>Synchronous</u><br>1 = Data (DT |                                                         | ctive-low)       |                                   |                 |                 |                |

| bit 4                         | -                                  | chronous Clock                                          |                  |                                   |                 |                 |                |

|                               | Asynchronou                        |                                                         |                  |                                   |                 |                 |                |

|                               | 1 = Idle state                     | e for transmit (T)<br>e for transmit (T)                | ,                |                                   |                 |                 |                |

|                               | Synchronous                        |                                                         | , ,              |                                   |                 |                 |                |

|                               |                                    | e for clock (CKx)<br>e for clock (CKx)                  |                  |                                   |                 |                 |                |

| bit 3                         | BRG16: 16-                         | Bit Baud Rate R                                         | egister Enable   | bit                               |                 |                 |                |

|                               |                                    |                                                         |                  | Hx and SPBRG> only (Compatibl     |                 | RGHx value is   | ignored        |

| bit 2                         | Unimpleme                          | nted: Read as '                                         | כי               |                                   |                 |                 |                |

| bit 1                         | WUE: Wake                          | up Enable bit                                           |                  |                                   |                 |                 |                |

|                               | cleared                            |                                                         | the following ri |                                   | rupt is generat | ed on the falli | ng edge; bit   |

|                               | Synchronous<br>Unused in th        |                                                         |                  |                                   |                 |                 |                |

| bit 0                         | ABDEN: Aut                         | o-Baud Detect                                           | Enable bit       |                                   |                 |                 |                |

|                               | cleared                            |                                                         | on completion.   | e next characte                   | r. Requires rec | ception of a Sy | vnc field (55h |

|                               | Synchronous                        |                                                         |                  | compicted                         |                 |                 |                |

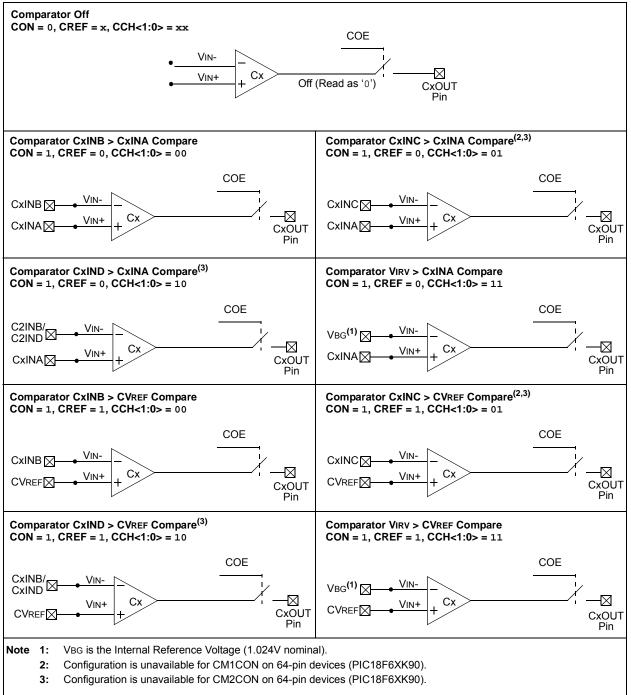

FIGURE 24-4: COMPARATOR CONFIGURATIONS

NOTES:

### REGISTER 28-13: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)<sup>(1)</sup>

| U-0                       | R/C-1                                                                   | U-0 | U-0 | U-0 | U-0  | U-0 | U-0   |

|---------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|-----|-------|

| —                         | EBTRB                                                                   |     | _   | —   |      | —   | —     |

| bit 7                     |                                                                         |     |     | •   |      |     | bit 0 |

|                           |                                                                         |     |     |     |      |     |       |

| Legend: C = Clearable bit |                                                                         |     |     |     |      |     |       |

| R = Readable b            | Readable bit W = Writable bit U = Unimplemented bit, read as '0'        |     |     |     |      |     |       |

| -n = Value at Po          | = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |     |     | nown |     |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

bit 7 Unimplemented: Read as '0'

| bit 6 | EBTRB: Boot Block Table Read Protection bit |

|-------|---------------------------------------------|

|-------|---------------------------------------------|

1 = Boot block is not protected from table reads executed in other blocks

0 = Boot block is protected from table reads executed in other blocks

bit 5-0 Unimplemented: Read as '0'

Note 1: For the memory size of the blocks, refer to Figure 28-6.

| GOTO                                                                                                                                                                 | Unconditio                | onal Brai                   | nch                        |                                         |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------|----------------------------|-----------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                                                                              | yntax: GOTO k             |                             |                            |                                         |  |  |  |  |  |

| Operands:                                                                                                                                                            | $0 \le k \le 104$         | $0 \leq k \leq 1048575$     |                            |                                         |  |  |  |  |  |

| Operation:                                                                                                                                                           | $k \rightarrow PC<20$     | ):1>                        |                            |                                         |  |  |  |  |  |

| Status Affected:                                                                                                                                                     | None                      |                             |                            |                                         |  |  |  |  |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>)                                                                                                                  | 1110<br>1111              | 1111<br>k <sub>19</sub> kkk | k <sub>7</sub> kkk<br>kkkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub>  |  |  |  |  |  |

| Description: GOTO allows an unconditional b<br>anywhere within entire 2-Mbyte<br>range. The 20-bit value 'k' is loa<br>PC<20:1>. GOTO is always a tw<br>instruction. |                           |                             |                            |                                         |  |  |  |  |  |

| Words:                                                                                                                                                               | 2                         |                             |                            |                                         |  |  |  |  |  |

| Cycles:                                                                                                                                                              | 2                         | 2                           |                            |                                         |  |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                    |                           |                             |                            |                                         |  |  |  |  |  |

| Q1                                                                                                                                                                   | Q2                        | Q3                          |                            | Q4                                      |  |  |  |  |  |

| Decode                                                                                                                                                               | Read literal<br>'k'<7:0>, | No<br>operat                | ion '                      | ead literal<br>k'<19:8>,<br>/rite to PC |  |  |  |  |  |

| No<br>operation                                                                                                                                                      | No<br>operation           |                             |                            | No<br>operation                         |  |  |  |  |  |

| operation     operation     operation       Example:     GOTO THERE       After Instruction       PC =     Address (THERE)                                           |                           |                             |                            |                                         |  |  |  |  |  |

| INCF                               | Increment                                                         | f                                                    |                               |                                                       |

|------------------------------------|-------------------------------------------------------------------|------------------------------------------------------|-------------------------------|-------------------------------------------------------|

| Syntax:                            | INCF f{,c                                                         | l {,a}}                                              |                               |                                                       |

| Operands:                          | $0 \leq f \leq 255$                                               |                                                      |                               |                                                       |

|                                    | d ∈ [0,1]<br>a ∈ [0,1]                                            |                                                      |                               |                                                       |

| Operation:                         | (f) + 1 $\rightarrow$ de                                          | est                                                  |                               |                                                       |

| Status Affected:                   | C, DC, N,                                                         | OV, Z                                                |                               |                                                       |

| Encoding:                          | 0010                                                              | 10da                                                 | fff                           | f ffff                                                |

| Description:                       | The conten<br>incremente<br>placed in W<br>placed bac             | d. lf 'd' is<br>/. lf 'd' is                         | '0', th<br>'1', the           | e result is                                           |

|                                    | ,                                                                 |                                                      |                               | k is selected.<br>to select the                       |

|                                    |                                                                   | ed, this i<br>Literal Of                             | nstruct<br>fset Ad            | 0                                                     |

|                                    | Section 29                                                        | .2.3 "By<br>ed Instru                                | te-Orie<br>ctions             | ented and<br>in Indexed                               |

| Words:                             | Section 29<br>Bit-Oriente                                         | .2.3 "By<br>ed Instru                                | te-Orie<br>ctions             | ented and<br>in Indexed                               |

|                                    | Section 29<br>Bit-Oriente<br>Literal Offs                         | .2.3 "By<br>ed Instru                                | te-Orie<br>ctions             | ented and<br>in Indexed                               |

|                                    | Section 29<br>Bit-Oriente<br>Literal Offs<br>1                    | .2.3 "By<br>ed Instru                                | te-Orie<br>ctions             | ented and<br>in Indexed                               |

| Cycles:<br>Q Cycle Activity:<br>Q1 | Section 29<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>Q2         | .2.3 "By<br>ed Instru<br>set Mode                    | te-Orie<br>ctions<br>" for d  | ented and<br>i in Indexed<br>letails.<br>Q4           |

| Cycles:<br>Q Cycle Activity:       | Section 29<br>Bit-Oriente<br>Literal Offs<br>1<br>1               | .2.3 "By<br>ed Instru<br>set Mode                    | te-Orie<br>ctions<br>:" for d | ented and<br>in Indexed<br>letails.                   |

| Q1                                 | Section 29<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>Q2<br>Read | 2.3 "Byted Instru<br>set Mode<br>Q3<br>Proce<br>Data | te-Orie<br>ctions<br>:" for d | ented and<br>in Indexed<br>letails.<br>Q4<br>Write to |

### 29.2.3 BYTE-ORIENTED AND BIT-ORIENTED INSTRUCTIONS IN INDEXED LITERAL OFFSET MODE

| Note: | Enabling the PIC18 instruction set exten- |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | sion may cause legacy applications to     |  |  |  |  |  |  |  |  |

|       | behave erratically or fail entirely.      |  |  |  |  |  |  |  |  |

In addition to eight new commands in the extended set, enabling the extended instruction set also enables Indexed Literal Offset Addressing (Section 6.6.1 "Indexed Addressing with Literal Offset"). This has a significant impact on the way that many commands of the standard PIC18 instruction set are interpreted.

When the extended set is disabled, addresses embedded in opcodes are treated as literal memory locations: either as a location in the Access Bank (a = 0) or in a GPR bank designated by the BSR (a = 1). When the extended instruction set is enabled and a = 0, however, a file register argument of 5Fh or less is interpreted as an offset from the pointer value in FSR2 and not as a literal address. For practical purposes, this means that all instructions that use the Access RAM bit as an argument – that is, all byte-oriented and bit-oriented instructions, or almost half of the core PIC18 instructions – may behave differently when the extended instruction set is enabled.

When the content of FSR2 is 00h, the boundaries of the Access RAM are essentially remapped to their original values. This may be useful in creating backward compatible code. If this technique is used, it may be necessary to save the value of FSR2 and restore it when moving back and forth between C and assembly routines in order to preserve the Stack Pointer. Users must also keep in mind the syntax requirements of the extended instruction set (see Section 29.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands").

Although the Indexed Literal Offset mode can be very useful for dynamic stack and pointer manipulation, it can also be very annoying if a simple arithmetic operation is carried out on the wrong register. Users who are accustomed to the PIC18 programming must keep in mind, that when the extended instruction set is enabled, register addresses of 5Fh or less are used for Indexed Literal Offset Addressing.

Representative examples of typical byte-oriented and bit-oriented instructions in the Indexed Literal Offset mode are provided on the following page to show how execution is affected. The operand conditions shown in the examples are applicable to all instructions of these types.

### 29.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands

When the extended instruction set is enabled, the file register argument, 'f', in the standard byte-oriented and bit-oriented commands is replaced with the literal offset value, 'k'. As already noted, this occurs only when 'f' is less than or equal to 5Fh. When an offset value is used, it must be indicated by square brackets ("[]"). As with the extended instructions, the use of brackets indicates to the compiler that the value is to be interpreted as an index or an offset. Omitting the brackets, or using a value greater than 5Fh within the brackets, will generate an error in the MPASM<sup>™</sup> Assembler.

If the index argument is properly bracketed for Indexed Literal Offset Addressing, the Access RAM argument is never specified; it will automatically be assumed to be '0'. This is in contrast to standard operation (extended instruction set disabled), when 'a' is set on the basis of the target address. Declaring the Access RAM bit in this mode will also generate an error in the MPASM Assembler.

The destination argument, 'd', functions as before.

In the latest versions of the MPASM Assembler, language support for the extended instruction set must be explicitly invoked. This is done with either the command line option,  $/_{Y}$ , or the PE directive in the source listing.

### 29.2.4 CONSIDERATIONS WHEN ENABLING THE EXTENDED INSTRUCTION SET

It is important to note that the extensions to the instruction set may not be beneficial to all users. In particular, users who are not writing code that uses a software stack may not benefit from using the extensions to the instruction set.

Additionally, the Indexed Literal Offset Addressing mode may create issues with legacy applications written to the PIC18 assembler. This is because instructions in the legacy code may attempt to address registers in the Access Bank below 5Fh. Since these addresses are interpreted as literal offsets to FSR2 when the instruction set extension is enabled, the application may read or write to the wrong data addresses.

When porting an application to the PIC18F87K90 family, it is very important to consider the type of code. A large, re-entrant application that is written in C and would benefit from efficient compilation will do well when using the instruction set extensions. Legacy applications that heavily use the Access Bank will most likely not benefit from using the extended instruction set.

### 29.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set for the PIC18F87K90 family family. This includes the MPLAB C18 C Compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option or dialog box within the environment that allows the user to configure the language tool and its settings for the project

- · A command line option

- · A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

### 31.2 DC Characteristics: Power-Down and Supply Current PIC18F87K90 Family (Industrial/Extended) (Continued)

| PIC18F87K90 Family |                           | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |     |       |        |                           |                                 |  |  |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|---------------------------|---------------------------------|--|--|

| Param<br>No.       | Device                    | Тур                                                                                                                                                                                                                                                        | Max | Units |        | Conditions                |                                 |  |  |

|                    | Supply Current (IDD) Cont | (2,3)                                                                                                                                                                                                                                                      |     |       |        |                           |                                 |  |  |

|                    | All devices               | 3.7                                                                                                                                                                                                                                                        | 8.5 | μA    | -40°C  |                           |                                 |  |  |

|                    |                           | 5.4                                                                                                                                                                                                                                                        | 10  | μA    | +25°C  | VDD = 1.8V <sup>(4)</sup> |                                 |  |  |

|                    |                           | 6.6                                                                                                                                                                                                                                                        | 13  | μA    | +85°C  | Regulator Disabled        |                                 |  |  |

|                    |                           | 13                                                                                                                                                                                                                                                         | 30  | μA    | +125°C |                           |                                 |  |  |

|                    | All devices               | 8.7                                                                                                                                                                                                                                                        | 18  | μA    | -40°C  |                           | <b>E</b>                        |  |  |

|                    |                           | 10                                                                                                                                                                                                                                                         | 20  | μA    | +25°C  | VDD = 3.3V <sup>(4)</sup> | Fosc = 32 kHz <sup>(3)</sup>    |  |  |

|                    |                           | 12                                                                                                                                                                                                                                                         | 23  | μA    | +85°C  | Regulator Disabled        | (SEC_RUN mode,<br>SOSCSEL = 01) |  |  |

|                    |                           | 25                                                                                                                                                                                                                                                         | 60  | μA    | +125°C |                           | 00000EE - 01)                   |  |  |

|                    | All devices               | 60                                                                                                                                                                                                                                                         | 160 | μA    | -40°C  |                           |                                 |  |  |

|                    |                           | 90                                                                                                                                                                                                                                                         | 190 | μA    | +25°C  | VDD = 5V <sup>(5)</sup>   |                                 |  |  |

|                    |                           | 100                                                                                                                                                                                                                                                        | 240 | μA    | +85°C  | Regulator Enabled         |                                 |  |  |

|                    |                           | 200                                                                                                                                                                                                                                                        | 450 | μA    | +125°C |                           |                                 |  |  |

|                    | All devices               | 1.2                                                                                                                                                                                                                                                        | 4   | μA    | -40°C  |                           |                                 |  |  |

|                    |                           | 1.7                                                                                                                                                                                                                                                        | 5   | μA    | +25°C  | VDD = 1.8V <sup>(4)</sup> |                                 |  |  |

|                    |                           | 2.6                                                                                                                                                                                                                                                        | 6   | μA    | +85°C  | Regulator Disabled        |                                 |  |  |

|                    |                           | 9                                                                                                                                                                                                                                                          | 20  | μA    | +125°C |                           |                                 |  |  |

|                    | All devices               | 1.6                                                                                                                                                                                                                                                        | 7   | μA    | -40°C  |                           | Fosc = 32 kHz <sup>(3)</sup>    |  |  |

|                    |                           | 2.8                                                                                                                                                                                                                                                        | 9   | μA    | +25°C  | VDD = 3.3V <sup>(4)</sup> | (SEC IDLE mode,                 |  |  |

|                    |                           | 4.1                                                                                                                                                                                                                                                        | 10  | μA    | +85°C  | Regulator Disabled        | SOSCSEL = 01)                   |  |  |

|                    |                           | 17                                                                                                                                                                                                                                                         | 40  | μA    | +125°C |                           |                                 |  |  |

|                    | All devices               | 60                                                                                                                                                                                                                                                         | 150 | μA    | -40°C  |                           |                                 |  |  |

|                    |                           | 80                                                                                                                                                                                                                                                         | 180 | μA    | +25°C  | VDD = 5V <sup>(5)</sup>   |                                 |  |  |

|                    |                           | 100                                                                                                                                                                                                                                                        | 240 | μA    | +85°C  | Regulator Enabled         |                                 |  |  |

|                    |                           | 180                                                                                                                                                                                                                                                        | 440 | μA    | +125°C |                           |                                 |  |  |

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in a high-impedance state and tied to VDD or VSS, and all features that add delta current are disabled (such as WDT, SOSC oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

3: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

4: Voltage regulator disabled (ENVREG = 0, tied to Vss, RETEN (CONFIG1L<0>) = 1).

5: Voltage regulator enabled (ENVREG = 1, tied to VDD, SRETEN (WDTCON<4>) = 1 and RETEN (CONFIG1L<0>) = 0).

6: LCD glass is not connected; resistor current is not included.

7: 48 MHz maximum frequency at 125°C.

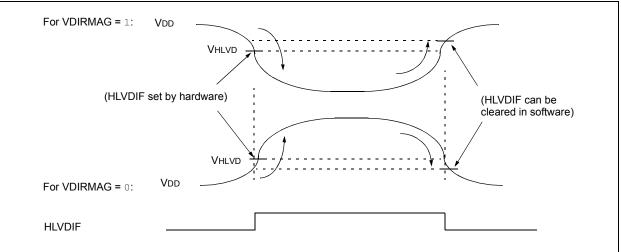

### TABLE 31-11: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |                        |                   |      |      |      |       |            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|-------------------|------|------|------|-------|------------|--|

| Param<br>No.                                                                                                                                                                            | Sym | Charact                | eristic           | Min  | Тур  | Max  | Units | Conditions |  |

| D420                                                                                                                                                                                    |     | HLVD Voltage on VDD    | HLVDL<3:0> = 0000 | 1.80 | 1.86 | 1.90 | V     |            |  |

|                                                                                                                                                                                         |     | Transition High-to-Low | HLVDL<3:0> = 0001 | 2.03 | 2.12 | 2.13 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 0010 | 2.24 | 2.33 | 2.35 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 0011 | 2.40 | 2.49 | 2.53 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 0100 | 2.50 | 2.59 | 2.62 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 0101 | 2.70 | 2.75 | 2.84 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 0110 | 2.82 | 2.93 | 2.97 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 0111 | 2.95 | 3.07 | 3.10 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 1000 | 3.24 | 3.30 | 3.41 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 1001 | 3.42 | 3.48 | 3.59 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 1010 | 3.61 | 3.67 | 3.79 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 1011 | 3.82 | 3.87 | 4.01 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 1100 | 4.06 | 4.21 | 4.26 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 1101 | 4.33 | 4.42 | 4.55 | V     |            |  |

|                                                                                                                                                                                         |     |                        | HLVDL<3:0> = 1110 | 4.64 | 4.77 | 4.87 | V     |            |  |

### 32.2 Package Details

The following sections give the technical details of the packages.

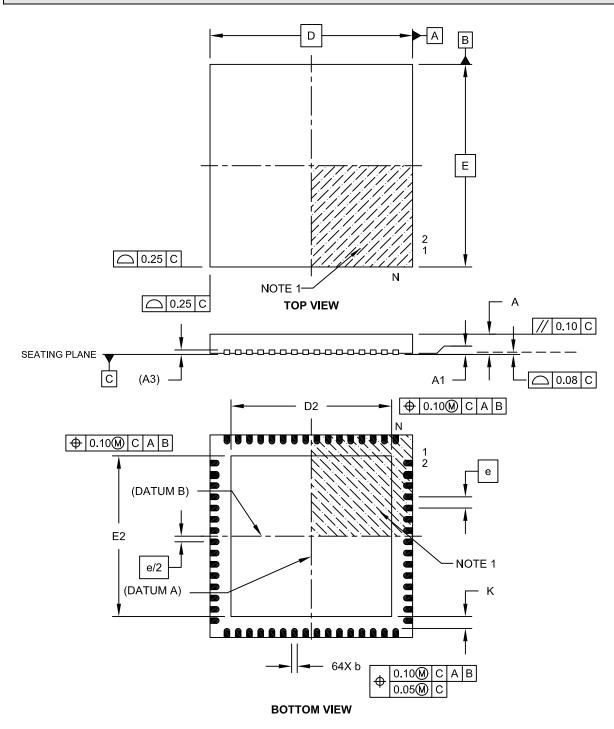

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-149B Sheet 1 of 2

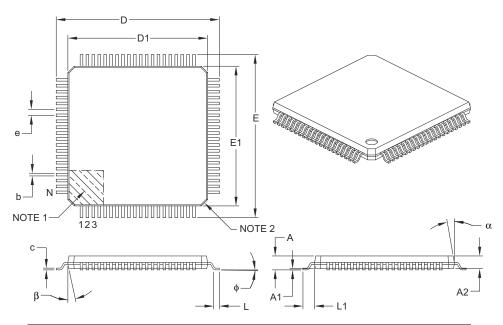

### 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |           |      |  |

|--------------------------|------------------|-------------|-----------|------|--|

|                          | Dimension Limits |             |           | MAX  |  |

| Number of Leads          | N                |             | 80        |      |  |

| Lead Pitch               | e                |             | 0.50 BSC  |      |  |

| Overall Height           | А                | -           | -         | 1.20 |  |

| Molded Package Thickness | A2               | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1               | 0.05        | _         | 0.15 |  |

| Foot Length              | L                | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1               | 1.00 REF    |           |      |  |

| Foot Angle               | φ                | 0°          | 3.5°      | 7°   |  |

| Overall Width            | E                |             | 14.00 BSC |      |  |

| Overall Length           | D                |             | 14.00 BSC |      |  |

| Molded Package Width     | E1               |             | 12.00 BSC |      |  |

| Molded Package Length    | D1               |             | 12.00 BSC |      |  |

| Lead Thickness           | С                | 0.09        | _         | 0.20 |  |

| Lead Width               | b                | 0.17        | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α                | 11°         | 12°       | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°       | 13°  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B