Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 69                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86k90-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                               | PIC18F65K90                                               | PIC18F66K90                                                                   | PIC18F67K90 |  |  |  |

|----------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|-------------|--|--|--|

| Operating Frequency                    |                                                           | DC – 64 MHz                                                                   |             |  |  |  |

| Program Memory (Bytes)                 | 32K                                                       | 64K                                                                           | 128K        |  |  |  |

| Program Memory (Instructions)          | 16,384                                                    | 32,768                                                                        | 65,536      |  |  |  |

| Data Memory (Bytes)                    | 2K                                                        | 4K                                                                            | 4K          |  |  |  |

| Interrupt Sources                      | 42                                                        | 4                                                                             | 8           |  |  |  |

| I/O Ports                              |                                                           | Ports A, B, C, D, E, F, G                                                     |             |  |  |  |

| LCD Driver (available pixels to drive) |                                                           | 132 (33 SEGs x 4 COMs                                                         | )           |  |  |  |

| Timers                                 | 8                                                         | 1                                                                             | 1           |  |  |  |

| Comparators                            | 3                                                         |                                                                               |             |  |  |  |

| СТМИ                                   | Yes                                                       |                                                                               |             |  |  |  |

| RTCC                                   |                                                           | Yes                                                                           |             |  |  |  |

| Capture/Compare/PWM (CCP) Modules      | 5                                                         | 7                                                                             | 7           |  |  |  |

| Enhanced CCP (ECCP) Modules            | 3                                                         |                                                                               |             |  |  |  |

| Serial Communications                  | Two MSSP and two Enhanced USART (EUSART)                  |                                                                               |             |  |  |  |

| 12-Bit Analog-to-Digital Module        | 16 Input Channels                                         |                                                                               |             |  |  |  |

| Resets (and Delays)                    | POR, BOR, RESET Inst                                      | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLF<br>(PWRT, OST) |             |  |  |  |

| Instruction Set                        | 75 Instructions, 83 with Extended Instruction Set Enabled |                                                                               |             |  |  |  |

| Packages                               | 64-Pin QFN, 64-Pin TQFP                                   |                                                                               |             |  |  |  |

## TABLE 1-1: DEVICE FEATURES FOR THE PIC18F6XK90 (64-PIN DEVICES)

## TABLE 1-2: DEVICE FEATURES FOR THE PIC18F8XK90 (80-PIN DEVICES)

| Features                               | PIC18F85K90                                                                 | PIC18F86K90                 | PIC18F87K90      |  |

|----------------------------------------|-----------------------------------------------------------------------------|-----------------------------|------------------|--|

| Operating Frequency                    |                                                                             | DC – 64 MHz                 |                  |  |

| Program Memory (Bytes)                 | 32K                                                                         | 64K                         | 128K             |  |

| Program Memory (Instructions)          | 16,384                                                                      | 32,768                      | 65,536           |  |

| Data Memory (Bytes)                    | 2K                                                                          | 4K                          | 4K               |  |

| Interrupt Sources                      | 42                                                                          | 4                           | 8                |  |

| I/O Ports                              | P                                                                           | orts A, B, C, D, E, F, G, H | , J              |  |

| LCD Driver (available pixels to drive) |                                                                             | 192 (48 SEGs x 4 COMs       | )                |  |

| Timers                                 | 8                                                                           | 1                           | 1                |  |

| Comparators                            |                                                                             | 3                           |                  |  |

| СТМИ                                   | Y                                                                           | es                          |                  |  |

| RTCC                                   | Y                                                                           | es                          |                  |  |

| Capture/Compare/PWM (CCP) Modules      | 5                                                                           | 7                           | 7                |  |

| Enhanced CCP (ECCP) Modules            | 3                                                                           |                             |                  |  |

| Serial Communications                  | Two MSSP a                                                                  | and two Enhanced USAR       | T (EUSART)       |  |

| 12-Bit Analog-to-Digital Module        | 24 Input Channels                                                           |                             |                  |  |

| Resets (and Delays)                    | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, (PWRT, OST) |                             |                  |  |

| Instruction Set                        | 75 Instructions,                                                            | 83 with Extended Instruc    | tion Set Enabled |  |

| Packages                               |                                                                             | 80-Pin TQFP                 |                  |  |

| TABLE 1-3: | PIC18F6XK90 PINOUT I/O DESCRIPTIONS (C | CONTINUED) |  |

|------------|----------------------------------------|------------|--|

|            |                                        |            |  |

| Pin Name                                                                            | Pin Number | Pin                            | Buffer                               | Description                                                                                                                                               |

|-------------------------------------------------------------------------------------|------------|--------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fin Name                                                                            | QFN/TQFP   | Туре                           | Туре                                 | Description                                                                                                                                               |

|                                                                                     |            |                                |                                      | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                                             |

| RB0/INT0/SEG30/FLTO<br>RB0<br>INT0<br>SEG30<br>FLTO                                 | 48         | I/O<br>I<br>O<br>I             | TTL<br>ST<br>Analog<br>ST            | Digital I/O.<br>External Interrupt 0.<br>SEG30 output for LCD.<br>Enhanced PWM Fault input for ECCP1/2/3.                                                 |

| RB1/INT1/SEG8<br>RB1<br>INT1<br>SEG8                                                | 47         | I/O<br>I<br>O                  | TTL<br>ST<br>Analog                  | Digital I/O.<br>External Interrupt 1.<br>SEG8 output for LCD.                                                                                             |

| RB2/INT2/SEG9/CTED1<br>RB2<br>INT2<br>CTED1<br>SEG9                                 | 46         | I/O<br>I<br>I<br>O             | TTL<br>ST<br>ST<br>Analog            | Digital I/O.<br>External Interrupt 2.<br>CTMU Edge 1 input.<br>SEG9 output for LCD.                                                                       |

| RB3/INT3/SEG10/CTED2/<br>ECCP2/P2A<br>RB3<br>INT3<br>SEG10<br>CTED2<br>ECCP2<br>P2A | 45         | I/O<br>I<br>0<br>I<br>I/O<br>0 | TTL<br>ST<br>Analog<br>ST<br>ST<br>— | Digital I/O.<br>External Interrupt 3.<br>SEG10 output for LCD.<br>CTMU Edge 2 input.<br>Capture 2 input/Compare 2 output/PWM2.<br>Enhanced PWM2 Output A. |

| RB4/KBI0/SEG11<br>RB4<br>KBI0<br>SEG11                                              | 44         | I/O<br>I<br>O                  | TTL<br>TTL<br>Analog                 | Digital I/O.<br>Interrupt-on-change pin.<br>SEG11 output for LCD.                                                                                         |

| RB5/KBI1/SEG29/T3CKI/<br>T1G<br>RB5<br>KBI1<br>SEG29<br>T3CKI<br>T1G                | 43         | I/O<br>I<br>O<br>I             | TTL<br>TTL<br>Analog<br>ST<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>SEG29 output for LCD.<br>Timer3 clock input.<br>Timer1 external clock gate input.                             |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                                                  | 42         | I/O<br>I<br>I/O                | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP™ programming clock pin.                                                          |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                                                  | 37         | I/O<br>I<br>I/O                | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                                                            |

| ST = Schm<br>I = Input<br>P = Powe<br>$I^2C^{TM} = I^2C/SN$                         | MBus       | with C                         |                                      | CMOS = CMOS compatible input or output<br>els Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)                                  |

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K90 and PIC18F85K90 devices.

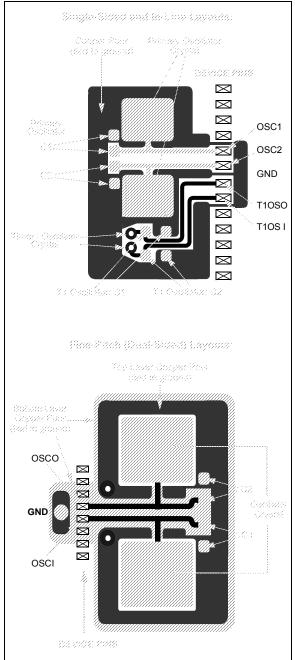

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0 "Oscillator Configurations"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

## 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### FIGURE 2-5:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

## TABLE 4-4:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Power-Managed<br>Mode | Clock Source <sup>(5)</sup> | Exit Delay                 | Clock Ready<br>Status Bits |

|-----------------------|-----------------------------|----------------------------|----------------------------|

|                       | LP, XT, HS                  |                            |                            |

|                       | HSPLL                       |                            | OSTS                       |

|                       | EC, RC                      | Tcsp <sup>(1)</sup>        |                            |

| PRI_IDLE mode         | HF-INTOSC <sup>(2)</sup>    |                            | HFIOFS                     |

|                       | MF-INTOSC <sup>(2)</sup>    |                            | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

| SEC_IDLE mode         | SOSC                        | TCSD <sup>(1)</sup>        | SOSCRUN                    |

|                       | HF-INTOSC <sup>(2)</sup>    |                            | HFIOFS                     |

| RC_IDLE mode          | MF-INTOSC <sup>(2)</sup>    | TCSD <sup>(1)</sup>        | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

|                       | LP, XT, HS                  | Tost <sup>(3)</sup>        |                            |

|                       | HSPLL                       | Tost + t <sub>rc</sub> (3) | OSTS                       |

| Sloop mode            | EC, RC                      | TCSD <sup>(1)</sup>        |                            |

| Sleep mode            | HF-INTOSC <sup>(2)</sup>    |                            | HFIOFS                     |

|                       | MF-INTOSC <sup>(2)</sup>    | TIOBST <sup>(4)</sup>      | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

**Note 1:** TCSD (Parameter 38, Table 31-10) is a required delay when waking from Sleep and all Idle modes, and runs concurrently with any other required delays (see **Section 4.4 "Idle Modes"**).

2: Includes postscaler derived frequencies. On Reset, INTOSC defaults to HF-INTOSC at 8 MHz.

**3:** TOST is the Oscillator Start-up Timer (Parameter 32, Table 31-10). TRC is the PLL Lock-out Timer (Parameter F12, Table 31-7); it is also designated as TPLL.

4: Execution continues during TIOBST (Parameter 39, Table 31-10), the INTOSC stabilization period.

**5:** The clock source is dependent upon the settings of the SCS (OSCCON<1:0>), IRCF (OSCCON<6:4>) and FOSC (CONFIG1H<3:0>) bits.

### REGISTER 7-1: EECON1: EEPROM CONTROL REGISTER 1

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | EEPGD: Flash Program or Data EEPROM Memory Select bit                                              |

|-------|----------------------------------------------------------------------------------------------------|

|       | 1 = Access Flash program memory                                                                    |

|       | 0 = Access data EEPROM memory                                                                      |

| bit 6 | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                        |

|       | 1 = Access Configuration registers                                                                 |

|       | 0 = Access Flash program or data EEPROM memory                                                     |

| bit 5 | Unimplemented: Read as '0'                                                                         |

| bit 4 | FREE: Flash Block Erase Enable bit                                                                 |

|       | 1 = Erase the program memory row addressed by TBLPTR on the next WR command                        |

|       | (cleared by completion of erase operation)                                                         |

|       | 0 = Perform write-only                                                                             |

| bit 3 | WRERR: Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup>                                     |

|       | 1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal |

|       | operation or an improper write attempt)                                                            |

|       | 0 = The write operation completed                                                                  |

| bit 2 | WREN: Flash Program/Data EEPROM Write Enable bit                                                   |

|       | 1 = Allows write cycles to Flash program/data EEPROM                                               |

|       | 0 = Inhibits write cycles to Flash program/data EEPROM                                             |

| bit 1 | WR: Write-Control bit                                                                              |

|       | 1 = Initiates a data EEPROM erase/write cycle, or a program memory erase cycle or write cycle      |

|       | (The operation is self-timed and the bit is cleared by hardware once write is complete.            |

|       | The WR bit can only be set (not cleared) in software.)                                             |

|       | 0 = Write cycle to the EEPROM is complete                                                          |

| bit 0 | RD: Read Control bit                                                                               |

|       | 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only |

|       | be set (not cleared) in software. The RD bit cannot be set when EEPGD = 1 or CFGS = 1.)            |

|       | 0 = Does not initiate an EEPROM read                                                               |

|       |                                                                                                    |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

#### R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 TMR12IP<sup>(1)</sup> TMR7GIP<sup>(1)</sup> TMR10IP<sup>(1)</sup> TMR8IP TMR7IP<sup>(1)</sup> TMR5IP TMR4IP TMR6IP bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**REGISTER 10-20: IPR5: PERIPHERAL INTERRUPT PRIORITY REGISTER 5**

| bit 7 | <b>TMR7GIP:</b> TMR7 Gate Interrupt Priority bit <sup>(1)</sup><br>1 = High priority<br>0 = Low priority           |

|-------|--------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>TMR12IP:</b> TMR12 to PR12 Match Interrupt Priority bit <sup>(1)</sup><br>1 = High priority<br>0 = Low priority |

| bit 5 | <b>TMR10IP:</b> TMR10 to PR10 Match Interrupt Priority bit <sup>(1)</sup><br>1 = High priority<br>0 = Low priority |

| bit 4 | <b>TMR8IP:</b> TMR8 to PR8 Match Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                   |

| bit 3 | <b>TMR7IP:</b> TMR7 Overflow Interrupt Priority bit <sup>(1)</sup><br>1 = High priority<br>0 = Low priority        |

| bit 2 | <b>TMR6IP:</b> TMR6 to PR6 Match Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                   |

| bit 1 | <b>TMR5IP:</b> TMR5 Overflow Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                       |

| bit 0 | <b>TMR4IP:</b> TMR4 to PR4 Match Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                   |

#### Note 1: Unimplemented in devices with a program memory of 32 Kbytes (PIC18FX5K90).

bit 0

## 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software-selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or SOSC oscillator internal options

- Interrupt-on-overflow

- Reset on ECCP Special Event Trigger

- Timer with gated control

Figure 13-1 displays a simplified block diagram of the Timer1 module.

The SOSC oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation. Timer1 can also work on the SOSC oscillator.

Timer1 is controlled through the T1CON Control register (Register 13-1), which also contains the SOSC Oscillator Enable bit (SOSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The FOSC clock source should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0 | R/W-0  |

|---------|---------|---------|---------|--------|--------|-------|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | SOSCEN | T1SYNC | RD16  | TMR10N |

| bit 7   | •       |         |         |        |        |       | bit 0  |

| Legend:            |                                                                                                   |                                                                                                                                                                     |                                                                                                                          |                                                        |

|--------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| R = Readable bit W |                                                                                                   | Readable bit W = Writable bit U                                                                                                                                     |                                                                                                                          | read as '0'                                            |

| -n = Value         | at POR                                                                                            | '1' = Bit is set                                                                                                                                                    | '0' = Bit is cleared                                                                                                     | x = Bit is unknown                                     |

| bit 7-6            | 10 = The<br><u>SOSCEN</u><br>External of<br><u>SOSCEN</u><br>Crystal of<br>fuse, COI<br>01 = Time | = 0:<br>clock is from the T1CKI pin (c<br>= 1:                                                                                                                      | a pin or an oscillator dependi<br>on the rising edge).<br>SCO pins or an extended clock<br>n clock (Fosc) <sup>(1)</sup> | ng on the SOSCEN bit.<br>< on SCKLI (depends on SOSCEL |

| bit 5-4            | <b>T1CKPS</b><br>11 = 1:8<br>10 = 1:4<br>01 = 1:2                                                 | x <b>1:0&gt;:</b> Timer1 Input Clock Pro<br>Prescale value<br>Prescale value<br>Prescale value<br>Prescale value<br>Prescale value                                  |                                                                                                                          |                                                        |

| bit 3              | 1 = SOS0<br>0 = SOS0                                                                              | : SOSC Oscillator Enable bit<br>C is enabled for Timer1 (base<br>C is disabled for Timer1<br>ator inverter and feedback re                                          |                                                                                                                          | te power drain.                                        |

| bit 2              | <u>TMR1CS</u><br>1 = Do no<br>0 = Syncl<br><u>TMR1CS</u>                                          | Timer1 External Clock Input<br><1:0> = 10:<br>to synchronize the external clored<br>for onize the external clock inp<br><1:0> = 0x:<br>ignored. Timer1 uses the int | ock input                                                                                                                | 0> = 1x.                                               |

| bit 1              | <b>RD16:</b> 16<br>1 = Enat                                                                       | -Bit Read/Write Mode Enable<br>les register read/write of Tim<br>les register read/write of Tim                                                                     | e bit<br>er1 in one 16-bit operation                                                                                     |                                                        |

| bit 0              | TMR1ON                                                                                            | : Timer1 On bit<br>les Timer1                                                                                                                                       |                                                                                                                          |                                                        |

Note 1: The Fosc clock source should not be selected if the timer will be used with the ECCP capture/compare features.

## 13.7 Resetting Timer1 Using the ECCP Special Event Trigger

If ECCP modules are configured to use Timer1 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer1. The trigger from ECCP2 will also start an A/D conversion, if the A/D module is enabled. (For more information, see **Section 19.3.4 "Special Event Trigger"**.)

To take advantage of this feature, the module must be configured as either a timer or a synchronous counter. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

| Note: | The Special Event Trigger from the         |

|-------|--------------------------------------------|

|       | ECCPx module will only clear the TMR1      |

|       | register's content, but not set the TMR1IF |

|       | interrupt flag bit (PIR1<0>).              |

## 13.8 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using the Timer1 gate circuitry. This is also referred to as Timer1 gate count enable.

Timer1 gate can also be driven by multiple selectable sources.

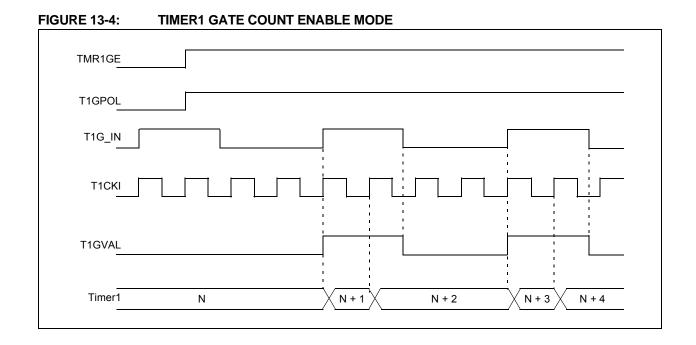

## 13.8.1 TIMER1 GATE COUNT ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit (T1GCON<6>).

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 13-4 for timing details.

| TABLE 13-3: | TIMER1 GATE ENABLE |

|-------------|--------------------|

|             | SELECTIONS         |

| T1CLK <sup>(†)</sup> | T1GPOL<br>(T1GCON<6>) | T1G Pin | Timer1 Operation |

|----------------------|-----------------------|---------|------------------|

| $\uparrow$           | 0                     | 0       | Counts           |

| $\uparrow$           | 0                     | 1       | Holds Count      |

| $\uparrow$           | 1                     | 0       | Holds Count      |

| $\uparrow$           | 1                     | 1       | Counts           |

† The clock on which TMR1 is running. For more information, see Figure 13-1.

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 18-2, Register 18-3 and Register 19-2

© 2009-2011 Microchip Technology Inc.

## REGISTER 17-5: ALRMRPT: ALARM REPEAT REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

The counter decrements on any alarm event. The counter is prevented from rolling over from 00h to FFh unless CHIME = 1.

### 17.1.2 RTCVALH AND RTCVALL REGISTER MAPPINGS

#### REGISTER 17-6: RESERVED REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 Unimplemented: Read as '0'

## 18.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F87K90 family devices have seven CCP (Capture/Compare/PWM) modules, designated CCP4 through CCP10. All the modules implement standard Capture, Compare and Pulse-Width Modulation (PWM) modes.

**Note:** Throughout this section, generic references are used for register and bit names that are the same, except for an 'x' variable that indicates the item's association with the specific CCP module. For example, the control register is named CCPxCON and refers to CCP4CON through CCP10CON.

Each CCP module contains a 16-bit register that can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operation in the following sections is described with respect to CCP4, but is equally applicable to CCP5 through CCP10.

Note: The CCP9 and CCP10 modules are disabled on the devices with 32 Kbytes of program memory (PIC18FX5K90).

## REGISTER 18-1: CCPxCON: CCPx CONTROL REGISTER (CCP4-CCP10 MODULES)<sup>(1)</sup>

| U-0        | U-0                              | R/W-0                                                                                | R/W-0          | R/W-0                                    | R/W-0            | R/W-0           | R/W-0                    |

|------------|----------------------------------|--------------------------------------------------------------------------------------|----------------|------------------------------------------|------------------|-----------------|--------------------------|

|            | _                                | DCxB1                                                                                | DCxB0          | CCPxM3                                   | CCPxM2           | CCPxM1          | CCPxM0                   |

| bit 7      |                                  |                                                                                      | ·              |                                          |                  | -<br>-          | bit 0                    |

| Legend:    |                                  |                                                                                      |                |                                          |                  |                 |                          |

| R = Read   | able bit                         | W = Writable                                                                         | bit            | U = Unimplen                             | nented bit, rea  | d as '0'        |                          |

| -n = Value | e at POR                         | '1' = Bit is set                                                                     |                | '0' = Bit is cle                         | ared             | x = Bit is unkr | nown                     |

| bit 7-6    | Unimplemen                       | ted: Read as '                                                                       | כי             |                                          |                  |                 |                          |

| bit 5-4    | DCxB<1:0>:                       | PWM Duty Cyc                                                                         | le for CCPx N  | 1odule bits (bit 1                       | , bit 0)         |                 |                          |

|            | Capture mod                      | <u>e:</u>                                                                            |                |                                          | · ·              |                 |                          |

|            | Unused.                          |                                                                                      |                |                                          |                  |                 |                          |

|            | Compare mo                       | <u>de</u> :                                                                          |                |                                          |                  |                 |                          |

|            | Unused.                          |                                                                                      |                |                                          |                  |                 |                          |

|            | <u>PWM mode:</u>                 |                                                                                      |                | he (hit 1 and hit )                      | 0) of the 10 hit |                 | la Tha airtht            |

|            |                                  |                                                                                      |                | ts (bit 1 and bit (<br>uty cycle are for |                  |                 | ie. The eight            |

| bit 3-0    | •                                | : CCPx Module                                                                        |                |                                          |                  |                 |                          |

|            | 0000 = Cap                       | ture/Compare/F                                                                       | WM disabled    | (resets CCPx n                           | nodule)          |                 |                          |

|            | 0001 = Res                       |                                                                                      |                |                                          |                  |                 |                          |

|            |                                  |                                                                                      | gle output on  | match (CCPxIF                            | bit is set)      |                 |                          |

|            | 0011 = Res                       |                                                                                      | . falling adap |                                          |                  |                 |                          |

|            |                                  | ture mode: ever                                                                      |                |                                          |                  |                 |                          |

|            |                                  | 0101 = Capture mode: every rising edge<br>0110 = Capture mode: every 4th rising edge |                |                                          |                  |                 |                          |

|            |                                  | ture mode: ever                                                                      |                |                                          |                  |                 |                          |

|            | 1000 = Com<br>is se              | ·                                                                                    | ialize CCPx p  | in low; on comp                          | are match, for   | ce CCPx pin hi  | gh (CCPxIF bit           |

|            |                                  | pare mode: init                                                                      | ialize CCPx p  | in high; on com                          | pare match, fo   | rce CCPx pin lo | w (CCPxIF bit            |

|            | 1010 = Com                       | ,                                                                                    | nerate softwa  | re interrupt on c                        | compare match    | (CCPxIF bit is  | set, CCPx pin            |

|            |                                  | npare mode: Sp                                                                       | ecial Event Tr | igger; reset time                        | er on CCPx ma    | atch (CCPxIF bi | t is set) <sup>(2)</sup> |

| Note 1:    | The CCP9 and C<br>(PIC18FX5K90). | CP10 modules                                                                         | are not availa | ble on devices                           | with 32 Kbytes   | s of program me | emory                    |

2: CCPxM<3:0> = 1011 will only reset the timer and not start the A/D conversion on a CCPx match.

### REGISTER 18-3: CCPTMRS2: CCPx TIMER SELECT REGISTER 2

| U-0   | U-0 | U-0 | R/W-0                   | U-0 | R/W-0                  | R/W-0   | R/W-0   |

|-------|-----|-----|-------------------------|-----|------------------------|---------|---------|

| —     | —   | _   | C10TSEL0 <sup>(1)</sup> | —   | C9TSEL0 <sup>(1)</sup> | C8TSEL1 | C8TSEL0 |

| bit 7 |     |     |                         |     |                        |         | bit 0   |

| Legend:           |                           |                        |                    |

|-------------------|---------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared   | x = Bit is unknown |

| -n = Value at POR | $1^{\prime}$ = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                         |

|---------|----------------------------------------------------|

| bit 4   | C10TSEL0: CCP10 Timer Selection bit <sup>(1)</sup> |

|         | 0 = CCP10 is based off of TMR1/TMR2                |

|         | 1 = CCP10 is based off of TMR7/TMR2                |

| bit 3   | Unimplemented: Read as '0'                         |

| bit 2   | C9TSEL0: CCP9 Timer Selection bit <sup>(1)</sup>   |

|         | 0 = CCP9 is based off of TMR1/TMR2                 |

|         | 1 = CCP9 is based off of TMR7/TMR4                 |

| bit 1-0 | C8TSEL<1:0>: CCP8 Timer Selection bits             |

|         | On non 32-Kbyte device variants:                   |

|         | 00 = CCP8 is based off of TMR1/TMR2                |

|         | 01 = CCP8 is based off of TMR7/TMR4                |

|         | 10 = CCP8 is based off of TMR7/TMR6                |

|         | 11 = Reserved; do not use                          |

|         | On 32-Kbyte device variants (PIC18F85K90/65K90:    |

|         | 00 = CCP8 is based off of TMR1/TMR2                |

|         | 01 = CCP8 is based off of TMR1/TMR4                |

|         | 10 = CCP8 is based off of TMR1/TMR6                |

11 = Reserved; do not use

Note 1: This bit is unimplemented and reads as '0' on devices with 32 Kbytes of program memory (PIC18FX5K90).

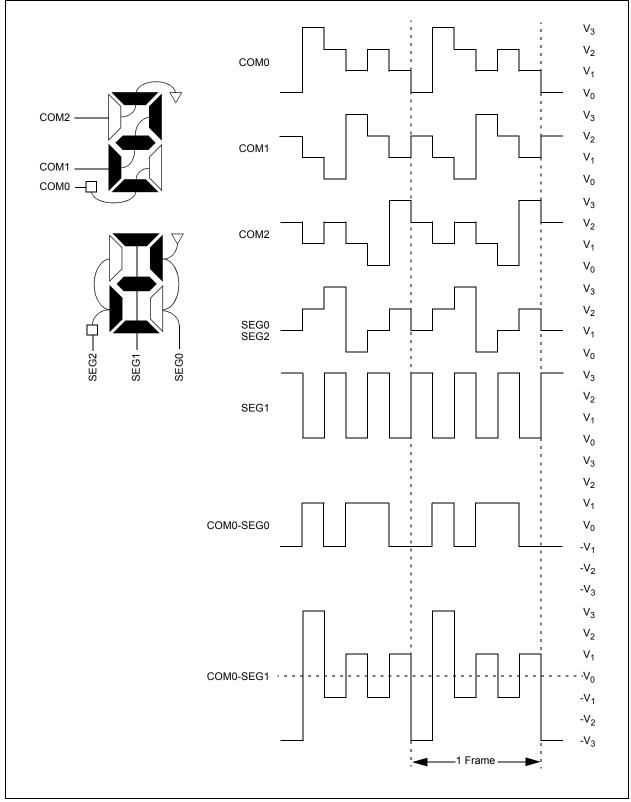

### FIGURE 20-14: TYPE-A WAVEFORMS IN 1/3 MUX, 1/3 BIAS DRIVE

## 21.4 I<sup>2</sup>C<sup>™</sup> Mode

FIGURE 21-7.

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support), and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial Clock (SCLx) RC3/SCK1/SCL1/SEG17 or RD6/SEG6/SCK2/SCL2

- Serial Data (SDAx) RC4/SDI1/SDA1/SEG16 or RD5/SEG5/SDI2/SDA2

The user must configure these pins as inputs by setting the associated TRIS bits.

MSSPY BLOCK DIAGRAM

| FIGURE 21-7: | MSSPx BLOCK DIAGRAM<br>(I <sup>2</sup> C™ MODE)                                                    |

|--------------|----------------------------------------------------------------------------------------------------|

| Read -       | k↓<br>SSPxSR reg ◀                                                                                 |

|              | Start and<br>Stop bit Detect S, P bits<br>(SSPxSTAT reg)                                           |

|              | ) names are used in this diagram for<br>revity. Refer to the text for a full list of<br>functions. |

## 21.4.1 REGISTERS

The MSSP module has seven registers for  ${\rm I}^2{\rm C}$  operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Control Register 2 (SSPxCON2)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

- MSSPx Address Register (SSPxADD)

- I<sup>2</sup>C Slave Address Mask Register (SSPxMSK)

SSPxCON1, SSPxCON2 and SSPxSTAT are the control and status registers in I<sup>2</sup>C mode operation. The SSPxCON1 and SSPxCON2 registers are readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

SSPxADD contains the slave device address when the MSSP is configured in  $I^2C$  Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPxADD act as the Baud Rate Generator reload value.

SSPxMSK holds the slave address mask value when the module is configured for 7-Bit Address Masking mode. While it is a separate register, it shares the same SFR address as SSPxADD. It is only accessible when the SSPM<3:0> bits are specifically set to permit access. Additional details are provided in Section 21.4.3.4 "7-Bit Address Masking Mode".

In receive operations, SSPxSR and SSPxBUF together, create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

| REGISTER      | 21-6: SSPx                                                                                                                                                                                                           | CON2: MSSI       | Px CONTRO | L REGISTER           | 2 (I <sup>2</sup> C™ SLA | VE MODE)           |                    |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|----------------------|--------------------------|--------------------|--------------------|--|--|

| R/W-0         | R/W-0                                                                                                                                                                                                                | R/W-0            | R/W-0     | R/W-0                | R/W-0                    | R/W-0              | R/W-0              |  |  |

| GCEN          | ACKSTAT                                                                                                                                                                                                              | ADMSK5           | ADMSK4    | ADMSK3               | ADMSK2                   | ADMSK1             | SEN <sup>(1)</sup> |  |  |

| bit 7         |                                                                                                                                                                                                                      |                  |           |                      |                          |                    | bit C              |  |  |

| Legend:       |                                                                                                                                                                                                                      |                  |           |                      |                          |                    |                    |  |  |

| R = Readabl   | e bit                                                                                                                                                                                                                | W = Writable     | bit       | U = Unimplen         | nented bit, read         | 1 as '0'           |                    |  |  |

| -n = Value at | POR                                                                                                                                                                                                                  | '1' = Bit is set |           | '0' = Bit is cleared |                          | x = Bit is unknown |                    |  |  |

| bit 7         | <b>GCEN:</b> General Call Enable bit<br>1 = Enables interrupt when a general call address (0000h) is received in the SSPxSR<br>0 = General call address is disabled                                                  |                  |           |                      |                          |                    |                    |  |  |

| bit 6         | ACKSTAT: Acknowledge Status bit<br>Unused in Slave mode.                                                                                                                                                             |                  |           |                      |                          |                    |                    |  |  |

| bit 5-2       | ADMSK<5:2>: Slave Address Mask Select bits (5-Bit Address Masking mode)<br>1 = Masking of corresponding bits of SSPxADD is enabled<br>0 = Masking of corresponding bits of SSPxADD is disabled                       |                  |           |                      |                          |                    |                    |  |  |

| bit 1         | ADMSK1: Slave Address Least Significant bit(s) Mask Select bit<br>In 7-Bit Addressing mode:<br>1 = Masking of SSPxADD<1> only is enabled<br>0 = Masking of SSPxADD<1> only is disabled<br>In 10-Bit Addressing mode: |                  |           |                      |                          |                    |                    |  |  |

| bit 0         | <ul> <li>1 = Masking of SSPxADD&lt;1:0&gt; is enabled</li> <li>0 = Masking of SSPxADD&lt;1:0&gt; is disabled</li> <li>SEN: Stretch Enable bit<sup>(1)</sup></li> </ul>                                               |                  |           |                      |                          |                    |                    |  |  |

|               | <ul> <li>1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)</li> <li>0 = Clock stretching is disabled</li> </ul>                                                            |                  |           |                      |                          |                    |                    |  |  |

**Note 1:** If the I<sup>2</sup>C module is active, this bit may not be set (no spooling) and the SSPxBUF may not be written to (or writes to the SSPxBUF are disabled).

| REGISTER 21-7: | SSPxMSK: I <sup>2</sup> C <sup>™</sup> SLAVE ADDRESS MASK REGISTER (7-BIT MASKING MODE) <sup>(1)</sup> |

|----------------|--------------------------------------------------------------------------------------------------------|

|----------------|--------------------------------------------------------------------------------------------------------|

| R/W-1       | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1               |

|-------------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7        | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(2)</sup> |

| bit 7 bit 0 |       |       |       |       |       |       |                     |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 MSK<7:0>: Slave Address Mask Select bit

1 = Masking of the corresponding bit of SSPxADD is enabled

0 = Masking of the corresponding bit of SSPxADD is disabled

Note 1: This register shares the same SFR address as SSPxADD and is only addressable in select MSSPx operating modes. See Section 21.4.3.4 "7-Bit Address Masking Mode" for more details.

2: MSK0 is not used as a mask bit in 7-bit addressing.

#### © 2009-2011 Microchip Technology Inc.

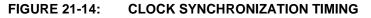

## 21.4.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCLx output is forced to '0'. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external  $I^2C$  master device has

already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 21-14).

| TABLE 21-4: | <b>REGISTERS ASSOCIATED WITH I<sup>2</sup>C™ OPERATION</b> |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

| Name                   | Bit 7                                                                                                                    | Bit 6     | Bit 5                 | Bit 4                 | Bit 3     | Bit 2     | Bit 1         | Bit 0   | Reset<br>Values<br>on Page: |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|-----------------------|-----------|-----------|---------------|---------|-----------------------------|

| INTCON                 | GIE/GIEH                                                                                                                 | PEIE/GIEL | TMR0IE                | INT0IE                | RBIE      | TMR0IF    | <b>INT0IF</b> | RBIF    | 75                          |

| PIR1                   | _                                                                                                                        | ADIF      | RC1IF                 | TX1IF                 | SSP1IF    | TMR1GIF   | TMR2IF        | TMR1IF  | 77                          |

| PIE1                   | —                                                                                                                        | ADIE      | RC1IE                 | TX1IE                 | SSP1IE    | TMR1GIE   | TMR2IE        | TMR1IE  | 77                          |

| IPR1                   | _                                                                                                                        | ADIP      | RC1IP                 | TX1IP                 | SSP1IP    | TMR1GIP   | TMR2IP        | TMR1IP  | 77                          |

| PIR2                   | OSCFIF                                                                                                                   |           | SSP2IF                | BLC2IF                | BCL1IF    | HLVDIF    | TMR3IF        | TMR3GIF | 77                          |

| PIE2                   | OSCFIE                                                                                                                   | _         | SSP2IE                | BLC2IE                | BCL1IE    | HLVDIE    | TMR3IE        | TMR3GIE | 77                          |

| IPR2                   | OSCFIP                                                                                                                   | _         | SSP2IP                | BLC2IP                | BCL1IP    | HLVDIP    | TMR3IP        | TMR3GIP | 77                          |

| PIR3                   | TMR5GIF                                                                                                                  | LCDIF     | RC2IF                 | TX2IF                 | CTMUIF    | CCP2IF    | CCP1IF        | RTCCIF  | 77                          |

| PIE3                   | TMR5GIE                                                                                                                  | LCDIE     | RC2IE                 | TX2IE                 | CTMUIE    | CCP2IE    | CCP1IE        | RTCCIE  | 77                          |

| IPR3                   | TMR5GIP                                                                                                                  | LCDIP     | RC2IP                 | TX2IP                 | CTMUIP    | CCP2IP    | CCP1IP        | RTCCIP  | 77                          |

| TRISC                  | TRISC7                                                                                                                   | TRISC6    | TRISC5                | TRISC4                | TRISC3    | TRISC2    | TRISC1        | TRISC0  | 78                          |

| TRISD                  | TRISD7                                                                                                                   | TRISD6    | TRISD5                | TRISD4                | TRISD3    | TRISD2    | TRISD1        | TRISD0  | 78                          |

| SSP1BUF                | MSSP1 Receive Buffer/Transmit Register                                                                                   |           |                       |                       |           |           |               | 76      |                             |

| SSP1ADD                | MSSP1 Address Register (I <sup>2</sup> C™ Slave mode),<br>MSSP1 Baud Rate Reload Register (I <sup>2</sup> C Master mode) |           |                       |                       |           |           |               | 76      |                             |

| SSP1MSK <sup>(1)</sup> | MSK7                                                                                                                     | MSK6      | MSK5                  | MSK4                  | MSK3      | MSK2      | MSK1          | MSK0    | _                           |

| SSP1CON1               | WCOL                                                                                                                     | SSPOV     | SSPEN                 | CKP                   | SSPM3     | SSPM2     | SSPM1         | SSPM0   | 76                          |

|                        | GCEN                                                                                                                     | ACKSTAT   | ACKDT                 | ACKEN                 | RCEN      | PEN       | RSEN          | SEN     | 76                          |

| SSP1CON2               | GCEN                                                                                                                     | ACKSTAT   | ADMSK5(2)             | ADMSK4(2)             | ADMSK3(2) | ADMSK2(2) | ADMSK1(2)     | SEN     |                             |

| SSP1STAT               | SMP                                                                                                                      | CKE       | D/A                   | Р                     | S         | R/W       | UA            | BF      | 76                          |

| SSP2BUF                | MSSP2 Receive Buffer/Transmit Register                                                                                   |           |                       |                       |           |           |               | 82      |                             |

| SSP2ADD                | MSSP2 Address Register (I <sup>2</sup> C Slave mode),<br>MSSP2 Baud Rate Reload Register (I <sup>2</sup> C Master mode)  |           |                       |                       |           |           |               | 82      |                             |

| SSP2MSK <sup>(1)</sup> | MSK7                                                                                                                     | MSK6      | MSK5                  | MSK4                  | MSK3      | MSK2      | MSK1          | MSK0    | —                           |

| SSP2CON1               | WCOL                                                                                                                     | SSPOV     | SSPEN                 | CKP                   | SSPM3     | SSPM2     | SSPM1         | SSPM0   | 82                          |

| SSP2CON2               | GCEN                                                                                                                     | ACKSTAT   | ACKDT                 | ACKEN                 | RCEN      | PEN       | RSEN          | SEN     | - 83                        |

|                        | GCEN                                                                                                                     | ACKSTAT   | ADMSK5 <sup>(2)</sup> | ADMSK4 <sup>(2)</sup> | ADMSK3(2) | ADMSK2(2) | ADMSK1(2)     | SEN     |                             |

| SSP2STAT               | SMP                                                                                                                      | CKE       | D/A                   | Р                     | S         | R/W       | UA            | BF      | 82                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

Note 1: SSPxMSK shares the same address in SFR space as SSPxADD, but is only accessible in certain I<sup>2</sup>C<sup>™</sup> Slave operating modes in 7-Bit Masking mode. See Section 21.4.3.4 "7-Bit Address Masking Mode" for more details.

2: Alternate bit definitions for use in I<sup>2</sup>C Slave mode operations only.

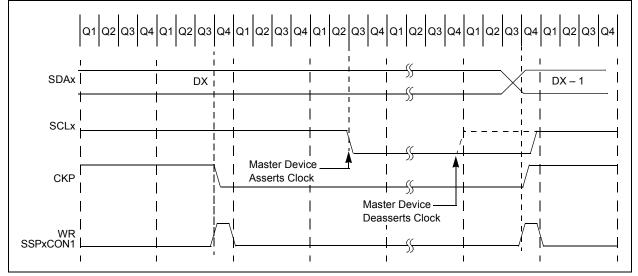

## 28.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the LF-INTOSC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 28-4) is accomplished by creating a sample clock signal, which is the output from the LF-INTOSC, divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor (CM) latch. The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 28-5). This causes the following:

- The FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>)

- The device clock source switches to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-Safe condition)

- The WDT is reset

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing-sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 28.4.1 "Special Considerations for Using Two-Speed Start-up" for more details.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

The FSCM will detect only failures of the primary or secondary clock sources. If the internal oscillator block fails, no failure would be detected nor would any action be possible.

## 28.5.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTOSC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTOSC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF<2:0> bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed, and decreasing the likelihood of an erroneous time-out.

## 28.5.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as the OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

#### 29.2.3 BYTE-ORIENTED AND BIT-ORIENTED INSTRUCTIONS IN INDEXED LITERAL OFFSET MODE

| Note: | Enabling the PIC18 instruction set exten- |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | sion may cause legacy applications to     |  |  |  |  |  |

|       | behave erratically or fail entirely.      |  |  |  |  |  |

In addition to eight new commands in the extended set, enabling the extended instruction set also enables Indexed Literal Offset Addressing (Section 6.6.1 "Indexed Addressing with Literal Offset"). This has a significant impact on the way that many commands of the standard PIC18 instruction set are interpreted.

When the extended set is disabled, addresses embedded in opcodes are treated as literal memory locations: either as a location in the Access Bank (a = 0) or in a GPR bank designated by the BSR (a = 1). When the extended instruction set is enabled and a = 0, however, a file register argument of 5Fh or less is interpreted as an offset from the pointer value in FSR2 and not as a literal address. For practical purposes, this means that all instructions that use the Access RAM bit as an argument – that is, all byte-oriented and bit-oriented instructions, or almost half of the core PIC18 instructions – may behave differently when the extended instruction set is enabled.

When the content of FSR2 is 00h, the boundaries of the Access RAM are essentially remapped to their original values. This may be useful in creating backward compatible code. If this technique is used, it may be necessary to save the value of FSR2 and restore it when moving back and forth between C and assembly routines in order to preserve the Stack Pointer. Users must also keep in mind the syntax requirements of the extended instruction set (see Section 29.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands").

Although the Indexed Literal Offset mode can be very useful for dynamic stack and pointer manipulation, it can also be very annoying if a simple arithmetic operation is carried out on the wrong register. Users who are accustomed to the PIC18 programming must keep in mind, that when the extended instruction set is enabled, register addresses of 5Fh or less are used for Indexed Literal Offset Addressing.

Representative examples of typical byte-oriented and bit-oriented instructions in the Indexed Literal Offset mode are provided on the following page to show how execution is affected. The operand conditions shown in the examples are applicable to all instructions of these types.

### 29.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands

When the extended instruction set is enabled, the file register argument, 'f', in the standard byte-oriented and bit-oriented commands is replaced with the literal offset value, 'k'. As already noted, this occurs only when 'f' is less than or equal to 5Fh. When an offset value is used, it must be indicated by square brackets ("[]"). As with the extended instructions, the use of brackets indicates to the compiler that the value is to be interpreted as an index or an offset. Omitting the brackets, or using a value greater than 5Fh within the brackets, will generate an error in the MPASM<sup>™</sup> Assembler.

If the index argument is properly bracketed for Indexed Literal Offset Addressing, the Access RAM argument is never specified; it will automatically be assumed to be '0'. This is in contrast to standard operation (extended instruction set disabled), when 'a' is set on the basis of the target address. Declaring the Access RAM bit in this mode will also generate an error in the MPASM Assembler.

The destination argument, 'd', functions as before.

In the latest versions of the MPASM Assembler, language support for the extended instruction set must be explicitly invoked. This is done with either the command line option,  $/_{Y}$ , or the PE directive in the source listing.

## 29.2.4 CONSIDERATIONS WHEN ENABLING THE EXTENDED INSTRUCTION SET

It is important to note that the extensions to the instruction set may not be beneficial to all users. In particular, users who are not writing code that uses a software stack may not benefit from using the extensions to the instruction set.

Additionally, the Indexed Literal Offset Addressing mode may create issues with legacy applications written to the PIC18 assembler. This is because instructions in the legacy code may attempt to address registers in the Access Bank below 5Fh. Since these addresses are interpreted as literal offsets to FSR2 when the instruction set extension is enabled, the application may read or write to the wrong data addresses.

When porting an application to the PIC18F87K90 family, it is very important to consider the type of code. A large, re-entrant application that is written in C and would benefit from efficient compilation will do well when using the instruction set extensions. Legacy applications that heavily use the Access Bank will most likely not benefit from using the extended instruction set.

## Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3180 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470