Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 69                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87k90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

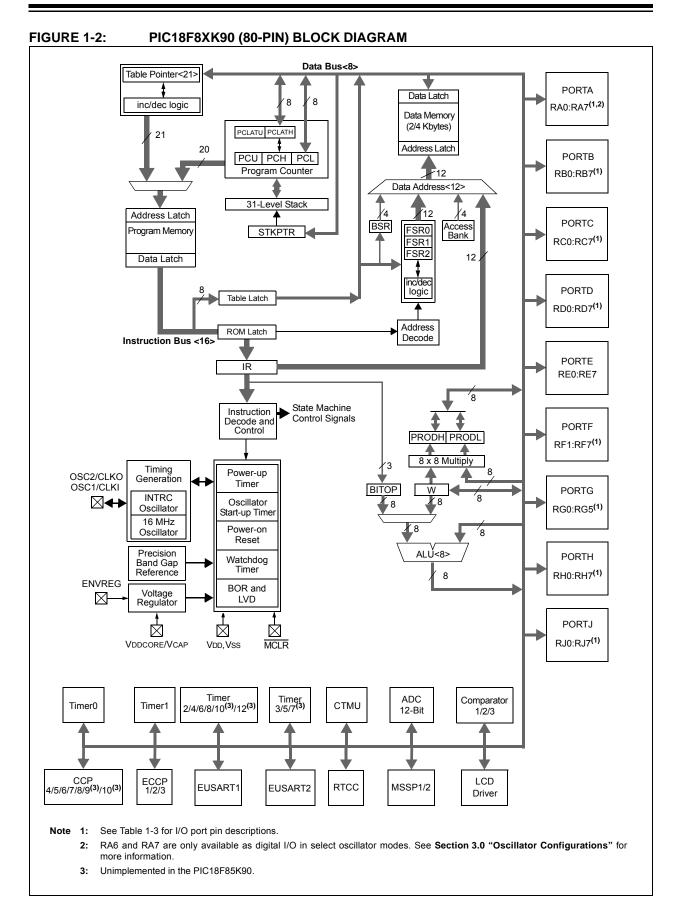

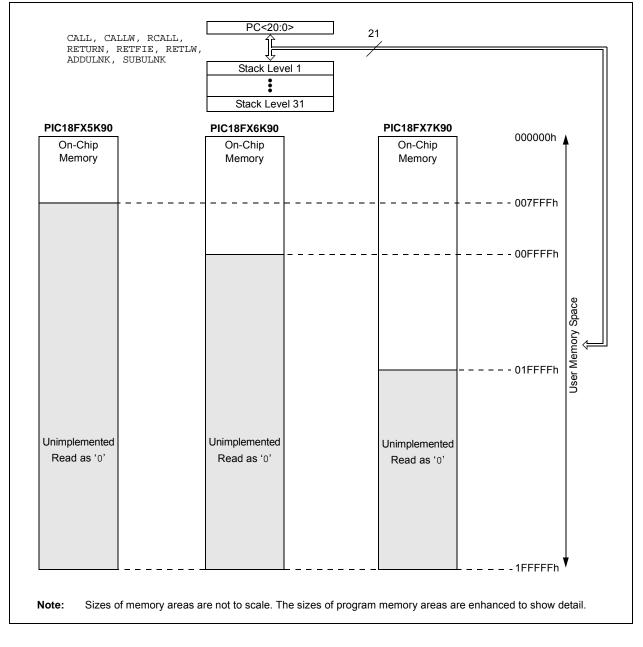

### 6.0 MEMORY ORGANIZATION

PIC18F87K90 family devices have these types of memory:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses. This enables concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device because it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**. The data EEPROM is discussed separately in **Section 8.0 "Data EEPROM Memory"**.

### FIGURE 6-1: MEMORY MAPS FOR PIC18F87K90 FAMILY DEVICES

### 10.5 RCON Register

bit 3

bit 2

bit 1

bit 0

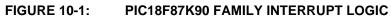

The RCON register contains the bits used to determine the cause of the last Reset, or wake-up from Idle or Sleep modes. RCON also contains the bit that enables interrupt priorities (IPEN).

### REGISTER 10-22: RCON: RESET CONTROL REGISTER

**TO:** Watchdog Timer Time-out Flag bit

PD: Power-Down Detection Flag bit

**POR:** Power-on Reset Status bit

BOR: Brown-out Reset Status bit

For details of bit operation, see Register 5-1.

| R/W-0 | R/W-1  | R/W-1 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|--------|-------|-------|-----|-----|-------|-------|

| IPEN  | SBOREN | CM    | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |        |       |       |     |     |       | bit 0 |

| Legend:    |             |                                         |                               |                                    |  |  |  |

|------------|-------------|-----------------------------------------|-------------------------------|------------------------------------|--|--|--|

| R = Read   | able bit    | W = Writable bit                        | U = Unimplemented bit         | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value | e at POR    | '1' = Bit is set                        | '0' = Bit is cleared          | x = Bit is unknown                 |  |  |  |

|            |             |                                         |                               |                                    |  |  |  |

| bit 7      | IPEN: Int   | errupt Priority Enable bit              |                               |                                    |  |  |  |

|            | 1 = Enat    | ole priority levels on interrupt        | S                             |                                    |  |  |  |

|            | 0 = Disa    | ble priority levels on interrup         | ts (PIC16CXXX Compatibility r | node)                              |  |  |  |

| bit 6      | SBOREN      | I: BOR Software Enable bit              |                               |                                    |  |  |  |

|            | If BOREN    | <b>\&lt;1:0&gt; =</b> 01:               |                               |                                    |  |  |  |

|            |             | is enabled                              |                               |                                    |  |  |  |

|            | 0 = BOR     | is disabled                             |                               |                                    |  |  |  |

|            |             | <pre>I&lt;1:0&gt; = 00, 10 or 11:</pre> |                               |                                    |  |  |  |

|            | Bit is disa | abled and read as '0'.                  |                               |                                    |  |  |  |

| bit 5      | CM: Con     | figuration Mismatch Flag bit            |                               |                                    |  |  |  |

|            |             | onfiguration Mismatch Reset             |                               |                                    |  |  |  |

|            | 0 = A Cc    | onfiguration Mismatch Reset             | has occurred (must be subsec  | quently set in software)           |  |  |  |

| bit 4      | RI: RESE    | T Instruction Flag bit                  |                               |                                    |  |  |  |

|            | For detail  | s of bit operation, see Regis           | ter 5-1.                      |                                    |  |  |  |

| REGISTER 11-3: | ODCON3: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 3 |

|----------------|--------------------------------------------------|

|----------------|--------------------------------------------------|

| R/W-0                             | R/W-0                                                                                                                                                                                                           | U-0                                  | U-0           | U-0              | U-0              | U-0             | R/W-0  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|------------------|------------------|-----------------|--------|

| U2OD                              | U10D                                                                                                                                                                                                            | —                                    | —             | —                | —                | —               | CTMUDS |

| bit 7                             | ·                                                                                                                                                                                                               |                                      |               |                  |                  |                 | bit 0  |

|                                   |                                                                                                                                                                                                                 |                                      |               |                  |                  |                 |        |

| Legend:                           |                                                                                                                                                                                                                 |                                      |               |                  |                  |                 |        |

| R = Readable bit W = Writable bit |                                                                                                                                                                                                                 |                                      |               | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at                     | POR                                                                                                                                                                                                             | '1' = Bit is set                     |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7<br>bit 6                    | <ul> <li>U2OD: EUSART2 Open-Drain Output Enable bit</li> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> <li>U1OD: EUSART1 Open-Drain Output Enable bit</li> </ul> |                                      |               |                  |                  |                 |        |

|                                   | <ul> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> </ul>                                                                                                         |                                      |               |                  |                  |                 |        |

| bit 5-1                           | Unimplemented: Read as '0'                                                                                                                                                                                      |                                      |               |                  |                  |                 |        |

| bit 0                             | CTMUDS: CT                                                                                                                                                                                                      | MU Pulse Dela                        | ay Enable bit |                  |                  |                 |        |

|                                   |                                                                                                                                                                                                                 | lay input for CT<br>lay input for CT |               |                  |                  |                 |        |

#### 11.1.4 ANALOG AND DIGITAL PORTS

Many of the ports multiplex analog and digital functionality, providing a lot of flexibility for hardware designers. PIC18F87K90 family devices can make any analog pin, analog or digital, depending on an application's needs. The ports' analog/digital functionality is controlled by the registers: ANCON0, ANCON1 and ANCON2. Setting these registers makes the corresponding pins analog and clearing the registers makes the ports digital. For details on these registers, see Section 23.0 "12-Bit Analog-to-Digital Converter (A/D) Module".

### REGISTER 16-1: TxCON: TIMER4/6/8/10/12 CONTROL REGISTER

| U-0           | R/W-0                                             | R/W-0            | R/W-0                        | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |

|---------------|---------------------------------------------------|------------------|------------------------------|-------------------|-----------------|-----------------|---------|--|

|               | TxOUTPS3                                          | TxOUTPS2         | TxOUTPS1                     | TxOUTPS0          | TMRxON          | TxCKPS1         | TxCKPS0 |  |

| bit 7         |                                                   |                  |                              |                   |                 |                 | bit 0   |  |

|               |                                                   |                  |                              |                   |                 |                 |         |  |

| Legend:       |                                                   |                  |                              |                   |                 |                 |         |  |

| R = Readabl   | e bit                                             | W = Writable     | oit                          | U = Unimplem      | ented bit, read | l as '0'        |         |  |

| -n = Value at | POR                                               | '1' = Bit is set |                              | '0' = Bit is clea | ired            | x = Bit is unkn | own     |  |

|               |                                                   |                  |                              |                   |                 |                 |         |  |

| bit 7         | Unimplemen                                        | ted: Read as 'd  | )'                           |                   |                 |                 |         |  |

| bit 6-3       | TxOUTPS<3:0>: Timerx Output Postscale Select bits |                  |                              |                   |                 |                 |         |  |

|               | 0000 = 1:1 Po                                     | ostscale         |                              |                   |                 |                 |         |  |

|               | 0001 <b>= 1:2 P</b>                               | ostscale         |                              |                   |                 |                 |         |  |

|               | •                                                 |                  |                              |                   |                 |                 |         |  |

|               | •                                                 |                  |                              |                   |                 |                 |         |  |

|               | 1111 = 1:16 F                                     | Postscale        |                              |                   |                 |                 |         |  |

| bit 2         | TMRxON: Tin                                       | nerx On bit      |                              |                   |                 |                 |         |  |

| 5.12          | 1 = Timerx is                                     |                  |                              |                   |                 |                 |         |  |

|               | 0 = Timerx is                                     | •••              |                              |                   |                 |                 |         |  |

| bit 1-0       | TxCKPS<1:0                                        | >: Timerx Clocl  | <pre>&lt; Prescale Sel</pre> | ect bits          |                 |                 |         |  |

|               | 00 = Prescale                                     | er is 1          |                              |                   |                 |                 |         |  |

|               | 01 = Prescale                                     | -                |                              |                   |                 |                 |         |  |

|               | 1x = Prescale                                     | eris 16          |                              |                   |                 |                 |         |  |

| R/W-0                 | R/W-0                                                                             | R/W-0                                                                                                                                                                                                        | R/W-0                      | R/W-0                     | R/W-0            | R/W-0                 | R/W-0          |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|------------------|-----------------------|----------------|--|--|--|

| PxM1                  | PxM0                                                                              | DCxB1                                                                                                                                                                                                        | DCxB0                      | CCPxM3                    | CCPxM2           | CCPxM1                | CCPxM0         |  |  |  |

| bit 7                 | •                                                                                 |                                                                                                                                                                                                              |                            | •                         | •                | •                     | bit            |  |  |  |

|                       |                                                                                   |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

| Legend:<br>R = Readab | le hit                                                                            | W = Writable                                                                                                                                                                                                 | hit                        | II = I Inimpler           | mented bit, read | d as 'O'              |                |  |  |  |

| -n = Value at         |                                                                                   | '1' = Bit is set                                                                                                                                                                                             |                            | '0' = Bit is cle          |                  | x = Bit is unk        | nown           |  |  |  |

|                       |                                                                                   |                                                                                                                                                                                                              | •                          |                           | arcu             |                       |                |  |  |  |

| bit 7-6               | <b>PxM&lt;1:0&gt;:</b> E                                                          | Enhanced PWM                                                                                                                                                                                                 | l Output Confi             | guration bits             |                  |                       |                |  |  |  |

|                       | If CCPxM<3:                                                                       | 2> = 00, 01, 10                                                                                                                                                                                              | <u>):</u>                  | -                         |                  |                       |                |  |  |  |

|                       | xx = PxA is                                                                       | assigned as a c                                                                                                                                                                                              | apture/compar              | e input/output; I         | PxB, PxC and P   | xD are assigned       | d as PORT pin  |  |  |  |

|                       | If CCPxM<3:                                                                       |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | output: PxA, P                                                                                                                                                                                               | xB, PxC and                | PxD are contro            | olled by steerin | g (see <b>Section</b> | 19.4.7 "Puls   |  |  |  |

|                       |                                                                                   | n <b>g Mode"</b> )<br>idae output forv                                                                                                                                                                       | vard <sup>.</sup> PxD is n | odulated <sup>.</sup> PxA | is active: PxB   | PxC are inactiv       | /e             |  |  |  |

|                       |                                                                                   | <ul> <li>01 = Full-bridge output forward: PxD is modulated; PxA is active; PxB, PxC are inactive</li> <li>10 = Half-bridge output: PxA, PxB are modulated with dead-band control; PxC and PxD are</li> </ul> |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | ied as PORT pi                                                                                                                                                                                               |                            |                           |                  |                       |                |  |  |  |

|                       | 11 = Full-br                                                                      | idge output revo                                                                                                                                                                                             | erse: PxB is m             | nodulated; PxC            | is active; PxA   | and PxD are in        | active         |  |  |  |

| bit 5-4               | DCxB<1:0>: PWM Duty Cycle Bit 1 and Bit 0                                         |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       | Capture mode:                                                                     |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       | Unused.                                                                           |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       | <u>Compare mo</u><br>Unused.                                                      | <u>de:</u>                                                                                                                                                                                                   |                            |                           |                  |                       |                |  |  |  |

|                       | PWM mode:                                                                         |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | e the two LSbs                                                                                                                                                                                               | of the 10-bit F            | WM duty cycle             | e. The eight MS  | bs of the duty c      | ycle are found |  |  |  |

|                       | in CCPRxL.                                                                        |                                                                                                                                                                                                              |                            |                           | C C              | -                     | -              |  |  |  |

| bit 3-0               | CCPxM<3:0                                                                         | >: ECCPx Mode                                                                                                                                                                                                | e Select bits              |                           |                  |                       |                |  |  |  |

|                       | 0000 = Capture/Compare/PWM off (resets ECCPx module)                              |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       | 0001 = Reserved                                                                   |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       | 0010 = Cor<br>0011 = Cap                                                          | npare mode: to                                                                                                                                                                                               | ggle output or             | match                     |                  |                       |                |  |  |  |

|                       |                                                                                   |                                                                                                                                                                                                              | erv falling edge           | 2                         |                  |                       |                |  |  |  |

|                       | 0100 = Capture mode: every falling edge<br>0101 = Capture mode: every rising edge |                                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       | 0110 = Cap                                                                        | oture mode: eve                                                                                                                                                                                              | ry fourth rising           | g edge                    |                  |                       |                |  |  |  |

|                       |                                                                                   | oture mode: eve                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | npare mode: ini                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | npare mode: init<br>npare mode: ge                                                                                                                                                                           |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | npare mode: tri                                                                                                                                                                                              |                            |                           |                  |                       |                |  |  |  |

|                       | sets                                                                              | CCxIF bit)                                                                                                                                                                                                   |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | M mode: PxA a                                                                                                                                                                                                |                            |                           |                  |                       |                |  |  |  |

|                       |                                                                                   | M mode: PxA a                                                                                                                                                                                                |                            | •                         |                  |                       |                |  |  |  |

|                       | 1110 = PW                                                                         | M mode: PxA a                                                                                                                                                                                                | nd PxC are a               | ctive-low; PxB a          | and PXD are ac   | nve-nigh              |                |  |  |  |

### REGISTER 19-1: CCPxCON: ENHANCED CAPTURE/COMPARE/PWM x CONTROL

1110 = PWM mode: PxA and PxC are active-low; PxB and PxD are active-high 1111 = PWM mode: PxA and PxC are active-low; PxB and PxD are active-low

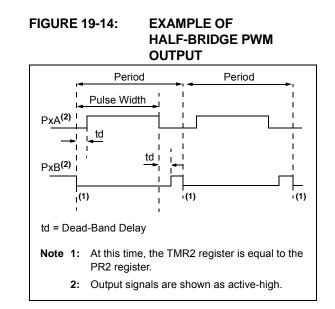

#### 19.4.6 PROGRAMMABLE DEAD-BAND DELAY MODE

In half-bridge applications, where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period until one switch completely turns off. During this brief interval, a very high current (shoot-through current) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. For an illustration, see Figure 19-14. The lower seven bits of the associated ECCPxDEL register (Register 19-4) set the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

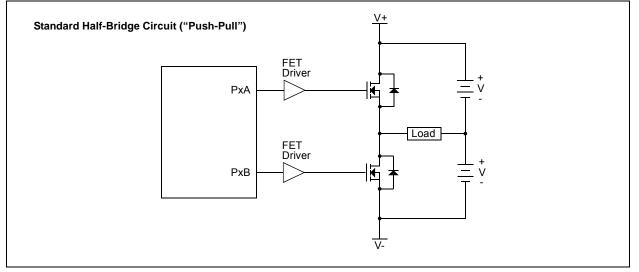

### FIGURE 19-15: EXAMPLE OF HALF-BRIDGE APPLICATIONS

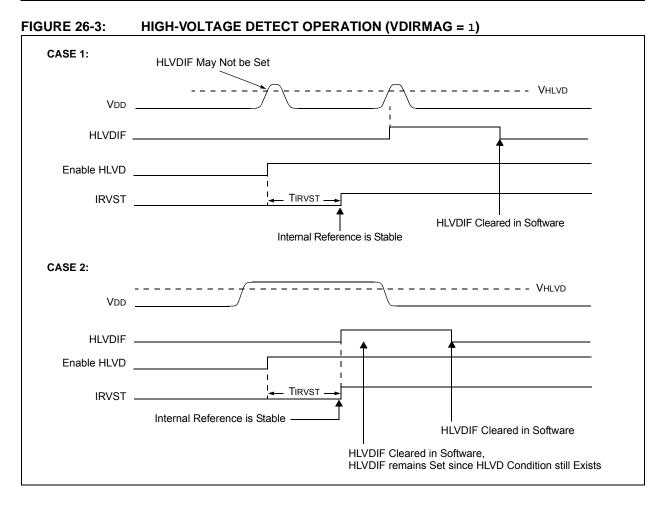

### 26.5 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a High-Voltage Detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

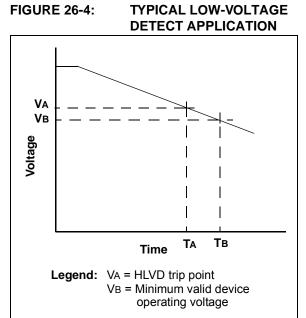

For general battery applications, Figure 26-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR (Interrupt Service Routine), which would allow the application to perform "housekeeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

NOTES:

### REGISTER 28-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0         | R/P-1                  | R/P-1                  | R/P-1                | R/P-1                | R/P-1                 | R/P-1                 | R/P-1                 |

|-------------|------------------------|------------------------|----------------------|----------------------|-----------------------|-----------------------|-----------------------|

| _           | BORPWR1 <sup>(1)</sup> | BORPWR0 <sup>(1)</sup> | BORV1 <sup>(1)</sup> | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BOREN0 <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |

| bit 7 bit 0 |                        |                        |                      |                      |                       |                       |                       |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | BORPWR<1:0>: BORMV Power Level bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>11 = ZPBORVMV instead of BORMV is selected</li> <li>10 = BORMV is set to high-power level</li> <li>01 = BORMV is set to medium-power level</li> <li>00 = BORMV is set to low-power level</li> </ul>                                                                                                                                                   |

| bit 4-3 | BORV<1:0>: Brown-out Reset Voltage bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                         |

|         | 11 = VBORMV is set to 1.8V<br>10 = VBORMV is set to 2.0V<br>01 = VBORMV is set to 2.7V<br>00 = VBORMV is set to 3.0V                                                                                                                                                                                                                                           |

| bit 2-1 | BOREN<1:0>: Brown-out Reset Enable bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>11 = Brown-out Reset is enabled in hardware only (SBOREN is disabled)</li> <li>10 = Brown-out Reset is enabled in hardware only and disabled in Sleep mode (SBOREN is disabled)</li> <li>01 = Brown-out Reset is enabled and controlled by software (SBOREN is enabled)</li> <li>00 = Brown-out Reset is disabled in hardware and software</li> </ul> |

| bit 0   | <b>PWRTEN:</b> Power-up Timer Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                        |

|         | 1 = PWRT is disabled<br>0 = PWRT is enabled                                                                                                                                                                                                                                                                                                                    |

| Note 1: | For the specifications, see Section 31.1 "DC Characteristics: Supply Voltage PIC18F87K90 Family (Industrial/Extended)".                                                                                                                                                                                                                                        |

2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

## REGISTER 28-13: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)<sup>(1)</sup>

| U-0                                | R/C-1                         | U-0 | U-0                                     | U-0                                | U-0 | U-0 | U-0   |  |

|------------------------------------|-------------------------------|-----|-----------------------------------------|------------------------------------|-----|-----|-------|--|

| —                                  | EBTRB                         |     | _                                       | —                                  |     | —   | —     |  |

| bit 7                              |                               |     |                                         | •                                  |     |     | bit 0 |  |

|                                    |                               |     |                                         |                                    |     |     |       |  |

| Legend: C = Clearable bit          |                               |     | bit                                     |                                    |     |     |       |  |

| R = Readable b                     | Readable bit W = Writable bit |     |                                         | U = Unimplemented bit, read as '0' |     |     |       |  |

| -n = Value at POR (1' = Bit is set |                               |     | '0' = Bit is cleared x = Bit is unknown |                                    |     |     |       |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

bit 7 Unimplemented: Read as '0'

| bit 6 | EBTRB: Boot Block Table Read Protection bit |

|-------|---------------------------------------------|

|-------|---------------------------------------------|

1 = Boot block is not protected from table reads executed in other blocks

0 = Boot block is protected from table reads executed in other blocks

bit 5-0 Unimplemented: Read as '0'

Note 1: For the memory size of the blocks, refer to Figure 28-6.

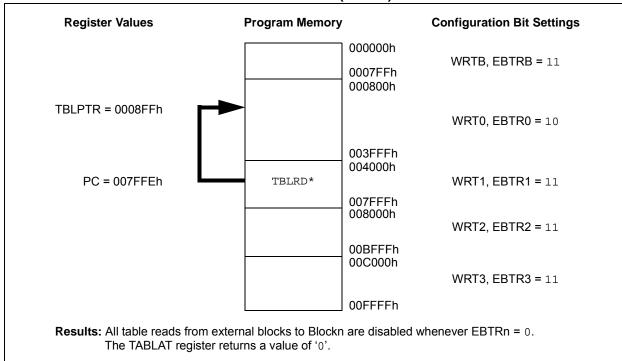

#### FIGURE 28-8: EXTERNAL BLOCK TABLE READ (EBTRn) DISALLOWED

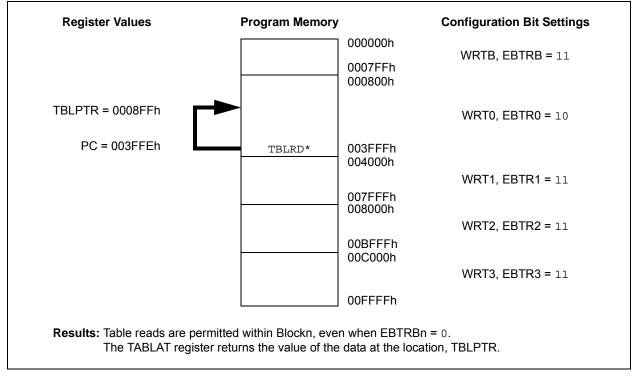

### FIGURE 28-9: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED

ADD W to f

f {,d {,a}}

01da

Add W to register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the

result is stored back in register 'f'.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing

ffff

ffff

ADDWF

$0 \leq f \leq 255$  $d \in [0\,,1]$

a ∈ [0,1]

0010

GPR bank.

$(W) + (f) \rightarrow dest$

N, OV, C, DC, Z

#### 29.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                         | ADD Litera                       | l to W          |      |               | ADDWF                                                               |

|---------------------------------------------------------------|----------------------------------|-----------------|------|---------------|---------------------------------------------------------------------|

| Syntax:                                                       | ADDLW                            | k               |      |               | Syntax:                                                             |

| Operands:                                                     | $0 \le k \le 255$                |                 |      |               | Operands:                                                           |

| Operation:                                                    | $(W) + k \rightarrow V$          | N               |      |               |                                                                     |

| Status Affected:                                              | N, OV, C, D                      | Ю, Z            |      |               | Operation:                                                          |

| Encoding:                                                     | 0000                             | 1111            | kkkk | kkkk          | Status Affected:                                                    |

| Description:                                                  | The conten<br>8-bit literal<br>W |                 |      |               | Encoding:<br>Description:                                           |

| Words:                                                        | 1                                |                 |      |               |                                                                     |

| Cycles:                                                       | 1                                |                 |      |               |                                                                     |

| Q Cycle Activity:                                             |                                  |                 |      |               |                                                                     |

| Q1                                                            | Q2                               | Q3              |      | Q4            |                                                                     |

| Decode                                                        | Read<br>literal 'k'              | Process<br>Data | V    | Vrite to<br>W |                                                                     |

| Example:<br>Before Instruct<br>W =<br>After Instructio<br>W = | tion<br>10h                      | 5h              |      |               | Words:<br>Cycles:<br>Q Cycle Activity:                              |

|                                                               |                                  |                 |      |               | Q1<br>Decode                                                        |

|                                                               |                                  |                 |      |               | Example:<br>Before Instru<br>W<br>REG<br>After Instruct<br>W<br>REG |

mode whenever  $f \le 95$  (5Fh). See Section 29.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details. 1 1 Q4 Q3 Q2 Read Process Write to register 'f Data destination ADDWF REG, 0, 0 uction = 17h = 0C2h tion 0D9h = = 0C2h

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| CLRF                                           | Clear f                                                               |                                           |                | CLRWDT        |          | Clear Wate                             | hdog Timer:     |                                           |

|------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------|----------------|---------------|----------|----------------------------------------|-----------------|-------------------------------------------|

| Syntax:                                        | CLRF f{,                                                              | a}                                        |                | Syntax:       |          | CLRWDT                                 |                 |                                           |

| Operands:                                      | $0 \leq f \leq 255$                                                   |                                           |                | Operands:     |          | None                                   |                 |                                           |

|                                                | $a \in [0,1]$                                                         |                                           |                | Operation:    |          | $000h \rightarrow Wl$                  | ЭT,             |                                           |

| Operation:                                     | $\begin{array}{l} 000h \rightarrow f, \\ 1 \rightarrow Z \end{array}$ |                                           |                | ·             |          | $1 \rightarrow \overline{\text{TO}}$ , | DT postscale    | r,                                        |

| Status Affected:                               | Z                                                                     |                                           |                |               |          | $1 \rightarrow PD$                     |                 |                                           |

| Encoding:                                      | 0110                                                                  | 101a ff:                                  | ff ffff        | Status Affect | cted:    | TO, PD                                 |                 | I                                         |

| Description:                                   | Clears the                                                            | contents of the                           | specified      | Encoding:     |          | 0000                                   | 0000 00         | 000 0100                                  |

|                                                | register.                                                             |                                           |                | Description:  | :        |                                        | struction rese  |                                           |

|                                                | ,                                                                     | he Access Bai<br>he BSR is use            |                |               |          |                                        | e WDT. Statu    | resets <u>the</u> post-<br>s bits, TO and |

|                                                | lf 'a' is '0' a                                                       | nd the extend                             | ed instruction | Words:        |          | 1                                      |                 |                                           |

|                                                |                                                                       | led, this instrue                         |                | Cycles:       |          | 1                                      |                 |                                           |

|                                                |                                                                       | Literal Offset A                          | 0              | Q Cycle Ac    | ctivity: |                                        |                 |                                           |

|                                                |                                                                       | never f ≤ 95 (5l<br>. <b>2.3 "Byte-Or</b> |                | C             | ג1       | Q2                                     | Q3              | Q4                                        |

|                                                | Bit-Oriente                                                           | ed Instruction<br>set Mode" for           | s in Indexed   | Dec           | ode      | No<br>operation                        | Process<br>Data | No<br>operation                           |

| Words:                                         | 1                                                                     |                                           |                |               |          |                                        |                 |                                           |

| Cycles:                                        | 1                                                                     |                                           |                | Example:      |          | CLRWDT                                 |                 |                                           |

| Q Cycle Activity:                              |                                                                       |                                           |                |               | Instruct |                                        | 0               |                                           |

| Q1                                             | Q2                                                                    | Q3                                        | Q4             |               | /DT Cou  |                                        | ?               |                                           |

| Decode                                         | Read                                                                  | Process                                   | Write          |               | /DT Cou  |                                        | 00h             |                                           |

|                                                | register 'f'                                                          | Data                                      | register 'f'   |               | /DT Post |                                        | 0               |                                           |

| Example:                                       | CLRF                                                                  | FLAG_REG,                                 | 1              | Ti<br>P       |          | =                                      | 1<br>1          |                                           |

| Before Instruct<br>FLAG_R<br>After Instruction | EG = 5A<br>on                                                         |                                           |                |               |          |                                        |                 |                                           |

| FLAG_R                                         | EG = 00                                                               | h                                         |                |               |          |                                        |                 |                                           |

| SUBWFB                                                                                                                                                                  | Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | W from f with Borrow                                                                                                                                                                                             | SW        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Syntax:                                                                                                                                                                 | SUBWFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f {,d {,a}}                                                                                                                                                                                                      | Syn       |

| Operands:                                                                                                                                                               | $0 \le f \le 25$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                | Ope       |

|                                                                                                                                                                         | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  |           |

| Operation:                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $(\overline{C}) \rightarrow \text{dest}$                                                                                                                                                                         |           |

| Status Affected:                                                                                                                                                        | (I) = (W) =<br>N, OV, C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                  | Ope       |

| Encoding:                                                                                                                                                               | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                  | ff Stat   |

| Description:                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V and the Carry flag (bor                                                                                                                                                                                        |           |

|                                                                                                                                                                         | from regis<br>method).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ter 'f' (2's complement<br>If 'd' is '0', the result is stored                                                                                                                                                   | bred Des  |

|                                                                                                                                                                         | in register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                  |           |

|                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | the Access Bank is select<br>the BSR is used to select<br>c.                                                                                                                                                     |           |