Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 64MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                     |

| Number of I/O              | 69                                                                             |

| Program Memory Size        | 128KB (64K x 16)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

| Data Converters            | A/D 24x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

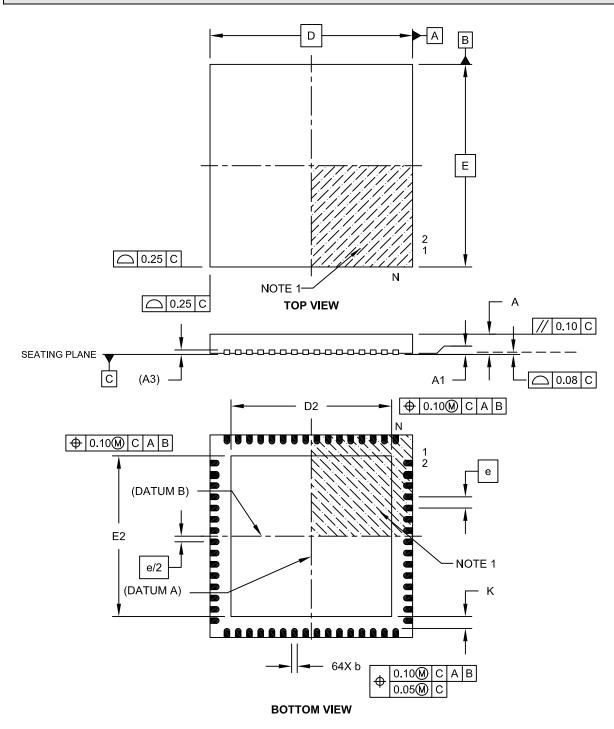

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87k90t-i-ptrsl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Special Microcontroller Features:**

- Operating Voltage Range: 1.8V to 5.5V

- On-Chip 3.3V Regulator

- Operating Speed up to 64 MHz

- Up to 128 Kbytes On-Chip Flash Program Memory

- Data EEPROM of 1,024 Bytes

- 4K x 8 General Purpose Registers (SRAM)

- 10,000 Erase/Write Cycle Flash Program Memory, Minimum

- 1,000,000 Erase/write Cycle Data EEPROM Memory, Typical

- Flash Retention 40 Years, Minimum

- Three Internal Oscillators: LF-INTRC (31 kHz), MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 4,194s (about 70 minutes)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- · In-Circuit Debug via Two Pins

- Programmable:

- BOR

- LVD

- Two Enhanced Addressable USART modules:

- LIN/J2602 support

- Auto-Baud Detect (ABD)

- 12-Bit A/D Converter with up to 24 Channels:

- Auto-acquisition and Sleep operation

- Differential Input mode of operation

#### 3.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC RUN and SEC IDLE), the SOSC oscillator is operating and providing the device clock. The SOSC oscillator may also run in all power-managed modes if required to clock SOSC.

In RC RUN and RC IDLE modes, the internal oscillator provides the device clock source. The 31 kHz LF-INTOSC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 28.2 "Watchdog Timer (WDT)" through Section 28.5 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up).

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped. Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTOSC is required to support WDT operation. The SOSC oscillator may be operating to support a

Real-Time Clock (RTC). Other features may be operating that do not require a device clock source (i.e., MSSP slave, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 31.2 "DC Characteristics: Power-Down and Supply Current PIC18F87K90 Family (Industrial/ Extended)".

#### 3.9 **Power-up Delays**

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see Section 5.6 "Power-up Timer (PWRT)".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on a power-up time of about 64 ms (Parameter 33, Table 31-10); it is always enabled.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (HS, XT or LP modes). The OST does this by counting 1,024 oscillator cycles before allowing the oscillator to clock the device.

There is a delay of interval, TCSD (Parameter 38, Table 31-10), following POR, while the controller becomes ready to execute instructions.

I/O pin, RA6, direction is controlled by

TRISA<7>

**Oscillator Mode OSC1 Pin OSC2** Pin EC, ECPLL Floating, pulled by external clock At logic low (clock/4 output) HS. HSPLL Feedback inverter is disabled at quiescent Feedback inverter is disabled at guiescent voltage level voltage level

I/O pin, RA6, direction is controlled by

**TABLE 3-4**: **OSC1 AND OSC2 PIN STATES IN SLEEP MODE**

TRISA<6>

Note: See Section 5.0 "Reset" for time-outs due to Sleep and MCLR Reset.

INTOSC, INTPLL1/2

### 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode provides controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. To maintain software compatibility with future devices, it is recommended that SCS0 also be cleared, though its value is ignored. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC/MFIOSEL bit is set, the INTOSC output is enabled. The HFIOFS/MFIOFS bits become set, after the INTOSC output becomes stable after an interval of TIOBST (Parameter 38, Table 31-10). (For information on the HFIOFS/MFIOFS bits, see Table 4-3.)

Clocks to the peripherals continue while the INTOSC source stabilizes. The HFIOFS/MFIOFS bits will remain set if the IRCF bits were previously at a non-zero value or if INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the HFIOFS/MFIOFS bits will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD (Parameter 38, Table 31-10), following the wake event, the CPU begins executing code clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 4.5 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what this mode does not provide: the allocation of power resources to the CPU, processing with minimal power consumption from the peripherals.

PIC18F87K90 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- Peripheral Enable bit, generically named XXXEN Located in the respective module's main control register

- Peripheral Module Disable (PMD) bit, generically named XXXMD – Located in one of the PMDx Control registers (PMD0, PMD1, PMD2 or PMD3)

Disabling a module by clearing its XXXEN bit disables the module's functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as the second approach.

Most peripheral modules have an enable bit.

In contrast, setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral are also disabled, so writes to those registers have no effect and read values are invalid. Many peripheral modules have a corresponding PMD bit.

There are four PMD registers in the PIC18F87K90 family devices: PMD0, PMD1, PMD2 and PMD3. These registers have bits associated with each module for disabling or enabling a particular peripheral.

# 5.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering a hard external Reset of the device. A Reset is generated by holding the pin low. PIC18 extended microcontroller devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

# 5.3 Power-on Reset (POR)

A Power-on Reset condition is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (Parameter D004). For a slow rise time, see Figure 5-2.

When the device starts normal operation (exiting the Reset condition), device operating parameters (such as voltage, frequency and temperature) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

Power-on Reset events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a Power-on Reset occurs and does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any Power-on Reset.

## 5.4 Brown-out Reset (BOR)

The PIC18F87K90 family has four BOR modes:

- High-Power BOR

- Medium Power BOR

- Low-Power BOR

- Zero-Power BOR

Each power mode is selected by the BORPWR<1:0> bits setting (CONFIG2L<6:5>). For low, medium and high-power BOR, the module monitors the VDD depending on the BORV<1:0> setting (CONFIG1L<3:2>). A BOR event re-arms the Power-on Reset. It also causes a Reset depending on which of the trip levels has been set: 1.8V, 2V, 2.7V or 3V. The typical ( $\Delta$ IBOR) trip level for the Low and Medium Power BOR will be 0.75 µA and 3 µA.

In Zero-Power BOR (ZPBORMV), the module monitors the VDD voltage and re-arms the POR at about 2V. ZPBORMV does not cause a Reset, but re-arms the POR.

The BOR accuracy varies with its power level. The lower the power setting, the less accurate the BOR trip levels are. So, the high-power BOR has the highest accuracy and the low-power BOR has the lowest accuracy. The trip levels (BVDD, Parameter D005), current consumption (Section 31.2 "DC Characteristics: Power-Down and Supply Current PIC18F87K90 Family (Industrial/Extended)") and time required below BVDD (TBOR, Parameter 35) can all be found in Section 31.0 "Electrical Characteristics"

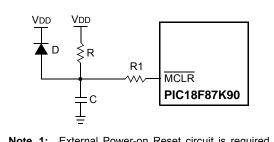

FIGURE 5-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode, D, helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 \ge 1 \ k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor, C, in the event of  $\overline{MCLR}/VPP$  pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

## 5.4.1 DETECTING BOR

The BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. If BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

LP-BOR cannot be detected with the  $\overline{\text{BOR}}$  bit in the RCON register. LP-BOR can rearm the  $\overline{\text{POR}}$  and can cause a Power-on Reset.

### REGISTER 10-21: IPR6: PERIPHERAL INTERRUPT PRIORITY REGISTER 6

| U-0           | U-0                                 | U-0                | R/W-1     | U-0              | R/W-1            | R/W-1           | R/W-1  |  |  |

|---------------|-------------------------------------|--------------------|-----------|------------------|------------------|-----------------|--------|--|--|

| —             | _                                   |                    | EEIP      |                  | CMP3IP           | CMP2IP          | CMP1IP |  |  |

| bit 7         |                                     |                    |           | •                |                  |                 | bit 0  |  |  |

|               |                                     |                    |           |                  |                  |                 |        |  |  |

| Legend:       |                                     |                    |           |                  |                  |                 |        |  |  |

| R = Readable  | e bit                               | W = Writable       | bit       | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |

| -n = Value at | POR                                 | '1' = Bit is set   |           | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |

|               |                                     |                    |           |                  |                  |                 |        |  |  |

| bit 7-5       | Unimplemen                          | ted: Read as '     | כ'        |                  |                  |                 |        |  |  |

| bit 4         | EEIP: EE Inte                       | errupt Priority bi | it        |                  |                  |                 |        |  |  |

|               | 1 = High priority                   |                    |           |                  |                  |                 |        |  |  |

|               | 0 = Low priority                    |                    |           |                  |                  |                 |        |  |  |

| bit 3         | SBOREN: Re                          | ad as '0'          |           |                  |                  |                 |        |  |  |

| bit 2         | CMP3IP: CMP3 Interrupt Priority bit |                    |           |                  |                  |                 |        |  |  |

|               | 1 = High priority                   |                    |           |                  |                  |                 |        |  |  |

|               | 0 = Low priority                    |                    |           |                  |                  |                 |        |  |  |

| bit 1         | CMP2IP: CMP2 Interrupt Priority bit |                    |           |                  |                  |                 |        |  |  |

|               | 1 = High priority                   |                    |           |                  |                  |                 |        |  |  |

|               | 0 = Low priority                    |                    |           |                  |                  |                 |        |  |  |

| bit 0         | CMP1IP: CM                          | P1 Interrupt Pri   | ority bit |                  |                  |                 |        |  |  |

|               | 1 = High prio                       | rity               |           |                  |                  |                 |        |  |  |

|               | 0 = Low prior                       | •                  |           |                  |                  |                 |        |  |  |

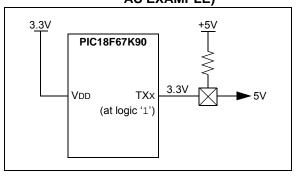

### 11.1.3 OPEN-DRAIN OUTPUTS

The output pins for several peripherals are also equipped with a configurable, open-drain output option. This allows the peripherals to communicate with external digital logic, operating at a higher voltage level, without the use of level translators.

The open-drain option is implemented on port pins specifically associated with the data and clock outputs of the USARTs, the MSSP module (in SPI mode) and the CCP modules. This option is selectively enabled by setting the open-drain control bits in the registers: ODCON1, ODCON2 and ODCON3.

When the open-drain option is required, the output pin must also be tied through an external pull-up resistor provided by the user to a higher voltage level, up to 5V (Figure 11-2). When a digital logic high signal is output, it is pulled up to the higher voltage level.

#### FIGURE 11-2: USING THE OPEN-DRAIN OUTPUT (USART SHOWN AS EXAMPLE)

### REGISTER 11-1: ODCON1: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|--------|--------|--------|-----|-----|-----|-----|--------|

| SSP10D | CCP2OD | CCP10D | _   | —   | —   | —   | SSP2OD |

| bit 7  |        |        |     |     |     |     | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | SSP10D: SPI1 Open-Drain Output Enable bit  |

|---------|--------------------------------------------|

|         | 1 = Open-drain capability is enabled       |

|         | 0 = Open-drain capability is disabled      |

| bit 6   | CCP2OD: ECCP2 Open-Drain Output Enable bit |

|         | 1 = Open-drain capability is enabled       |

|         | 0 = Open-drain capability is disabled      |

| bit 5   | CCP10D: ECCP1 Open-Drain Output Enable bit |

|         | 1 = Open-drain capability is enabled       |

|         | 0 = Open-drain capability is disabled      |

| bit 4-1 | Unimplemented: Read as '0'                 |

| bit 0   | SSP2OD: SPI2 Open-Drain Output Enable bit  |

|         | 1 = Open-drain capability is enabled       |

|         | Open drain conchility is dischlod          |

0 = Open-drain capability is disabled

# 11.7 PORTF, LATF and TRISF Registers

PORTF is a 7-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISF and LATF. All pins on PORTF are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTF is multiplexed with analog peripheral functions, as well as LCD segments. Pins, RF1 through RF6, may be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RF<7:1> as digital inputs, it is also necessary to turn off the comparators.

- **Note 1:** On device Resets, pins, RF<7:1>, are configured as analog inputs and are read as '0'.

- To configure PORTF as a digital I/O, turn off the comparators and clear ANCON1 and ANCON2 to digital.

PORTF is also multiplexed with LCD segment drives controlled by bits in the LCDSE2 and LCDSE3 registers. I/O port functions are only available when the segments are disabled.

EXAMPLE 11-6: INITIALIZING PORTF

| CLRF    | PORTF  | <pre>; Initialize PORTF by ; clearing output ; data latches</pre> |

|---------|--------|-------------------------------------------------------------------|

| CLRF    | LATF   | ; Alternate method                                                |

|         |        | ; to clear output                                                 |

|         |        | ; data latches                                                    |

| BANKSEL | ANCON1 |                                                                   |

| MOVLW   | 01Fh   | ; Make AN6, AN7 and AN5 digital                                   |

| MOVWF   | ANCON1 | ;                                                                 |

| MOVLW   | 0F0h   | ; Make AN8, AN9, AN10 and AN11                                    |

|         |        | digital                                                           |

| MOVWF   | ANCON2 | ; Set PORTF as digital I/O                                        |

| MOVLW   | 0CEh   | ; Value used to                                                   |

|         |        | ; initialize data                                                 |

|         |        | ; direction                                                       |

| MOVWF   | TRISF  | ; Set RF3:RF1 as inputs                                           |

|         |        | ; RF5:RF4 as outputs                                              |

|         |        | ; RF7:RF6 as inputs                                               |

|         |        |                                                                   |

# 20.1 LCD Registers

The LCD driver module has 32 registers:

- LCD Control Register (LCDCON)

- LCD Phase Register (LCDPS)

- LCD Reference Ladder Register (LCDRL)

- LCD Reference Voltage Control Register (LCDREF)

- Six LCD Segment Enable Registers (LCDSE5:LCDSE0)

- 24 LCD Data Registers (LCDDATA23:LCDDATA0)

The LCDCON register, shown in Register 20-1, controls the overall operation of the module. Once the module is configured, the LCDEN (LCDCON<7>) bit is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN (LCDCON<6>) bit.

The LCDPS register, shown in Register 20-2, configures the LCD clock source prescaler and the type of waveform, Type-A or Type-B. For details on these features, see Section 20.2 "LCD Clock Source Selection", Section 20.3 "LCD Bias Types" and Section 20.8 "LCD Waveform Generation".

| R/W-0 | R/W-0 | R/C-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-------|-------|-------|-------|

| LCDEN | SLPEN | WERR  | —   | CS1   | CS0   | LMUX1 | LMUX0 |

| bit 7 |       |       |     |       |       |       | bit 0 |

### REGISTER 20-1: LCDCON: LCD CONTROL REGISTER

| Legend:           | C = Clearable bit |                       |                                    |  |  |

|-------------------|-------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 7   | LCDEN: LCD Driver Enable bit<br>1 = LCD driver module is enabled<br>0 = LCD driver module is disabled                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>SLPEN:</b> LCD Driver Enable in Sleep mode bit<br>1 = LCD driver module is disabled in Sleep mode<br>0 = LCD driver module is enabled in Sleep mode |

| bit 5   | WERR: LCD Write Failed Error bit<br>1 = LCDDATAx register is written while WA (LCDPS<4>) = 0 (must be cleared in software)<br>0 = No LCD write error   |

| bit 4   | Unimplemented: Read as '0'                                                                                                                             |

| bit 3-2 | <b>CS&lt;1:0&gt;:</b> Clock Source Select bits<br>00 = (Fosc/4)/8192<br>01 = SOSC oscillator/32<br>1x = INTRC (31.25 kHz)/32                           |

| bit 1-0 | LMUX<1:0>: Commons Select bits                                                                                                                         |

| LMUX<1:0> | Multiplex Number of Pixels Nu<br>(PIC18F6X90) |     | Maximum<br>Number of Pixels<br>(PIC18F8X90) | Bias       |  |

|-----------|-----------------------------------------------|-----|---------------------------------------------|------------|--|

| 00        | Static (COM0)                                 | 33  | 48                                          | Static     |  |

| 01        | 1/2 (COM<1:0>)                                | 66  | 96                                          | 1/2 or 1/3 |  |

| 10        | 10 1/3 (COM<2:0>)                             |     | 144                                         | 1/2 or 1/3 |  |

| 11        | 1/4 (COM<3:0>)                                | 132 | 192                                         | 1/3        |  |

NOTES:

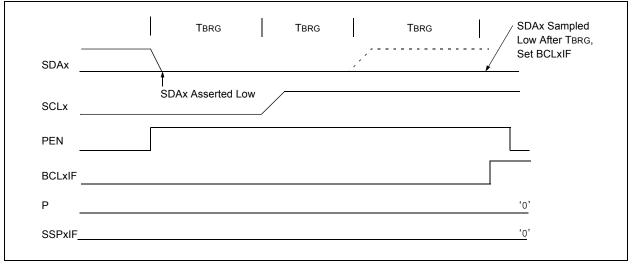

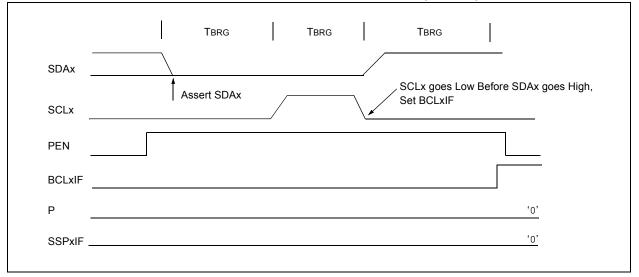

#### 21.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD<6:0> and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 21-33). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 21-34).

### FIGURE 21-33: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 21-34: BUS COLLISION DURING A STOP CONDITION (CASE 2)

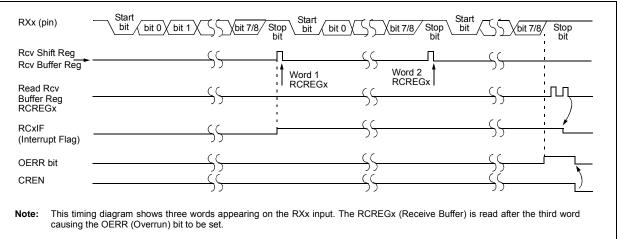

### FIGURE 22-7: ASYNCHRONOUS RECEPTION

#### TABLE 22-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name     | Bit 7    | Bit 6       | Bit 5       | Bit 4        | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------|----------|-------------|-------------|--------------|--------|---------|--------|--------|-----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE   | TMR0IF  | INT0IF | RBIF   | 75                          |

| PIR1     | —        | ADIF        | RC1IF       | TX1IF        | SSP1IF | TMR1GIF | TMR2IF | TMR1IF | 77                          |

| PIE1     | _        | ADIE        | RC1IE       | TX1IE        | SSP1IE | TMR1GIE | TMR2IE | TMR1IE | 77                          |

| IPR1     | —        | ADIP        | RC1IP       | TX1IP        | SSP1IP | TMR1GIP | TMR2IP | TMR1IP | 77                          |

| PIR3     | TMR5GIF  | LCDIF       | RC2IF       | TX2IF        | CTMUIF | CCP2IF  | CCP1IF | RTCCIF | 77                          |

| PIE3     | TMR5GIE  | LCDIE       | RC2IE       | TX2IE        | CTMUIE | CCP2IE  | CCP1IE | RTCCIE | 77                          |

| IPR3     | TMR5GIP  | LCDIP       | RC2IP       | TX2IP        | CTMUIP | CCP2IP  | CCP1IP | RTCCIP | 77                          |

| RCSTA1   | SPEN     | RX9         | SREN        | CREN         | ADDEN  | FERR    | OERR   | RX9D   | 77                          |

| RCREG1   | EUSART1  | Receive Reg | ister       |              |        |         |        |        | 77                          |

| TXSTA1   | CSRC     | TX9         | TXEN        | SYNC         | SENDB  | BRGH    | TRMT   | TX9D   | 77                          |

| BAUDCON1 | ABDOVF   | RCIDL       | RXDTP       | TXCKP        | BRG16  | _       | WUE    | ABDEN  | 79                          |

| SPBRGH1  | EUSART1  | Baud Rate G | enerator Re | egister High | n Byte |         |        |        | 76                          |

| SPBRG1   | EUSART1  | Baud Rate G | enerator Re | egister Low  | Byte   |         |        |        | 77                          |

| RCSTA2   | SPEN     | RX9         | SREN        | CREN         | ADDEN  | FERR    | OERR   | RX9D   | 81                          |

| RCREG2   | EUSART2  | Receive Reg | ister       |              |        |         |        |        | 82                          |

| TXSTA2   | CSRC     | TX9         | TXEN        | SYNC         | SENDB  | BRGH    | TRMT   | TX9D   | 81                          |

| BAUDCON2 | ABDOVF   | RCIDL       | RXDTP       | TXCKP        | BRG16  | —       | WUE    | ABDEN  | 81                          |

| SPBRGH2  | EUSART2  | Baud Rate G | enerator Re | egister High | Byte   |         |        |        | 82                          |

| SPBRG2   | EUSART2  | Baud Rate G | enerator Re | egister Low  | Byte   |         |        |        | 82                          |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

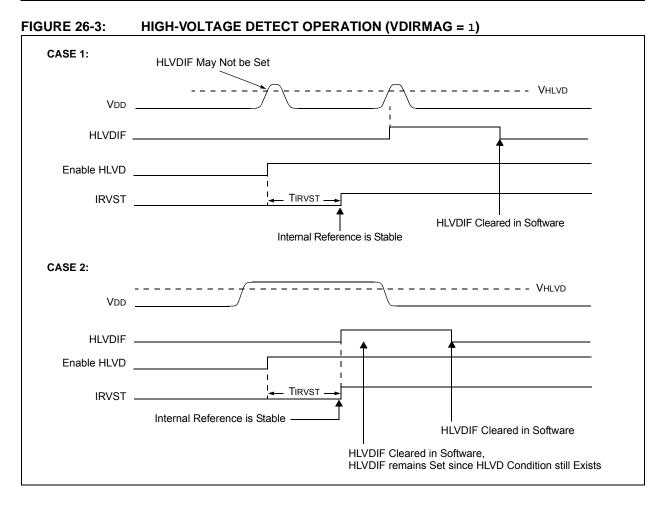

## 26.5 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a High-Voltage Detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

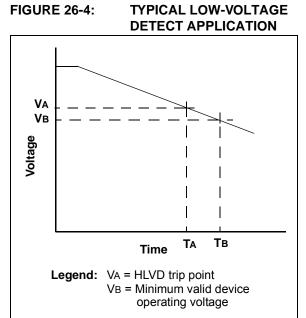

For general battery applications, Figure 26-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR (Interrupt Service Routine), which would allow the application to perform "housekeeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

# REGISTER 28-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| U-0   | R/P-1 | U-0 | R/P-1    | R/P-1    | R/P-1      | U-0 | R/P-1 |

|-------|-------|-----|----------|----------|------------|-----|-------|

| _     | XINST | —   | SOSCSEL1 | SOSCSEL0 | INTOSCSEL0 | _   | RETEN |

| bit 7 |       |     |          |          |            |     | bit 0 |

| Legend:           | P = Programmable bit |                       |                    |

|-------------------|----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | XINST: Extended Instruction Set Enable bit                                                                                                                                                                                |

|         | <ul> <li>1 = Instruction set extension and Indexed Addressing mode are enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode are disabled (Legacy mode)</li> </ul>                                   |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 4-3 | SOSCSEL<1:0>: SOSC Power Selection and Mode Configuration bits                                                                                                                                                            |

|         | <ul> <li>11 = High-power SOSC circuit is selected</li> <li>10 = Digital (SCLKI) mode: I/O port functionality of RC0 and RC1 is enabled</li> <li>01 = Low-power SOSC circuit is selected</li> <li>00 = Reserved</li> </ul> |

| bit 2   | INTOSCSEL: LF-INTOSC Low-Power Enable bit                                                                                                                                                                                 |

|         | 1 = LF-INTOSC is in High-Power mode during Sleep<br>0 = LF-INTOSC is in Low-Power mode during Sleep                                                                                                                       |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 0   | RETEN: VREG Sleep Enable bit                                                                                                                                                                                              |

|         | <ul> <li>1 = Ultra low-power regulator is disabled. Regulator power in Sleep mode is controlled by VREGSLP<br/>(WDTCON&lt;7&gt;)</li> </ul>                                                                               |

|         | 0 - Illtra low power regulator is enabled. Regulator power in Sleep mode is controlled by SPETEN                                                                                                                          |

0 = Ultra low-power regulator is enabled. Regulator power in Sleep mode is controlled by SRETEN (WDTCON<4>).

| R/P-0      | R/P-0                                                                                                                                                                     | U-0                                                                                                                                                                                                                     | U-0                                                                                                              | R/P-1                                                                                                                           | R/P-0                                                                 | R/P-0                                              | R/P-0                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|----------------------|

| IESO       | FCMEN                                                                                                                                                                     | —                                                                                                                                                                                                                       | PLLCFG <sup>(1)</sup>                                                                                            | FOSC3 <sup>(2)</sup>                                                                                                            | FOSC2 <sup>(2)</sup>                                                  | FOSC1 <sup>(2)</sup>                               | FOSC0 <sup>(2)</sup> |

| bit 7      |                                                                                                                                                                           |                                                                                                                                                                                                                         |                                                                                                                  |                                                                                                                                 |                                                                       |                                                    | bit (                |

| Legend:    |                                                                                                                                                                           | P = Program                                                                                                                                                                                                             | mable bit                                                                                                        |                                                                                                                                 |                                                                       |                                                    |                      |

| R = Reada  | ble bit                                                                                                                                                                   | W = Writable                                                                                                                                                                                                            |                                                                                                                  | U = Unimpler                                                                                                                    | nented bit, read                                                      | d as '0'                                           |                      |

| -n = Value | at POR                                                                                                                                                                    | '1' = Bit is se                                                                                                                                                                                                         | t                                                                                                                | '0' = Bit is cle                                                                                                                | = Bit is cleared x = Bit is unknown                                   |                                                    |                      |

| bit 7      | IESO: Interna                                                                                                                                                             | al/External Osc                                                                                                                                                                                                         | cillator Switchov                                                                                                | ver bit                                                                                                                         |                                                                       |                                                    |                      |

|            |                                                                                                                                                                           | ed Start-up is e<br>ed Start-up is c                                                                                                                                                                                    |                                                                                                                  |                                                                                                                                 |                                                                       |                                                    |                      |

| bit 6      | 1 = Fail-Safe                                                                                                                                                             | -Safe Clock M<br>Clock Monitor<br>Clock Monitor                                                                                                                                                                         |                                                                                                                  | it                                                                                                                              |                                                                       |                                                    |                      |

| bit 5      | Unimplemen                                                                                                                                                                | ted: Read as                                                                                                                                                                                                            | ʻ0'                                                                                                              |                                                                                                                                 |                                                                       |                                                    |                      |

| bit 4      | PLLCFG: 4x                                                                                                                                                                | PLL Enable bi                                                                                                                                                                                                           | t(1)                                                                                                             |                                                                                                                                 |                                                                       |                                                    |                      |

|            |                                                                                                                                                                           | is multiplied b                                                                                                                                                                                                         | •                                                                                                                |                                                                                                                                 |                                                                       |                                                    |                      |

| bit 3-0    | FOSC<3:0>:                                                                                                                                                                | Oscillator Sele                                                                                                                                                                                                         | ection bits <sup>(2)</sup>                                                                                       |                                                                                                                                 |                                                                       |                                                    |                      |

|            | 1100 = EC1<br>1011 = EC2<br>1010 = EC2<br>0101 = EC3<br>0100 = EC3<br>0011 = HS1<br>0010 = HS2<br>0001 = XT o<br>0000 = LP o<br>0111 = RC,<br>0110 = RCI0<br>1000 = INTIO | IO, EC oscillat<br>, EC oscillator<br>IO, EC oscillator<br>IO, EC oscillator<br>IO, EC oscillator<br>, HS oscillator<br>, HS oscillator<br>scillator<br>scillator<br>External RC o<br>O, External RC<br>O2, Internal RC | (medium powe<br>or with CLKOU<br>(high power, 4<br>or with CLKOU<br>(medium powe<br>(high power, 10<br>scillator | T function on<br>r, 160 kHz-16<br>T function on<br>MHz-64 MHz)<br>T function on<br>r, 4 MHz-16 M<br>6 MHz-25 MHz<br>CKLOUT func | MHz)<br>RA6 (medium p<br>RA6 (high powe<br>IHz)<br>z)<br>stion on RA6 | r, DC-160 kHz)<br>bower,160 kHz-<br>er, 4 MHz-64 M | 16MHz)               |

|            | Not valid for the IN                                                                                                                                                      |                                                                                                                                                                                                                         |                                                                                                                  |                                                                                                                                 |                                                                       |                                                    |                      |

| 2:         | INTIO+PLL can or                                                                                                                                                          | niv be enabled                                                                                                                                                                                                          | by the PLLEN                                                                                                     | bit (OSCTUNE                                                                                                                    | =<6>). Other Pl                                                       | L modes can b                                      | e enabled b          |

# REGISTER 28-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

2: INTIO+PLL can only be enabled by the PLLEN bit (OSCTUNE<6>). Other PLL modes can be enabled by either the PLLEN bit or the PLLCFG (CONFIG1H<4>) bit.

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <u>15 10 9 8 7 0</u>                                                                                                                                                                                                                                  |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| 15 12 11 9 8 7 0                                                                                                                                                                                                                                      |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

|                                                                                                                                                                                                                                                       |                      |

| CALL, GOTO and Branch operations<br>15 8 7 0                                                                                                                                                                                                          |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | BRA MYFUNC           |

|                                                                                                                                                                                                                                                       |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | BC MYFUNC            |

| RET          | URN             | Return from                                                                              | m Subro                                                                                                                                                                                                                                                                                                                      | utine |                      |  |

|--------------|-----------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|--|

| Synta        | ax:             | RETURN                                                                                   | {s}                                                                                                                                                                                                                                                                                                                          |       |                      |  |

| Oper         | ands:           | $s \in [0,1]$                                                                            |                                                                                                                                                                                                                                                                                                                              |       |                      |  |

| Oper         | ation:          | if s = 1,<br>(WS) $\rightarrow$ W,<br>(STATUSS)<br>(BSRS) $\rightarrow$                  | $(TOS) \rightarrow PC;$<br>if s = 1,<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged                                                                                                                                                                |       |                      |  |

| Statu        | s Affected:     | None                                                                                     |                                                                                                                                                                                                                                                                                                                              |       |                      |  |

| Enco         | ding:           | 0000                                                                                     | 0000                                                                                                                                                                                                                                                                                                                         | 0001  | 001s                 |  |

| Description: |                 | popped and<br>is loaded in<br>'s'= 1, the c<br>registers W<br>loaded into<br>registers W | Return from subroutine. The stack is<br>popped and the top of the stack (TOS)<br>is loaded into the Program Counter. If<br>'s'= 1, the contents of the shadow<br>registers WS, STATUSS and BSRS are<br>loaded into their corresponding<br>registers W, STATUS and BSR. If<br>'s' = 0, no update of these registers<br>occurs |       |                      |  |

| Word         | ls:             | 1                                                                                        |                                                                                                                                                                                                                                                                                                                              |       |                      |  |

| Cycle        | es:             | 2                                                                                        |                                                                                                                                                                                                                                                                                                                              |       |                      |  |

| QC           | ycle Activity:  |                                                                                          |                                                                                                                                                                                                                                                                                                                              |       |                      |  |

|              | Q1              | Q2                                                                                       | Q3                                                                                                                                                                                                                                                                                                                           | 3     | Q4                   |  |

|              | Decode          | No<br>operation                                                                          | Proce<br>Data                                                                                                                                                                                                                                                                                                                |       | POP PC<br>from stack |  |

|              | No<br>operation | No<br>operation                                                                          | No<br>operat                                                                                                                                                                                                                                                                                                                 |       | No<br>operation      |  |

| <u>Exan</u>  | nple:           | RETURN                                                                                   |                                                                                                                                                                                                                                                                                                                              |       |                      |  |

After Instruction: PC = TOS

| RLCF                                                                             | Rotate Left                                                                                                                                                                                | fthroug                                                            | gh Carry                                                                 |                                                |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|

| Syntax:                                                                          | RLCF f {                                                                                                                                                                                   | {,d {,a}}                                                          |                                                                          |                                                |

| Operands:                                                                        | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                             |                                                                    |                                                                          |                                                |

| Operation:                                                                       | $(f < n >) \rightarrow de$<br>$(f < 7 >) \rightarrow C$<br>$(C) \rightarrow dest$                                                                                                          | ,                                                                  | >,                                                                       |                                                |

| Status Affected:                                                                 | C, N, Z                                                                                                                                                                                    |                                                                    |                                                                          |                                                |

| Encoding:                                                                        | 0011                                                                                                                                                                                       | 01da                                                               | ffff                                                                     | ffff                                           |

| Description:                                                                     | The conten<br>one bit to th<br>If 'd' is '0', t<br>is '1', the re<br>'f'.                                                                                                                  | ne left thre<br>he result                                          | ough the<br>is placed                                                    | Carry flag.<br>in W. If 'd'                    |

|                                                                                  | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.                                                                                                                                          |                                                                    |                                                                          |                                                |

|                                                                                  | If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 29<br>Bit-Oriente<br>Literal Offs                                                                                  | ed, this in<br>Literal Of<br>never f ≤ 9<br>.2.3 "Byt<br>ed Instru | nstruction<br>fset Addre<br>95 (5Fh).<br>a <b>e-Oriente</b><br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |

|                                                                                  | C                                                                                                                                                                                          | ] <b>∢</b> r                                                       | egister f                                                                |                                                |

| Words:                                                                           | 1                                                                                                                                                                                          |                                                                    |                                                                          |                                                |

| Cycles:                                                                          | 1                                                                                                                                                                                          |                                                                    |                                                                          |                                                |

| Q Cycle Activity:                                                                |                                                                                                                                                                                            |                                                                    |                                                                          |                                                |

|                                                                                  |                                                                                                                                                                                            |                                                                    |                                                                          |                                                |

| Q1                                                                               | Q2                                                                                                                                                                                         | Q                                                                  | 3                                                                        | Q4                                             |

| Q1<br>Decode                                                                     | Q2<br>Read<br>register 'f'                                                                                                                                                                 | Q:<br>Proce<br>Dat                                                 | ess                                                                      | Q4<br>Write to<br>estination                   |

|                                                                                  | Read                                                                                                                                                                                       | Proce<br>Dat                                                       | ess                                                                      | Write to                                       |

| Decode                                                                           | Read<br>register 'f'                                                                                                                                                                       | Proce<br>Dat                                                       | ess de                                                                   | Write to                                       |

| Decode                                                                           | Read<br>register 'f'                                                                                                                                                                       | Proce<br>Dat                                                       | ess de                                                                   | Write to                                       |

| Decode<br>Example:<br>Before Instruct<br>REG<br>C<br>After Instructio            | Read           register 'f'           RLCF           ction           =         1110           =         0                                                                                  | Proce<br>Dat                                                       | ess de                                                                   | Write to                                       |

| Decode<br>Example:<br>Before Instruct<br>REG<br>C<br>After Instructio<br>REG     | Read<br>register 'f'<br>RLCF<br>ction<br>= 1110<br>= 0<br>on<br>= 1110                                                                                                                     | Proce<br>Dat<br>REC<br>0110                                        | ess de                                                                   | Write to                                       |