Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Active                                                        |

| Core Processor             | HC08                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | SCI, SPI                                                      |

| Peripherals                | LVD, POR, PWM                                                 |

| Number of I/O              | 33                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 512 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                   |

| Data Converters            | A/D 8x8b                                                      |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 44-QFP                                                        |

| Supplier Device Package    | 44-QFP (10x10)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908gp16cfb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

## http://motorola.com/semiconductors

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History**

| Date         | Revision<br>Level | Description                                                                                            | Page<br>Number(s) |  |  |

|--------------|-------------------|--------------------------------------------------------------------------------------------------------|-------------------|--|--|

| August, 2002 | 6                 | Section 22. Timer Interface Module (TIM) — Timer discrepancies corrected throughout this section.      |                   |  |  |

|              | 0                 | Section 24. Mechanical Specifications — Replaced incorrect 44-pin QFP drawing, case 824E to case 824A. |                   |  |  |

|              | 5                 | In <b>Table 15-1</b> , second cell in "Comment" column, corrected PTC to PTC1.                         | 199               |  |  |

| July, 2001   |                   | In Figure 21-2, Timebase control register, bit 0 is a reserved bit.                                    | 337               |  |  |

| July, 2001   |                   | Updated crystal oscillator component values in 23.17.1 CGM Component Specifications.                   | 387               |  |  |

|              |                   | Added appendix A: MC68HC08GP32 — ROM part.                                                             | 397               |  |  |

# **Table of Contents**

# **Section 1. General Description**

| 1.1                   | Contents                                                                         | 31 |

|-----------------------|----------------------------------------------------------------------------------|----|

| 1.2                   | Introduction                                                                     | 32 |

| 1.3<br>1.3.1<br>1.3.2 | Features                                                                         | 32 |

| 1.4                   | MCU Block Diagram                                                                | 35 |

| 1.5                   | Pin Assignments                                                                  | 37 |

| 1.6                   | Pin Functions                                                                    | 39 |

| 1.6.1                 | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )                         | 39 |

| 1.6.2                 | Oscillator Pins (OSC1 and OSC2)                                                  | 40 |

| 1.6.3                 | External Reset Pin (RST)                                                         |    |

| 1.6.4                 | External Interrupt Pin (IRQ)                                                     | 40 |

| 1.6.5                 | CGM Power Supply Pins (V <sub>DDA</sub> and V <sub>SSA</sub> )                   | 41 |

| 1.6.6                 | External Filter Capacitor Pin (CGMXFC)                                           | 41 |

| 1.6.7                 | ADC Power Supply/Reference Pins                                                  |    |

|                       | (V <sub>DDAD</sub> /V <sub>REFH</sub> and V <sub>SSAD</sub> /V <sub>REFL</sub> ) | 41 |

| 1.6.8                 | Port A Input/Output (I/O) Pins (PTA7/KBD7-PTA0/KBD0) .                           | 41 |

| 1.6.9                 | Port B I/O Pins (PTB7/AD7–PTB0/AD0)                                              |    |

| 1.6.10                |                                                                                  |    |

| 1.6.11                | Port D I/O Pins (PTD7/T2CH1-PTD0/SS)                                             | 42 |

| 1.6.12                | Port E I/O Pins (PTE1/RxD–PTE0/TxD)                                              | 42 |

MC68HC908GP32•MC68HC08GP32 — Rev. 6

**Technical Data**

| Pins not available on 42-pin package | Internal connection |

|--------------------------------------|---------------------|

| PTC5                                 | Connected to ground |

| PTC6                                 | Connected to ground |

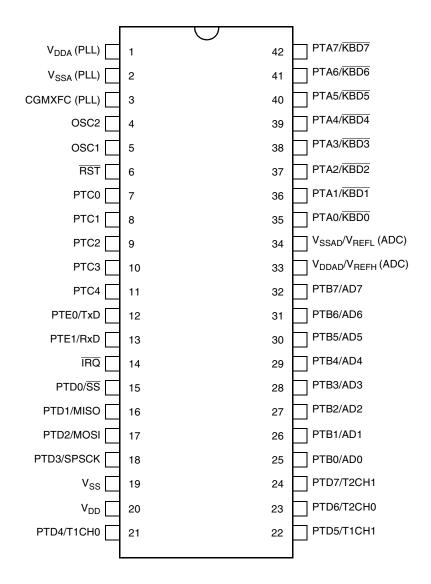

Figure 1-3. 42-Pin SDIP Pin Assignments

# 3.12 Serial Peripheral Interface Module (SPI)

#### 3.12.1 Wait Mode

The SPI module remains active in wait mode. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

### 3.12.2 Stop Mode

The SPI module is inactive in stop mode. The STOP instruction does not affect SPI register states. SPI operation resumes after an external interrupt. If stop mode is exited by reset, any transfer in progress is aborted, and the SPI is reset.

# 3.13 Timer Interface Module (TIM1 and TIM2)

#### 3.13.1 Wait Mode

The TIM remains active in wait mode. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

# 3.13.2 Stop Mode

The TIM is inactive in stop mode. The STOP instruction does not affect register states or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

**Table 5-2. ADC Clock Divide Ratio**

| ADIV2 | ADIV1 | ADIV0 | ADC Clock Rate       |

|-------|-------|-------|----------------------|

| 0     | 0     | 0     | ADC input clock ÷ 1  |

| 0     | 0     | 1     | ADC input clock ÷ 2  |

| 0     | 1     | 0     | ADC input clock ÷ 4  |

| 0     | 1     | 1     | ADC input clock ÷ 8  |

| 1     | Х     | Х     | ADC input clock ÷ 16 |

X = don't care

### ADICLK — ADC Input Clock Select Bit

ADICLK selects either the bus clock or CGMXCLK as the input clock source to generate the internal ADC clock. Reset selects CGMXCLK as the ADC clock source.

If the external clock (CGMXCLK) is equal to or greater than 1 MHz, CGMXCLK can be used as the clock source for the ADC. If CGMXCLK is less than 1 MHz, use the PLL-generated bus clock as the clock source. As long as the internal ADC clock is at approximately 1 MHz, correct operation can be guaranteed.

1 = Internal bus clock

0 = External clock (CGMXCLK)

$$\frac{ADC \text{ input clock frequency}}{ADIV2-ADIV0} = 1MHz$$

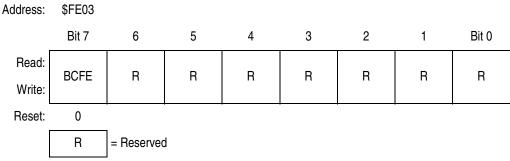

### 6.6.4 Break Flag Control Register

The SIM break flag control register (SBFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 6-7. SIM Break Flag Control Register (SBFCR)

### BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

# **Clock Generator Module (CGMC)**

The following conditions apply when the PLL is in automatic bandwidth control mode:

- The ACQ bit (See 7.6.2 PLL Bandwidth Control Register.) is a read-only indicator of the mode of the filter. (See 7.4.4 Acquisition and Tracking Modes.)

- The ACQ bit is set when the VCO frequency is within a certain tolerance and is cleared when the VCO frequency is out of a certain tolerance. (See 7.9 Acquisition/Lock Time Specifications for more information.)

- The LOCK bit is a read-only indicator of the locked state of the PLL.

- The LOCK bit is set when the VCO frequency is within a certain tolerance and is cleared when the VCO frequency is out of a certain tolerance. (See 7.9 Acquisition/Lock Time Specifications for more information.)

- CPU interrupts can occur if enabled (PLLIE = 1) when the PLL's lock condition changes, toggling the LOCK bit. (See 7.6.1 PLL Control Register.)

The PLL also may operate in manual mode (AUTO = 0). Manual mode is used by systems that do not require an indicator of the lock condition for proper operation. Such systems typically operate well below  $f_{\text{BUSMAX}}$ .

## **Clock Generator Module (CGMC)**

P, the power of two multiplier, and N, the range multiplier, are integers.

In cases where desired bus frequency has some tolerance, choose  $f_{RCLK}$  to a value determined either by other module requirements (such as modules which are clocked by CGMXCLK), cost requirements, or ideally, as high as the specified range allows. See **Section 23**. **Electrical Specifications**. Choose the reference divider, R = 1. After choosing N and P, the actual bus frequency can be determined using equation in 2 above.

When the tolerance on the bus frequency is tight, choose  $f_{RCLK}$  to an integer divisor of  $f_{BUSDES}$ , and R=1. If  $f_{RCLK}$  cannot meet this requirement, use the following equation to solve for R with practical choices of  $f_{RCLK}$ , and choose the  $f_{RCLK}$  that gives the lowest R.

$$R = round \left[ R_{MAX} \times \left\{ \left( \frac{f_{VCLKDES}}{f_{RCLK}} \right) - integer \left( \frac{f_{VCLKDES}}{f_{RCLK}} \right) \right\} \right]$$

4. Select a VCO frequency multiplier, N.

$$N = round \left( \frac{R \times f_{VCLKDES}}{f_{RCLK}} \right)$$

Reduce N/R to the lowest possible R.

5. If N is  $< N_{max}$ , use P = 0. If N  $> N_{max}$ , choose P using this table:

| Current N Value                                           | Р |

|-----------------------------------------------------------|---|

| 0 < N ≤ N <sub>max</sub>                                  | 0 |

| $N_{max} < N \le N_{max} \times 2$                        | 1 |

| $N_{\text{max}} \times 2 < N \le N_{\text{max}} \times 4$ | 2 |

| $N_{\text{max}} \times 4 < N \le N_{\text{max}} \times 8$ | 3 |

Then recalculate N:

$$N = round \left( \frac{R \times f_{VCLKDES}}{f_{RCLK} \times 2^{P}} \right)$$

The COP counter is a free-running 6-bit counter preceded by a 12-bit prescaler counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after  $2^{18} - 2^4$  or  $2^{13} - 2^4$  CGMXCLK cycles, depending on the state of the COP rate select bit, COPRS, in the configuration register. With a  $2^{13} - 2^4$  CGMXCLK cycle overflow option, a 32.768-kHz crystal gives a COP timeout period of 250 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12 through 5 of the prescaler.

#### NOTE:

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the  $\overline{RST}$  pin low for 32 CGMXCLK cycles and sets the COP bit in the reset status register (RSR).

In monitor mode, the COP is disabled if the  $\overline{RST}$  pin or the  $\overline{IRQ}$  is held at  $V_{TST}$ . During the break state,  $V_{TST}$  on the  $\overline{RST}$  pin disables the COP.

#### NOTE:

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

# 9.4 I/O Signals

The following paragraphs describe the signals shown in Figure 9-1.

#### 9.4.1 CGMXCLK

CGMXCLK is the crystal oscillator output signal. CGMXCLK frequency is equal to the crystal frequency.

### 9.4.2 STOP Instruction

The STOP instruction clears the COP prescaler.

MC68HC908GP32•MC68HC08GP32 — Rev. 6

**Technical Data**

#### 15.3 Features

Features of the monitor ROM include:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between monitor ROM and host computer

- Standard mark/space non-return-to-zero (NRZ) communication with host computer

- Execution of code in RAM or FLASH

- FLASH memory security feature<sup>1</sup>

- FLASH memory programming interface

- Enhanced PLL (phase-locked loop) option to allow use of external 32.768-kHz crystal to generate internal frequency of 2.4576 MHz

- 307 bytes monitor ROM code size (\$FE20 to \$FF52)

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage, V<sub>TST</sub>, is applied to IRQ

# 15.4 Functional Description

The monitor ROM receives and executes commands from a host computer. Figure 15-1 shows an example circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTAO pin. A level-shifting and multiplexing interface is required

**Technical Data**

MC68HC908GP32•MC68HC08GP32 - Rev. 6

<sup>1.</sup> No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the FLASH difficult for unauthorized users.

MC68HC908GP32•MC68HC08GP32 — Rev. 6

Technical Data

**Table 15-1. Monitor Mode Signal Requirements and Options**

| 100                          | D=0==                                     | \$FFFE/                          |     |      |      |      | External             |               | ССМОИТ        | Bus      |      | For Serial<br>Communication |                                      |                                                                  | 0                   |

|------------------------------|-------------------------------------------|----------------------------------|-----|------|------|------|----------------------|---------------|---------------|----------|------|-----------------------------|--------------------------------------|------------------------------------------------------------------|---------------------|

| ĪRQ                          | RESET                                     | \$FFFE/<br>\$FFFF                | PLL | PTC0 | PTC1 | PTC3 | Clock <sup>(1)</sup> | CGMOUT        | Frequency     | СОР      | PTA0 | PTA7                        | Baud<br>Rate <sup>(2) (3)</sup>      | Comment                                                          |                     |

| Х                            | GND                                       | Х                                | Х   | Х    | Х    | Х    | Х                    | 0             | 0             | Disabled | Х    | Х                           | 0                                    | No operation until reset goes high                               |                     |

| V <sub>TST</sub>             | V <sub>DD</sub><br>or                     | Х                                | OFF | 1    | 0    | 0    | 4.9152<br>MHz        | 4.9152<br>MHz | 2.4576<br>MHz | Disabled | 1    | 0                           | 9600                                 | PTC0 and PTC1 voltages only required                             |                     |

|                              | V <sub>TST</sub>                          |                                  |     |      |      |      |                      |               |               |          | Х    | 1                           | DNA                                  | if IRQ = V <sub>TST</sub> ; PTC3 determines frequency divider    |                     |

| V <sub>TST</sub>             | V <sub>DD</sub><br>or                     | Х                                | OFF | 1    | 0    | 1    | 9.8304<br>MHz        | 4.9152<br>MHz | 2.4576<br>MHz | Disabled | 1    | voltages only req           | PTC0 and PTC1 voltages only required |                                                                  |                     |

|                              | V <sub>TST</sub>                          |                                  |     |      |      |      |                      |               |               |          | Х    | 1                           | DNA                                  | if IRQ = V <sub>TST</sub> ; PTC3 determines frequency divider    |                     |

| V <sub>DD</sub>              | V <sub>DD</sub>                           | D \$FF OF (blank)                | OFF | Х    | Х    | Х    | 9.8304               | 4.9152        |               | Disabled | 1    | 0                           | 9600                                 | External frequency                                               |                     |

|                              |                                           |                                  |     |      |      |      | MHz                  | MHz MHz       | IVIHZ         | MHz      |      | Х                           | 1                                    | DNA                                                              | always divided by 4 |

| GND                          | V <sub>DD</sub>                           | \$FF ON                          | ON  | х    | Х    | Х    | X 32.768 kHz         | 4.9152        |               | Disabled | 1    | 0                           | 9600                                 | PLL enabled                                                      |                     |

|                              |                                           | (blank)                          |     |      |      |      | KHZ                  | MHz           | MHz           |          | Х    | 1                           | DNA                                  | (BCS set)<br>in monitor code                                     |                     |

| V <sub>DD</sub><br>or<br>GND | V <sub>TST</sub>                          | \$FF<br>(blank)                  | OFF | Х    | Х    | Х    | х                    | _             | _             | Enabled  | Х    | Х                           | _                                    | Enters user mode —<br>will encounter an<br>illegal address reset |                     |

| V <sub>DD</sub><br>or<br>GND | V <sub>DD</sub><br>or<br>V <sub>TST</sub> | Not<br>\$FF<br>(progra-<br>mmed) | OFF | Х    | Х    | Х    | Х                    | _             | _             | Enabled  | Х    | Х                           | _                                    | Enters user mode                                                 |                     |

#### Notes:

- 1. External clock is derived by a 32.768 kHz crystal or a 4.9152/9.8304 MHz off-chip oscillator 2. PTA0 = 1 if serial communication; PTA0 = X if parallel communication 3. PTA7 = 0  $\rightarrow$  serial, PTA7 = 1  $\rightarrow$  parallel communication for security code entry 4. DNA = does not apply, X = don't care

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

**Description** Reads stack pointer Operand None Returns incremented stack pointer value (SP + 1) in high-byte:low-Data Returned byte order Opcode \$0C **Command Sequence** FROM HOST READSP READSP **ECHO** RETURN

Table 15-8. READSP (Read Stack Pointer) Command

Table 15-9. RUN (Run User Program) Command

| Description      | Executes PULH and RTI instructions |  |  |  |  |  |

|------------------|------------------------------------|--|--|--|--|--|

| Operand          | None                               |  |  |  |  |  |

| Data<br>Returned | None                               |  |  |  |  |  |

| Opcode           | \$28                               |  |  |  |  |  |

|                  | Command Sequence                   |  |  |  |  |  |

|                  | FROM HOST    V RUN                 |  |  |  |  |  |

**Table 16-1. Port Control Register Bits Summary**

| Port     | Bit | DDR   | Modu     | ile Control | Pin        |

|----------|-----|-------|----------|-------------|------------|

|          | 0   | DDRA0 |          | KBIE0       | PTA0/KBD0  |

|          | 1   | DDRA1 | _        | KBIE1       | PTA1/KBD1  |

|          | 2   | DDRA2 |          | KBIE2       | PTA2/KBD2  |

| Α        | 3   | DDRA3 | KBD      | KBIE3       | PTA3/KBD3  |

| _ A      | 4   | DDRA4 | KDD      | KBIE4       | PTA4/KBD4  |

|          | 5   | DDRA5 |          | KBIE5       | PTA5/KBD5  |

|          | 6   | DDRA6 |          | KBIE6       | PTA6/KBD6  |

|          | 7   | DDRA7 |          | KBIE7       | PTA7/KBD7  |

|          | 0   | DDRB0 |          |             | PTB0/AD0   |

|          | 1   | DDRB1 |          |             | PTB1/AD1   |

|          | 2   | DDRB2 |          |             | PTB2/AD2   |

| В        | 3   | DDRB3 | ADC      | ADCH4-ADCH0 | PTB3/AD3   |

| В        | 4   | DDRB4 | ADC      | ADCH4-ADCH0 | PTB4/AD4   |

|          | 5   | DDRB5 |          |             | PTB5/AD5   |

|          | 6   | DDRB6 |          |             | PTB6/AD6   |

|          | 7   | DDRB7 |          |             | PTB7/AD7   |

|          | 0   | DDRC0 |          |             | PTC0       |

|          | 1   | DDRC1 |          |             | PTC1       |

|          | 2   | DDRC2 |          |             | PTC2       |

| С        | 3   | DDRC3 |          |             | PTC3       |

|          | 4   | DDRC4 |          |             | PTC4       |

|          | 5   | DDRC5 |          |             | PTC5       |

|          | 6   | DDRC6 |          |             | PTC6       |

|          | 0   | DDRD0 |          |             | PTD0/SS    |

|          | 1   | DDRD1 | SPI      | SPE         | PTD1/MISO  |

|          | 2   | DDRD2 | 51 1     |             | PTD2/MOSI  |

| D        | 3   | DDRD3 |          |             | PTD3/SPSCK |

|          | 4   | DDRD4 | TIM1     | ELS0B:ELS0A | PTD4/T1CH0 |

|          | 5   | DDRD5 | I IIVI I | ELS1B:ELS1A | PTD5/T1CH1 |

|          | 6   | DDRD6 | TIM2     | ELS0B:ELS0A | PTD6/T2CH0 |

|          | 7   | DDRD7 | I IIVIZ  | ELS1B:ELS1A | PTD7/T2CH1 |

| Е        | 0   | DDRE0 | SCI      | ENSCI       | PTE0/TxD   |

| <u>_</u> | 1   | DDRE1 | JOI      | LINGOI      | PTE1/RxD   |

**Technical Data**

MC68HC908GP32•MC68HC08GP32 — Rev. 6

**MOTOROLA**

## **Serial Communications Interface Module (SCI)**

### 18.5.3 Receiver

Figure 18-5 shows the structure of the SCI receiver.

### 18.5.3.1 Character Length

The receiver can accommodate either 8-bit or 9-bit data. The state of the M bit in SCI control register 1 (SCC1) determines character length. When receiving 9-bit data, bit R8 in SCI control register 2 (SCC2) is the ninth bit (bit 8). When receiving 8-bit data, bit R8 is a copy of the eighth bit (bit 7).

### 18.5.3.2 Character Reception

During an SCI reception, the receive shift register shifts characters in from the PTE1/RxD pin. The SCI data register (SCDR) is the read-only buffer between the internal data bus and the receive shift register.

After a complete character shifts into the receive shift register, the data portion of the character transfers to the SCDR. The SCI receiver full bit, SCRF, in SCI status register 1 (SCS1) becomes set, indicating that the received byte can be read. If the SCI receive interrupt enable bit, SCRIE, in SCC2 is also set, the SCRF bit generates a receiver CPU interrupt request.

## **Serial Communications Interface Module (SCI)**

#### R8 — Received Bit 8

When the SCI is receiving 9-bit characters, R8 is the read-only ninth bit (bit 8) of the received character. R8 is received at the same time that the SCDR receives the other 8 bits.

When the SCI is receiving 8-bit characters, R8 is a copy of the eighth bit (bit 7). Reset has no effect on the R8 bit.

### T8 — Transmitted Bit 8

When the SCI is transmitting 9-bit characters, T8 is the read/write ninth bit (bit 8) of the transmitted character. T8 is loaded into the transmit shift register at the same time that the SCDR is loaded into the transmit shift register. Reset has no effect on the T8 bit.

DMARE — DMA Receive Enable Bit

#### **CAUTION:**

The DMA module is not included on this MCU. Writing a logic 1 to DMARE or DMATE may adversely affect MCU performance.

- 1 = DMA not enabled to service SCI receiver DMA service requests generated by the SCRF bit (SCI receiver CPU interrupt requests enabled)

- 0 = DMA not enabled to service SCI receiver DMA service requests generated by the SCRF bit (SCI receiver CPU interrupt requests enabled)

DMATE — DMA Transfer Enable Bit

#### **CAUTION:**

The DMA module is not included on this MCU. Writing a logic 1 to DMARE or DMATE may adversely affect MCU performance.

- 1 = SCTE DMA service requests enabled; SCTE CPU interrupt requests disabled

- 0 = SCTE DMA service requests disabled; SCTE CPU interrupt requests enabled

266

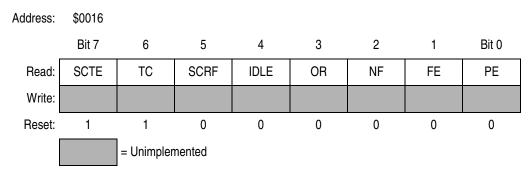

### 18.9.4 SCI Status Register 1

SCI status register 1 (SCS1) contains flags to signal these conditions:

- Transfer of SCDR data to transmit shift register complete

- Transmission complete

- Transfer of receive shift register data to SCDR complete

- Receiver input idle

- Receiver overrun

- Noisy data

- Framing error

- Parity error

Figure 18-12. SCI Status Register 1 (SCS1)

### SCTE — SCI Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an SCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an SCI transmitter CPU interrupt request. In normal operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

When CPHA = 1 for a slave, the first edge of the SPSCK indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the transmit data register. Therefore, the SPI data register of the slave must be loaded with transmit data before the first edge of SPSCK. Any data written after the first edge is stored in the transmit data register and transferred to the shift register after the current transmission.

### 20.6.4 Transmission Initiation Latency

When the SPI is configured as a master (SPMSTR = 1), writing to the SPDR starts a transmission. CPHA has no effect on the delay to the start of the transmission, but it does affect the initial state of the SPSCK signal. When CPHA = 0, the SPSCK signal remains inactive for the first half of the first SPSCK cycle. When CPHA = 1, the first SPSCK cycle begins with an edge on the SPSCK line from its inactive to its active level. The SPI clock rate (selected by SPR1:SPR0) affects the delay from the write to SPDR and the start of the SPI transmission. (See Figure 20-7.) The internal SPI clock in the master is a free-running derivative of the internal MCU clock. To conserve power, it is enabled only when both the SPE and SPMSTR bits are set. SPSCK edges occur halfway through the low time of the internal MCU clock. Since the SPI clock is free-running, it is uncertain where the write to the SPDR occurs relative to the slower SPSCK. This uncertainty causes the variation in the initiation delay shown in Figure 20-7. This delay is no longer than a single SPI bit time. That is, the maximum delay is two MCU bus cycles for DIV2, eight MCU bus cycles for DIV8, 32 MCU bus cycles for DIV32, and 128 MCU bus cycles for DIV128.

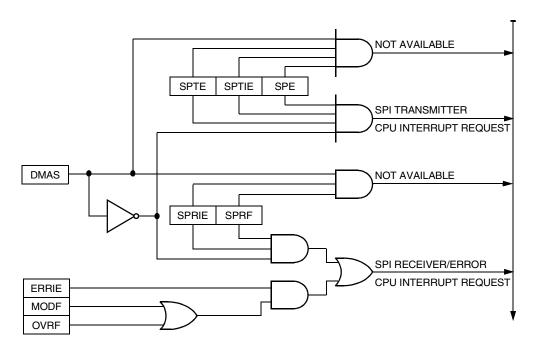

Reading the SPI status and control register with SPRF set and then reading the receive data register clears SPRF. The clearing mechanism for the SPTE flag is always just a write to the transmit data register.

The SPI transmitter interrupt enable bit (SPTIE) enables the SPTE flag to generate transmitter CPU interrupt requests, provided that the SPI is enabled (SPE = 1).

The SPI receiver interrupt enable bit (SPRIE) enables the SPRF bit to generate receiver CPU interrupt requests, regardless of the state of the SPE bit. (See Figure 20-11.)

The error interrupt enable bit (ERRIE) enables both the MODF and OVRF bits to generate a receiver/error CPU interrupt request.

The mode fault enable bit (MODFEN) can prevent the MODF flag from being set so that only the OVRF bit is enabled by the ERRIE bit to generate receiver/error CPU interrupt requests.

Figure 20-11. SPI Interrupt Request Generation

# Serial Peripheral Interface Module (SPI)

### SPTE — SPI Transmitter Empty Bit

This clearable, read-only flag is set each time the transmit data register transfers a byte into the shift register. SPTE generates an SPTE CPU interrupt request or an SPTE DMA service request if the SPTIE bit in the SPI control register is set also.

**NOTE:** Do not write to the SPI data register unless the SPTE bit is high.

During an SPTE CPU interrupt, the CPU clears the SPTE bit by writing to the transmit data register.

Reset sets the SPTE bit.

- 1 = Transmit data register empty

- 0 = Transmit data register not empty

#### MODFEN — Mode Fault Enable Bit

This read/write bit, when set to 1, allows the MODF flag to be set. If the MODF flag is set, clearing the MODFEN does not clear the MODF flag. If the SPI is enabled as a master and the MODFEN bit is low, then the  $\overline{SS}$  pin is available as a general-purpose I/O.

If the MODFEN bit is set, then this pin is not available as a general-purpose I/O. When the SPI is enabled as a slave, the  $\overline{SS}$  pin is not available as a general-purpose I/O regardless of the value of MODFEN. (See 20.13.4 SS (Slave Select).)

If the MODFEN bit is low, the level of the  $\overline{SS}$  pin does not affect the operation of an enabled SPI configured as a master. For an enabled SPI configured as a slave, having MODFEN low only prevents the MODF flag from being set. It does not affect any other part of SPI operation. (See 20.8.2 Mode Fault Error.)

#### SPR1 and SPR0 — SPI Baud Rate Select Bits

In master mode, these read/write bits select one of four baud rates as shown in **Table 20-4**. SPR1 and SPR0 have no effect in slave mode. Reset clears SPR1 and SPR0.

# Section 25. Ordering Information

### 25.1 Contents

| 25.2 | Introduction     | 395 |

|------|------------------|-----|

| )E 0 | MC Order Numbers | 205 |

# 25.2 Introduction

This section contains ordering numbers for the MC68HC908GP32.

### 25.3 MC Order Numbers

**Table 25-1. MC Order Numbers**

| MC order number  | Operating temperature range | Package     |

|------------------|-----------------------------|-------------|

| MC68HC908GP32CP  | −40 °C to +85 °C            | 40-pin PDIP |

| MC68HC908GP32CB  | −40 °C to +85 °C            | 42-pin SDIP |

| MC68HC908GP32CFB | −40 °C to +85 °C            | 44-pin QFP  |