Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 36MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                             |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 10K × 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101r8t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Figures

| Figure 1.  | STM32F101xx medium-density access line block diagram                                         | 12 |

|------------|----------------------------------------------------------------------------------------------|----|

| Figure 2.  | Clock tree                                                                                   | 13 |

| Figure 3.  | STM32F101xx medium-density access line LQFP100 pinout                                        | 21 |

| Figure 4.  | STM32F101xx medium-density access line LQFP64 pinout                                         | 22 |

| Figure 5.  | STM32F101xx medium-density access line LQFP48 pinout                                         | 22 |

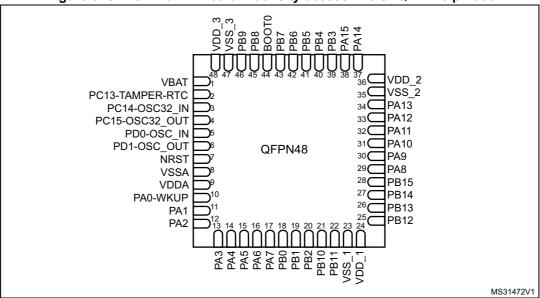

| Figure 6.  | STM32F101xx medium-density access line UFQPFN48 pinout.                                      | 23 |

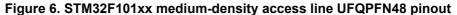

| Figure 7.  | STM32F101xx medium-density access line VFQPFN36 pinout                                       | 23 |

| Figure 8.  | Memory map                                                                                   | 29 |

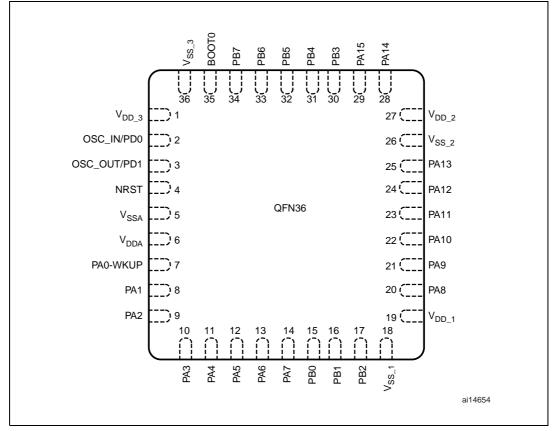

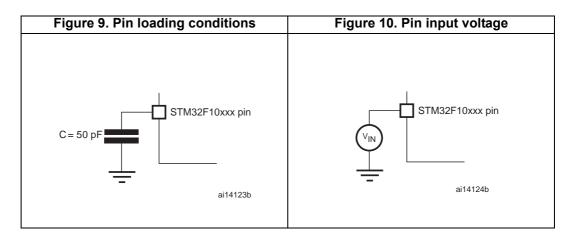

| Figure 9.  | Pin loading conditions.                                                                      |    |

| Figure 10. | Pin input voltage                                                                            | 31 |

| Figure 11. | Power supply scheme                                                                          | 31 |

| Figure 12. | Current consumption measurement scheme                                                       | 32 |

| Figure 13. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                        |    |

|            | code with data processing running from RAM, peripherals enabled.                             | 38 |

| Figure 14. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                        |    |

|            | code with data processing running from RAM, peripherals disabled                             | 38 |

| Figure 15. | Typical current consumption on V <sub>BAT</sub> with RTC on versus temperature at different  |    |

|            |                                                                                              | 40 |

| Figure 16. | Typical current consumption in Stop mode with regulator in Run mode versus                   |    |

|            | temperature at V <sub>DD</sub> = 3.3 V and 3.6 V                                             | 40 |

| Figure 17. | Typical current consumption in Stop mode with regulator in Low-power mode versus             |    |

|            | temperature at V <sub>DD</sub> = 3.3 V and 3.6 V                                             | 41 |

| Figure 18. | Typical current consumption in Standby mode versus temperature at $V_{DD}$ = 3.3 V and 3.6 V | 41 |

| Figure 19. | High-speed external clock source AC timing diagram                                           |    |

| Figure 20. | Low-speed external clock source AC timing diagram.                                           |    |

| Figure 21. | Typical application with an 8 MHz crystal.                                                   |    |

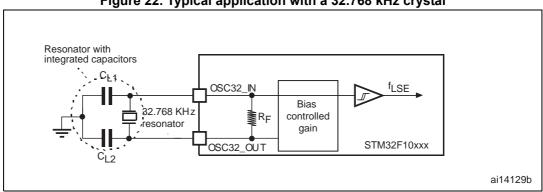

| Figure 22. | Typical application with a 32.768 kHz crystal                                                |    |

| Figure 23. | Standard I/O input characteristics - CMOS port                                               |    |

| Figure 24. | Standard I/O input characteristics - TTL port                                                |    |

| Figure 25. | 5 V tolerant I/O input characteristics - CMOS port                                           |    |

| Figure 26. | 5 V tolerant I/O input characteristics - TTL port                                            |    |

| Figure 27. | I/O AC characteristics definition                                                            |    |

| Figure 28. | Recommended NRST pin protection                                                              |    |

| Figure 29. | I <sup>2</sup> C bus AC waveforms and measurement circuit <sup>(1)</sup>                     |    |

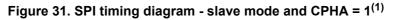

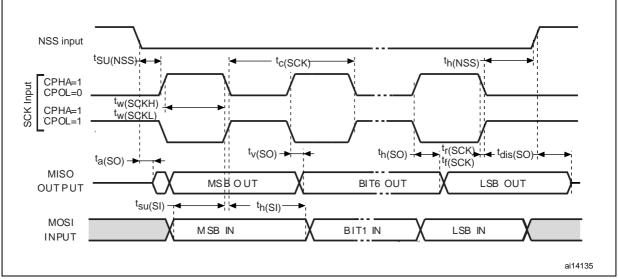

| Figure 30. | SPI timing diagram - slave mode and CPHA = 0                                                 | 66 |

| Figure 31. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                  | 66 |

| Figure 32. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 67 |

| Figure 33. | ADC accuracy characteristics                                                                 |    |

| Figure 34. | Typical connection diagram using the ADC                                                     | 71 |

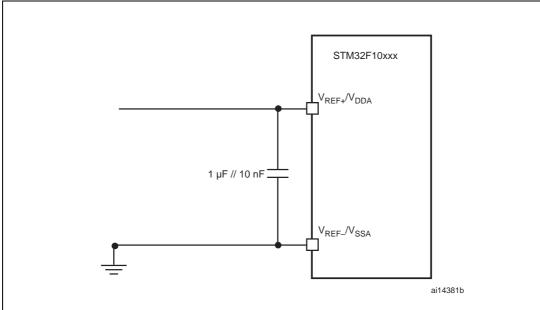

| Figure 35. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) | 71 |

| Figure 36. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     | 72 |

| Figure 37. | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline                                             |    |

| Figure 38. | UFQFPN48 recommended footprint                                                               | 74 |

| Figure 39. | UFQFPN48 marking example (package top view)                                                  | 75 |

| Figure 40. | VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat               |    |

|            | package outline                                                                              | 76 |

| Figure 41. | VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat               |    |

## 2.1 Device overview

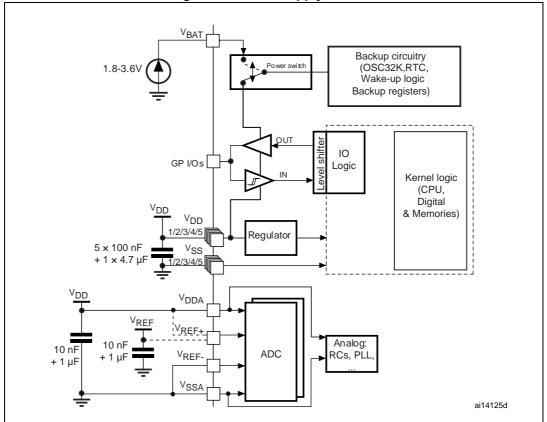

Figure 1 shows the general block diagram of the device family.

|               | medium-density access line)   |                                                                                                                        |     |                     |        |              |     |              |     |  |   |

|---------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|---------------------|--------|--------------|-----|--------------|-----|--|---|

| i i           | Peripheral                    | STM32F101Tx                                                                                                            |     | STM32               | F101Cx | STM32F101Rx  |     | STM32F101Vx  |     |  |   |

| Flash - K     | bytes                         | 64                                                                                                                     | 128 | 64                  | 128    | 64           | 128 | 64           | 128 |  |   |

| SRAM - K      | lbytes                        | 10                                                                                                                     | 16  | 10                  | 16     | 10           | 16  | 10           | 16  |  |   |

| Timers        | General -purpose              |                                                                                                                        | 3 3 |                     | 3      |              | 3   | 3            |     |  | 3 |

|               | SPI                           | 1                                                                                                                      |     | 2                   |        | 2            |     | 2            |     |  |   |

| cation        | l <sup>2</sup> C              | 1                                                                                                                      |     | 2                   |        | 2            |     | 2            |     |  |   |

| Communication | USART                         | 2                                                                                                                      |     | 3                   |        | 3            |     | 3            |     |  |   |

| -             | nchronized ADC<br>of channels | 110 channels                                                                                                           |     | 110 channels        |        | 116 channels |     | 116 channels |     |  |   |

| GPIOs         |                               | 2                                                                                                                      | 26  | 3                   | 7      | 51           |     | 80           |     |  |   |

| CPU freq      | uency                         | 36 MHz                                                                                                                 |     |                     |        |              |     |              |     |  |   |

| Operating     | g voltage                     | 2.0 to 3.6 V                                                                                                           |     |                     |        |              |     |              |     |  |   |

| Operating     | g temperatures                | Ambient temperature: -40 to +85 °C (see <i>Table 8</i> )<br>Junction temperature: -40 to +105 °C (see <i>Table 8</i> ) |     |                     |        |              |     |              |     |  |   |

| Packages      | 3                             | VFQFPN36                                                                                                               |     | LQFP48,<br>UFQFPN48 |        | LQFP64       |     | LQFP100      |     |  |   |

# Table 2. Device features and peripheral counts (STM32F101xxmedium-density access line)

|                     | Pin    | IS      |          |                   |                     |                            |                                                  | Alternate functions <sup>(3)(4)</sup>              |                          |

|---------------------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------|--------------------------|

| LQFP48/<br>UFQFPN48 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                            | Remap                    |

| 23                  | 31     | 49      | 18       | V <sub>SS_1</sub> | S                   | -                          | V <sub>SS_1</sub>                                | -                                                  | -                        |

| 24                  | 32     | 50      | 19       | V <sub>DD_1</sub> | S                   | -                          | V <sub>DD_1</sub>                                | -                                                  | -                        |

| 25                  | 33     | 51      | -        | PB12              | I/O                 | FT                         | PB12                                             | SPI2_NSS / I2C2_SMBA<br>/ USART3_CK <sup>(8)</sup> | -                        |

| 26                  | 34     | 52      | -        | PB13              | I/O                 | FT                         | PB13                                             | SPI2_SCK/<br>USART3_CTS <sup>(8)</sup>             | -                        |

| 27                  | 35     | 53      | -        | PB14              | I/O                 | FT                         | PB14                                             | SPI2_MISO/<br>USART3_RTS <sup>(8)</sup>            | -                        |

| 28                  | 36     | 54      | -        | PB15              | I/O                 | FT                         | PB15                                             | SPI2_MOSI                                          | -                        |

| -                   | -      | 55      | -        | PD8               | I/O                 | FT                         | PD8                                              | -                                                  | USART3_TX                |

| -                   | -      | 56      | -        | PD9               | I/O                 | FT                         | PD9                                              | -                                                  | USART3_RX                |

| -                   | -      | 57      | -        | PD10              | I/O                 | FT                         | PD10                                             | -                                                  | USART3_CK                |

| -                   | -      | 58      | -        | PD11              | I/O                 | FT                         | PD11                                             | -                                                  | USART3_CTS               |

| -                   | -      | 59      | -        | PD12              | I/O                 | FT                         | PD12                                             | -                                                  | TIM4_CH1 /<br>USART3_RTS |

| -                   | -      | 60      | -        | PD13              | I/O                 | FT                         | PD13                                             | -                                                  | TIM4_CH2                 |

| -                   | -      | 61      | -        | PD14              | I/O                 | FT                         | PD14                                             | -                                                  | TIM4_CH3                 |

| -                   | -      | 62      | -        | PD15              | I/O                 | FT                         | PD15                                             | -                                                  | TIM4_CH4                 |

| -                   | 37     | 63      | -        | PC6               | I/O                 | FT                         | PC6                                              | -                                                  | TIM3_CH1                 |

| -                   | 38     | 64      | -        | PC7               | I/O                 | FT                         | PC7                                              | -                                                  | TIM3_CH2                 |

| -                   | 39     | 65      | -        | PC8               | I/O                 | FT                         | PC8                                              | -                                                  | TIM3_CH3                 |

| -                   | 40     | 66      | -        | PC9               | I/O                 | FT                         | PC9                                              | -                                                  | TIM3_CH4                 |

| 29                  | 41     | 67      | 20       | PA8               | I/O                 | FT                         | PA8                                              | USART1_CK/MCO                                      | -                        |

| 30                  | 42     | 68      | 21       | PA9               | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(8)</sup>                           | -                        |

| 31                  | 43     | 69      | 22       | PA10              | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(8)</sup>                           | -                        |

| 32                  | 44     | 70      | 23       | PA11              | I/O                 | FT                         | PA11                                             | USART1_CTS                                         | -                        |

| 33                  | 45     | 71      | 24       | PA12              | I/O                 | FT                         | PA12                                             | USART1_RTS                                         | -                        |

| 34                  | 46     | 72      | 25       | PA13              | I/O                 | FT                         | JTMS-<br>SWDIO                                   | -                                                  | PA13                     |

| -                   | -      | 73      | -        |                   |                     | No                         | ot connected                                     |                                                    | -                        |

## Table 4. Medium-density STM32F101xx pin definitions (continued)

## 5.1.6 Power supply scheme

### Figure 11. Power supply scheme

**Caution:** In *Figure 11*, the 4.7  $\mu$ F capacitor must be connected to V<sub>DD3</sub>.

|                        | Peripheral               | Typical consumption at 25 °C <sup>(1)</sup> | Unit   |

|------------------------|--------------------------|---------------------------------------------|--------|

| AHB (up to             | DMA1                     | 16.53                                       |        |

| 36 MHz)                | BusMatrix <sup>(2)</sup> | 8.33                                        |        |

|                        | APB1-Bridge              | 10.28                                       |        |

|                        | TIM2                     | 32.50                                       |        |

|                        | TIM3                     | 31.39                                       |        |

|                        | TIM4                     | 31.94                                       |        |

| l                      | SPI2                     | 4.17                                        |        |

|                        | USART2                   | 12.22                                       |        |

| APB1 (up to<br>18 MHz) | USART3                   | 12.22                                       |        |

|                        | I2C1                     | 10.00                                       |        |

|                        | I2C2                     | 10.00                                       |        |

|                        | WWDG                     | 2.50                                        |        |

|                        | PWR                      | 1.67                                        | µA/MHz |

|                        | BKP                      | 2.50                                        |        |

|                        | IWDG                     | 11.67                                       |        |

|                        | APB2-Bridge              | 3.75                                        |        |

|                        | GPIO A                   | 6.67                                        |        |

|                        | GPIO B                   | 6.53                                        |        |

|                        | GPIO C                   | 6.53                                        |        |

| APB2 (up to<br>36 MHz) | GPIO D                   | 6.53                                        |        |

| 00 Mi 12)              | GPIO E                   | 6.39                                        |        |

|                        | ADC1 <sup>(3)</sup>      | 17.50                                       |        |

|                        | SPI1                     | 4.72                                        |        |

|                        | USART1                   | 11.94                                       |        |

Table 18. Peripheral current consumption

1.  $f_{HCLK}$  = 36 MHz,  $f_{APB1}$  =  $f_{HCLK}/2$ ,  $f_{APB2}$  =  $f_{HCLK}$ , default prescaler value for each peripheral.

2. The BusMatrix is automatically active when at least one master is ON.

Specific conditions for ADC: f<sub>HCLK</sub> = 28 MHz, f<sub>APB1</sub> = f<sub>HCLK</sub>/2, f<sub>APB2</sub> = f<sub>HCLK</sub>, f<sub>ADCCLK</sub> = f<sub>APB2</sub>/2. When ADON bit in the ADC\_CR2 register is set to 1, the consumption added is equal to 0.65 mA. When the ADC is enabled, a current consumption is added equal to 0.05 mA.

## 5.3.6 External clock source characteristics

## High-speed external user clock generated from an external source

The characteristics given in *Table 19* result from tests performed using an high-speed external clock source, and under the ambient temperature and supply voltage conditions summarized in *Table 8*.

| Symbol                                     | Parameter                                              | Conditions                         | Min         | Тур | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|------------------------------------|-------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                       | User external clock source<br>frequency <sup>(1)</sup> |                                    | 1           | 8   | 25                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                    |                                    | $0.7V_{DD}$ | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                     | _                                  | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>                 |                                    | 5           | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>                |                                    | -           | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>                | -                                  | -           | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                             | _                                  | 45          | -   | 55                 | %    |

| ١L                                         | OSC_IN Input leakage current                           | $V_{SS} \leq ~V_{IN} \leq ~V_{DD}$ | -           | -   | ±1                 | μA   |

Table 19. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an low-speed external clock source, and under the ambient temperature and supply voltage conditions summarized in *Table 8*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User external clock source frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>            |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>           |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>           | -                                | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                          | -                                | 30                 | -      | 70                 | %    |

| ١ <sub>L</sub>                             | OSC32_IN Input leakage current                      | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 20. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

Figure 22. Typical application with a 32.768 kHz crystal

## 5.3.7 Internal clock source characteristics

The parameters given in *Table 23* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                        | Conditions                                           |                                | Min  | Тур | Max              | Unit |

|-------------------------------------|----------------------------------|------------------------------------------------------|--------------------------------|------|-----|------------------|------|

| f <sub>HSI</sub>                    | Frequency                        |                                                      | -                              | -    | 8   | -                | MHz  |

| DuCy <sub>(HSI)</sub>               | Duty cycle                       |                                                      | -                              | 45   | -   | 55               | %    |

|                                     |                                  | User-trimmed with the RCC_CR register <sup>(2)</sup> |                                | -    | -   | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the HSI oscillator   | Factory-<br>calibrated<br>(4) (5)                    | T <sub>A</sub> = -40 to 105 °C | -2   | -   | 2.5              | %    |

| ACC <sub>HSI</sub>                  |                                  |                                                      | T <sub>A</sub> = −10 to 85 °C  | -1.5 | -   | 2.2              | %    |

|                                     |                                  |                                                      | T <sub>A</sub> = 0 to 70 °C    | -1.3 | -   | 2                | %    |

|                                     |                                  |                                                      | T <sub>A</sub> = 25 °C         | -1.1 | -   | 1.8              | %    |

| t <sub>su(HSI)</sub> <sup>(4)</sup> | HSI oscillator<br>startup time   | -                                                    |                                | 1    | -   | 2                | μs   |

| I <sub>DD(HSI)</sub> <sup>(4)</sup> | HSI oscillator power consumption | -                                                    |                                | -    | 80  | 100              | μA   |

Table 23. HSI oscillator characteristics<sup>(1)</sup>

1. V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = –40 to 105 °C unless otherwise specified.

2. Refer to application note AN2868 "STM32F10xxx internal RC oscillator (HSI) calibration" available from the ST website *www.st.com*.

3. Guaranteed by design, not tested in production.

- 4. Based on characterization, not tested in production.

- 5. The actual frequency of HSI oscillator may be impacted by a reflow, but does not drift out of the specified range.

## Low-speed internal (LSI) RC oscillator

| Table 24. LS | l oscillator | characteristics | (1) |

|--------------|--------------|-----------------|-----|

|--------------|--------------|-----------------|-----|

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 30  | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.65 | 1.2 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 85 °C unless otherwise specified.

2. Based on characterization, not tested in production.

3. Guaranteed by design, not tested in production.

#### Wakeup time from low-power mode

The wakeup times given in *Table 25* are measured on a wakeup phase with an 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode (regulator in run mode)       | 3.6 | 116  |

|                                     | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                            | 50  | μs   |

Table 25. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

## 5.3.8 PLL characteristics

The parameters given in *Table 26* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol               | Parameter                      | Value<br>Min <sup>(1)</sup> Typ Max <sup>(1)</sup> |     |      | Unit |

|----------------------|--------------------------------|----------------------------------------------------|-----|------|------|

| Symbol               | Parameter                      |                                                    |     | Unit |      |

| f <sub>PLL_IN</sub>  | PLL input clock <sup>(2)</sup> | 1                                                  | 8.0 | 25   | MHz  |

|                      | PLL input clock duty cycle     | 40                                                 | -   | 60   | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                                                 | -   | 36   | MHz  |

The test results are given in *Table 28*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                                                           | Level/Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = +25 \ ^{\circ}\text{C}, \\ \text{f}_{\text{HCLK}} = 36 \ \text{MHz} \\ \text{conforms to IEC 61000-4-2} \end{array}$ | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = +25 \ ^{\circ}\text{C}, \\ \text{f}_{\text{HCLK}} = 36 \ \text{MHz} \\ \text{conforms to IEC 61000-4-4} \end{array}$ | 4A          |

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

## **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device is monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol | Parameter                   | Conditions                                                          | Monitored<br>frequency band | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ]<br>8/36 MHz | Unit |

|--------|-----------------------------|---------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|

|        | S <sub>EMI</sub> Peak level | V 22V T 25°C                                                        | 0.1 MHz to 30 MHz           | 7                                                          |      |

| 6      |                             | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25 °C,<br>LQFP100 package | 30 MHz to 130 MHz           | 8                                                          | dBµV |

| SEMI   |                             | compliant with<br>IEC 61967-2                                       | 130 MHz to 1GHz             | 13                                                         |      |

|        |                             | SAE EMI Level                                                       | 3.5                         | -                                                          |      |

| Table | 29.         | EMI | chara  | cteristics |

|-------|-------------|-----|--------|------------|

| Table | <b>Z</b> J. |     | cilaia | CLEITSLICS |

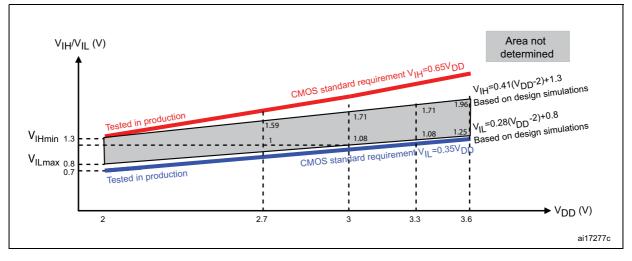

52/101

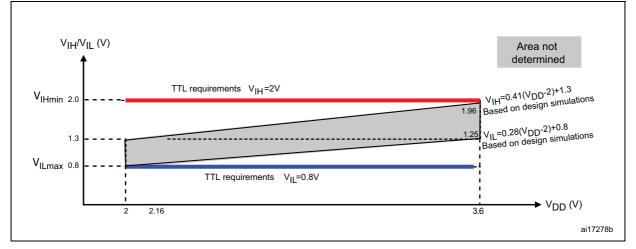

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 23* and *Figure 24* for standard I/Os, and in *Figure 25* and *Figure 26* for 5 V tolerant I/Os.

Figure 23. Standard I/O input characteristics - CMOS port

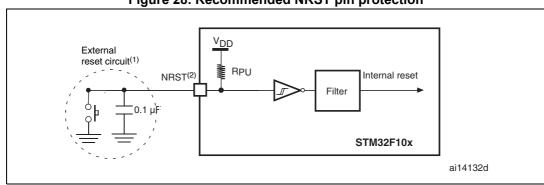

Figure 28. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

2. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 36*. Otherwise the reset will not be taken into account by the device.

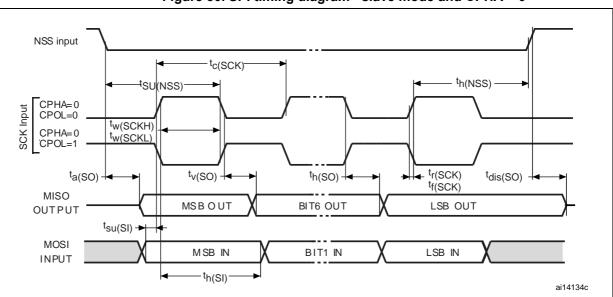

Figure 30. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

## Equation 1: R<sub>AIN</sub> max formula:

$$R_{AIN} < \frac{\Gamma_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 0.4                       |

| 7.5                     | 0.54                | 5.9                       |

| 13.5                    | 0.96                | 11.4                      |

| 28.5                    | 2.04                | 25.2                      |

| 41.5                    | 2.96                | 37.2                      |

| 55.5                    | 3.96                | 50                        |

| 71.5                    | 5.11                | NA                        |

| 239.5                   | 17.1                | NA                        |

1. Guaranteed by design, not tested in production.

| Table 40. Abb accuracy - initica test conditions |                              |                                                           |      |                    |      |  |

|--------------------------------------------------|------------------------------|-----------------------------------------------------------|------|--------------------|------|--|

| Symbol                                           | Parameter                    | Test conditions                                           | Тур  | Max <sup>(3)</sup> | Unit |  |

| ET                                               | Total unadjusted error       | f <sub>PCLK2</sub> = 28 MHz,                              | ±1.3 | ±2                 |      |  |

| EO                                               | Offset error                 | $f_{ADC}$ = 14 MHz, $R_{AIN}$ < 10 k $\Omega$ ,           | ±1   | ±1.5               |      |  |

| EG                                               | Gain error                   | V <sub>DDA</sub> = 3 V to 3.6 V<br>T <sub>A</sub> = 25 °C | ±0.5 | ±1.5               | LSB  |  |

| ED                                               | Differential linearity error | Measurements made after                                   | ±0.7 | ±1                 |      |  |

| EL                                               | Integral linearity error     | ADC calibration                                           | ±0.8 | ±1.5               |      |  |

| Table 43. ADC accuracy  | - limited test conditions <sup>(1)</sup> (2) |

|-------------------------|----------------------------------------------|

| 14010 -017 100 40041409 |                                              |

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.12 does not affect the ADC accuracy.

3. Based on characterization, not tested in production.

Figure 36. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

## 5.3.18 Temperature sensor characteristics

#### Table 45. TS characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Мах  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | $V_{SENSE}$ linearity with temperature         | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>        | Voltage at 25°C                                | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                   | 4    | -    | 10   | μs    |

| T <sub>S_temp</sub> <sup>(3)(2)</sup> | ADC sampling time when reading the temperature | -    | -    | 17.1 | μs    |

1. Guaranteed by characterization, not tested in production.

2. Guaranteed by design, not tested in production.

3. Shortest sampling time can be determined in the application by multiple iterations.

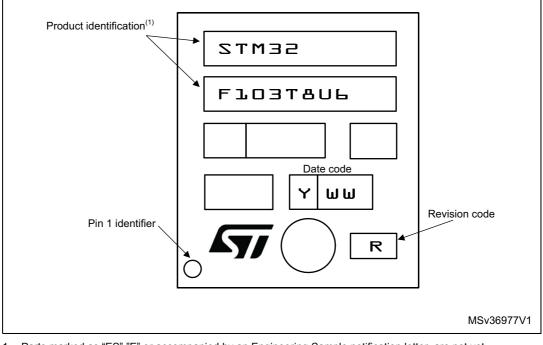

### **Device Marking for VFQFPN36**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

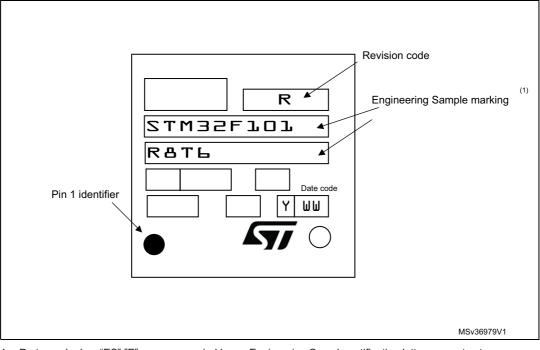

#### **Device Marking for LQFP64**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 7 Ordering information scheme

| Example:                                    | STM32F | 101 C 8 | T | 6 | xxx |

|---------------------------------------------|--------|---------|---|---|-----|

| Device family                               |        |         |   |   |     |

| STM32 = ARM-based 32-bit microcontroller    |        |         |   |   |     |

| Product type                                |        |         |   |   |     |

| F = general-purpose                         |        |         |   |   |     |

| Device subfamily                            |        |         |   |   |     |

| 101 = access line                           |        |         |   |   |     |

| Pin count                                   |        |         |   |   |     |

| T = 36 pins                                 |        |         |   |   |     |

| C = 48 pins                                 |        |         |   |   |     |

| R = 64 pins                                 |        |         |   |   |     |

| V = 100 pins                                |        |         |   |   |     |

| Flash memory size <sup>(1)</sup>            |        |         |   |   |     |

| 8 = 64 Kbytes of Flash memory               |        |         |   |   |     |

| B = 128 Kbytes of Flash memory              |        |         |   |   |     |

| Package                                     |        |         |   |   |     |

| T = LQFP                                    |        |         |   |   |     |

| U = VFQFPN or UFQFPN                        |        |         |   |   |     |

|                                             |        |         |   |   |     |

| Temperature range                           |        |         |   |   |     |

| 6 = Industrial temperature range, -40 to 85 | °C.    |         |   |   |     |

| Options                                     |        |         |   |   |     |

#### Table 52. Ordering information scheme

xxx = programmed parts

TR = tape and real

<sup>1.</sup> Although STM32F101x6 devices are not described in this datasheet, orderable part numbers that do not show the A internal code after temperature range code 6 should be referred to this datasheet for the electrical characteristics. The low-density datasheet only covers STM32F101x6 devices that feature the A code.

| Date | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date |          | <ul> <li>V<sub>ESD(CDM)</sub> value added to <i>Table 30</i>: <i>ESD absolute maximum ratings</i>.</li> <li>Note added below <i>Table 10</i>: <i>Embedded reset and power control block characteristics</i>.</li> <li>Note added below <i>Table 34</i>: <i>Output voltage characteristics</i> and V<sub>OH</sub> parameter description modified.</li> <li><i>Table 41</i>: <i>ADC characteristics</i> and <i>Table 43</i>: <i>ADC accuracy - limited test conditions</i> modified.</li> <li><i>Figure 33</i>: <i>ADC accuracy characteristics</i> modified.</li> <li>Packages are ECOPACK® compliant.</li> <li>Tables modified in <i>Section 5.3.5</i>: <i>Supply current characteristics</i>.</li> <li>ADC and ANTI_TAMPER signal names modified (see <i>Table 4</i>: <i>Medium-density STM32F101xx pin definitions</i>). <i>Table 4</i>: <i>Medium-density STM32F101xx pin definitions</i>.</li> <li><i>Table 21</i>: <i>Typical current consumption in Standby mode</i>.</li> <li>V<sub>hys</sub> modified in <i>Table 33</i>: <i>I/O static characteristics</i>.</li> <li>Updated: <i>Table 28</i>: <i>EMS characteristics</i> and <i>Table 29</i>: <i>EMI characteristics</i>.</li> <li><i>t</i><sub>VDD</sub> modified in <i>Table 9</i>: <i>Operating conditions at power-up / power-down</i>.</li> <li>Typical values modified, note 2 modified and note 3 removed in <i>Table 25</i>: <i>Low-power mode wakeup timings</i>.</li> <li>Maximum current consumption <i>Table 15</i>: <i>Typical and maximum current consumptions in Stop and Standby modes</i>.</li> <li><i>On-chip peripheral current consumption on page 43</i> added.</li> <li>Package mechanical data inch values are calculated from mm and rounded to <i>4 decimal digits</i> (see <i>Section 6: Package characteristics</i>).</li> <li>V<sub>prog</sub> added to <i>Table 27: Flash memory characteristics</i>.</li> <li>T<sub>S_trefint</sub> added to <i>Table 27: Flash memory characteristics</i></li></ul> |

|      |          | Note 7 modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |          | Option byte addresses corrected in <i>Figure 8: Memory map</i> .<br>ACC <sub>HSI</sub> modified in <i>Table 23: HSI oscillator characteristics</i> .<br>t <sub>JITTER</sub> removed from <i>Table 26: PLL characteristics</i> .<br><i>Appendix A: Important notes on page 71</i> added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |          | Added: Figure 13, Figure 14, Figure 16 and Figure 18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 53. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             |          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 21-Apr-2009 | 11       | <ul> <li>I/O information clarified on page 1. Figure 8: Memory map modified.</li> <li>In Table 4: Medium-density STM32F101xx pin definitions: PB4, PB13, PB14, PB15, PB3/TRACESWO moved from Default column to Remap column.</li> <li>Note modified in Table 12: Maximum current consumption in Run mode, code with data processing running from Flash and Table 14: Maximum current consumption in Sleep mode, code running from Flash or RAM.</li> <li>Figure 16, Figure 17 and Figure 18 show typical curves.</li> <li>Table 19: High-speed external user clock characteristics and Table 20: Low-speed external user clock characteristics modified.</li> <li>ACC<sub>HSI</sub> max values modified in Table 23: HSI oscillator characteristics.</li> </ul> |  |  |  |

| 22-Sep-2009 |          | Small text changes.         Note 5 updated and Note 4 added in Table 4: Medium-density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|             | 12       | $STM32F101xx \ pin \ definitions.$ $V_{\text{RERINT}} \ and \ T_{\text{Coeff}} \ added \ to \ Table \ 11: \ Embedded \ internal \ reference \ voltage. \ Typical \ I_{\text{DD}\_VBAT} \ value \ added \ in \ Table \ 15: \ Typical \ and \ maximum \ current \ consumptions \ in \ Stop \ and \ Standby \ modes. \ Figure \ 15: \ Typical \ current \ consumption \ on \ VBAT \ with \ RTC \ on \ versus \ temperature \ at \ different \ VBAT \ values \ added.$                                                                                                                                                                                                                                                                                              |  |  |  |

|             |          | f <sub>HSE_ext</sub> min modified in <i>Table 19: High-speed external user clock characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|             |          | $C_{L1}$ and $C_{L2}$ replaced by C in <i>Table 21: HSE 4-16 MHz oscillator</i><br><i>characteristics</i> and <i>Table 22: LSE oscillator characteristics (fLSE =</i><br><i>32.768 kHz)</i> , notes modified and moved below the tables.<br><i>Table 23: HSI oscillator characteristics</i> modified. Conditions removed from                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|             |          | Table 25: Low-power mode wakeup timings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|             |          | Figure 28: Recommended NRST pin protection modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|             |          | <i>Note 1</i> modified below <i>Figure 21: Typical application with an 8 MHz crystal.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|             |          | Figure 28: Recommended NRST pin protection modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|             |          | IEC 1000 standard updated to IEC 61000 and SAE J1752/3 updated to IEC 61967-2 in Section 5.3.10: EMC characteristics on page 51.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|             |          | Jitter added to <i>Table 26: PLL characteristics</i> . $C_{ADC}$ and $R_{AIN}$ parameters modified in <i>Table 41: ADC characteristics</i> . $R_{AIN}$ max values modified in <i>Table 42: RAIN max for fADC = 14 MHz</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|             |          | Small text changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 20-May-2010 | 13       | Added STM32F101TB devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             |          | Added VFQFPN48 package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|             |          | Updated note 2 below Table 38: I2C characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|             |          | Updated Figure 29: I2C bus AC waveforms and measurement circuit(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|             |          | Updated Figure 28: Recommended NRST pin protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|             |          | Updated Section 5.3.12: I/O current injection characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Table 53. Document revision history (continued) | Table 53. | . Document | revision | history | (continued) |

|-------------------------------------------------|-----------|------------|----------|---------|-------------|

|-------------------------------------------------|-----------|------------|----------|---------|-------------|