Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 36MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                             |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 36-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 36-VFQFPN (6x6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101tbu6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F101xB and STM32F101x8 medium-density access line family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup> -M3 32-bit RISC core operating at a 36 MHz frequency, high-speed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 16 Kbytes), and an extensive range of enhanced peripherals and I/Os connected to two APB buses. All devices offer standard communication interfaces (two I<sup>2</sup>Cs, two SPIs, and up to three USARTs), one 12-bit ADC and three general-purpose 16-bit timers.

The STM32F101xx medium-density access line family operates in the –40 to +85 °C temperature range, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F101xx medium-density access line family includes devices in four different packages ranging from 36 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F101xx medium-density access line microcontroller family suitable for a wide range of applications such as application control and user interface, medical and handheld equipment, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, Video intercoms, and HVACs.

#### STM32F101x8, STM32F101xB

1. When the HSI is used as a PLL clock input, the maximum system clock frequency that can be achieved is 36 MHz.

2. To have an ADC conversion time of 1  $\mu s,$  APB2 must be at 14 MHz or 28 MHz.

## 2.2 Full compatibility throughout the family

The STM32F101xx is a complete family whose members are fully pin-to-pin, software and feature compatible. In the reference manual, the STM32F101x4 and STM32F101x6 are referred to as low-density devices, the STM32F101x8 and STM32F101xB are referred to as medium-density devices, and the STM32F101xC, STM32F101xD and STM32F101xE are referred to as high-density devices.

Low- and high-density devices are an extension of the STM32F101x8/B devices, they are specified in the STM32F101x4/6 and STM32F101xC/D/E datasheets, respectively. Low-density devices feature lower Flash memory and RAM capacities and a timer less. High-density devices have higher Flash memory and RAM capacities, and additional peripherals like FSMC and DAC, while remaining fully compatible with the other members of the STM32F101xx family.

The STM32F101x4, STM32F101x6, STM32F101xC, STM32F101xD and STM32F101xE are a drop-in replacement for the STM32F101x8/B medium-density devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.

Moreover, the STM32F101xx performance line family is fully compatible with all existing STM32F101xx access line and STM32F102xx USB access line devices.

|        |                                |     |                          |       | •                    |                                               |                 |  |  |

|--------|--------------------------------|-----|--------------------------|-------|----------------------|-----------------------------------------------|-----------------|--|--|

|        | Memory size                    |     |                          |       |                      |                                               |                 |  |  |

|        | Low-density devices            |     | Medium-density devices   |       | High-density devices |                                               |                 |  |  |

| Pinout | 16 KB<br>Flash                 | (4) |                          |       | 256 KB<br>Flash      | 384 KB<br>Flash                               | 512 KB<br>Flash |  |  |

|        | 4 KB RAM 6 KB RAM              |     | 10 KB RAM 16 KB RAM      |       | 32 KB<br>RAM         | 48 KB<br>RAM                                  | 48 KB<br>RAM    |  |  |

| 144    | -                              | -   | -                        | -     | 5 × USARTs           |                                               |                 |  |  |

| 100    | -                              | -   |                          |       |                      | ners, 2 × basi<br>× I <sup>2</sup> Cs, 1 × AI |                 |  |  |

| 64     | 2 × USART                      |     | J ^ USANIS               |       | ,                    | SMC (100 an                                   | ,               |  |  |

| 48     | 2 × 16-bit tii<br>1 × SPI, 1 × |     | 2 × SPIs, 2 ×<br>1 × ADC | I2Cs, | -                    | -                                             | -               |  |  |

| 36     | 1 × ADC                        |     | 1                        |       | -                    | _                                             | -               |  |  |

Table 3. STM32F101xx family

1. For orderable part numbers that do not show the A internal code after the temperature range code (6), the reference datasheet for electrical characteristics is that of the STM32F101x8/B medium-density devices.

#### 2.3.17 SysTick timer

This timer is dedicated for OS, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

#### 2.3.18 General-purpose timers (TIMx)

There are three synchronizable general-purpose timers embedded in the STM32F101xx medium-density access line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture, output compare, PWM or one pulse mode output. This gives up to 12 input captures / output compares / PWMs on the largest packages.

The general-purpose timers can work together via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

## 2.3.19 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7/10-bit addressing in master mode. A hardware CRC generation/verification is embedded. They can be served by DMA and they support SM Bus 2.0/PM Bus.

#### 2.3.20 Universal synchronous/asynchronous receiver transmitter (USART)

The available USART interfaces communicate at up to 2.25 Mbit/s. They provide hardware management of the CTS and RTS signals, support IrDA SIR ENDEC, are ISO 7816 compliant and have LIN Master/Slave capability.

The USART interfaces can be served by the DMA controller.

#### 2.3.21 Serial peripheral interface (SPI)

Up to two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in fullduplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

Both SPIs can be served by the DMA controller.

#### 2.3.22 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the

DocID13586 Rev 17

GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current-capable.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

#### 2.3.23 ADC (analog to digital converter)

The 12-bit analog to digital converter has up to 16 external channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

#### 2.3.24 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

#### 2.3.25 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

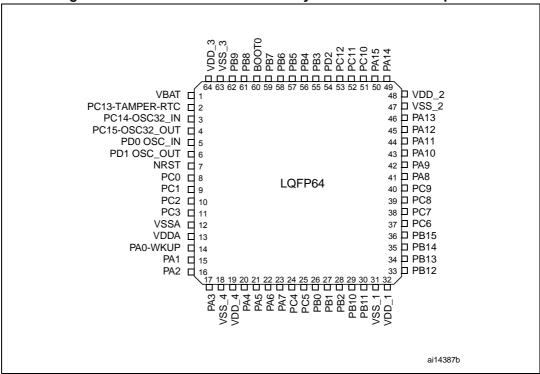

Figure 4. STM32F101xx medium-density access line LQFP64 pinout

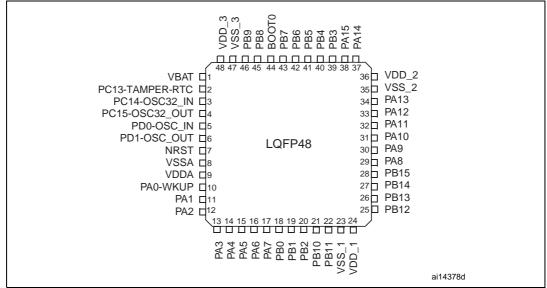

Figure 5. STM32F101xx medium-density access line LQFP48 pinout

|                     | Pin    | IS      |          |                   |                     |                            |                                                  | Alternate functions <sup>(3)(4)</sup>                          |          |

|---------------------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------|----------|

| LQFP48/<br>UFQFPN48 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                        | Remap    |

| 12                  | 16     | 25      | 9        | PA2               | I/O                 | -                          | PA2                                              | USART2_TX <sup>(8)</sup> /<br>ADC_IN2/TIM2_CH3 <sup>(8)</sup>  | -        |

| 13                  | 17     | 26      | 10       | PA3               | I/O                 | -                          | PA3                                              | USART2_RX <sup>(8)</sup> /<br>ADC_IN3/TIM2_CH4 <sup>(8)</sup>  | -        |

| -                   | 18     | 27      | -        | V <sub>SS_4</sub> | S                   | -                          | V <sub>SS_4</sub>                                | -                                                              | -        |

| -                   | 19     | 28      | -        | V <sub>DD_4</sub> | S                   | -                          | V <sub>DD_4</sub>                                | -                                                              | -        |

| 14                  | 20     | 29      | 11       | PA4               | I/O                 | -                          | PA4                                              | SPI1_NSS <sup>(8)</sup> /ADC_IN4<br>USART2_CK <sup>(8)</sup> / | -        |

| 15                  | 21     | 30      | 12       | PA5               | I/O                 | -                          | PA5                                              | SPI1_SCK <sup>(8)</sup> /ADC_IN5                               | -        |

| 16                  | 22     | 31      | 13       | PA6               | I/O                 | -                          | PA6                                              | SPI1_MISO <sup>(8)</sup> /ADC_IN6<br>TIM3_CH1 <sup>(8)</sup>   | -        |

| 17                  | 23     | 32      | 14       | PA7               | I/O                 | -                          | PA7                                              | SPI1_MOSI <sup>(8)</sup> /ADC_IN7<br>TIM3_CH2 <sup>(8)</sup>   | -        |

| -                   | 24     | 33      | -        | PC4               | I/O                 | -                          | PC4                                              | ADC_IN14                                                       | -        |

| -                   | 25     | 34      | -        | PC5               | I/O                 | -                          | PC5                                              | ADC_IN15                                                       | -        |

| 18                  | 26     | 35      | 15       | PB0               | I/O                 | -                          | PB0                                              | ADC_IN8/TIM3_CH3 <sup>(8)</sup>                                | -        |

| 19                  | 27     | 36      | 16       | PB1               | I/O                 | -                          | PB1                                              | ADC_IN9/TIM3_CH4 <sup>(8)</sup>                                | -        |

| 20                  | 28     | 37      | 17       | PB2               | I/O                 | FT                         | PB2/BOOT1                                        | -                                                              | -        |

| -                   | -      | 38      | -        | PE7               | I/O                 | FT                         | PE7                                              | -                                                              | -        |

| -                   | -      | 39      | -        | PE8               | I/O                 | FT                         | PE8                                              | -                                                              | -        |

| -                   | -      | 40      | -        | PE9               | I/O                 | FT                         | PE9                                              | -                                                              | -        |

| -                   | -      | 41      | -        | PE10              | I/O                 | FT                         | PE10                                             | -                                                              | -        |

| -                   | -      | 42      | -        | PE11              | I/O                 | FT                         | PE11                                             | -                                                              | -        |

| -                   | -      | 43      | -        | PE12              | I/O                 | FT                         | PE12                                             | -                                                              | -        |

| -                   | -      | 44      | -        | PE13              | I/O                 | FT                         | PE13                                             | -                                                              | -        |

| -                   | -      | 45      | -        | PE14              | I/O                 | FT                         | PE14                                             | -                                                              | -        |

| -                   | -      | 46      | -        | PE15              | I/O                 | FT                         | PE15                                             | -                                                              | -        |

| 21                  | 29     | 47      | -        | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/<br>USART3_TX <sup>(8)</sup>                          | TIM2_CH3 |

| 22                  | 30     | 48      | -        | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/<br>USART3_RX <sup>(8)</sup>                          | TIM2_CH4 |

| Table 4. Medium-densit | y STM32F101xx pin | n definitions ( | (continued) | 1 |

|------------------------|-------------------|-----------------|-------------|---|

|                        |                   |                 |             |   |

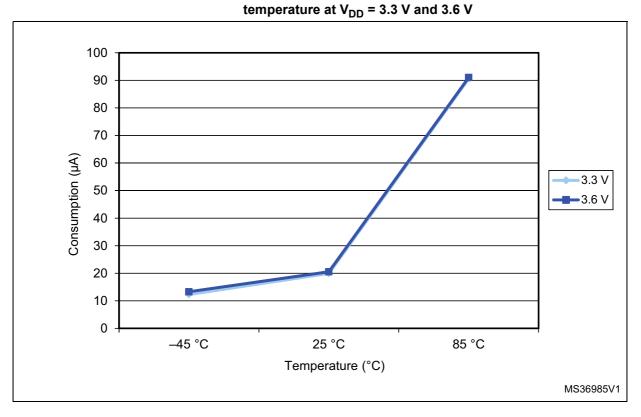

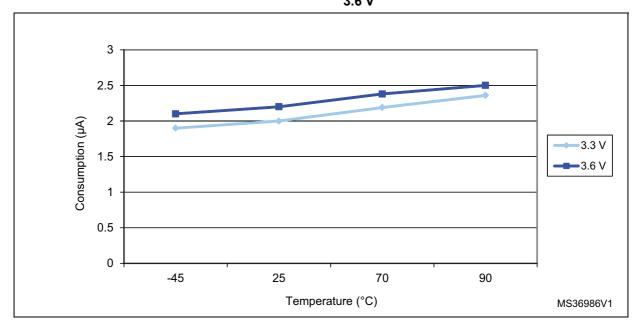

Figure 17. Typical current consumption in Stop mode with regulator in Low-power mode versus

Figure 18. Typical current consumption in Standby mode versus temperature at V\_{DD} = 3.3 V and 3.6 V

DocID13586 Rev 17

| Peripheral             |                          | Typical consumption at 25 °C <sup>(1)</sup> | Unit   |

|------------------------|--------------------------|---------------------------------------------|--------|

| AHB (up to             | DMA1                     | 16.53                                       |        |

| 36 MHz)                | BusMatrix <sup>(2)</sup> | 8.33                                        |        |

|                        | APB1-Bridge              | 10.28                                       |        |

|                        | TIM2                     | 32.50                                       |        |

|                        | TIM3                     | 31.39                                       |        |

|                        | TIM4                     | 31.94                                       |        |

| l                      | SPI2                     | 4.17                                        |        |

|                        | USART2                   | 12.22                                       |        |

| APB1 (up to<br>18 MHz) | USART3                   | 12.22                                       |        |

|                        | I2C1                     | 10.00                                       |        |

|                        | I2C2                     | 10.00                                       |        |

|                        | WWDG                     | 2.50                                        |        |

|                        | PWR                      | 1.67                                        | µA/MHz |

|                        | BKP                      | 2.50                                        |        |

|                        | IWDG                     | 11.67                                       |        |

|                        | APB2-Bridge              | 3.75                                        |        |

|                        | GPIO A                   | 6.67                                        |        |

|                        | GPIO B                   | 6.53                                        |        |

|                        | GPIO C                   | 6.53                                        |        |

| APB2 (up to<br>36 MHz) | GPIO D                   | 6.53                                        |        |

|                        | GPIO E                   | 6.39                                        |        |

|                        | ADC1 <sup>(3)</sup>      | 17.50                                       |        |

|                        | SPI1                     | 4.72                                        |        |

|                        | USART1                   | 11.94                                       |        |

Table 18. Peripheral current consumption

1.  $f_{HCLK}$  = 36 MHz,  $f_{APB1}$  =  $f_{HCLK}/2$ ,  $f_{APB2}$  =  $f_{HCLK}$ , default prescaler value for each peripheral.

2. The BusMatrix is automatically active when at least one master is ON.

Specific conditions for ADC: f<sub>HCLK</sub> = 28 MHz, f<sub>APB1</sub> = f<sub>HCLK</sub>/2, f<sub>APB2</sub> = f<sub>HCLK</sub>, f<sub>ADCCLK</sub> = f<sub>APB2</sub>/2. When ADON bit in the ADC\_CR2 register is set to 1, the consumption added is equal to 0.65 mA. When the ADC is enabled, a current consumption is added equal to 0.05 mA.

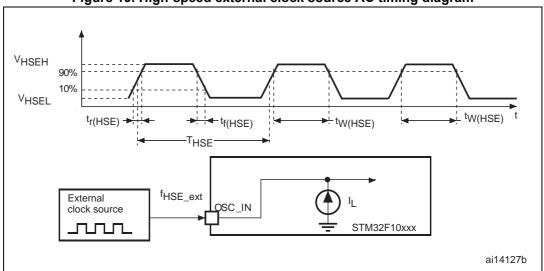

## 5.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

The characteristics given in *Table 19* result from tests performed using an high-speed external clock source, and under the ambient temperature and supply voltage conditions summarized in *Table 8*.

Figure 19. High-speed external clock source AC timing diagram

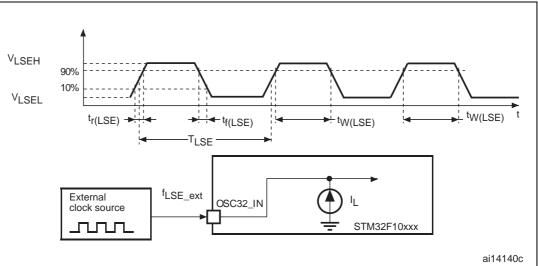

Figure 20. Low-speed external clock source AC timing diagram

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 21*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

#### Low-speed internal (LSI) RC oscillator

| Table 24. LS | l oscillator | characteristics | (1) |

|--------------|--------------|-----------------|-----|

|--------------|--------------|-----------------|-----|

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 30  | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.65 | 1.2 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 85 °C unless otherwise specified.

2. Based on characterization, not tested in production.

3. Guaranteed by design, not tested in production.

#### Wakeup time from low-power mode

The wakeup times given in *Table 25* are measured on a wakeup phase with an 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode (regulator in run mode)       | 3.6 | 116  |

| 'WUSTOP` '                          | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                            | 50  | μs   |

Table 25. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

#### 5.3.8 PLL characteristics

The parameters given in *Table 26* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol               | Devenueter                     |                    | Unit |                    |      |

|----------------------|--------------------------------|--------------------|------|--------------------|------|

| Symbol               | Parameter                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| f <sub>PLL_IN</sub>  | PLL input clock <sup>(2)</sup> | 1                  | 8.0  | 25                 | MHz  |

|                      | PLL input clock duty cycle     | 40                 | -    | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                 | -    | 36                 | MHz  |

The test results are given in *Table 28*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                                                           | Level/Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = +25 \ ^{\circ}\text{C}, \\ \text{f}_{\text{HCLK}} = 36 \ \text{MHz} \\ \text{conforms to IEC 61000-4-2} \end{array}$ | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = +25 \ ^{\circ}\text{C}, \\ \text{f}_{\text{HCLK}} = 36 \ \text{MHz} \\ \text{conforms to IEC 61000-4-4} \end{array}$ | 4A          |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device is monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol              | Parameter  | Conditions                                                          | Monitored<br>frequency band | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ]<br>8/36 MHz | Unit |

|---------------------|------------|---------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|

|                     |            | 0.1 MHz to 30 MHz                                                   | 7                           |                                                            |      |

| 6                   | Peak level | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25 °C,<br>LQFP100 package | 30 MHz to 130 MHz           | 8                                                          | dBµV |

| S <sub>EMI</sub> Pe | Peak level | compliant with<br>IEC 61967-2                                       | 130 MHz to 1GHz             | 13                                                         |      |

|                     |            | IEC 01907-2                                                         | SAE EMI Level               | 3.5                                                        | -    |

| Table | 29.         | EMI | chara  | cteristics |

|-------|-------------|-----|--------|------------|

| Table | <b>Z</b> J. |     | cilaia |            |

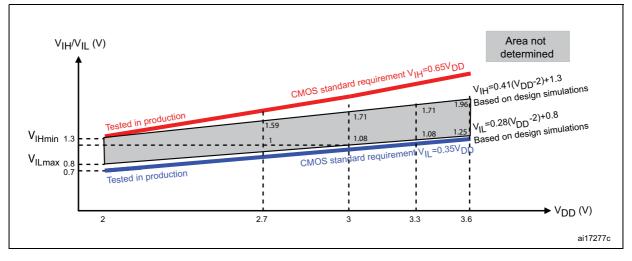

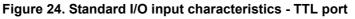

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 23* and *Figure 24* for standard I/Os, and in *Figure 25* and *Figure 26* for 5 V tolerant I/Os.

Figure 23. Standard I/O input characteristics - CMOS port

#### **Output driving current**

The GPIOs (general-purpose inputs/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to +/-3mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 6*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 6*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                                                                                       | Conditions                                                  | Min                  | Max | Unit |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output Low level voltage for an I/O pin<br>when 8 pins are sunk at the same time CMOS port <sup>(2)</sup> ,     |                                                             | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output High level voltage for an I/O pin when 8 pins are sourced at the same time                               | I <sub>IO</sub> = +8 mA,<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin<br>when 8 pins are sunk at the same time                                |                                                             | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time                               |                                                             |                      | -   |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time                                   | I <sub>IO</sub> = +20 mA <sup>(4)</sup>                     | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time                               | 2.7 V < V <sub>DD</sub> < 3.6 V                             | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin<br>when 8 pins are sunk at the same time $I_{IO} = +6 \text{ mA}^{(4)}$ |                                                             | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time                               | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   | v    |

#### Table 34. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 6* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 6 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data, not tested in production.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 27* and *Table 35*, respectively.

Unless otherwise specified, the parameters given in *Table 35* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                             | Мах                | Unit |  |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|--|

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                 | 2                  | MHz  |  |

| 10                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C = 50  pE V = 2 V  to  2  GV                          | 125 <sup>(3)</sup> | ns   |  |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 125 <sup>(3)</sup> |      |  |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V               | 10                 | MHz  |  |

| 01                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    |                                                        | 25 <sup>(3)</sup>  |      |  |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 25 <sup>(3)</sup>  | ns   |  |

|                                            | F <sub>max(IO)out</sub> | Maximum Frequency <sup>(2)</sup>                                      | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 50                 | MHz  |  |

|                                            |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 30                 | MHz  |  |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 20                 | MHz  |  |

|                                            | t <sub>f(IO)out</sub>   | Output low to high level rise                                         | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   | -    |  |

| 11                                         |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 8 <sup>(3)</sup>   |      |  |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |  |

|                                            |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   | ns   |  |

|                                            |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 8 <sup>(3)</sup>   | 1    |  |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |  |

| -                                          | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                                      | 10                 | ns   |  |

Table 35. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure 27*.

3. Guaranteed by design, not tested in production.

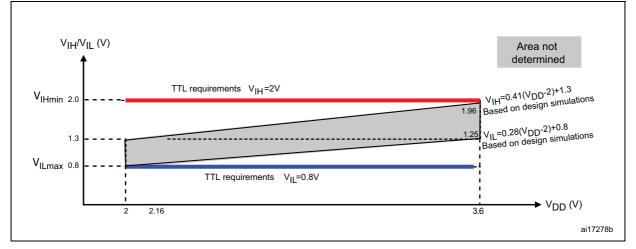

# 6.3 VFQFPN36 package information

Figure 40. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat

1. Drawing is not to scale.

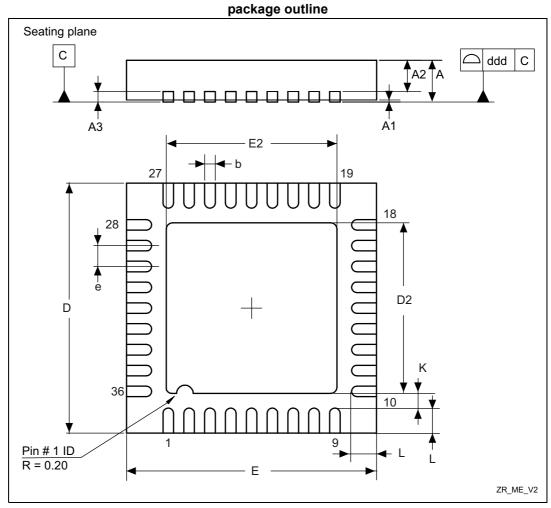

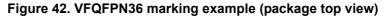

#### **Device Marking for VFQFPN36**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

#### 6.5 LQFP64 package information

SEATING PLANE С 0.25 mm GAUGE PLANE ¥ G 7 D K D1 L1 D3 48 33 32 49 <u>A A A A A A A A A A A A A</u> b E3 Ш ш 64 17 ₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽ 16 PIN 1 IDENTIFICATION 1 ⊾e 5W\_ME\_V3

Figure 46. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |

|-------------------------------------------------------------|

| package mechanical data                                     |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

# 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-Jun-2007 | 1        | First draft.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |          | IDD values modified in Table 11: Maximum current consumption in Run and Sleep modes (TA = 85 °C).         VBAT range modified in Power supply schemes.         VREF+ min value, t <sub>STAB</sub> , t <sub>lat</sub> and f <sub>TRIG</sub> added to Table 41: ADC characteristics. Table 37: TIMx characteristics modified.         Note 6 modified and Note 8, Note 5 and Note 7 added below Table 4: Medium-density STM32F101xx pin definitions.         Figure 20: Low-speed external clock source AC timing diagram, Figure 11: Power supply scheme, Figure 28: Recommended NRST pin protection and Figure 29: I2C bus AC waveforms and measurement simult(1) modified                                           |

| 20-Jul-07   | 2        | <i>circuit(1)</i> modified.<br>Sample size modified and machine model removed in <i>Electrostatic</i><br><i>discharge (ESD)</i> .<br>Number of parts modified and standard reference updated in <i>Static latch-<br/>up</i> . 25 °C and 85 °C conditions removed and class name modified in<br><i>Table 31: Electrical sensitivities</i> .<br>t <sub>SU(LSE)</sub> changed to t <sub>SU(LSE)</sub> in <i>Table 21: HSE 4-16 MHz oscillator</i>                                                                                                                                                                                                                                                                       |

|             |          | characteristics.<br>In Table 27: Flash memory characteristics, typical endurance added, data retention for $T_A = 25$ °C removed and data retention for $T_A = 85$ °C added.<br>Note removed below Table 8: General operating conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |          | <ul> <li>V<sub>BG</sub> changed to V<sub>REFINT</sub> in <i>Table 11: Embedded internal reference</i> voltage. I<sub>DD</sub> max values added to <i>Table 11: Maximum current</i> consumption in Run and Sleep modes (TA = 85 °C).</li> <li>I<sub>DD(HSI)</sub> max value added to <i>Table 23: HSI oscillator characteristics</i>.</li> <li>R<sub>PU</sub> and R<sub>PD</sub> min and max values added to <i>Table 33: I/O static</i> characteristics. R<sub>PU</sub> min and max values added to <i>Table 36: NRST pin</i> characteristics (two notes removed).</li> <li>Datasheet title corrected. USB characteristics section removed. <i>Features on page 1</i> list optimized. Small text changes.</li> </ul> |

| Table 53. | Document | revision | history |

|-----------|----------|----------|---------|

|-----------|----------|----------|---------|

| Table 53. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 21-Jul-2008                                     | 8        | Small text changes.Power supply supervisor on page 16 modified and $V_{DDA}$ added to Table 8:General operating conditions on page 33.Capacitance modified in Figure 11: Power supply scheme on page 31.Table notes revised in Section 5: Electrical characteristics.Maximum value of $t_{RSTTEMPO}$ modified in Table 10: Embedded reset and<br>power control block characteristics on page 35.Values added to Table 15: Typical and maximum current consumptions in<br>Stop and Standby modes and Table 21: Typical current consumption in<br>Standby mode removed.f_HSE_extf_HSE_ext modified in Table 19: High-speed external user clock<br>characteristics on page 45.f_HCLKcorrected in Table 28: EMS characteristics.Minimum SDA and SCL fall time value for Fast mode removed from<br>Table 38: I2C characteristics on page 63, note 1 modified.t_h(NSS)modified in Table 40: SPI characteristics on page 65 and<br>Figure 30: SPI timing diagram - slave mode and CPHA = 0 on page 66.C_{ADC}C_ADCmodified in Table 43: ADC caccuracy - limited test conditions and<br>Table 44: ADC accuracy.Typical T_s_tempvalue removed from Table 45: TS characteristics on<br>page 72.LQFP48 package specifications updated (see Table 50, Table 49 and<br>Table 50).Axx option removed from Table 52: Ordering information scheme on<br>page 92. |  |  |

| 24-Jul-2008                                     | 9        | First page modified: "Up to 2 x I <sup>2</sup> C interfaces" instead of "1 x I <sup>2</sup> C interface'<br>STM32F101xx devices with 32 Kbyte Flash memory capacity removed,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 23-Sep-2008                                     | 10       | Shinszi fortx devices with 32 kbyte hash memory capacity removed,<br>document updated accordingly.<br>Section 2.2: Full compatibility throughout the family on page 14 updated.<br>Notes modified in Table 4: Medium-density STM32F101xx pin definitions<br>on page 24.<br>Note 2 modified below Table 5: Voltage characteristics on page 32,<br>$ \Delta V_{DDx} $ min and $ \Delta V_{DDx} $ min removed.<br>Note 2 added to Table 8: General operating conditions on page 33.<br>Measurement conditions specified in Section 5.3.5: Supply current<br>characteristics on page 36.<br>I <sub>DD</sub> in standby mode at 85 °C modified in Table 15: Typical and maximum<br>current consumptions in Stop and Standby modes on page 39.<br>General input/output characteristics on page 55 modified.<br>Note added below Table 52: Ordering information scheme.<br>Section 7.1: Future family enhancements removed. Small text changes.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |