# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 36MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                             |

| Number of I/O              | 80                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 10K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101v8t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Revis | ion hist  | ory                                                            | 94 |

|---|-------|-----------|----------------------------------------------------------------|----|

| 7 | Orde  | ring info | rmation scheme                                                 | 92 |

|   |       | 6.7.2     | Evaluating the maximum junction temperature for an application | 91 |

|   |       | 6.7.1     | Reference document                                             | 90 |

|   | 6.7   | Therma    | characteristics                                                | 90 |

|   | 6.6   | LQFP48    | package information                                            | 86 |

|   | 6.5   | LQFP64    | package information                                            | 83 |

|   | 6.4   | LQFP10    | 0 package information                                          | 80 |

# 5 Electrical characteristics

## 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to  $\mathsf{V}_{SS}.$

## 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 2 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

## 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 10*.

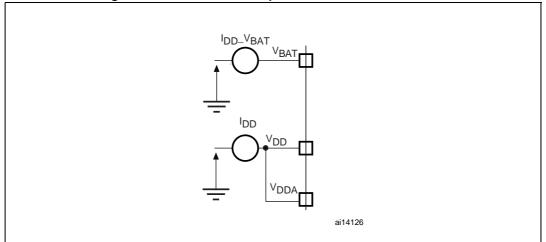

### 5.1.7 Current consumption measurement

#### Figure 12. Current consumption measurement scheme

# 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 5: Voltage characteristics*, *Table 6: Current characteristics*, and *Table 7: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                         | Ratings                                                               | Min          | Max                                                                         | Unit |

|--------------------------------|-----------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------|------|

| $V_{DD} - V_{SS}$              | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{(1)}$ | -0.3         | 4.0                                                                         |      |

| V <sub>IN</sub> <sup>(2)</sup> | Input voltage on five volt tolerant pin                               | $V_{SS}-0.3$ | $V_{DD}$ + 4.0                                                              | V    |

| VIN` ∕                         | Input voltage on any other pin                                        | $V_{SS}-0.3$ | 4.0                                                                         |      |

| $ \Delta V_{DDx} $             | Variations between different $V_{DD}$ power pins                      | -            | 50                                                                          |      |

| $ V_{SSX} - V_{SS} $           | Variations between all the different ground pins                      | -            | 50                                                                          | mV   |

| V <sub>ESD(HBM)</sub>          | Electrostatic discharge voltage (human body model)                    | maximum rati | see Section 5.3.11: Absolute<br>maximum ratings (electrical<br>sensitivity) |      |

#### Table 5. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 6: Current characteristics* for the maximum allowed injected current values.

| Symbol              | Deremeter         | Quandi di una                                         | 4                 | Max <sup>(1)</sup>     | Unit |

|---------------------|-------------------|-------------------------------------------------------|-------------------|------------------------|------|

|                     | Parameter         | Conditions                                            | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | Unit |

|                     |                   |                                                       | 36 MHz            | 15.5                   |      |

| . Supply current in |                   | External clock <sup>(2)</sup> all peripherals enabled | 24 MHz            | 11.5                   |      |

|                     |                   |                                                       | 16 MHz            | 8.5                    |      |

|                     | Supply current in |                                                       | 8 MHz             | 5.5                    | mA   |

| IDD                 | Sleep mode        |                                                       | 36 MHz            | 5                      | ША   |

|                     |                   | External clock <sup>(2)</sup> , all                   | 24 MHz            | 4.5                    |      |

|                     |                   | peripherals disabled                                  | 16 MHz            | 4                      |      |

|                     |                   |                                                       | 8 MHz             | 3                      |      |

# Table 14. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. Based on characterization, tested in production at  $V_{\text{DD}}$  max and  $f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                                |                                                                                                                                                |                                                                                                                                          |      | Тур <sup>(1)</sup>                               |                         | Max                                      |      |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------|-------------------------|------------------------------------------|------|

| Symbol Parame                  | Parameter                                                                                                                                      | Parameter Conditions                                                                                                                     |      | V <sub>DD</sub> /<br>V <sub>BAT</sub> =<br>2.4 V | $V_{DD}/V_B$<br>= 3.3 V | T <sub>A</sub> =<br>85 °C <sup>(2)</sup> | Unit |

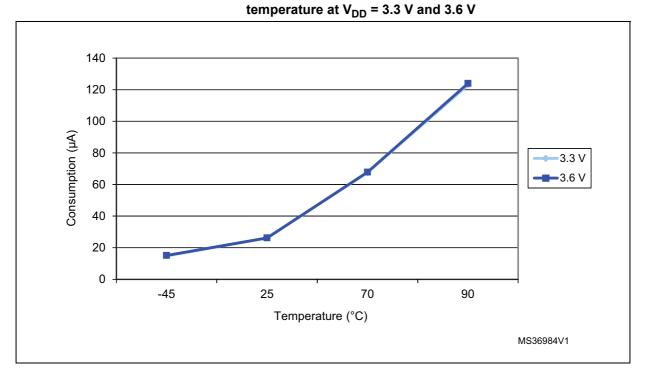

| Supply current<br>in Stop mode | Supply current                                                                                                                                 | Regulator in Run mode,<br>Low-speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -    | 23.5                                             | 24                      | 200                                      |      |

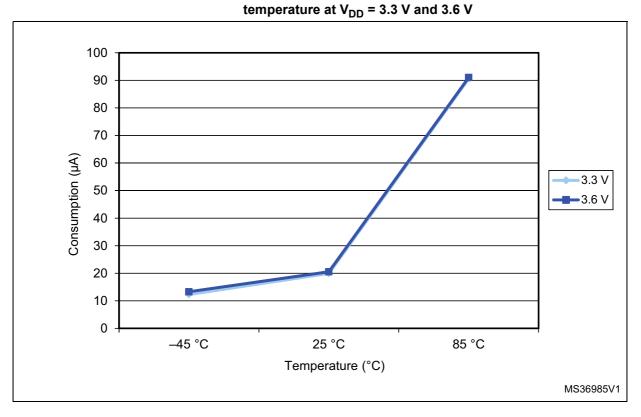

|                                | Regulator in Low-Power mode,<br>Low-speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -                                                                                                                                        | 13.5 | 14                                               | 180                     |                                          |      |

| I <sub>DD</sub>                |                                                                                                                                                | Low-speed internal RC oscillator and independent watchdog ON                                                                             | -    | 2.6                                              | 3.4                     | -                                        | μA   |

|                                | Supply current in Standby                                                                                                                      | Low-speed internal RC oscillator ON, independent watchdog OFF                                                                            | -    | 2.4                                              | 3.2                     | -                                        |      |

| mode                           | mode                                                                                                                                           | Low-speed internal RC oscillator and<br>independent watchdog OFF, low-speed<br>oscillator and RTC OFF                                    | -    | 1.7                                              | 2                       | 4                                        |      |

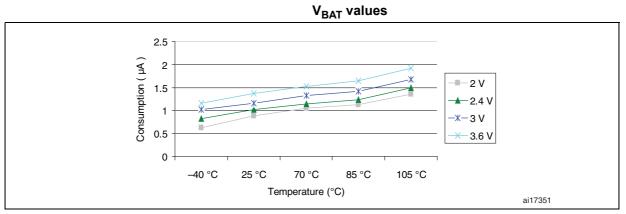

| I <sub>DD_VBA</sub><br>T       | Backup<br>domain supply<br>current                                                                                                             | Low-speed oscillator and RTC ON                                                                                                          | 0.9  | 1.1                                              | 1.4                     | 1.9                                      |      |

| Table 15. Typical and maximum current | t consumptions in Sto | n and Standby modes |

|---------------------------------------|-----------------------|---------------------|

| Table 15. Typical and maximum current | i consumptions in Sto | p and Standby modes |

1. Typical values are measured at T\_A = 25 °C.

2. Based on characterization, not rested in production.

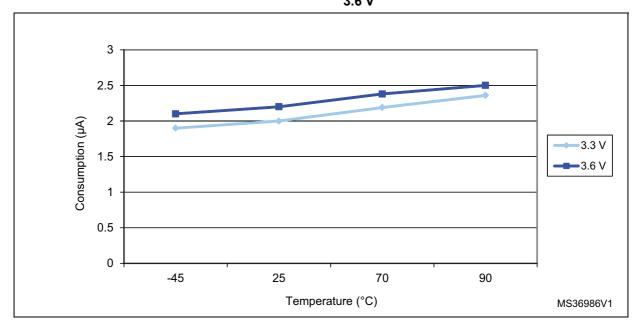

Figure 15. Typical current consumption on  $V_{\text{BAT}}$  with RTC on versus temperature at different

Figure 16. Typical current consumption in Stop mode with regulator in Run mode versus

Figure 17. Typical current consumption in Stop mode with regulator in Low-power mode versus

Figure 18. Typical current consumption in Standby mode versus temperature at V\_{DD} = 3.3 V and 3.6 V

DocID13586 Rev 17

| -                   |                                                                                               |                                                       |     |     |     |      |  |  |

|---------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|------|--|--|

| Symbol              | Parameter                                                                                     | Conditions                                            | Min | Тур | Max | Unit |  |  |

| f <sub>OSC_IN</sub> | Oscillator frequency                                                                          | -                                                     | 4   | 8   | 16  | MHz  |  |  |

| R <sub>F</sub>      | Feedback resistor                                                                             | -                                                     | -   | 200 | -   | kΩ   |  |  |

| С                   | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                 | -   | 30  | -   | pF   |  |  |

| i <sub>2</sub>      | HSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ with 30 pF load | -   | -   | 1   | mA   |  |  |

| 9 <sub>m</sub>      | Oscillator transconductance                                                                   | Startup                                               | 25  | -   | -   | mA/V |  |  |

| $t_{SU(HSE)}^{(4)}$ | Startup time                                                                                  | $V_{\text{DD}}$ is stabilized                         | -   | 2   | -   | ms   |  |  |

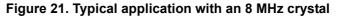

Table 21. HSE 4-16 MHz oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Based on characterization, not tested in production.

The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 21*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization

time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                               | Conditions                                                   | -                       | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>F</sub>                      | Feedback resistor                                                                                       | -                                                            | -                       | -   | 5   | -   | MΩ   |

| С                                   | Recommended load capacitance<br>versus equivalent serial<br>resistance of the crystal (R <sub>S</sub> ) | R <sub>S</sub> = 30 KΩ                                       | -                       | -   | -   | 15  | pF   |

| I <sub>2</sub>                      | LSE driving current                                                                                     | V <sub>DD</sub> = 3.3 V<br>V <sub>IN</sub> = V <sub>SS</sub> | -                       | -   | -   | 1.4 | μA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                             | -                                                            | -                       | 5   | -   | -   | µA/V |

|                                     |                                                                                                         | V <sub>DD</sub> is                                           | T <sub>A</sub> = 50 °C  | -   | 1.5 | -   |      |

|                                     |                                                                                                         |                                                              | T <sub>A</sub> = 25 °C  | -   | 2.5 | -   |      |

|                                     |                                                                                                         |                                                              | T <sub>A</sub> = 10 °C  | -   | 4   | -   |      |

| <b>↓</b> (3)                        | Startup time                                                                                            |                                                              | T <sub>A</sub> = 0 °C   | -   | 6   | -   |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                                                                                            | stabilized                                                   | T <sub>A</sub> = -10 °C | -   | 10  | -   | S    |

|                                     |                                                                                                         |                                                              | T <sub>A</sub> = -20 °C | -   | 17  | -   |      |

|                                     |                                                                                                         |                                                              | T <sub>A</sub> = -30 °C | -   | 32  | -   |      |

|                                     |                                                                                                         |                                                              | T <sub>A</sub> = -40 °C | -   | 60  | -   |      |

Table 22. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)<sup>(1) (2)</sup>

1. Based on characterization, not tested in production.

is between 2 pF and 7 pF.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3.  $t_{SU(LSE)}$  is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For CL1 and CL2 it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator. CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. *Load capacitance* CL *has the following formula:* CL = CL1 x CL2 / (CL1 + CL2) + C<sub>stray</sub> where C<sub>stray</sub> is the pin capacitance and board or trace PCB-related capacitance. Typically, it

Caution:To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended<br/>to use a resonator with a load capacitance  $CL \le 7$  pF. Never use a resonator with a load<br/>capacitance of 12.5 pF.Example:if resonator with a load capacitance of CL = 6 pF, and  $C_{stray} = 2$  pF is chosen,<br/>then CL1 = CL2 = 8 pF.

### 5.3.11 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                               | Conditions                                                    | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \ ^{\circ}C$<br>conforming to JESD22-A114          | 2     | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \ ^{\circ}C$<br>conforming to<br>ANSI/ESD STM5.3.1 | II    | 500                             | V    |

| Table 30. | ESD | absolute | maximum | ratings |

|-----------|-----|----------|---------|---------|

|-----------|-----|----------|---------|---------|

1. Based on characterization results, not tested in production.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78 IC latch-up standard.

#### Table 31. Electrical sensitivities

| Symbol | Parameter             | Conditions                           | Class      |

|--------|-----------------------|--------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +85$ °C conforming to JESD78A | II level A |

## 5.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

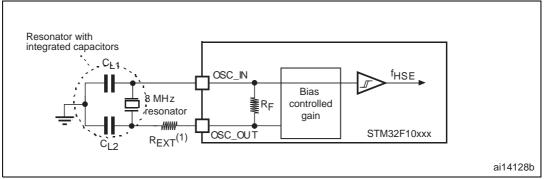

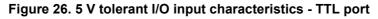

Figure 25. 5 V tolerant I/O input characteristics - CMOS port

#### **Output driving current**

The GPIOs (general-purpose inputs/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to +/-3mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 6*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 6*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                                                         | Conditions                                                 | Min                  | Max | Unit |

|--------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output Low level voltage for an I/O pin when 8 pins are sunk at the same time     | CMOS port <sup>(2)</sup> ,,<br>I <sub>IO</sub> = +8 mA,    | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output High level voltage for an I/O pin when 8 pins are sourced at the same time | $1_{O} - 40$ mA,<br>2.7 V < V <sub>DD</sub> < 3.6 V        | V <sub>DD</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time     | TTL port <sup>(2)</sup><br>I <sub>IO</sub> = +8 mA         | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time | $1_{O} - 40 \text{ mA}$<br>2.7 V < V <sub>DD</sub> < 3.6 V | 2.4                  | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time     | I <sub>IO</sub> = +20 mA <sup>(4)</sup>                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time     | I <sub>IO</sub> = +6 mA <sup>(4)</sup>                     | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> -0.4 | -   | v    |

#### Table 34. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 6* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 6 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data, not tested in production.

#### Input/output AC characteristics

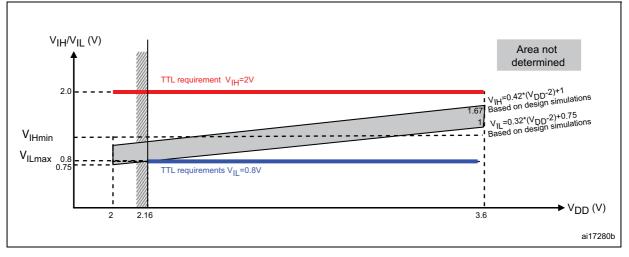

The definition and values of input/output AC characteristics are given in *Figure 27* and *Table 35*, respectively.

Unless otherwise specified, the parameters given in *Table 35* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                             | Мах                | Unit |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                 | 2                  | MHz  |

| 10                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C = 50  pE V = 2 V  to  2  GV                          | 125 <sup>(3)</sup> | ns   |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 125 <sup>(3)</sup> |      |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V               | 10                 | MHz  |

| 01                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    |                                                        | 25 <sup>(3)</sup>  |      |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 25 <sup>(3)</sup>  | ns   |

|                                            | F <sub>max(IO)out</sub> | Maximum Frequency <sup>(2)</sup>                                      | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 50                 | MHz  |

|                                            |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 30                 | MHz  |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 20                 | MHz  |

|                                            | t <sub>f(IO)out</sub>   |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   |      |

| 11                                         |                         | Output high to low level fall time                                    | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |

|                                            |                         | Output low to high level rise                                         | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   | MHz  |

|                                            | t <sub>r(IO)out</sub>   | time                                                                  | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |

| -                                          | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                                      | 10                 | ns   |

Table 35. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure 27*.

3. Guaranteed by design, not tested in production.

#### Figure 27. I/O AC characteristics definition

#### 5.3.14 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 33).

Unless otherwise specified, the parameters given in Table 36 are derived from tests performed under the ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 8.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -0.5 | -   | 0.8                  | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 2    | -   | V <sub>DD</sub> +0.5 | v    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      | -                 | -    | 200 | -                    | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 30   | 40  | 50                   | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -    | -   | 100                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | _                 | 300  | -   | -                    | ns   |

Table 36. NRST pin characteristics

1. Guaranteed by design, not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to 2. the series resistance must be minimum (~10% order).

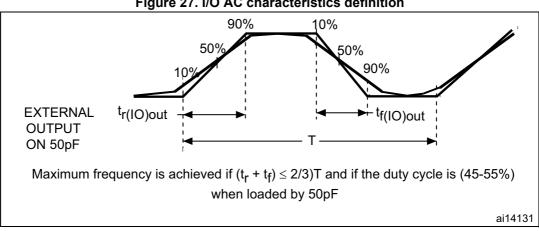

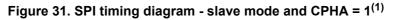

Figure 30. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

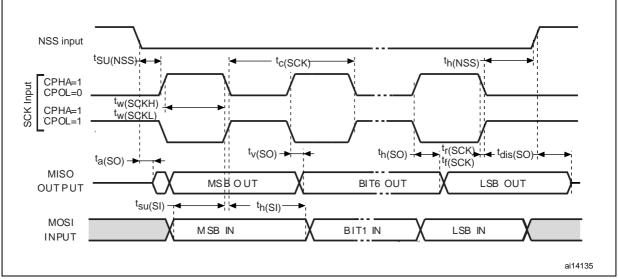

Figure 32. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

## 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 41* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 8*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                           | Parameter                                             | Conditions                                            | Min                                                                        | Тур                | Мах                | Unit               |

|----------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                                          | -                                                     | 2.4                                                                        | -                  | 3.6                | V                  |

| $V_{REF^+}$                      | Positive reference voltage                            | -                                                     | 2.4                                                                        | -                  | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the $V_{\mbox{\scriptsize REF}}$ input pin | -                                                     | -                                                                          | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                                   | -                                                     | 0.6                                                                        | -                  | 14                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                         | -                                                     | 0.05                                                                       | -                  | 1                  | MHz                |

| f (2)                            | External trigger frequency                            | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -                  | 823                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> |                                                       | -                                                     | -                                                                          | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>               | -                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground)                | -                  | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                              | See <i>Equation 1</i> and <i>Table 42</i> for details | -                                                                          | -                  | 50                 | κΩ                 |

| $R_{ADC}^{(2)}$                  | Sampling switch resistance                            | -                                                     | -                                                                          | -                  | 1                  | κΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                    | -                                                     | -                                                                          | -                  | 8                  | pF                 |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                                      | f <sub>ADC</sub> = 14 MHz                             | 5.9                                                                        |                    |                    | μs                 |

| 'CAL` ′                          |                                                       | -                                                     | 83                                                                         |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (2)             | Injection trigger conversion                          | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -                  | 0.214              | μs                 |

| 'lat` '                          | latency                                               | -                                                     | -                                                                          | -                  | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| . (2)                            | Regular trigger conversion                            | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -                  | 0.143              | μs                 |

| t <sub>latr</sub> <sup>(2)</sup> | latency                                               | -                                                     | -                                                                          | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| . (2)                            | Compling time                                         |                                                       | 0.107                                                                      | -                  | 17.1               | μs                 |

| t <sub>S</sub> <sup>(2)</sup>    | Sampling time                                         | f <sub>ADC</sub> = 14 MHz                             | 1.5                                                                        | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                         | -                                                     | 0                                                                          | 0                  | 1                  | μs                 |

|                                  | Total conversion time                                 | f <sub>ADC</sub> = 14 MHz                             | 1                                                                          | -                  | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time<br>(including sampling time)    | -                                                     | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    |                    | 1/f <sub>ADC</sub> |

1. Based on characterization results, not tested in production.

2. Guaranteed by design, not tested in production.

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 3: Pinouts and pin description for further details.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 41.

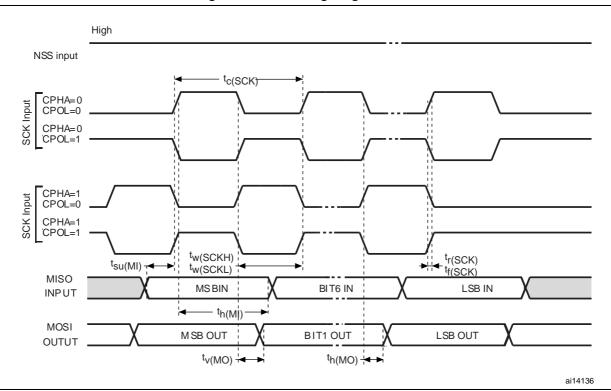

# 6.3 VFQFPN36 package information

Figure 40. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat

1. Drawing is not to scale.

| <b>•</b> • • • | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|----------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol         | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А              | 0.800       | 0.900 | 1.000 | 0.0315                | 0.0354 | 0.0394 |  |

| A1             | -           | 0.020 | 0.050 | -                     | 0.0008 | 0.0020 |  |

| A2             | -           | 0.650 | 1.000 | -                     | 0.0256 | 0.0394 |  |

| A3             | -           | 0.200 | -     | -                     | 0.0079 | -      |  |

| b              | 0.180       | 0.230 | 0.300 | 0.0071                | 0.0091 | 0.0118 |  |

| D              | 5.875       | 6.000 | 6.125 | 0.2313                | 0.2362 | 0.2411 |  |

| D2             | 1.750       | 3.700 | 4.250 | 0.0689                | 0.1457 | 0.1673 |  |

| E              | 5.875       | 6.000 | 6.125 | 0.2313                | 0.2362 | 0.2411 |  |

| E2             | 1.750       | 3.700 | 4.250 | 0.0689                | 0.1457 | 0.1673 |  |

| е              | 0.450       | 0.500 | 0.550 | 0.0177                | 0.0197 | 0.0217 |  |

| L              | 0.350       | 0.550 | 0.750 | 0.0138                | 0.0217 | 0.0295 |  |

| К              | 0.250       | -     | -     | 0.0098                | -      | -      |  |

| ddd            | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

# Table 47. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat

1. Values in inches are converted from mm and rounded to 4 decimal digits.

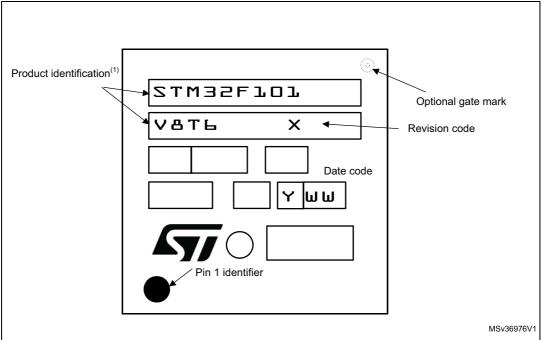

#### **Device Marking for LQFP100**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

1. Dimensions are expressed in millimeters.