#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 36MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                               |

| Number of I/O              | 80                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 16K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101vbt6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to  $\mathsf{V}_{SS}.$

## 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 2 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

## 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 10*.

| Symbol                               | Parameter                                     | Conditions                  | Min                | Тур  | Мах  | Unit |  |  |

|--------------------------------------|-----------------------------------------------|-----------------------------|--------------------|------|------|------|--|--|

|                                      |                                               | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 |      |  |  |

|                                      |                                               | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 |      |  |  |

|                                      |                                               | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 |      |  |  |

|                                      |                                               | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 |      |  |  |

|                                      |                                               | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 |      |  |  |

|                                      |                                               | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 |      |  |  |

|                                      |                                               | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 |      |  |  |

| V                                    | Programmable voltage detector level selection | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |  |  |

| V <sub>PVD</sub>                     |                                               | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 |      |  |  |

|                                      |                                               | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 |      |  |  |

|                                      |                                               | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 |      |  |  |

|                                      |                                               | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 |      |  |  |

|                                      |                                               | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  |      |  |  |

|                                      |                                               | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  | -    |  |  |

|                                      |                                               | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    |      |  |  |

|                                      |                                               | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  |      |  |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis                                | -                           | -                  | 100  | -    | mV   |  |  |

| V <sub>POR/PDR</sub>                 | Power on/power down                           | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |  |  |

|                                      | reset threshold                               | Rising edge                 | 1.84               | 1.92 | 2.0  | ]    |  |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis                                | -                           | -                  | 40   | -    | mV   |  |  |

| t <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization                           | -                           | 1.5                | 2.5  | 4.5  | ms   |  |  |

1. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

2. Guaranteed by design, not tested in production.

## 5.3.4 Embedded reference voltage

The parameters given in *Table 11* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                                | Parameter                                                     | Conditions                       | Min  | Тур  | Max                 | Unit       |

|---------------------------------------|---------------------------------------------------------------|----------------------------------|------|------|---------------------|------------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | –40 °C < T <sub>A</sub> < +85 °C | 1.16 | 1.20 | 1.24                | V          |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage |                                  | -    | 5.1  | 17.1 <sup>(2)</sup> | μs         |

| V <sub>RERINT</sub> <sup>(2)</sup>    | Internal reference voltage spread over the temperature range  | V <sub>DD</sub> = 3 V ±10 mV     | -    | -    | 10                  | mV         |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                       | -                                | -    | -    | 100                 | ppm/<br>°C |

| Table 11. I | Embedded | internal | reference | voltage |

|-------------|----------|----------|-----------|---------|

|-------------|----------|----------|-----------|---------|

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

## 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 12: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if it is explicitly mentioned

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 36 MHz)

- Prefetch in on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK/2}$ ,  $f_{PCLK2} = f_{HCLK}$

The parameters given in *Table 12* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 27* and *Table 35*, respectively.

Unless otherwise specified, the parameters given in *Table 35* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                             | Мах                | Unit |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                 | 2                  | MHz  |

| 10                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C = 50  pE V = 2 V  to  2  GV                          | 125 <sup>(3)</sup> | 20   |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 125 <sup>(3)</sup> | ns   |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V               | 10                 | MHz  |

| 01                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    |                                                        | 25 <sup>(3)</sup>  |      |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 25 <sup>(3)</sup>  | ns   |

|                                            |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 50                 | MHz  |

|                                            | F <sub>max(IO)out</sub> | Maximum Frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 30                 | MHz  |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 20                 | MHz  |

|                                            |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   |      |

| 11                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |

|                                            |                         | Output low to high level rise                                         | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   | ns   |

| t <sub>r(IO)out</sub>                      | t <sub>r(IO)out</sub>   | <sup>D)out</sup> time                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |

| -                                          | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                                      | 10                 | ns   |

Table 35. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure 27*.

3. Guaranteed by design, not tested in production.

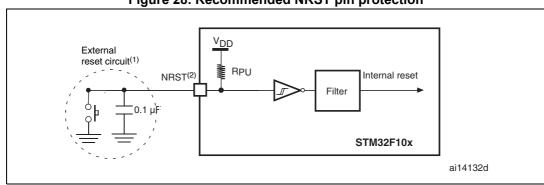

Figure 28. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

2. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 36*. Otherwise the reset will not be taken into account by the device.

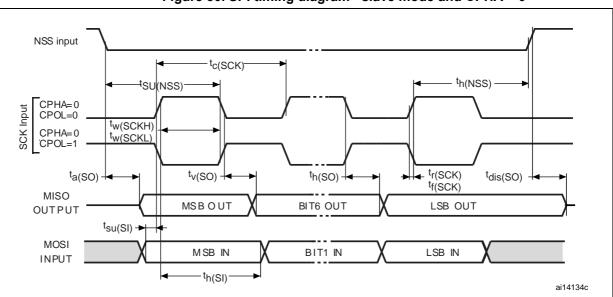

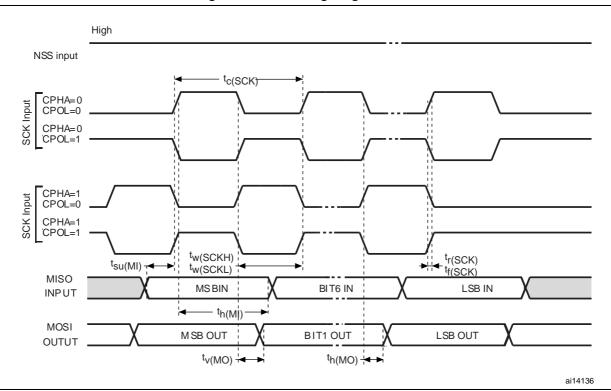

Figure 30. SPI timing diagram - slave mode and CPHA = 0

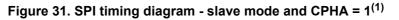

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

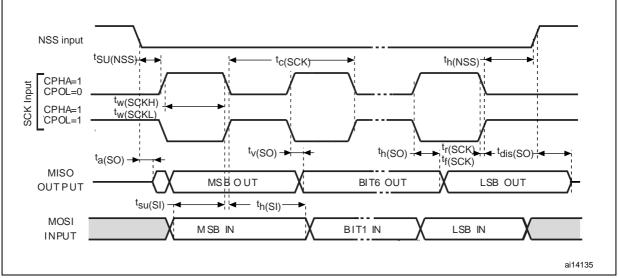

Figure 32. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

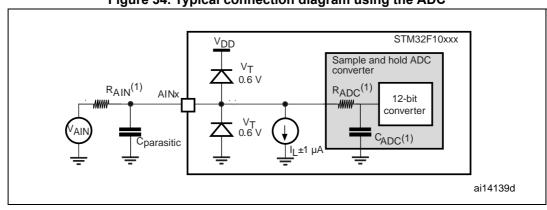

# 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 41* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 8*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                                                                              | Parameter                                             | Conditions                                            | Min                                                         | Тур                | Мах                | Unit               |

|-------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|

| V <sub>DDA</sub>                                                                    | Power supply                                          | -                                                     | 2.4                                                         | -                  | 3.6                | V                  |

| $V_{REF^+}$                                                                         | Positive reference voltage                            | -                                                     | 2.4                                                         | -                  | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                                                                   | Current on the $V_{\mbox{\scriptsize REF}}$ input pin | -                                                     | -                                                           | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                                                                    | ADC clock frequency                                   | -                                                     | 0.6                                                         | -                  | 14                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>                                                       | Sampling rate                                         | -                                                     | 0.05                                                        | -                  | 1                  | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>                                                    | External trigger frequency                            | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 823                | kHz                |

| 'TRIG` ′                                                                            |                                                       | -                                                     | -                                                           | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                                                                    | Conversion voltage range <sup>(3)</sup>               | -                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -                  | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>                                                     | External input impedance                              | See <i>Equation 1</i> and <i>Table 42</i> for details | -                                                           | -                  | 50                 | κΩ                 |

| $R_{ADC}^{(2)}$                                                                     | Sampling switch resistance                            | -                                                     | -                                                           | -                  | 1                  | кΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>                                                     | Internal sample and hold capacitor                    | -                                                     | -                                                           | -                  | 8                  | pF                 |

| t <sub>CAL</sub> <sup>(2)</sup>                                                     | Calibration time                                      | f <sub>ADC</sub> = 14 MHz                             | 5.9                                                         |                    | μs                 |                    |

| <sup>L</sup> CAL`                                                                   |                                                       | -                                                     | 83                                                          |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (2)                                                                | Injection trigger conversion                          | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 0.214              | μs                 |

| 'lat` '                                                                             | latency                                               | -                                                     | -                                                           | -                  | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| <b>•</b> (2)                                                                        | Regular trigger conversion                            | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 0.143              | μs                 |

| t <sub>latr</sub> <sup>(2)</sup>                                                    | latency                                               | -                                                     | -                                                           | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                                                                   | Compling time                                         |                                                       | 0.107                                                       | -                  | 17.1               | μs                 |

| ι <sub>S</sub> ,-,                                                                  | Sampling time                                         | f <sub>ADC</sub> = 14 MHz                             | 1.5                                                         | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup>                                                    | Power-up time                                         | -                                                     | 0                                                           | 0                  | 1                  | μs                 |

|                                                                                     |                                                       | f <sub>ADC</sub> = 14 MHz                             | 1                                                           | -                  | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> Total conversion time<br>(including sampling time) |                                                       | -                                                     | 14 to 252 (t <sub>S</sub> for sa<br>successive approx       |                    |                    | 1/f <sub>ADC</sub> |

1. Based on characterization results, not tested in production.

2. Guaranteed by design, not tested in production.

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 3: Pinouts and pin description for further details.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 41.

Figure 34. Typical connection diagram using the ADC

1. Refer to *Table 41* for the values of  $R_{AIN}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

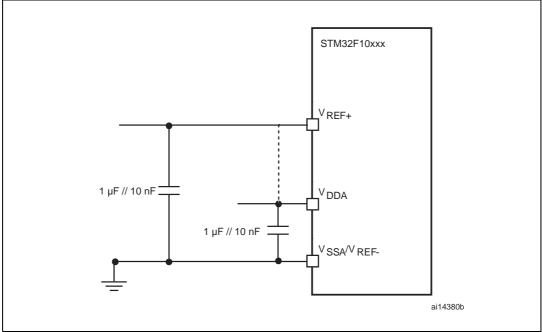

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 35* or *Figure 36*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

<sup>1.</sup>  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

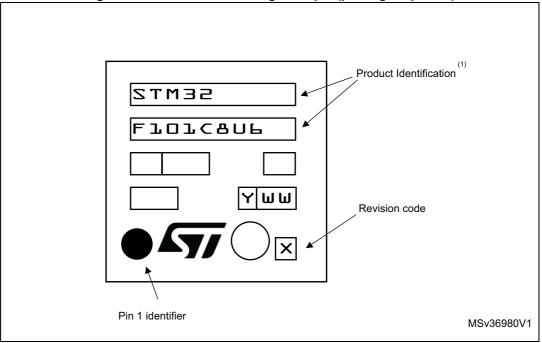

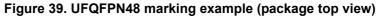

#### **Device Marking for UFQFPN48**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

#### Figure 41. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

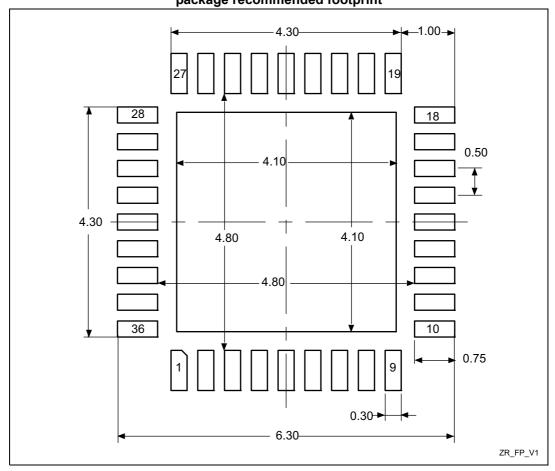

#### 6.5 LQFP64 package information

SEATING PLANE С 0.25 mm GAUGE PLANE ¥ G 7 D K D1 L1 D3 48 33 32 49 <u>A A A A A A A A A A A A A</u> b E3 Ш ш 64 17 ₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽ 16 PIN 1 IDENTIFICATION 1 ⊾e 5W\_ME\_V3

Figure 46. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |

|-------------------------------------------------------------|

| package mechanical data                                     |

| Symbol | millimeters |        |       |        | inches <sup>(1)</sup> | es <sup>(1)</sup> |  |

|--------|-------------|--------|-------|--------|-----------------------|-------------------|--|

| Symbol | Min         | Тур    | Мах   | Min    | Тур                   | Max               |  |

| A      | -           | -      | 1.600 | -      | -                     | 0.0630            |  |

| A1     | 0.050       | -      | 0.150 | 0.0020 | -                     | 0.0059            |  |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531 | 0.0551                | 0.0571            |  |

| b      | 0.170       | 0.220  | 0.270 | 0.0067 | 0.0087                | 0.0106            |  |

| с      | 0.090       | -      | 0.200 | 0.0035 | -                     | 0.0079            |  |

| D      | -           | 12.000 | -     | -      | 0.4724                | -                 |  |

| D1     | -           | 10.000 | -     | -      | 0.3937                | -                 |  |

| D3     | -           | 7.500  | -     | -      | 0.2953                | -                 |  |

| E      | -           | 12.000 | -     | -      | 0.4724                | -                 |  |

| E1     | -           | 10.000 | -     | -      | 0.3937                | -                 |  |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| ССС    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

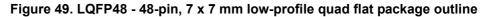

# 6.6 LQFP48 package information

SEATING PLANE С A A ŨŦŨŦŨŦŨŦĬĦŮ<del>Ÿ</del>ŨŦŨŦŨŦŨŦŎŹ ¥ 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 <u>ÅAAAAA AAAAAAA</u> 24 37 Œ b E E ш Ē ----------€ 48 13 PIN 1 IDENTIFICATION 1 12 e 5B\_ME\_V2

<sup>1.</sup> Drawing is not to scale.

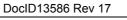

#### 6.7.2 Evaluating the maximum junction temperature for an application

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Table 52: Ordering information scheme*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature. Here, only temperature range 6 is available (-40 to 85 °C).

The following example shows how to calculate the temperature range needed for a given application, making it possible to check whether the required temperature range is compatible with the STM32F101xx junction temperature range.

#### **Example: high-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 82$  °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output mode at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>INTmax =</sub> 50 mA × 3.5 V= 175 mW

P<sub>IOmax = 20</sub> × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW

P<sub>Dmax =</sub> 175 <sub>+</sub> 272 = 447 mW

Thus: P<sub>Dmax</sub> = 447 mW

Using the values obtained in *Table 51*  $T_{Jmax}$  is calculated as follows:

For LQFP64, 45 °C/W

T<sub>Jmax</sub> = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.1 °C = 102.1 °C

This is within the junction temperature range of the STM32F101xx ( $-40 < T_J < 105 \text{ °C}$ ).

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact the nearest ST sales office.

| Date | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date |          | <ul> <li>V<sub>ESD(CDM)</sub> value added to <i>Table 30</i>: <i>ESD absolute maximum ratings</i>.</li> <li>Note added below <i>Table 10</i>: <i>Embedded reset and power control block characteristics</i>.</li> <li>Note added below <i>Table 34</i>: <i>Output voltage characteristics</i> and V<sub>OH</sub> parameter description modified.</li> <li><i>Table 41</i>: <i>ADC characteristics</i> and <i>Table 43</i>: <i>ADC accuracy - limited test conditions</i> modified.</li> <li><i>Figure 33</i>: <i>ADC accuracy characteristics</i> modified.</li> <li>Packages are ECOPACK® compliant.</li> <li>Tables modified in <i>Section 5.3.5</i>: <i>Supply current characteristics</i>.</li> <li>ADC and ANTI_TAMPER signal names modified (see <i>Table 4</i>: <i>Medium-density STM32F101xx pin definitions</i>). <i>Table 4</i>: <i>Medium-density STM32F101xx pin definitions</i>.</li> <li><i>Table 21</i>: <i>Typical current consumption in Standby mode</i>.</li> <li>V<sub>hys</sub> modified in <i>Table 33</i>: <i>I/O static characteristics</i>.</li> <li>Updated: <i>Table 28</i>: <i>EMS characteristics</i> and <i>Table 29</i>: <i>EMI characteristics</i>.</li> <li><i>t</i><sub>VDD</sub> modified in <i>Table 9</i>: <i>Operating conditions at power-up / power-down</i>.</li> <li>Typical values modified, note 2 modified and note 3 removed in <i>Table 25</i>: <i>Low-power mode wakeup timings</i>.</li> <li>Maximum current consumption <i>Table 15</i>: <i>Typical and maximum current consumptions in Stop and Standby modes</i>.</li> <li><i>On-chip peripheral current consumption on page 43</i> added.</li> <li>Package mechanical data inch values are calculated from mm and rounded to <i>4 decimal digits</i> (see <i>Section 6: Package characteristics</i>).</li> <li>V<sub>prog</sub> added to <i>Table 27: Flash memory characteristics</i>.</li> <li>T<sub>s_temp</sub> added to <i>Table 27: Flash memory characteristics</i>.</li> <li></li></ul> |

|      |          | Note 7 modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | Option byte addresses corrected in <i>Figure 8: Memory map</i> .<br>ACC <sub>HSI</sub> modified in <i>Table 23: HSI oscillator characteristics</i> .<br>t <sub>JITTER</sub> removed from <i>Table 26: PLL characteristics</i> .<br><i>Appendix A: Important notes on page 71</i> added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |          | Added: Figure 13, Figure 14, Figure 16 and Figure 18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 53. Document revision history (continued)

| Date | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date |          | <ul> <li>Document status promoted from preliminary data to datasheet. Small text changes.</li> <li>STM32F101CB part number corrected in <i>Table 1: Device summary</i>.</li> <li>Number of communication peripherals corrected for STM32F101Tx in <i>Table 2: Device features and peripheral counts (STM32F101x medium-density access line)</i> and Number of GPIOs corrected for LQFP package.</li> <li><i>Power supply schemes on page 16</i> modified.</li> <li>Main function and default alternate function modified for PC14 and PC15 in <i>Table 4: Medium-density STM32F101xx pin definitions</i>, <i>Note</i> 6 added, Remap column added.</li> <li><i>Figure 11: Power supply scheme</i> modified. V<sub>DD</sub> – V<sub>SS</sub> ratings modified and <i>Note</i> 1 modified in <i>Table 5: Voltage characteristics</i>. <i>Note</i> 1 modified in <i>Table 5: Voltage characteristics</i>. <i>Note</i> 1 modified in <i>Table 10: Embedded reset and power control block characteristics</i>.</li> <li>48 and 72 MHz frequencies removed from <i>Table</i> 12, <i>Table</i> 13 and <i>Table</i> 14. MCU 's operating conditions modified in <i>Typical current consumption on page</i> 42.</li> <li>IDD_VBAT typical value at 2.4 V modified and I<sub>DD_VBAT</sub> maximum value added in <i>Table</i> 15: <i>Typical and maximum current consumptions in Stop and Standby modes</i>. Note added in <i>Table</i> 16 on page 42 and <i>Table</i> 17 on page 43. <i>Table</i> 18: Peripheral current consumption modified.</li> <li>Figure 17: <i>Typical current consumption in Stop mode with regulator in Low-power mode versus temperature at VDD</i> = 3.3 V and 3.6 V added.</li> <li>Note removed below <i>Figure</i> 30: SPI timing diagram - slave mode and CPHA = 1(1).</li> <li><i>Figure</i> 34: <i>Typical connection diagram using the ADC</i> modified.</li> <li>t<sub>SU(HSE)</sub> and t<sub>SU(LSE)</sub> conditions modified in <i>Table</i> 27: <i>Flash memory characteristics</i>. Conditions modified in <i>Table</i> 27: <i>Elash memory characteristics</i>.</li> <li>Impedance size specified in A.4: Voltage glitch on ADC input 0 on</li> </ul> |  |

|      |          | Note removed below Figure 30: SPI timing diagram - slave mode and CPHA = 0. Note added below Figure 31: SPI timing diagram - slave mode and CPHA = 1(1).<br>Figure 34: Typical connection diagram using the ADC modified.<br>$t_{SU(HSE)}$ and $t_{SU(LSE)}$ conditions modified in Table 21 and Table 22,<br>respectively. Maximum values removed from Table 25: Low-power mode<br>wakeup timings. $t_{RET}$ conditions modified in Table 27: Flash memory<br>characteristics. Conditions modified in Table 28: EMS characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|      |          | page 71. Small text changes in <i>Table 34: Output voltage characteristics</i> .<br>Section 5.3.11: Absolute maximum ratings (electrical sensitivity) updated.<br>Details on unused pins removed from <i>General input/output characteristics</i><br>on page 55.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|      |          | Table 40: SPI characteristics updated. Notes added and $I_{Ikg}$ removed in<br>Table 41: ADC characteristics. Note added in Table 42 and Table 45.<br>Note 3 and Note 2 added below Table 43: ADC accuracy - limited test<br>conditions. Avg_Slope and V <sub>25</sub> modified in Table 45: TS characteristics.<br>$\Theta_{JA}$ value for VFQFPN36 package added in Table 51: Package thermal<br>characteristics. I2C interface characteristics on page 62 modified.<br>Order codes replaced by Section 7: Ordering information scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Dute        | Revision | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 14-Mar-2008 | 5        | <ul> <li><i>Figure 2: Clock tree on page 13</i> added.</li> <li>CRC added (see <i>CRC (cyclic redundancy check) calculation unit on page 9</i> and <i>Figure 8: Memory map on page 29</i> for address).</li> <li>Maximum T<sub>J</sub> value given in <i>Table 7: Thermal characteristics on page 33</i>.</li> <li>P<sub>D</sub>, T<sub>A</sub> and T<sub>J</sub> added, t<sub>prog</sub> values modified and t<sub>prog</sub> description clarified in <i>Table 27: Flash memory characteristics on page 51</i>.</li> <li>I<sub>DD</sub> modified in <i>Table 15: Typical and maximum current consumptions in Stop and Standby modes on page 39</i>.</li> <li>ACC<sub>HSI</sub> modified in <i>Table 23: HSI oscillator characteristics on page 49</i>, note 2 removed.</li> <li>t<sub>RET</sub> modified in <i>Table 27: Flash memory characteristics</i>.</li> <li>V<sub>NF(NRST)</sub> unit corrected in <i>Table 36: NRST pin characteristics on page 60</i>.</li> <li><i>Table 40: SPI characteristics on page 65</i> modified.</li> <li>I<sub>VREF</sub> added in <i>Table 41: ADC characteristics on page 68</i>.</li> <li><i>Table 43: ADC accuracy - limited test conditions</i> added. <i>Table 44: ADC accuracy</i> modified.</li> <li>LQFP100 package specifications updated (see <i>Section 6: Package</i>)</li> </ul> |  |

|             |          | <i>characteristics on page</i> 73).<br>Recommended LQFP100, LQFP64, LQFP48 and VFQFPN36 footprints<br>added (see <i>Figure</i> 44, <i>Figure</i> 47, <i>Figure</i> 50 and <i>Figure</i> 41).<br><i>Section</i> 6.7: <i>Thermal characteristics on page</i> 90 modified.<br><i>Appendix A: Important notes</i> removed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 21-Mar-2008 | 6        | Small text changes.In Table 27: Flash memory characteristics: $- N_{END}$ tested over the whole temperature range $- cycling conditions specified for t_{RET}$ $- t_{RET}$ min modified at $T_A = 55 ^{\circ}C$ <i>Figure 2: Clock tree</i> corrected. <i>Figure 8: Memory map</i> clarified. $V_{25}$ , Avg_Slope and $T_L$ modified in <i>Table 45: TS characteristics</i> .CRC feature removed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 22-May-2008 | 7        | Section 1: Introduction modified, Section 2.2: Full compatibility throughout the family added. CRC feature added.         IDD_VBAT removed from Table 21: Typical current consumption in Standby mode on page 42.         Values added to Table 39: SCL frequency (fPCLK1= 36 MHz, VDD_I2C = 3.3 V) on page 64.         Figure 30: SPI timing diagram - slave mode and CPHA = 0 on page 66 modified. Equation 1 corrected.         Section 6.7.2: Evaluating the maximum junction temperature for an application on page 91 added.         Axx option added to Table 52: Ordering information scheme on page 92.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Table 53. Document revision history (continued) | Table 53. | Document | revision | history | (continued) |

|-------------------------------------------------|-----------|----------|----------|---------|-------------|

|-------------------------------------------------|-----------|----------|----------|---------|-------------|

| Table 53. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 21-Jul-2008                                     | 8        | Small text changes.Power supply supervisor on page 16 modified and $V_{DDA}$ added to Table 8:General operating conditions on page 33.Capacitance modified in Figure 11: Power supply scheme on page 31.Table notes revised in Section 5: Electrical characteristics.Maximum value of $t_{RSTTEMPO}$ modified in Table 10: Embedded reset and<br>power control block characteristics on page 35.Values added to Table 15: Typical and maximum current consumptions in<br>Stop and Standby modes and Table 21: Typical current consumption in<br>Standby mode removed.f_HSE_extf_HSE_ext modified in Table 19: High-speed external user clock<br>characteristics on page 45.f_HCLKcorrected in Table 28: EMS characteristics.Minimum SDA and SCL fall time value for Fast mode removed from<br>Table 38: I2C characteristics on page 63, note 1 modified.t_h(NSS)modified in Table 40: SPI characteristics on page 65 and<br>Figure 30: SPI timing diagram - slave mode and CPHA = 0 on page 66.C_{ADC}C_ADCmodified in Table 43: ADC caccuracy - limited test conditions and<br>Table 44: ADC accuracy.Typical T_s_tempvalue removed from Table 45: TS characteristics on<br>page 72.LQFP48 package specifications updated (see Table 50, Table 49 and<br>Table 50).Axx option removed from Table 52: Ordering information scheme on<br>page 92. |  |  |  |

| 24-Jul-2008                                     | 9        | First page modified: "Up to 2 x I <sup>2</sup> C interfaces" instead of "1 x I <sup>2</sup> C interface"<br>STM32F101xx devices with 32 Kbyte Flash memory capacity removed,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 23-Sep-2008                                     | 10       | Shinszi fortx devices with 32 kbyte hash memory capacity removed,<br>document updated accordingly.<br>Section 2.2: Full compatibility throughout the family on page 14 updated.<br>Notes modified in Table 4: Medium-density STM32F101xx pin definitions<br>on page 24.<br>Note 2 modified below Table 5: Voltage characteristics on page 32,<br>$ \Delta V_{DDx} $ min and $ \Delta V_{DDx} $ min removed.<br>Note 2 added to Table 8: General operating conditions on page 33.<br>Measurement conditions specified in Section 5.3.5: Supply current<br>characteristics on page 36.<br>$I_{DD}$ in standby mode at 85 °C modified in Table 15: Typical and maximum<br>current consumptions in Stop and Standby modes on page 39.<br>General input/output characteristics on page 55 modified.<br>Note added below Table 52: Ordering information scheme.<br>Section 7.1: Future family enhancements removed. Small text changes.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |