Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3865axi-056 |

## **PRELIMINARY**

## PSoC® 3: CY8C38 Family Datasheet

For more details on the peripherals see the "Example Peripherals" section on page 35 of this datasheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 34 of this datasheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 0.1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

- Digital filter block (DFB)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±2 LSB

- DNL less than ±1 LSB

- SINAD better than 84 dB in 16-bit mode

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors. The output of the ADC can optionally feed the programmable DFB through the DMA without CPU intervention. You can configure the DFB to perform IIR and FIR digital filters and several user-defined custom functions. The DFB can implement filters with up to 64 taps. It can perform a 48-bit multiply-accumulate (MAC) operation in one clock cycle.

Four high-speed voltage or current DACs support 8-bit output signals at an update rate of up to 8 Msps. They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths. In addition to the ADC, DACs, and DFB, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- □ Programmable gain amplifiers

- Mixers

- Other similar analog components

See the "Analog Subsystem" section on page 46 of this datasheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 67 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after POR.

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the Vddio pins. Every GPIO has analog I/O, LCD drive<sup>[4]</sup>, CapSense<sup>[5]</sup>, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow VOH to be set independently of Vddio when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 28 of this datasheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The internal main oscillator (IMO) is the master clock base for the system, and has 1-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 62 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs. The device provides a PLL to generate system clock frequencies up to 67 MHz from the IMO, external crystal, or external reference clock.

#### Notes

- 4. This feature on select devices only. See Ordering Information on page 105 for details.

- 5. GPIOs with opamp outputs are not recommended for use with CapSense.

## **PRELIMINARY**

# PSoC® 3: CY8C38 Family Datasheet

### 4.3.1 Instruction Set Summary

#### 4.3.1.1 Arithmetic Instructions

Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions. Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations. Table 4-1 lists the different arithmetic instructions.

Table 4-1. Arithmetic Instructions

| Mnemonic      | Description                                          | Bytes | Cycles |

|---------------|------------------------------------------------------|-------|--------|

| ADD A,Rn      | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct  | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri     | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data   | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn     | Add register to accumulator with carry               | 1     | 1      |

| ADDC A,Direct | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri    | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data  | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn     | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A,Direct | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri    | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data  | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A         | Increment accumulator                                | 1     | 1      |

| INC Rn        | Increment register                                   | 1     | 2      |

| INC Direct    | Increment direct byte                                | 2     | 3      |

| INC @Ri       | Increment indirect RAM                               | 1     | 3      |

| DEC A         | Decrement accumulator                                | 1     | 1      |

| DEC Rn        | Decrement register                                   | 1     | 2      |

| DEC Direct    | Decrement direct byte                                | 2     | 3      |

| DEC @Ri       | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR      | Increment data pointer                               | 1     | 1      |

| MUL           | Multiply accumulator and B                           | 1     | 2      |

| DIV           | Divide accumulator by B                              | 1     | 6      |

| DAA           | Decimal adjust accumulator                           | 1     | 3      |

### 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

Table 4-2. Logical Instructions

|     | Mnemonic Description |                                   | Bytes | Cycles |

|-----|----------------------|-----------------------------------|-------|--------|

| ANL | A,Rn                 | AND register to accumulator       | 1     | 1      |

| ANL | A,Direct             | AND direct byte to accumulator    | 2     | 2      |

| ANL | A,@Ri                | AND indirect RAM to accumulator   | 1     | 2      |

| ANL | A,#data              | AND immediate data to accumulator | 2     | 2      |

| ANL | Direct, A            | AND accumulator to direct byte    | 2     | 3      |

Document Number: 001-11729 Rev. \*Q

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal.

#### 6.1.2 External Oscillators

## 6.1.2.1 MHz External Crystal Oscillator

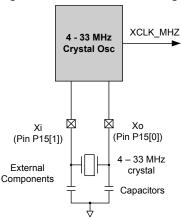

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 33 MHz. When used in conjunction with the PLL, it can generate CPU and system clocks up to the device's maximum frequency (see PLL). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

Figure 6-2. MHzECO Block Diagram

#### 6.1.2.2 32.768-kHz ECO

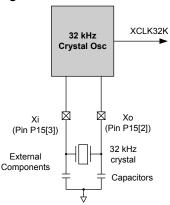

The 32.768-kHz external crystal oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768-kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the RTC. The RTC uses a 1-second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

Figure 6-3. 32kHzECO Block Diagram

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

#### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The system clock is used to select and supply the fastest clock in the system for general system clock requirements and clock synchronization of the PSoC device.

- Bus clock 16-bit divider uses the system clock to generate the system's bus clock used for data transfers. Bus clock is the source clock for the CPU clock divider.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the UDBs and fixed function timer/counter/PWMs can also generate clocks.

- Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as ADC and mixers. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise.

Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50 percent duty cycle clocks, system clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

### 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency can be generated from different sources, including DSI clock at 48 MHz or doubled value of 24 MHz from internal oscillator, DSI signal, or crystal oscillator.

voltage. In standby mode, most boost functions are disabled, thus reducing power consumption of the boost circuit. The converter can be configured to provide low-power, low-current regulation in the standby mode. The external 32-kHz crystal can be used to generate inductor boost pulses on the rising and falling edge of the clock when the output voltage is less than the programmed value. This is called automatic thump mode (ATM).

The boost typically draws 200  $\mu A$  in active mode and 12  $\mu A$  in standby mode. The boost operating modes must be used in conjunction with chip power modes to minimize the total chip power consumption. Table 6-4 lists the boost power modes available in different chip power modes.

Table 6-4. Chip and Boost Power Modes Compatibility

| Chip Power Modes      | Boost Power Modes                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip – Active mode    | Boost can be operated in either active or standby mode.                                                                                                            |

| Chip – Sleep mode     | Boost can be operated in either active or standby mode. However, it is recommended to operate boost in standby mode for low-power consumption                      |

| Chip – Hibernate mode | Boost can only be operated in active mode. However, it is recommended not to use boost in chip hibernate mode due to high current consumption in boost active mode |

If the boost converter is not used in a given application, tie the Vbat, Vssb, and Vboost pins to ground and leave the Ind pin unconnected.

#### 6.3 Reset

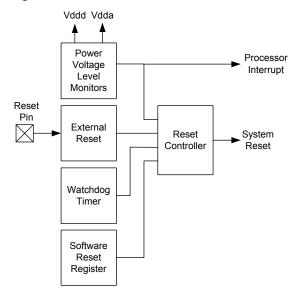

CY8C38 has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring The analog and digital power voltages, Vdda, Vddd, Vcca, and Vccd are monitored in several different modes during power up, active mode, and sleep mode (buzzing). If any of the voltages goes outside predetermined ranges then a reset is generated. The monitors are programmable to generate an interrupt to the processor under certain conditions before reaching the reset thresholds.

- External The device <u>can</u> be reset fro<u>m an external</u> source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull-up to Vddio1. Vddd, Vdda, and Vddio1 must all have voltage applied before the part comes out of reset.

- Watchdog timer A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset.

- Software The device can be reset under program control.

Figure 6-7. Resets

The term **device reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register holds the source of the most recent reset or power voltage monitoring interrupt. The program may examine this register to detect and report exception conditions. This register is cleared after a power-on reset.

#### 6.3.1 Reset Sources

### 6.3.1.1 Power Voltage Level Monitors

#### ■ IPOR – Initial power-on reset

At initial power on, IPOR monitors the power voltages  $V_{DDD}$  and  $V_{DDA}$ , both directly at the pins and at the outputs of the corresponding internal regulators. The trip level is not precise. It is set to approximately 1 volt, which is below the lowest specified operating voltage but high enough for the internal circuits to be reset and to hold their reset state. The monitor generates a reset pulse that is at least 100 ns wide. It may be much wider if one or more of the voltages ramps up slowly.

To save power the IPOR circuit is disabled when the internal digital supply is stable. Voltage supervision is then handed off to the precise low voltage reset (PRES) circuit. When the voltage is high enough for PRES to release, the IMO starts.

#### ■ PRES – Precise low voltage reset

This circuit monitors the outputs of the analog and digital internal regulators after power up. The regulator outputs are compared to a precise reference voltage. The response to a PRES trip is identical to an IPOR reset.

In normal operating mode, the program cannot disable the digital PRES circuit. The analog regulator can be disabled, which also disables the analog portion of the PRES. The PRES circuit is disabled automatically during sleep and hibernate modes, with one exception: During sleep mode the regulators are periodically activated (buzzed) to provide supervisory services and to reduce wakeup time. At these times the PRES circuit is also buzzed to allow periodic voltage monitoring.

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt

Interrupt circuits are available to detect when Vdda and Vddd go outside a voltage range. For AHVI, Vdda is compared to a fixed trip level. For ALVI and DLVI, Vdda and Vddd are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply           | Normal<br>Voltage<br>Range | Available Trip<br>Settings               | Accuracy |

|-----------|------------------|----------------------------|------------------------------------------|----------|

| DLVI      | V <sub>DDD</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| ALVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| AHVI      | $V_{DDA}$        | 1.71 V-5.5 V               | 5.75 V                                   | ±2%      |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

#### 6.3.1.2 Other Reset Sources

#### ■ XRES – External reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

#### ■ SRFS – Software reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

#### ■ DRES – Digital logic reset

A logic signal can be routed from the UDBs or other digital peripheral source through the DSI to the Configurable XRES pin, P1[2], to generate a hardware-controlled reset. The pin must be placed in XRES mode. The response to a DRES is the same as after an IPOR reset.

#### ■ WRES – Watchdog timer reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

#### Note

14. GPIOs with opamp outputs are not recommended for use with CapSense.

#### 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the Vddio pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[14]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of V<sub>DDA</sub> and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- □ Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- □ Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[14]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating  $V_{DD}$ )

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- □ Highest drive strength for general purpose use

- Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- □ Digital output (CMOS) drive mode

- □ Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

## **PRELIMINARY**

## PSoC® 3: CY8C38 Family Datasheet

### 7.1 Example Peripherals

The flexibility of the CY8C38 family's UDBs and analog blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog, however, users may also create their own custom components using PSoC Creator. Using PSoC Creator, users may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the datasheet, and the list is always growing. An example of a component available for use in CY8C38 family, but, not explicitly called out in this datasheet is the UART component.

#### 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- □ I<sup>2</sup>C

- □ UART

- □ SPI

- Functions

- EMIF

- □ PWMs

- □ Timers

- Counters

- Logic

- □ NOT

- □ OR

- XOR

- AND

## 7.1.2 Example Analog Components

The following is a sample of the analog components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Amplifiers

- □ TIA

- □ PGA

- opamp

- ADC

- Delta-sigma

- DACs

- Current

- Voltage

- □ PWM

- Comparators

- Mixers

#### 7.1.3 Example System Function Components

The following is a sample of the system function components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, DFB taps, SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- CapSense

- LCD drive

- LCD control

- Filters

#### 7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

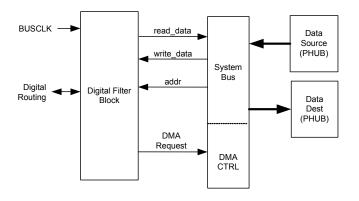

Figure 7-22. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

## 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

DAC DAC DelSig ADC Precision DAC Ν N Α L SC/CT Block SC/CT Block 0 ō GPIO GPIO G G Port Port g M SC/CT Block SC/CT Block R R 0 0 U U Т Comparators Ν Ν CMF CMP CMP CMP G CapSense Subsystem Config & Analog Interface **PHUB** CPU Registers DSI Clock Decimator

Figure 8-1. Analog Subsystem Block Diagram

### PRELIMINARY

## PSoC® 3: CY8C38 Family Datasheet

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to configure the various analog blocks to perform application specific functions (PGA, transimpedance amplifier, voltage DAC, current DAC, and so on). The tool also generates API interface libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

## 8.1 Analog Routing

The CY8C38 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

#### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

#### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C38 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C38, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2 on page 48.

Vcca Vssa AMUXBUSI AMUXBUSR AGR[4] AGL[4] AGL[5] AGL[7] 3210 76543210 ExVrefR P0[7] COMPARATOR \*P15[1] GPXT \*P15[0] out CAPSENSE out ref refbuff refbuff in \* Vccd P4[7] \* Vssd Vccd \* Vddd Vssd USB IO \* P15[7] USB IO \* DAC1 VIDAC P15[6] DAC2 DAC3 DSM DSM refs P5[5] GPIO FxVrefR FxVrefl AMUXBUSL 01234567 0123 ANALOG ANALOG GLOBALS BUS 3210 76543210 ANALOG ANALOG BUS GLOBALS Vddio2\* AGL[3] AGR[3] AGL[2] AGR[2] AGL[1] AGR[1]

AGL[0] AGR[0]

AMUXBUSL AMUXBUS Mux Group Vddio1\* Switch Group Connection

Vssd

\* Denotes pins on all packages

LCD signals are not shown.

Vssb

Figure 8-2. CY8C38 Analog Interconnect

Switch Resistance

Small (~870 Ohms)

Large ( ~200 Ohms)

Rev #51

2-April-2010

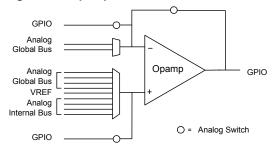

Figure 8-7. Opamp

The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or internal signals.

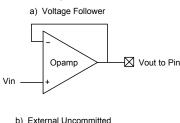

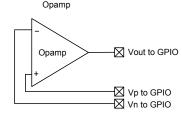

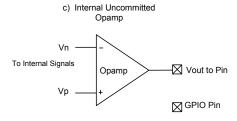

See Figure 8-8. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

Figure 8-8. Opamp Configurations

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

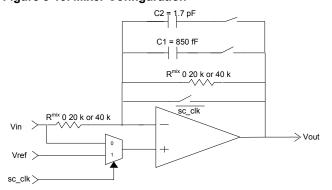

## 8.5 Programmable SC/CT Blocks

The CY8C38 family of devices contains up to four switched capacitor/continuous time (SC/CT) blocks in a device. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters such as gain, amplifier polarity, V<sub>REF</sub> connection, and so on.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

The opamp and resistor array is programmable to perform various analog functions including

- Naked operational amplifier Continuous mode

- Unity-gain buffer Continuous mode

- PGA Continuous mode

- Transimpedance amplifier (TIA) Continuous mode

- Up/down mixer Continuous mode

- Sample and hold mixer (NRZ S/H) Switched cap mode

- First order analog to digital modulator Switched cap mode

### 8.5.1 Naked Opamp

The Naked Opamp presents both inputs and the output for connection to internal or external signals. The opamp has a unity gain bandwidth greater than 6.0 MHz and output drive current up to 650  $\mu$ A. This is sufficient for buffering internal signals (such as DAC outputs) and driving external loads greater than 7.5 kohms.

### 8.5.2 Unity Gain

The Unity Gain buffer is a Naked Opamp with the output directly connected to the inverting input for a gain of 1.00. It has a –3 dB bandwidth greater than 6.0 MHz.

### 8.5.3 PGA

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-9. The schematic in Figure 8-9 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

I source Range 1x,8x,64x Vout Reference Scaler lout Source I<sub>sink</sub> Range 1x.8x.64x

Figure 8-12. DAC Block Diagram

#### 8.9.1 Current DAC

The current DAC (IDAC) can be configured for the ranges 0 to  $32 \mu A$ , 0 to 256  $\mu A$ , and 0 to 2.048 mÅ. The IDAC can be configured to source or sink current.

#### 8.9.2 Voltage DAC

For the voltage DAC (VDAC), the current DAC output is routed through resistors. The two ranges available for the VDAC are 0 to 1.024 V and 0 to 4.096 V. In voltage mode any load connected to the output of a DAC should be purely capacitive (the output of the VDAC is not buffered).

## 8.10 Up/Down Mixer

In continuous time mode, the SC/CT block components are used to build an up or down mixer. Any mixing application contains an input signal frequency and a local oscillator frequency. The polarity of the clock, Fclk, switches the amplifier between inverting or noninverting gain. The output is the product of the input and the switching function from the local oscillator, with frequency components at the local oscillator plus and minus the signal frequency (Fclk + Fin and Fclk – Fin) and reduced-level frequency components at odd integer multiples of the local oscillator frequency. The local oscillator frequency is provided by the selected clock source for the mixer.

Continuous time up and down mixing works for applications with input signals and local oscillator frequencies up to 1 MHz.

Figure 8-13. Mixer Configuration

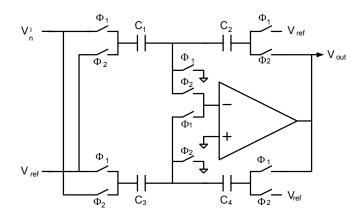

### 8.11 Sample and Hold

The main application for a sample and hold, is to hold a value stable while an ADC is performing a conversion. Some applications require multiple signals to be sampled simultaneously, such as for power calculations (V and I).

Figure 8-14. Sample and Hold Topology  $(\Phi 1 \text{ and } \Phi 2 \text{ are opposite phases of a clock})$

Table 11-3. AC Specifications [24]

| Parameter              | Description                                                                                                                    | Conditions                                                                                                                                   | Min | Тур | Max | Units |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

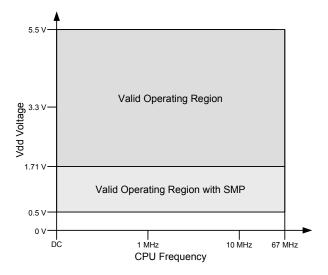

| F <sub>CPU</sub>       | CPU frequency                                                                                                                  | 1.71 V ≤ V <sub>DDD</sub> ≤ 5.5 V                                                                                                            | DC  | _   | 67  | MHz   |

| F <sub>BUSCLK</sub>    | Bus frequency                                                                                                                  | 1.71 V ≤ V <sub>DDD</sub> ≤ 5.5 V                                                                                                            | DC  | _   | 67  | MHz   |

| Svdd                   | V <sub>DD</sub> ramp rate                                                                                                      |                                                                                                                                              | _   | _   | 1   | V/ns  |

| T <sub>IO_INIT</sub>   | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ IPOR to I/O ports set to their reset states |                                                                                                                                              | -   | -   | 10  | μs    |

| T <sub>STARTUP</sub>   | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ PRES to CPU executing code at reset vector  | V <sub>CCA</sub> /V <sub>DDA</sub> = regulated from<br>V <sub>DDA</sub> /V <sub>DDD</sub> , no PLL used, fast IMO<br>boot mode (48 MHz typ.) | -   | -   | 33  | μs    |

|                        |                                                                                                                                | $V_{CCA}/V_{CCD}$ = regulated from $V_{DDA}/V_{DDD}$ , no PLL used, slow IMO boot mode (12 MHz typ.)                                         | -   | -   | 66  | μs    |

| T <sub>SLEEP</sub>     | Wakeup from sleep mode –<br>Application of non-LVD interrupt to<br>beginning of execution of next CPU<br>instruction           |                                                                                                                                              | -   | -   | 15  | μs    |

| T <sub>HIBERNATE</sub> | Wakeup from hibernate mode –<br>Application of external interrupt to<br>beginning of execution of next CPU<br>instruction      |                                                                                                                                              | -   | ı   | 100 | μs    |

Figure 11-1.  $F_{CPU}$  vs.  $V_{DD}$

24. Based on device characterization (Not production tested).

Table 11-19. Opamp AC Specifications

| Parameter      | Description            | Conditions                                | Min | Тур | Max | Units     |

|----------------|------------------------|-------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 200 pF load         | 1   | _   | _   | MHz       |

|                |                        | Power mode = low, 200 pF load             | 2   | _   | _   | MHz       |

|                |                        | Power mode = medium, 200 pF load          | 1   | _   | _   | MHz       |

|                |                        | Power mode = high, 200 pF load            | 3   | _   | -   | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = low, 200 pF load             | 1.1 | _   | _   | V/µs      |

|                |                        | Power mode = medium, 200 pF load          | 0.9 | _   | _   | V/µs      |

|                |                        | Power mode = high, 200 pF load            | 3   | _   | _   | V/µs      |

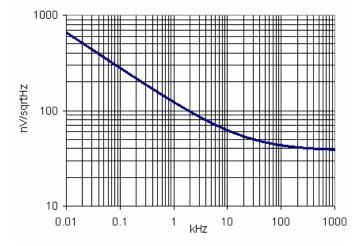

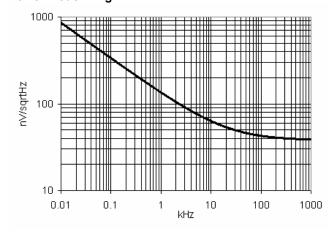

| e <sub>n</sub> | Input noise density    | Power mode = high, Vdda = 5 V, at 100 kHz | ı   | 45  | _   | nV/sqrtHz |

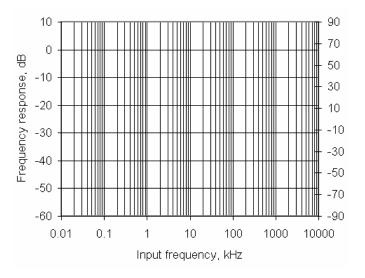

Figure 11-10. Open Loop Gain and Phase vs Frequency and Temperature, Power Mode = High, CI = 15 Pf, Vdda = 5V

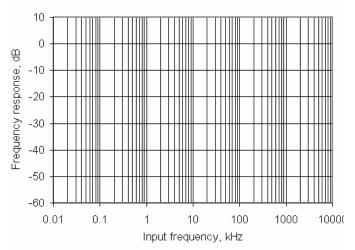

Figure 11-11. Opamp Closed Loop Frequency Response, Gain = 1, Vdda = 5V

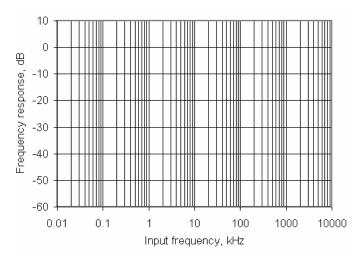

Figure 11-12. Opamp Closed Loop Frequency Response, Gain = 10, Vdda = 5V

Figure 11-14. Opamp Noise vs Frequency, Power Mode = High, Vdda = 5V

Figure 11-13. Opamp test Circuit for Gain = 10

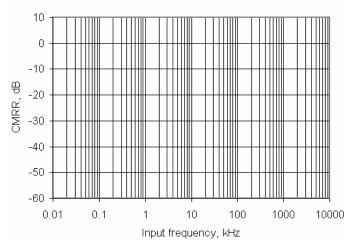

Figure 11-15. Opamp CMRR vs Frequency

## Table 11-20. 20-bit Delta-sigma ADC DC Specifications (continued)

| Parameter          | Description                                                                                       | Conditions           | Min | Тур | Max  | Units |  |  |

|--------------------|---------------------------------------------------------------------------------------------------|----------------------|-----|-----|------|-------|--|--|

| Vextref            | ADC external reference input voltage, see also internal reference in Voltage Reference on page 80 | Pins P0[3], P3[2]    | 0.9 | _   | 1.3  | V     |  |  |

| Current Co         | Current Consumption                                                                               |                      |     |     |      |       |  |  |

| I <sub>DD_20</sub> | Current consumption, 20 bit <sup>[35]</sup>                                                       | 187 sps, unbuffered  | _   | _   | 1.25 | mA    |  |  |

| I <sub>DD_16</sub> | Current consumption, 16 bit <sup>[35]</sup>                                                       | 48 ksps, unbuffered  | _   | _   | 1.2  | mA    |  |  |

| I <sub>DD_12</sub> | Current consumption, 12 bit <sup>[35]</sup>                                                       | 192 ksps, unbuffered | _   | _   | 1.4  | mA    |  |  |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[35]</sup>                                                        |                      | 1   | _   | 2.5  | mA    |  |  |

Table 11-21. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | _   | _   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[35]</sup>                         | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V | -   | -   | 0.0032 | %       |

| 20-Bit Resol | ution Mode                                                        |                                              |     | •   |        | •       |

| SR20         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 7.8 | _   | 187    | sps     |

| BW20         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 40  | _      | Hz      |

| 16-Bit Resol | ution Mode                                                        |                                              |     | •   |        | •       |

| SR16         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 2   | _   | 48     | ksps    |

| BW16         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 11  | _      | kHz     |

| SINAD16int   | Signal to noise ratio, 16-bit, internal reference <sup>[35]</sup> | Range = ±1.024V, unbuffered                  | 81  | -   | -      | dB      |

| SINAD16ext   | Signal to noise ratio, 16-bit, external reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 84  | -   | _      | dB      |

| 12-Bit Resol | ution Mode                                                        |                                              |     | •   |        | •       |

| SR12         | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | _   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 44  | _      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         |                                              |     | •   |        | •       |

| SR8          | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | _   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 88  | _      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[35]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | _   | _      | dB      |

#### Notes

35. Based on device characterization (Not production tested).

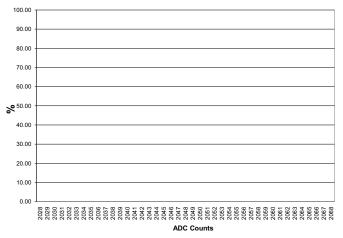

Figure 11-19. Delta-sigma ADC Noise Histogram, 1000 Samples, 20-Bit, 187 sps, Ext Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

Figure 11-21. Delta-sigma ADC Noise Histogram, 1000 samples, 16-bit, 48 ksps, Int Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

Figure 11-20. Delta-sigma ADC Noise Histogram, 1000 samples, 16-bit, 48 ksps, Ext Ref,  $V_{IN} = V_{REF}/2$ , Range = ±1.024 V

Figure 11-22. Delta-sigma ADC Noise Histogram, 1000 samples, 12-bit, 192 ksps, Int Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

Table 11-23. Delta-sigma ADC RMS Noise vs. Input Range and Sample Rate, 20-bit, External Reference

| RMS Noise,       |                       |                           |                        | Input Volta               | age Range         |                      |                      |                      |                       |

|------------------|-----------------------|---------------------------|------------------------|---------------------------|-------------------|----------------------|----------------------|----------------------|-----------------------|

| Counts           |                       | Single-Ended              |                        |                           | Differential      |                      |                      |                      |                       |

| Sample rate, sps | 0 to V <sub>REF</sub> | 0 to V <sub>REF</sub> × 2 | $V_{SSA}$ to $V_{DDA}$ | 0 to V <sub>REF</sub> × 6 | ±V <sub>REF</sub> | ±V <sub>REF</sub> /2 | ±V <sub>REF</sub> /4 | ±V <sub>REF</sub> /8 | ±V <sub>REF</sub> /16 |

| 2.8              |                       |                           |                        |                           |                   |                      |                      |                      |                       |

| 5.6              |                       |                           |                        |                           |                   |                      |                      |                      |                       |

| 11.3             |                       |                           |                        |                           |                   |                      |                      |                      |                       |

| 22.5             |                       |                           |                        |                           |                   |                      |                      |                      |                       |

| 45               |                       |                           |                        |                           |                   |                      |                      |                      |                       |

| 90               |                       |                           |                        |                           |                   |                      |                      |                      |                       |

| 187.5            |                       |                           |                        |                           |                   |                      |                      |                      |                       |

Table 11-38. PGA AC Specifications

| Parameter      | Description         | Conditions                                                     | Min | Тур | Max | Units     |

|----------------|---------------------|----------------------------------------------------------------|-----|-----|-----|-----------|

| BW1            | -3 dB bandwidth     | Power mode = high,<br>gain = 1, input = 100 mV<br>peak-to-peak | 6.7 | 8   | -   | MHz       |

| SR1            | Slew rate           | Power mode = high,<br>gain = 1, 20% to 80%                     | 3   | _   | -   | V/µs      |

| e <sub>n</sub> | Input noise density | Power mode = high,<br>Vdda = 5 V, at 100 kHz                   | -   | 43  | ı   | nV/sqrtHz |

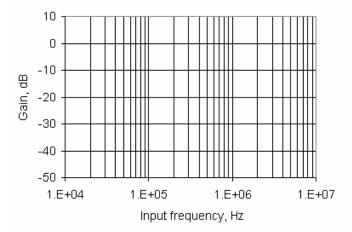

Figure 11-44. Gain vs. Frequency, at Different Gain Settings, Vdda = 3.3 V, Power Mode = High

Figure 11-46. Noise vs. Frequency, Vdda = 5 V, Power Mode = High

## 11.5.11 Temperature Sensor

Table 11-39. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: -40 °C to +85 °C | 1   | ±5  | _   | °C    |

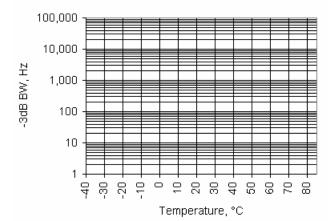

Figure 11-45. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High

## 13. Packaging

**Table 13-1. Package Characteristics**

| Parameter      | Description                                                                      | Conditions | Min | Тур   | Max | Units   |

|----------------|----------------------------------------------------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature                                                    |            | -40 | 25.00 | 85  | °C      |

| T <sub>J</sub> | Operating junction temperature                                                   |            | -40 | -     | 100 | °C      |

| Tja            | Package θJA (48-pin SSOP)                                                        |            | _   | 45.16 | _   | °C/Watt |

| Tja            | Package θJA (48-pin QFN)                                                         |            | _   | 15.94 | 1   | °C/Watt |

| Tja            | Package θJA (68-pin QFN)                                                         |            | _   | 11.72 | _   | °C/Watt |

| Tja            | Package θJA (100-pin TQFP)                                                       |            | _   | 30.52 | _   | °C/Watt |

| Tjc            | Package θJC (48-pin SSOP)                                                        |            | _   | 27.84 | _   | °C/Watt |

| Tjc            | Package θJC (48-pin QFN)                                                         |            | _   | 7.05  | _   | °C/Watt |

| Tjc            | Package θJC (68-pin QFN)                                                         |            | _   | 6.32  | _   | °C/Watt |

| Tjc            | Package θJC (100-pin TQFP)                                                       |            | _   | 9.04  | _   | °C/Watt |

|                | Pb-free assemblies (20s to 40s) –<br>Sn-Ag-Cu solder paste reflow<br>temperature |            | 235 | _     | 245 | °C      |

|                | Pb-free assemblies (20s to 40s) – Sn-Pb solder paste reflow temperature          |            | 205 | _     | 220 | °C      |

Table 13-2. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 1 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

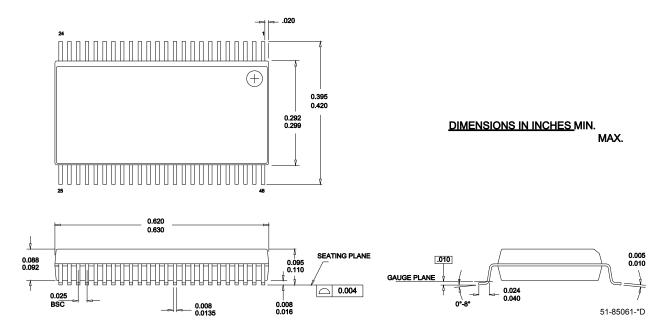

Figure 13-1. 48-pin (300 mil) SSOP Package Outline

## 17. Revision History

| Rev. | ECN No. | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 571504  | See ECN            | HMT                | New datasheet for new device Part Number family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *A   | 754416  | See ECN            | HMT                | Prepare Preliminary for PR1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *B   | 2253366 | See ECN            | DSG                | Prepare Preliminary2 for PR3total rewrite.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *C   | 2350209 | See ECN            | DSG                | Minor change: Added "Confidential" watermark. Corrected typo on 68QFN pinout: pin 13 XREF to XRES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| *D   | 2481747 | See ECN            | SFV                | Changed part numbers and datasheet title.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *E   | 2521877 | See ECN            | DSG                | Prelim3 release–extensive spec, writing, and formatting changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *F   | 2660161 | 02/16/09           | GDK                | Reorganized content to be consistent with the TRM. Added Xdata Space Acces SFRs and DAC sections. Updated Boost Converter section and Conversion Signals section. Classified Ordering Information according to CPU speed; added information on security features and ROHS compliance Added a section on XRES Specifications under Electrical Specification. Updated Analog Subsystem and CY8C35/55 Architecture block diagrams. Updated Electrical Specifications. Renamed CyDesigner as PSoC Creator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *G   | 2712468 | 05/29/09           | MKEA               | Updates to Electrical Specifications. Added Analog Routing section Updates to Ordering Information table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *H   | 2758970 | 09/02/09           | MKEA               | Updated Part Numbering Conventions. Added Section 11.7.5 (EMIF Figures and Tables). Updated GPIO and SIO AC specifications. Updated XRES Pin Description and Xdata Address Map specifications. Updated DFB and Comparator specifications. Updated PHUB features section and RTC in slee mode. Updated IDAC and VDAC DC and Analog Global specifications Updated USBIO AC and Delta Sigma ADC specifications. Updated PPOR ar Voltage Monitors DC specifications. Updated Drive Mode diagram Added 48-QFN Information. Updated other electrical specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *    | 2824546 | 12/09/09           | MKEA               | Updated I2C section to reflect 1 Mbps. Updated Table 11-6 and 11-7 (Boost A and DC specs); also added Shottky Diode specs. Changed current for sleep/hibernate mode to include SIO; Added footnote to analog global spec Updated Figures 1-1, 6-2, 7-14, and 8-1. Updated Table 6-2 and Table 6-3 (Hibernate and Sleep rows) and Power Modes section. Updated GPIO and S AC specifications. Updated Gain error in IDAC and VDAC specifications. Updated description of V <sub>DDA</sub> spec in Table 11-1 and removed GPIO Clamp Current parameter. Updated number of UDBs on page 1. Moved FILO from ILO DC to AC table. Added PCB Layout and PCB Schematic diagrams. Updated Fgpioout spec (Table 11-9). Added duty cycle frequency in PLL AC spec table. Added note for Sleep and Hibernate modes and Active Mode spe in Table 11-2. Linked URL in Section 10.3 to PSoC Creator site. Updated Ja and Jc values in Table 13-1. Updated Single Sample Mode and Fa FIR Mode sections. Updated Input Resistance specification in Del-Sig ADC table. Added Tio_init parameter. Updated PGA and UGB AC Specs. Remove SPC ADC. Updated Boost Converter section. Added section 'SIO as Comparator'; updated Hysteresis spec (differential mode) in Table 11-10. Updated V <sub>BAT</sub> condition and deleted Vstart parameter in Table 11-6. Added 'Bytes' column for Tables 4-1 to 4-5. |

| *J   | 2873322 | 02/04/10           | MKEA               | Changed maximum value of PPOR_TR to '1'. Updated V <sub>BIAS</sub> specification. Updated PCB Schematic. Updated Figure 8-1 and Figure 6-3. Updated Intern Vector table, Updated Sales links. Updated JTAG and SWD specifications. Removed Jp-p and Jperiod from ECO AC Spec table. Added note on sleep tin in Table 11-2. Updated ILO AC and DC specifications. Added Resolution parameter in VDAC and IDAC tables. Updated I <sub>OUT</sub> typical and maximum values. Changed Temperature Sensor range to -40 °C to +85 °C. Removed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| scription Title: PSoC <sup>®</sup> 3: CY8C38 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> )<br>cument Number: 001-11729 |         |            |      |                                                                                                   |