#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3865lti-059 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

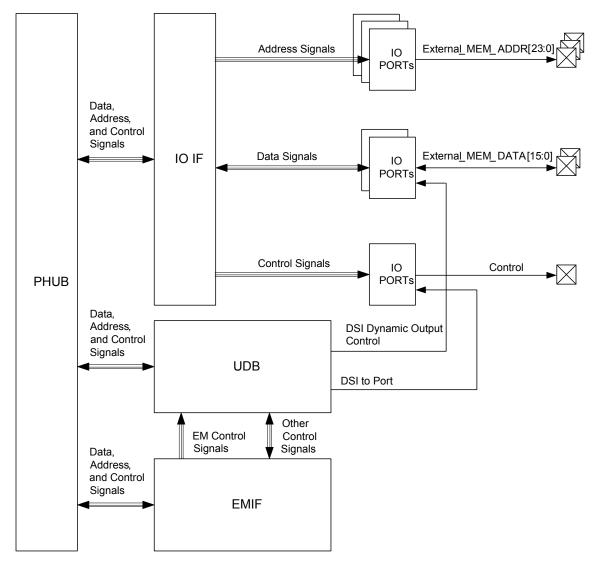

For more details on the peripherals see the "Example Peripherals" section on page 35 of this datasheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 34 of this datasheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 0.1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

- Digital filter block (DFB)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±2 LSB

- DNL less than ±1 LSB

- SINAD better than 84 dB in 16-bit mode

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors. The output of the ADC can optionally feed the programmable DFB through the DMA without CPU intervention. You can configure the DFB to perform IIR and FIR digital filters and several user-defined custom functions. The DFB can implement filters with up to 64 taps. It can perform a 48-bit multiply-accumulate (MAC) operation in one clock cycle.

Four high-speed voltage or current DACs support 8-bit output signals at an update rate of up to 8 Msps. They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths. In addition to the ADC, DACs, and DFB, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- Programmable gain amplifiers

- Mixers

- Dother similar analog components

See the "Analog Subsystem" section on page 46 of this datasheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 67 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after POR.

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the Vddio pins. Every GPIO has analog I/O, LCD drive<sup>[4]</sup>, CapSense<sup>[5]</sup>, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow V<sub>OH</sub> to be set independently of Vddio when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 28 of this datasheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The internal main oscillator (IMO) is the master clock base for the system, and has 1-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 62 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs. The device provides a PLL to generate system clock frequencies up to 67 MHz from the IMO, external crystal, or external reference clock.

#### Notes

4. This feature on select devices only. See Ordering Information on page 105 for details.

<sup>5.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

# PSoC<sup>®</sup> 3: CY8C38 Family Datasheet

#### Table 4-2. Logical Instructions (continued)

|      | Mnemonic      | Description                           | Bytes | Cycles |

|------|---------------|---------------------------------------|-------|--------|

| ANL  | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL  | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL  | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL  | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL  | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL  | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL  | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL  | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL  | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL  | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL  | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL  | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL  | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR  | А             | Clear accumulator                     | 1     | 1      |

| CPL  | A             | Complement accumulator                | 1     | 1      |

| RL   | А             | Rotate accumulator left               | 1     | 1      |

| RLC  | Α             | Rotate accumulator left through carry | 1     | 1      |

| RR   | Α             | Rotate accumulator right              | 1     | 1      |

| RRC  | А             | Rotate accumulator right though carry | 1     | 1      |

| SWAF | PA            | Swap nibbles within accumulator       | 1     | 1      |

#### 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed

addressing mode. Table 4-3 lists the various data transfer instructions available.

#### 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit-addressable memory location. It has 128 bits of bit addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 lists the available Boolean instructions.

|     | Mnemonic   | Description                        | Bytes | Cycles |

|-----|------------|------------------------------------|-------|--------|

| MOV | A,Rn       | Move register to accumulator       | 1     | 1      |

| MOV | A,Direct   | Move direct byte to accumulator    | 2     | 2      |

| MOV | A,@Ri      | Move indirect RAM to accumulator   | 1     | 2      |

| MOV | A,#data    | Move immediate data to accumulator | 2     | 2      |

| MOV | Rn,A       | Move accumulator to register       | 1     | 1      |

| MOV | Rn,Direct  | Move direct byte to register       | 2     | 3      |

| MOV | Rn, #data  | Move immediate data to register    | 2     | 2      |

| MOV | Direct, A  | Move accumulator to direct byte    | 2     | 2      |

| MOV | Direct, Rn | Move register to direct byte       | 2     | 2      |

#### Table 4-3. Data Transfer Instructions

Figure 5-1. EMIF Block Diagram

### 5.6 Memory Map

The CY8C38 8051 memory map is very similar to the MCS-51 memory map.

#### 5.6.1 Code Space

The CY8C38 8051 code space is 64 KB. Only main flash exists in this space. See the Flash Program Memory on page 18.

#### 5.6.2 Internal Data Space

The CY8C38 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 18) and a 128-byte space for special function registers (SFR). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

#### Figure 5-2. 8051 Internal Data Space

| 0x00<br>0x1F | 4 Banks, R0-R7 Each                                                     |                                                          |  |  |

|--------------|-------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| 0x20<br>0x2F | Bit-Addressable Area                                                    |                                                          |  |  |

| 0x30<br>0x7F | Lower Core RAM Shared with Stack Space (direct and indirect addressing) |                                                          |  |  |

| 0x80         | Upper Core RAM Shared<br>with Stack Space<br>(indirect addressing)      | SFR<br>Special Function Registers<br>(direct addressing) |  |  |

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 11.

#### 5.6.3 SFRs

The SFR space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-2.

#### Table 5-2. SFR Map

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | -    | _    | _    | -   | -   |

| 0×F0    | В          | -          | SFRPRT12SEL | -    | -    | -    | -   | -   |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        | -    | -    | -    | -   | -   |

| 0×E0    | ACC        | -          | -           | -    | -    | _    | -   | -   |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | -    | -    | -    | -   | -   |

| 0×D0    | PSW        | -          | -           | -    | -    | -    | -   | -   |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | -    | -    | _    | -   | -   |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | -    | -    | -    | -   | -   |

| 0×B8    |            |            |             | -    | -    | -    | -   | -   |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | -    | -    | _    | -   | -   |

| 0×A8    | IE         | -          | -           | -    | -    | -    | -   | -   |

| 0×A0    | P2AX       | -          | SFRPRT1SEL  | -    | -    | -    | -   | -   |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | -    | -    | _    | -   | -   |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  | -           | DPX0 | -    | DPX1 | -   | -   |

| 0×88    | -          | SFRPRT0PS  | SFRPRT0SEL  | -    | -    | -    | -   | -   |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | -   |

The CY8C38 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C38 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C38 family.

#### **XData Space Access SFRs**

The 8051 core features dual DPTR registers for faster data transfer operations. The data pointer select SFR, DPS, selects which data pointer register, DPTR0 or DPTR1, is used for the following instructions:

- MOVX @DPTR, A

- MOVX A, @DPTR

- MOVC A, @A+DPTR

- JMP @A+DPTR

- INC DPTR

- MOV DPTR, #data16

The extended data pointer SFRs, DPX0, DPX1, MXAX, and P2AX, hold the most significant parts of memory addresses during access to the xdata space. These SFRs are used only with the MOVX instructions.

During a MOVX instruction using the DPTR0/DPTR1 register, the most significant byte of the address is always equal to the contents of DPX0/DPX1.

During a MOVX instruction using the R0 or R1 register, the most significant byte of the address is always equal to the contents of MXAX, and the next most significant byte is always equal to the contents of P2AX.

### I/O Port SFRs

The I/O ports provide digital input sensing, output drive, pin interrupts, connectivity for analog inputs and outputs, LCD, and access to peripherals through the DSI. Full information on I/O ports is found in I/O System and Routing on page 28.

I/O ports are linked to the CPU through the PHUB and are also available in the SFRs. Using the SFRs allows faster access to a limited set of I/O port registers, while using the PHUB allows boot configuration and access to all I/O port registers.

Each SFR supported I/O port provides three SFRs:

- SFRPRTxDR sets the output data state of the port (where × is port number and includes ports 0–6, 12 and 15).

- The SFRPRTxSEL selects whether the PHUB PRTxDR register or the SFRPRTxDR controls each pin's output buffer within the port. If a SFRPRTxSEL[y] bit is high, the corresponding SFRPRTxDR[y] bit sets the output state for that pin. If a SFRPRTxSEL[y] bit is low, the corresponding PRTxDR[y] bit sets the output state of the pin (where y varies from 0 to 7).

- The SFRPRTxPS is a read only register that contains pin state values of the port pins.

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal.

#### 6.1.2 External Oscillators

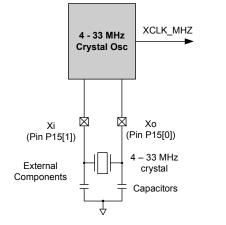

#### 6.1.2.1 MHz External Crystal Oscillator

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 33 MHz. When used in conjunction with the PLL, it can generate CPU and system clocks up to the device's maximum frequency (see PLL). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

#### Figure 6-2. MHzECO Block Diagram

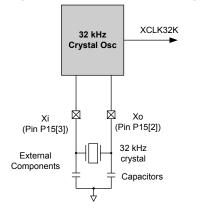

#### 6.1.2.2 32.768-kHz ECO

The 32.768-kHz external crystal oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768-kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the RTC. The RTC uses a 1-second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

#### Figure 6-3. 32kHzECO Block Diagram

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

#### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The system clock is used to select and supply the fastest clock in the system for general system clock requirements and clock synchronization of the PSoC device.

- Bus clock 16-bit divider uses the system clock to generate the system's bus clock used for data transfers. Bus clock is the source clock for the CPU clock divider.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the UDBs and fixed function timer/counter/PWMs can also generate clocks.

- Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as ADC and mixers. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise.

Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50 percent duty cycle clocks, system clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

#### 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency can be generated from different sources, including DSI clock at 48 MHz or doubled value of 24 MHz from internal oscillator, DSI signal, or crystal oscillator. PRELIMINARY

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt

Interrupt circuits are available to detect when Vdda and Vddd go outside a voltage range. For AHVI, Vdda is compared to a fixed trip level. For ALVI and DLVI, Vdda and Vddd are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

# Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply           | Normal<br>Voltage<br>Range | Available Trip<br>Settings               | Accuracy |

|-----------|------------------|----------------------------|------------------------------------------|----------|

| DLVI      | V <sub>DDD</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| ALVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| AHVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 5.75 V                                   | ±2%      |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

- 6.3.1.2 Other Reset Sources

- XRES External reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

SRES – Software reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

DRES – Digital logic reset

A logic signal can be routed from the UDBs or other digital peripheral source through the DSI to the Configurable XRES pin, P1[2], to generate a hardware-controlled reset. The pin must be placed in XRES mode. The response to a DRES is the same as after an IPOR reset.

WRES – Watchdog timer reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

#### Note

14. GPIOs with opamp outputs are not recommended for use with CapSense.

# 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the Vddio pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[14]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of V<sub>DDA</sub> and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[14]</sup>

- □ Analog input and output capability

- □ Continuous 100 µA clamp current capability

- □ Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- $\square$  Hot swap capability (5 V tolerance at any operating V<sub>DD</sub>)

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

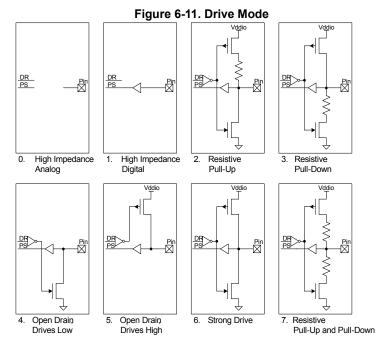

#### 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-11 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull-up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

#### Table 6-6. Drive Modes

| Diagram | Drive Mode                                      | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|-------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedence analog                           | 0       | 0       | 0       | High Z        | High Z       |

| 1       | High Impedance digital                          | 0       | 0       | 1       | High Z        | High Z       |

| 2       | Resistive pull-up <sup>[15]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[15]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                          | 1       | 0       | 0       | High Z        | Strong Low   |

| 5       | Open drain, drive high                          | 1       | 0       | 1       | Strong High   | High Z       |

| 6       | Strong drive                                    | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[15]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

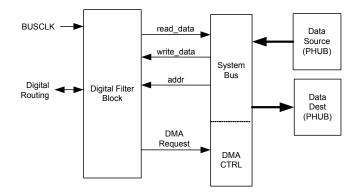

# Figure 7-22. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

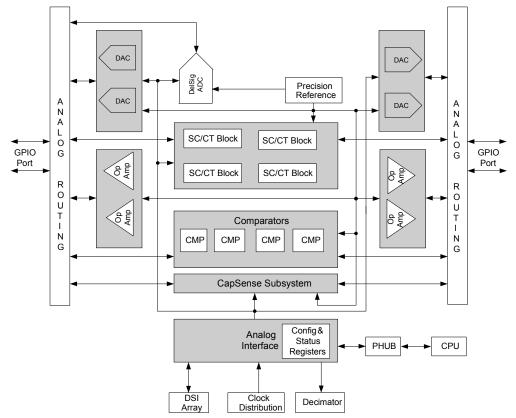

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

Figure 8-1. Analog Subsystem Block Diagram

#### Table 8-3. Bandwidth

| Gain | Bandwidth |

|------|-----------|

| 1    | 6.0 MHz   |

| 24   | 340 kHz   |

| 48   | 220 kHz   |

| 50   | 215 kHz   |

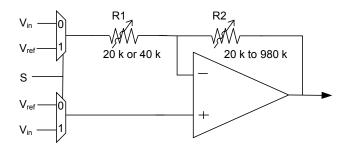

Figure 8-9. PGA Resistor Settings

The PGA is used in applications where the input signal may not be large enough to achieve the desired resolution in the ADC, or dynamic range of another SC/CT block such as a mixer. The gain is adjustable at runtime, including changing the gain of the PGA prior to each ADC sample.

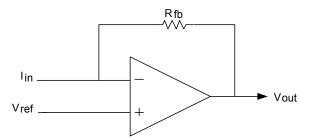

#### 8.5.4 TIA

The Transimpedance Amplifier (TIA) converts an internal or external current to an output voltage. The TIA uses an internal feedback resistor in a continuous time configuration to convert input current to output voltage. For an input current lin, the output voltage is lin x Rfb +V<sub>REF</sub>, where V<sub>REF</sub> is the value placed on the non inverting input. The feedback resistor Rfb is programmable between 20 K $\Omega$  and 1 M $\Omega$  through a configuration register. Table 8-4 shows the possible values of Rfb and associated configuration settings.

| Table 8-4. | Feedback | Resistor | Settings |

|------------|----------|----------|----------|

|------------|----------|----------|----------|

| Configuration Word | Nominal R <sub>fb</sub> (KΩ) |

|--------------------|------------------------------|

| 000b               | 20                           |

| 001b               | 30                           |

| 010b               | 40                           |

| 011b               | 60                           |

| 100b               | 120                          |

| 101b               | 250                          |

| 110b               | 500                          |

| 111b               | 1000                         |

#### Figure 8-10. Continuous Time TIA Schematic

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the V<sub>REF</sub> TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

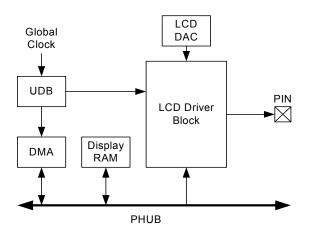

#### 8.6 LCD Direct Drive

The PSoC LCD driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C38 family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

#### Figure 8-11. LCD System

#### 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through the DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

#### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

#### 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

A capacitive sensing method using a Delta-sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

#### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

#### 8.9 DAC

The CY8C38 parts contain up to four Digital to Analog Convertors (DACs). Each DAC is 8-bit and can be configured for either voltage or current output. The DACs support CapSense, power supply regulation, and waveform generation. Each DAC has the following features:

- Adjustable voltage or current output in 255 steps

- Programmable step size (range selection)

- Eight bits of calibration to correct ± 25 percent of gain error

- Source and sink option for current output

- 8 Msps conversion rate for current output

- 1 Msps conversion rate for voltage output

- Monotonic in nature

- Data and strobe inputs can be provided by the CPU or DMA, or routed directly from the DSI

- Dedicated low-resistance output pin for high-current mode

# Table 11-20. 20-bit Delta-sigma ADC DC Specifications (continued)

| Parameter          | Description                                                                                             | Conditions           | Min | Тур | Max  | Units |  |

|--------------------|---------------------------------------------------------------------------------------------------------|----------------------|-----|-----|------|-------|--|

| Vextref            | ADC external reference input voltage, see<br>also internal reference in Voltage<br>Reference on page 80 | Pins P0[3], P3[2]    | 0.9 | -   | 1.3  | V     |  |

| Current Co         | Current Consumption                                                                                     |                      |     |     |      |       |  |

| I <sub>DD_20</sub> | Current consumption, 20 bit <sup>[35]</sup>                                                             | 187 sps, unbuffered  | -   | -   | 1.25 | mA    |  |

| I <sub>DD_16</sub> | Current consumption, 16 bit <sup>[35]</sup>                                                             | 48 ksps, unbuffered  | -   | -   | 1.2  | mA    |  |

| I <sub>DD_12</sub> | Current consumption, 12 bit <sup>[35]</sup>                                                             | 192 ksps, unbuffered | _   | -   | 1.4  | mA    |  |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[35]</sup>                                                              |                      | -   | -   | 2.5  | mA    |  |

### Table 11-21. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | _   | _   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[35]</sup>                         | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V | _   | -   | 0.0032 | %       |

| 20-Bit Resol | ution Mode                                                        |                                              |     | •   | •      |         |

| SR20         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 7.8 | _   | 187    | sps     |

| BW20         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 40  | -      | Hz      |

| 16-Bit Resol | ution Mode                                                        |                                              |     |     |        |         |

| SR16         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 2   | _   | 48     | ksps    |

| BW16         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 11  | _      | kHz     |

| SINAD16int   | Signal to noise ratio, 16-bit, internal reference <sup>[35]</sup> | Range = ±1.024V, unbuffered                  | 81  | -   | -      | dB      |

| SINAD16ext   | Signal to noise ratio, 16-bit, external reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 84  | -   | -      | dB      |

| 12-Bit Resol | ution Mode                                                        |                                              |     |     | •      |         |

| SR12         | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | _   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 44  | -      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         |                                              |     |     |        |         |

| SR8          | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | _   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 88  | -      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[35]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | -   | -      | dB      |

Notes

35. Based on device characterization (Not production tested).

| Resolution, | Cont | inuous | Multi- | Sample | Multi-Sar | nple Turbo |

|-------------|------|--------|--------|--------|-----------|------------|

| Bits        | Min  | Max    | Min    | Max    | Min       | Max        |

| 8           | 8000 | 384000 | 1911   | 91701  | 1829      | 87771      |

| 9           | 6400 | 307200 | 1543   | 74024  | 1489      | 71441      |

| 10          | 5566 | 267130 | 1348   | 64673  | 1307      | 62693      |

| 11          | 4741 | 227555 | 1154   | 55351  | 1123      | 53894      |

| 12          | 4000 | 192000 | 978    | 46900  | 956       | 45850      |

| 13          | 3283 | 157538 | 806    | 38641  | 791       | 37925      |

| 14          | 2783 | 133565 | 685    | 32855  | 674       | 32336      |

| 15          | 2371 | 113777 | 585    | 28054  | 577       | 27675      |

| 16          | 2000 | 48000  | 495    | 11861  | 489       | 11725      |

| 17          | 500  | 12000  | 124    | 2965   | 282       | 6766       |

| 18          | 125  | 3000   | 31     | 741    | 105       | 2513       |

| 19          | 16   | 375    | 4      | 93     | 15        | 357        |

| 20          | 8    | 187.5  | 2      | 46     | 8         | 183        |

# Table 11-22. Delta-sigma ADC Sample Rates, Range = ±1.024 V

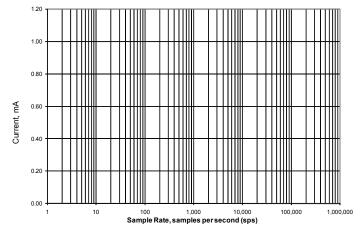

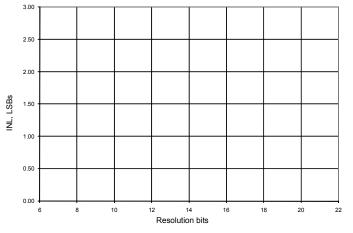

Figure 11-17. Delta-sigma ADC I<sub>DD</sub> vs sps, Range = ±1.024 V Figure 11-18. Delta-sigma ADC INL at Maximum Sample Rate

### Table 11-28. Comparator AC Specifications

| Parameter         | Description                                         | Conditions                           | Min | Тур | Max | Units |

|-------------------|-----------------------------------------------------|--------------------------------------|-----|-----|-----|-------|

| T <sub>RESP</sub> | Response time, high current mode <sup>[39]</sup>    | 50 mV overdrive, measured pin-to-pin | -   | 75  | 110 | ns    |

|                   | Response time, low current mode <sup>[39]</sup>     | 50 mV overdrive, measured pin-to-pin | _   | 155 | 200 | ns    |

|                   | Response time, ultra low-power mode <sup>[39]</sup> | 50 mV overdrive, measured pin-to-pin | -   | 55  | -   | μs    |

# 11.5.6 Current Digital-to-analog Converter(IDAC)

See the IDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

Table 11-29. IDAC DC Specifications

| Parameter        | Description                              | Conditions                                                                                                                                                        | Min | Тур    | Max  | Units  |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|

|                  | Resolution                               |                                                                                                                                                                   | _   | -      | 8    | bits   |

| I <sub>OUT</sub> | Output current at code = 255             | $\label{eq:rescaled} \begin{array}{l} \mbox{Range} = 2.048 \mbox{ mA, code} = 255, \\ \mbox{V}_{\mbox{DDA}} \geq 2.7 \mbox{ V, Rload} = 600 \ \Omega \end{array}$ | -   | 2.048  | -    | mA     |

|                  |                                          | Range = 2.048 mA, High mode, code = 255, V_{DDA} $\leq$ 2.7 V, Rload = 300 $\Omega$                                                                               | -   | 2.048  | -    | mA     |

|                  |                                          | Range = $255 \mu$ A, code = $255$ , Rload<br>= $600 \Omega$                                                                                                       | -   | 255    | _    | μA     |

|                  |                                          | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                                                                       | -   | 31.875 | -    | μA     |

|                  | Monotonicity                             |                                                                                                                                                                   | -   | -      | Yes  |        |

| Ezs              | Zero scale error                         |                                                                                                                                                                   | -   | 0      | ±1   | LSB    |

| Eg               | Gain error                               | Range = 2.048 mA, 25 °C                                                                                                                                           | -   | -      | ±2.5 | %      |

|                  |                                          | Range = 255 µA, 25 ° C                                                                                                                                            | _   | _      | ±2.5 | %      |

|                  |                                          | Range = 31.875 µA, 25 ° C                                                                                                                                         | _   | _      | ±3.5 | %      |

| TC_Eg            | Temperature coefficient of gain<br>error | Range = 2.048 mA                                                                                                                                                  | -   | -      | 0.04 | % / °C |

|                  |                                          | Range = 255 µA                                                                                                                                                    | -   | -      | 0.04 | % / °C |

|                  |                                          | Range = 31.875 µA                                                                                                                                                 | -   | -      | 0.05 | % / °C |

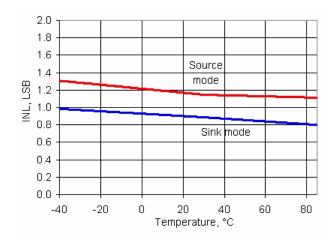

| INL              | Integral nonlinearity                    | Sink mode, range = 255 $\mu$ A, Codes<br>8 – 255, Rload = 2.4 k $\Omega$ , Cload =<br>15 pF                                                                       | -   | ±0.9   | ±1   | LSB    |

|                  |                                          | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 k $\Omega$ ,<br>Cload = 15 pF                                                                     | -   | ±1.2   | ±1.5 | LSB    |

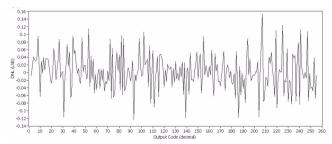

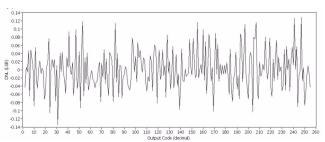

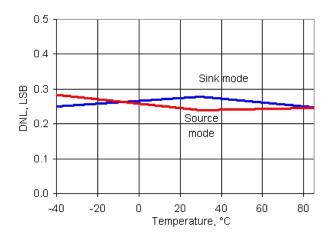

| DNL              | Differential nonlinearity                | Sink mode, range = 255 $\mu$ A, Rload<br>= 2.4 k $\Omega$ , Cload = 15 pF                                                                                         | -   | ±0.3   | ±1   | LSB    |

|                  |                                          | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 k $\Omega$ , Cload = 15 pF                                                                                       | _   | ±0.3   | ±1   | LSB    |

| Vcompliance      | Dropout voltage, source or sink mode     | Voltage headroom at max current,<br>Rload to Vdda or Rload to Vssa,<br>Vdiff from Vdda                                                                            | 1   | -      | -    | V      |

#### Note

39. Based on device characterization (Not production tested).

# Figure 11-27. IDAC DNL vs Input Code, Range = 255 $\mu\text{A},$ Source Mode

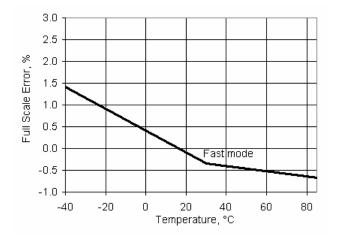

Figure 11-29. IDAC INL vs Temperature, Range = 255  $\mu A,$  Fast Mode

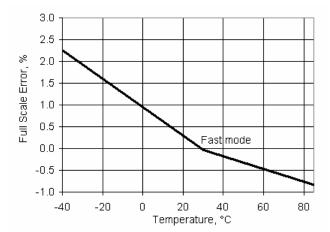

Figure 11-31. IDAC Full Scale Error vs Temperature, Range =  $255 \ \mu$ A, Source Mode

Figure 11-28. IDAC DNL vs Input Code, Range = 255  $\mu\text{A},$  Sink Mode

Figure 11-30. IDAC DNL vs Temperature, Range = 255  $\mu$ A, Fast Mode

Figure 11-32. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Sink Mode

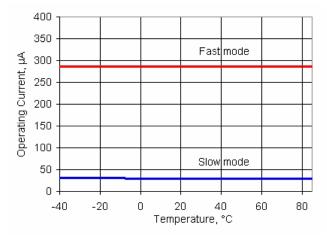

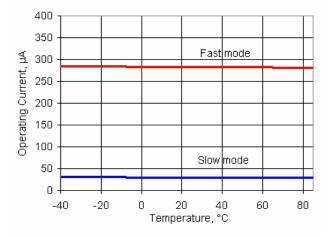

Figure 11-33. IDAC Operating Current vs Temperature, Range =  $255 \mu$ A, Code = 0, Source Mode

# Figure 11-34. IDAC Operating Current vs Temperature, Range = $255 \mu$ A, Code = 0, Sink Mode

# Table 11-30. IDAC AC Specifications

| Parameter           | Description | Conditions                                                                                             | Min | Тур | Max | Units |

|---------------------|-------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| F <sub>DAC</sub>    | Update rate |                                                                                                        | -   | -   | 8   | Msps  |

| T <sub>SETTLE</sub> | 0           | Range = 31.875 $\mu$ A or 255 $\mu$ A, full<br>scale transition, fast mode, 600 $\Omega$<br>15-pF load |     | _   | 125 | ns    |

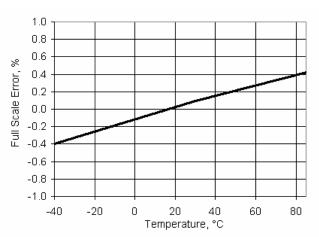

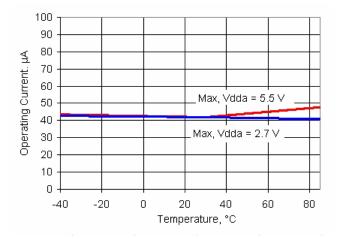

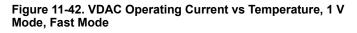

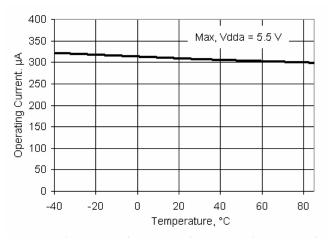

Figure 11-39. VDAC Full Scale Error vs Temperature, 1 V Mode

Figure 11-41. VDAC Operating Current vs Temperature, 1V Mode, Slow Mode

Table 11-32. VDAC AC Specifications

Mode 1.0 0.8 0.6 Full Scale Error, % 0.4 0.2 0.0 -0.2 -0.4 -0.6 -0.8 -1.0 -40 -20 0 40 60 80 20 Temperature, °C

Figure 11-40. VDAC Full Scale Error vs Temperature, 4 V

| Parameter        | Description                            | Conditions               | Min | Тур  | Max  | Units |

|------------------|----------------------------------------|--------------------------|-----|------|------|-------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                | -   | -    | 1000 | ksps  |

|                  |                                        | 4 V scale                | -   | -    | 250  | ksps  |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF | -   | 0.45 | 1    | μs    |

|                  |                                        | 4 V scale, Cload = 15 pF | -   | 0.8  | 3.2  | μs    |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF | -   | 0.45 | 1    | μs    |

|                  |                                        | 4 V scale, Cload = 15 pF | -   | 0.7  | 3    | μs    |

# 11.5.12 LCD Direct Drive

#### Table 11-40. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                       | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| I <sub>CC</sub>     | LCD system operating current                                                        | Device sleep mode with wakeup at<br>400-Hz rate to refresh LCDs, bus<br>clock = 3 Mhz, Vddio = Vdda = 3 V,<br>4 commons, 16 segments, 1/4 duty<br>cycle, 50 Hz frame rate, no glass<br>connected | -   | 38                     | -    | μΑ    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                                | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | -   | 9.1 × V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                          | -   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                                  | I   | _                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | Vddio = 5.5V, strong drive mode                                                                                                                                                                  | 355 | -                      | 710  | μA    |

### Table 11-41. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

PRELIMINARY

# **11.6 Digital Peripherals**

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.6.1 Timer

The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; for more information, see the Timer component datasheet in PSoC Creator.

#### Table 11-42. Timer DC Specifications

| Parameter | Description               | Conditions                                    | Min | Тур | Max | Units |

|-----------|---------------------------|-----------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit timer, at listed input clock frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                               | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                               | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                               | -   | 260 | _   | μA    |

|           | 67 MHz                    |                                               | -   | 350 | _   | μA    |

#### Table 11-43. Timer AC Specifications

| Parameter | Description                    | Conditions | Min | Тур | Max | Units |

|-----------|--------------------------------|------------|-----|-----|-----|-------|

|           | Operating frequency            |            | DC  | -   | 67  | MHz   |

|           | Capture pulse width (Internal) |            | 15  | -   | _   | ns    |

|           | Capture pulse width (external) |            | 30  | -   | -   | ns    |

|           | Timer resolution               |            | 15  | -   | _   | ns    |

|           | Enable pulse width             |            | 15  | -   | _   | ns    |

|           | Enable pulse width (external)  |            | 30  | -   | -   | ns    |

|           | Reset pulse width              |            | 15  | -   | -   | ns    |

|           | Reset pulse width (external)   |            | 30  | _   | _   | ns    |

#### 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component datasheet in PSoC Creator.

#### Table 11-44. Counter DC Specifications

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                                 | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                                 | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                                 | I   | 260 | -   | μA    |

|           | 67 MHz                    |                                                 | -   | 350 | -   | μA    |

#### Table 11-45. Counter AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------------|------------|-----|-----|-----|-------|

|           | Operating frequency           |            | DC  | -   | 67  | MHz   |

|           | Capture pulse                 |            | 15  | -   | -   | ns    |

|           | Resolution                    |            | 15  | -   | -   | ns    |

|           | Pulse width                   |            | 15  | -   | -   | ns    |

|           | Pulse width (external)        |            | 30  |     |     | ns    |

|           | Enable pulse width            |            | 15  | -   | -   | ns    |

|           | Enable pulse width (external) |            | 30  | -   | -   | ns    |

|           | Reset pulse width             |            | 15  | -   | -   | ns    |

|           | Reset pulse width (external)  |            | 30  | -   | -   | ns    |

|    | on Title: PSo<br>t Number: 00 |            | Family Da | tasheet Programmable System-on-Chip (PSoC <sup>®</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----|-------------------------------|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *L | 2938381                       | 05/27/10   | MKEA      | Replaced V <sub>DDIO</sub> with V <sub>DDD</sub> in USBIO diagram and specification tables, added text in USBIO section of Electrical Specifications.         Added Table 13-2 (Package MSL)         Modified Tstorag condition and changed max spec to 100         Added bullet (Pass) under ALU (section 7.2.2.2)         Added figures for kHzECO and MHzECO in the External Oscillator section         Updated Figure 6-1(Clocking Subsystem diagram)         Removed CPUCLK_DIV in table 5-2, Deleted Clock Divider SFR subsection         Updated SIO DC Specifications (V <sub>IH</sub> and V <sub>IL</sub> parameters)         Updated Figure 8-2         Updated Figure 8-2         Updated PCB Layout and Schematic, updated as per MTRB review comments         Updated Table 6-3 (power changed to current)         In 32kHZ EC DC Specifications table, updated Supply Current values         Updated GPIO DC Specifications table                                        |

| *M | 2958674                       | 06/22/10   | SHEA      | Minor ECN to post datasheet to external website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *N | 2989685                       | 08/04/10   | MKEA      | INL max is changed from 16 to 32 in Table 11-20, 20-bit Delta-sigma ADC AC<br>Specifications.<br>Added to Table 6-6 a footnote and references to same.<br>Added sentences to the resistive pullup and pull-down description bullets.<br>Added sentence to Section 6.4.11, Adjustable Output Level.<br>Updated section 5.5 External Memory Interface<br>Updated Table 11-73 JTAG Interface AC Specifications<br>Updated Table 11-74 SWD Interface AC Specifications<br>Updated style changes as per the new template.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *0 | 3078568                       | 11/04/10   | MKEA      | Added 48-SSOP pin and package details.<br>Removed PLL output duty cycle spec.<br>Updated "Current Digital-to-analog Converter(IDAC)" on page 81<br>Updated "Voltage Digital to Analog Converter (VDAC)" on page 85<br>Updated Table 11-2, "DC Specifications," on page 60<br>Updated Table 11-25, "Voltage Reference Specifications," on page 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *P | 3107314                       | 12/10/2010 | MKEA      | Updated delta-sigma tables and graphs.<br>Updated Flash AC specs<br>Formatted table 11.2.<br>Updated interrupt controller table<br>Updated transimpedance amplifier section<br>Updated SIO DC specs table<br>Updated Voltage Monitors DC Specifications table<br>Updated LCD Direct Drive DC specs table<br>Replaced the Discrete Time Mixer and Continuous Time Mixer tables with Mixer<br>DC and AC specs tables<br>Updated ESD <sub>HBM</sub> value.<br>Updated IDAC and VDAC sections<br>Removed ESO parts from ordering information<br>Changed USBIO pins from NC to DNU and removed redundant USBIO pin<br>description notes<br>Updated PGA AC specs<br>Updated PGA AC specs<br>Updated a 2 kHz External Crystal DC Specifications<br>Updated opamp AC specs<br>Updated ARES IO specs<br>Updated Inductive boost regulator section<br>Delta sigma ADC spec updates<br>Updated comparator section<br>Removed buzz mode from Power Mode Transition diagram<br>Updated PGA DC table |

Page 116 of 117

| Description Title: PSoC <sup>®</sup> 3: CY8C38 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> )<br>Document Number: 001-11729 |         |            |  |                                                                                                                             |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|-----------------------------------------------------------------------------------------------------------------------------|--|

| *Q                                                                                                                                             | 3179219 | 02/22/2011 |  | Updated conditions for flash data retention time<br>Updated 100-pin TQFP package spec.<br>Updated EEPROM AC specifications. |  |

# 18. Sales, Solutions, and Legal Information

# Worldwide Sales and Design Support

. . . . . . . . .

Cypress maintains a worldwide network of offices, solution centers, manufacturers' representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

| Products                 |                           |

|--------------------------|---------------------------|

| Automotive               | cypress.com/go/automotive |

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

|                          | cypress.com/go/plc        |

| Memory                   | cypress.com/go/memory     |

| Optical & Image Sensing  | cypress.com/go/image      |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

|                          |                           |

PSoC Solutions psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2006-2011. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-11729 Rev. \*Q

Revised February 24, 2011

Page 117 of 117

CapSense<sup>®</sup>, PSoC<sup>®</sup>3, PSoC<sup>®</sup>5, and PSoC<sup>®</sup> Creator<sup>™</sup> are trademarks and PSoC<sup>®</sup> is a registered trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are property of the respective corporations.

Purchase of I2C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use these components in an I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips. ARM is a registered trademark, and Keil, and RealView are trademarks, of ARM Limited. All products and company names mentioned in this document may be the trademarks of their respective holders.