#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3865lti-061 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PSoC<sup>®</sup> 3: CY8C38 Family Datasheet

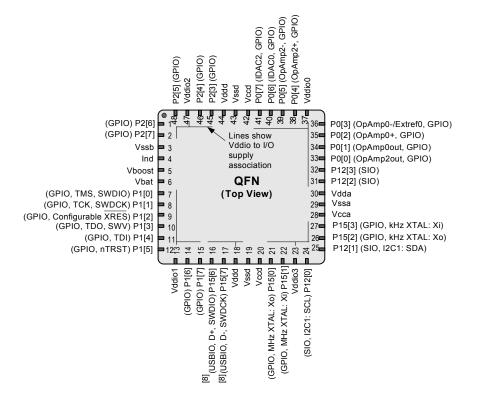

#### Figure 2-2. 48-pin QFN Part Pinout<sup>[7]</sup>

Notes

7.

Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating. The center pad on the QFN package should be connected to digital ground (V<sub>SSD</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. 8.

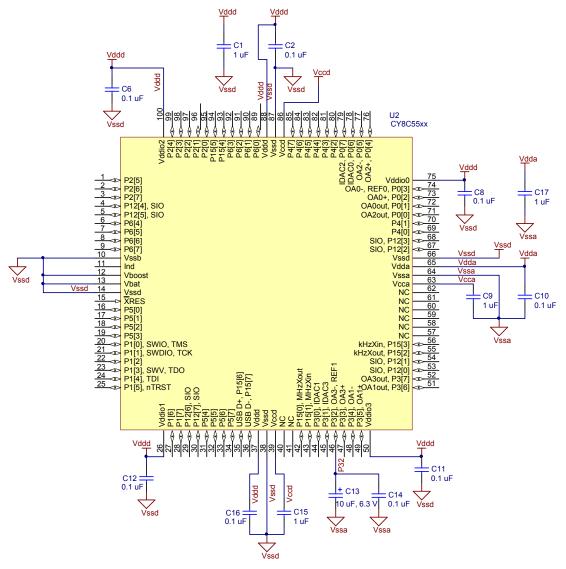

## Figure 2-5. Example Schematic for 100-pin TQFP Part with Power Connections

Note The two Vccd pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-6 on page 10.

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 11.

#### 5.6.3 SFRs

The SFR space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-2.

#### Table 5-2. SFR Map

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | -    | _    | _    | -   | -   |

| 0×F0    | В          | -          | SFRPRT12SEL | -    | -    | -    | -   | -   |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        | -    | -    | -    | -   | -   |

| 0×E0    | ACC        | -          | -           | -    | -    | _    | -   | -   |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | -    | -    | -    | -   | -   |

| 0×D0    | PSW        | -          | -           | -    | -    | -    | -   | -   |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | -    | -    | _    | -   | -   |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | -    | -    | -    | -   | -   |

| 0×B8    |            |            |             | -    | -    | -    | -   | -   |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | -    | -    | _    | -   | -   |

| 0×A8    | IE         | -          | -           | -    | -    | -    | -   | -   |

| 0×A0    | P2AX       | -          | SFRPRT1SEL  | -    | -    | -    | -   | -   |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | -    | -    | _    | -   | -   |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  | -           | DPX0 | -    | DPX1 | -   | -   |

| 0×88    | -          | SFRPRT0PS  | SFRPRT0SEL  | -    | -    | -    | -   | -   |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | -   |

The CY8C38 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C38 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C38 family.

#### **XData Space Access SFRs**

The 8051 core features dual DPTR registers for faster data transfer operations. The data pointer select SFR, DPS, selects which data pointer register, DPTR0 or DPTR1, is used for the following instructions:

- MOVX @DPTR, A

- MOVX A, @DPTR

- MOVC A, @A+DPTR

- JMP @A+DPTR

- INC DPTR

- MOV DPTR, #data16

The extended data pointer SFRs, DPX0, DPX1, MXAX, and P2AX, hold the most significant parts of memory addresses during access to the xdata space. These SFRs are used only with the MOVX instructions.

During a MOVX instruction using the DPTR0/DPTR1 register, the most significant byte of the address is always equal to the contents of DPX0/DPX1.

During a MOVX instruction using the R0 or R1 register, the most significant byte of the address is always equal to the contents of MXAX, and the next most significant byte is always equal to the contents of P2AX.

## I/O Port SFRs

The I/O ports provide digital input sensing, output drive, pin interrupts, connectivity for analog inputs and outputs, LCD, and access to peripherals through the DSI. Full information on I/O ports is found in I/O System and Routing on page 28.

I/O ports are linked to the CPU through the PHUB and are also available in the SFRs. Using the SFRs allows faster access to a limited set of I/O port registers, while using the PHUB allows boot configuration and access to all I/O port registers.

Each SFR supported I/O port provides three SFRs:

- SFRPRTxDR sets the output data state of the port (where × is port number and includes ports 0–6, 12 and 15).

- The SFRPRTxSEL selects whether the PHUB PRTxDR register or the SFRPRTxDR controls each pin's output buffer within the port. If a SFRPRTxSEL[y] bit is high, the corresponding SFRPRTxDR[y] bit sets the output state for that pin. If a SFRPRTxSEL[y] bit is low, the corresponding PRTxDR[y] bit sets the output state of the pin (where y varies from 0 to 7).

- The SFRPRTxPS is a read only register that contains pin state values of the port pins.

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt

Interrupt circuits are available to detect when Vdda and Vddd go outside a voltage range. For AHVI, Vdda is compared to a fixed trip level. For ALVI and DLVI, Vdda and Vddd are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

# Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply           | Normal<br>Voltage<br>Range | Available Trip<br>Settings               | Accuracy |

|-----------|------------------|----------------------------|------------------------------------------|----------|

| DLVI      | V <sub>DDD</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| ALVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| AHVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 5.75 V                                   | ±2%      |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

- 6.3.1.2 Other Reset Sources

- XRES External reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

SRES – Software reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

DRES – Digital logic reset

A logic signal can be routed from the UDBs or other digital peripheral source through the DSI to the Configurable XRES pin, P1[2], to generate a hardware-controlled reset. The pin must be placed in XRES mode. The response to a DRES is the same as after an IPOR reset.

WRES – Watchdog timer reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

#### Note

14. GPIOs with opamp outputs are not recommended for use with CapSense.

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the Vddio pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[14]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of V<sub>DDA</sub> and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[14]</sup>

- □ Analog input and output capability

- □ Continuous 100 µA clamp current capability

- □ Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- $\square$  Hot swap capability (5 V tolerance at any operating V<sub>DD</sub>)

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

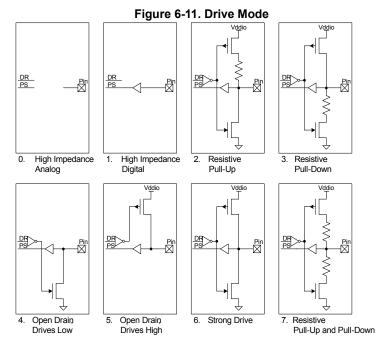

#### 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-11 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull-up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

#### Table 6-6. Drive Modes

| Diagram | Drive Mode                                      | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|-------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedence analog                           | 0       | 0       | 0       | High Z        | High Z       |

| 1       | High Impedance digital                          | 0       | 0       | 1       | High Z        | High Z       |

| 2       | Resistive pull-up <sup>[15]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[15]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                          | 1       | 0       | 0       | High Z        | Strong Low   |

| 5       | Open drain, drive high                          | 1       | 0       | 1       | Strong High   | High Z       |

| 6       | Strong drive                                    | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[15]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

#### High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

#### High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (High Z) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pullup and pull-down are not available with SIO in regulated output mode.

Open drain, drives high and open drain, drives low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the  $I^2C$  bus signal lines.

Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pullup and pull-down are not available with SIO in regulated output mode.

#### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

#### 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

#### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

#### 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to '1' and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt. While level sensitive interrupts are not directly supported; UDB provide this functionality to the system when needed.

#### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog ( $V_{DDA}$ ) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine Vddio capability for a given port and pin. The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

#### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

#### 7.2.2.5 Built in CRC/PRS

The datapath has built-in support for single cycle CRC computation and PRS generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

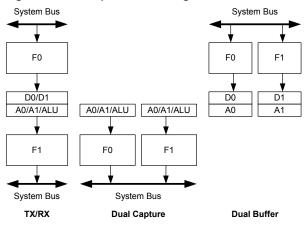

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

## 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

#### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

#### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

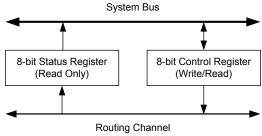

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

#### Figure 7-10. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

#### 7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component blocks and allows unused UDB resources to be used by other functions for maximum system efficiency.

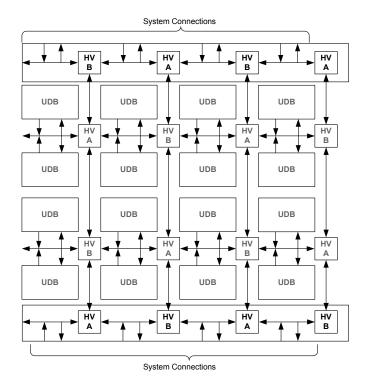

#### 7.3 UDB Array Description

Figure 7-11 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

#### Figure 7-11. Digital System Interface Structure

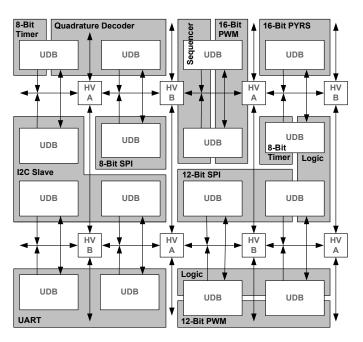

#### 7.3.1 UDB Array Programmable Resources

Figure 7-12 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions. An example of this is the 8-bit timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

#### Figure 7-12. Function Mapping Example in a Bank of UDBs

## 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-13 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

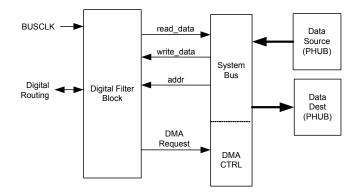

## Figure 7-22. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

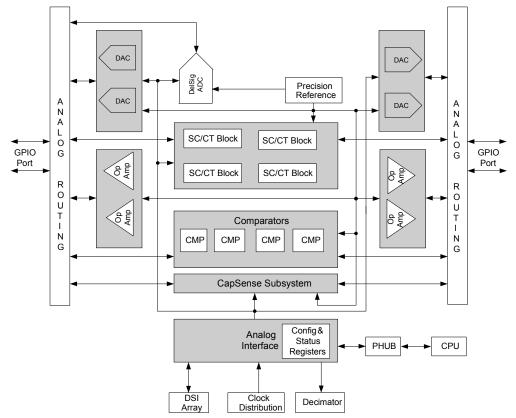

## 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

Figure 8-1. Analog Subsystem Block Diagram

## 10. Development Support

The CY8C38 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

## 10.1 Documentation

A suite of documentation, supports the CY8C38 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component datasheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes:** PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

## 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

## 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C38 family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

## 11.4.2 SIO

## Table 11-11. SIO DC Specifications

| Parameter       | Description                                                       | Conditions                                                                 | Min                                   | Тур | Max                     | Units |

|-----------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------|-----|-------------------------|-------|

| Vinmax          | Maximum input voltage                                             | All allowed values of Vddio and Vddd, see <i>Section 11.2.1</i>            | -                                     | -   | 5.5                     | V     |

| Vinref          | Input voltage reference<br>(Differential input mode)              |                                                                            | 0.5                                   | -   | $0.52 \times V_{DDIO}$  | V     |

|                 | Output voltage reference (Regulat                                 | ed output mode)                                                            |                                       |     |                         |       |

| Voutref         |                                                                   | V <sub>DDIO</sub> > 3.7                                                    | 1                                     | -   | V <sub>DDIO</sub> – 1   | V     |

|                 |                                                                   | V <sub>DDIO</sub> < 3.7                                                    | 1                                     | -   | V <sub>DDIO</sub> – 0.5 | V     |

|                 | Input voltage high threshold                                      |                                                                            |                                       |     |                         |       |

| V <sub>IH</sub> | GPIO mode                                                         | CMOS input                                                                 | $0.7 \times V_{DDIO}$                 | -   | -                       | V     |

|                 | Differential input mode <sup>[30]</sup>                           | Hysteresis disabled                                                        | SIO_ref + 0.2                         | _   | _                       | V     |

|                 | Input voltage low threshold                                       | 1                                                                          | · · · · · · · · · · · · · · · · · · · |     |                         |       |

| V <sub>IL</sub> | GPIO mode                                                         | CMOS input                                                                 | _                                     | _   | $0.3 \times V_{DDIO}$   | V     |

|                 | Differential input mode <sup>[30]</sup>                           | Hysteresis disabled                                                        | _                                     | _   | SIO_ref - 0.2           | V     |

|                 | Output voltage high                                               | 1                                                                          | ц                                     |     |                         |       |

|                 | Unregulated mode                                                  | I <sub>OH</sub> = 4 mA, V <sub>DDIO</sub> = 3.3 V                          | V <sub>DDIO</sub> – 0.4               | _   | -                       | V     |

| V <sub>OH</sub> | Regulated mode <sup>[30]</sup>                                    | I <sub>OH</sub> = 1 mA                                                     | SIO_ref-0.65                          | -   | SIO_ref + 0.2           | V     |

|                 | Regulated mode <sup>[30]</sup>                                    | I <sub>OH</sub> = 0.1 mA                                                   | SIO_ref – 0.3                         | -   | SIO_ref + 0.2           | V     |

|                 | Output voltage low                                                |                                                                            |                                       |     |                         |       |

| V <sub>OL</sub> |                                                                   | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 25 mA                        | -                                     | -   | 0.8                     | V     |

|                 |                                                                   | V <sub>DDIO</sub> = 1.80 V, I <sub>OL</sub> = 4 mA                         | —                                     | -   | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                                  |                                                                            | 3.5                                   | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                                |                                                                            | 3.5                                   | 5.6 | 8.5                     | kΩ    |

| IIL             | Input leakage current (Absolute value) <sup>[31]</sup>            |                                                                            |                                       |     |                         |       |

|                 | V <sub>IH</sub> ≤ Vddsio                                          | 25 °C, Vddsio = $3.0 \text{ V}$ , $\text{V}_{\text{IH}}$ = $3.0 \text{ V}$ | _                                     | _   | 14                      | nA    |

|                 | V <sub>IH</sub> > Vddsio                                          | 25 °C, Vddsio = 0 V, V <sub>IH</sub> = 3.0 V                               | _                                     | _   | 10                      | μA    |

| C <sub>IN</sub> | Input Capacitance <sup>[31]</sup>                                 |                                                                            | _                                     | _   | 7                       | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[31]</sup>     | Single ended mode (GPIO mode)                                              | -                                     | 40  | _                       | mV    |

|                 |                                                                   | Differential mode                                                          | -                                     | 35  | -                       | mV    |

| Idiode          | Current through protection diode to $V_{\mbox{\scriptsize SSIO}}$ |                                                                            | -                                     | -   | 100                     | μA    |

## Table 11-12. SIO AC Specifications

| Parameter | Description                                            | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in fast strong mode (90/10%) <sup>[31]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TfallF    | Fall time in fast strong mode (90/10%) <sup>[31]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TriseS    | Rise time in slow strong mode (90/10%) <sup>[31]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | -   | 75  | ns    |

| TfallS    | Fall time in slow strong mode (90/10%) <sup>[31]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | -   | 60  | ns    |

Notes 30. See Figure 6-9 on page 30 and Figure 6-12 on page 33 for more information on SIO reference. 31. Based on device characterization (Not production tested).

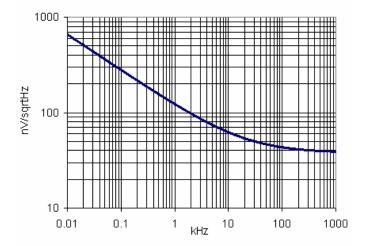

Figure 11-14. Opamp Noise vs Frequency, Power Mode = High, Vdda = 5V

Figure 11-13. Opamp test Circuit for Gain = 10

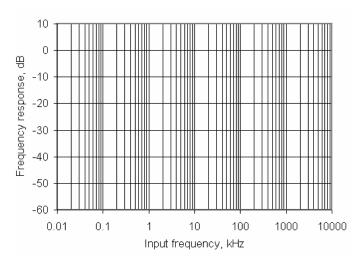

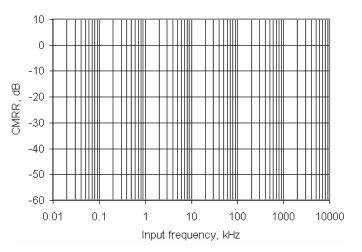

Figure 11-15. Opamp CMRR vs Frequency

| Resolution, | Cont | inuous | Multi- | Sample | Multi-Sar | Multi-Sample Turbo |  |  |

|-------------|------|--------|--------|--------|-----------|--------------------|--|--|

| Bits        | Min  | Max    | Min    | Max    | Min       | Max                |  |  |

| 8           | 8000 | 384000 | 1911   | 91701  | 1829      | 87771              |  |  |

| 9           | 6400 | 307200 | 1543   | 74024  | 1489      | 71441              |  |  |

| 10          | 5566 | 267130 | 1348   | 64673  | 1307      | 62693              |  |  |

| 11          | 4741 | 227555 | 1154   | 55351  | 1123      | 53894              |  |  |

| 12          | 4000 | 192000 | 978    | 46900  | 956       | 45850              |  |  |

| 13          | 3283 | 157538 | 806    | 38641  | 791       | 37925              |  |  |

| 14          | 2783 | 133565 | 685    | 32855  | 674       | 32336              |  |  |

| 15          | 2371 | 113777 | 585    | 28054  | 577       | 27675              |  |  |

| 16          | 2000 | 48000  | 495    | 11861  | 489       | 11725              |  |  |

| 17          | 500  | 12000  | 124    | 2965   | 282       | 6766               |  |  |

| 18          | 125  | 3000   | 31     | 741    | 105       | 2513               |  |  |

| 19          | 16   | 375    | 4      | 93     | 15        | 357                |  |  |

| 20          | 8    | 187.5  | 2      | 46     | 8         | 183                |  |  |

## Table 11-22. Delta-sigma ADC Sample Rates, Range = ±1.024 V

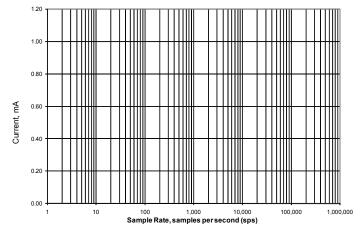

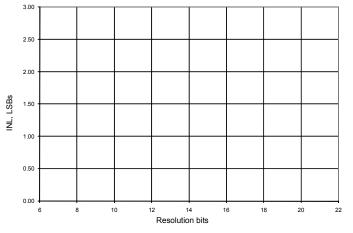

Figure 11-17. Delta-sigma ADC I<sub>DD</sub> vs sps, Range = ±1.024 V Figure 11-18. Delta-sigma ADC INL at Maximum Sample Rate

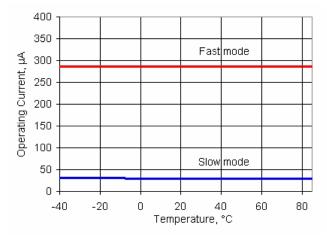

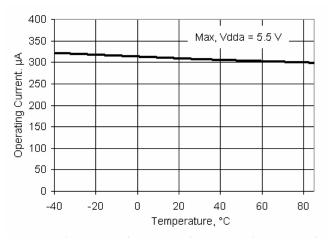

Figure 11-33. IDAC Operating Current vs Temperature, Range =  $255 \mu$ A, Code = 0, Source Mode

# Figure 11-34. IDAC Operating Current vs Temperature, Range = $255 \mu$ A, Code = 0, Sink Mode

## Table 11-30. IDAC AC Specifications

| Parameter           | Description | Conditions                                                                                             | Min | Тур | Мах | Units |

|---------------------|-------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| F <sub>DAC</sub>    | Update rate |                                                                                                        | -   | -   | 8   | Msps  |

| T <sub>SETTLE</sub> | 0           | Range = 31.875 $\mu$ A or 255 $\mu$ A, full<br>scale transition, fast mode, 600 $\Omega$<br>15-pF load |     | _   | 125 | ns    |

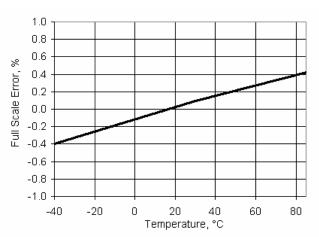

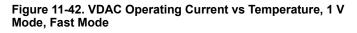

Figure 11-39. VDAC Full Scale Error vs Temperature, 1 V Mode

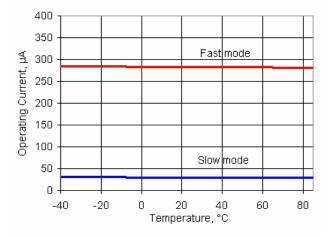

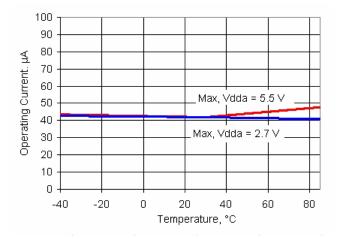

Figure 11-41. VDAC Operating Current vs Temperature, 1V Mode, Slow Mode

Table 11-32. VDAC AC Specifications

Mode 1.0 0.8 0.6 Full Scale Error, % 0.4 0.2 0.0 -0.2 -0.4 -0.6 -0.8 -1.0 -40 -20 0 40 60 80 20 Temperature, °C

Figure 11-40. VDAC Full Scale Error vs Temperature, 4 V

| Parameter        | Description                            | Conditions               | Min | Тур  | Max  | Units |

|------------------|----------------------------------------|--------------------------|-----|------|------|-------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                | -   | -    | 1000 | ksps  |

|                  |                                        | 4 V scale                | -   | -    | 250  | ksps  |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF | -   | 0.45 | 1    | μs    |

|                  |                                        | 4 V scale, Cload = 15 pF | -   | 0.8  | 3.2  | μs    |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF | -   | 0.45 | 1    | μs    |

|                  |                                        | 4 V scale, Cload = 15 pF | -   | 0.7  | 3    | μs    |

### 11.5.10 Programmable Gain Amplifier

The PGA is created using a SC/CT analog block; see the PGA component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, operating conditions are:

- Operating temperature = 25 °C for typical values

- Unless otherwise specified, all charts and graphs show typical values

#### Table 11-37. PGA DC Specifications

| Parameter | Description                                 | Conditions                                                                        | Min                    | Тур | Max                     | Units       |

|-----------|---------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-----|-------------------------|-------------|

| Vin       | Input voltage range                         | Power mode = minimum                                                              | Vssa                   | -   | Vdda                    | V           |

| Vos       | Input offset voltage                        | Power mode = high,<br>gain = 1                                                    | -                      | -   | 10                      | mV          |

| TCVos     | Input offset voltage drift with temperature | Power mode = high,<br>gain = 1                                                    | -                      | -   | ±30                     | µV/°C       |

| Ge1       | Gain error, gain = 1                        |                                                                                   | -                      | -   | ±0.15                   | %           |

| Ge16      | Gain error, gain = 16                       |                                                                                   | -                      | -   | ±2.5                    | %           |

| Ge50      | Gain error, gain = 50                       |                                                                                   | -                      | -   | ±5                      | %           |

| Vonl      | DC output nonlinearity                      | Gain = 1                                                                          | -                      | -   | ±0.01                   | % of<br>FSR |

| Cin       | Input capacitance                           |                                                                                   | _                      | _   | 7                       | pF          |

| Voh       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | V <sub>DDA</sub> -0.15 | -   | _                       | V           |

| Vol       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | -                      | -   | V <sub>SSA</sub> + 0.15 | V           |

| Vsrc      | Output voltage under load                   | lload = 250 µA, Vdda ≥ 2.7V, power mode = high                                    | -                      | -   | 300                     | mV          |

| ldd       | Operating current                           | Power mode = high                                                                 | -                      | 1.5 | 1.65                    | mA          |

| PSRR      | Power supply rejection ratio                |                                                                                   | 48                     | -   | _                       | dB          |

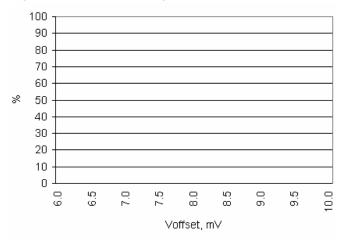

Figure 11-43. Voffset Histogram, 1000 Samples, Vdda = 5 V

## 11.6.8 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component datasheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

#### Table 11-54. UDB AC Specifications

| Parameter              | Description                                                   | Conditions                                       | Min | Тур | Max | Units |

|------------------------|---------------------------------------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| Datapath Per           | formance                                                      |                                                  |     |     |     |       |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                  | -   | -   | 67  | MHz   |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                  | -   | -   | 67  | MHz   |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit<br>CRC/PRS in a UDB pair          |                                                  | -   | -   | 67  | MHz   |

| PLD Perform            | ance                                                          |                                                  |     |     |     |       |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass<br>PLD function in a UDB pair |                                                  | -   | -   | 67  | MHz   |

| Clock to Outp          | but Performance                                               |                                                  |     |     |     |       |

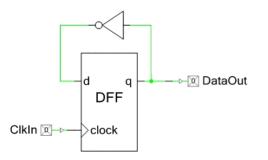

| <sup>t</sup> сlк_оит   | Propagation delay for clock in to data out, see Figure 11-47. | 25 °C, Vddd $\ge$ 2.7 V                          | -   | 20  | 25  | ns    |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-47. | Worst-case placement, routing, and pin selection | -   | _   | 55  | ns    |

#### Figure 11-47. Clock to Output Performance

## 11.8.3 Interrupt Controller

## Table 11-71. Interrupt Controller AC Specifications

| Parameter | Description                                                           | Conditions                                                                    | Min | Тур | Max | Units   |

|-----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|---------|

|           | Delay from interrupt signal input to ISR code execution from ISR code | Includes worse case completion of<br>longest instruction DIV with 6<br>cycles | -   | -   | 25  | Tcy CPU |

## 11.8.4 JTAG Interface

## Table 11-72. JTAG Interface AC Specifications<sup>[46]</sup>

| Parameter                             | Description                  | Conditions                                            | Min        | Тур | Max                | Units |

|---------------------------------------|------------------------------|-------------------------------------------------------|------------|-----|--------------------|-------|

| f_TCK                                 | TCK frequency                | $3.3 \text{ V} \le \text{V}_{DDD} \le 5 \text{ V}$    | -          | -   | 14 <sup>[47]</sup> | MHz   |

|                                       |                              | $1.71 \text{ V} \le \text{V}_{DDD}$ < $3.3 \text{ V}$ | -          | -   | 7 <sup>[47]</sup>  | MHz   |

| T_TDI_setup TDI setup before TCK high |                              |                                                       | (T/10) – 5 | -   | -                  | ns    |

| T_TMS_setup                           | TMS setup before TCK high    |                                                       | T/4        | -   | -                  |       |

| T_TDI_hold                            | TDI, TMS hold after TCK high | T = 1/f_TCK                                           | T/4        | -   | -                  |       |

| T_TDO_valid TCK low to TDO valid      |                              | T = 1/f_TCK                                           | 2T/5       | -   | -                  |       |

| T_TDO_hold                            | TDO hold after TCK high      | T = 1/f_TCK                                           | T/4        | -   | -                  |       |

|                                       | TCK to device outputs valid  |                                                       | _          | -   | 2T/5               |       |

## 11.8.5 SWD Interface

## Table 11-73. SWD Interface AC Specifications<sup>[46]</sup>

| Parameter    | Description                         | Conditions                                                  | Min  | Тур | Max                 | Units |

|--------------|-------------------------------------|-------------------------------------------------------------|------|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \le V_{DDD} \le 5~V$                                 | -    | -   | 14 <sup>[48]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$  | -    | -   | 7 <sup>[48]</sup>   | MHz   |

|              |                                     | 1.71 V $\leq$ V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins | -    | _   | 5.5 <sup>[48]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK                                               | T/4  | -   | -                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK                                               | T/4  | -   | -                   |       |

| T_SWDO_valid | SWDCK low to SWDIO output valid     | T = 1/f_SWDCK                                               | 2T/5 | -   | -                   |       |

| T_SWDO_hold  | SWDIO output hold after SWDCK high  | T = 1/f_SWDCK                                               | T/4  | _   | _                   |       |

#### 11.8.6 SWV Interface

## Table 11-74. SWV Interface AC Specifications<sup>[46]</sup>

| Paramet               | r Description | Conditions | Min | Тур | Мах | Units |

|-----------------------|---------------|------------|-----|-----|-----|-------|

| SWV mode SWV bit rate |               |            | 1   | _   | 33  | Mbit  |

Notes

- 46. Based on device characterization (Not production tested).

- 47. f\_TCK must also be no more than 1/3 CPU clock frequency.

48. f\_SWDCK must also be no more than 1/3 CPU clock frequency.

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym                                 | Description                                                  |  |

|-----------------------------------------|--------------------------------------------------------------|--|

| PGA                                     | programmable gain amplifier                                  |  |

| PHUB                                    | peripheral hub                                               |  |

| PHY                                     | physical layer                                               |  |

| PICU                                    | port interrupt control unit                                  |  |

| PLA                                     | programmable logic array                                     |  |

| PLD                                     | programmable logic device, see also PAL                      |  |

| PLL                                     | phase-locked loop                                            |  |

| PMDD                                    | package material declaration datasheet                       |  |

| POR                                     | power-on reset                                               |  |

| PRES                                    | precise power-on reset                                       |  |

| PRS                                     | pseudo random sequence                                       |  |

| PS                                      | port read data register                                      |  |

| PSoC <sup>®</sup>                       | Programmable System-on-Chip™                                 |  |

| PSRR                                    | power supply rejection ratio                                 |  |

| PWM                                     | pulse-width modulator                                        |  |

| RAM                                     | random-access memory                                         |  |

| RISC                                    | reduced-instruction-set computing                            |  |

| RMS                                     | root-mean-square                                             |  |

| RTC                                     | real-time clock                                              |  |

| RTL                                     | register transfer language                                   |  |

| RTR                                     | remote transmission request                                  |  |

| RX                                      | receive                                                      |  |

| SAR                                     | successive approximation register                            |  |

| SC/CT                                   | witched capacitor/continuous time                            |  |

| SCL                                     | I <sup>2</sup> C serial clock                                |  |

| SDA                                     | I <sup>2</sup> C serial data                                 |  |

| S/H                                     | sample and hold                                              |  |

| SINAD                                   | signal to noise and distortion ratio                         |  |

| SIO                                     | special input/output, GPIO with advanced features. See GPIO. |  |

| SOC                                     | start of conversion                                          |  |

| SOF                                     | start of frame                                               |  |

| SPI                                     | Serial Peripheral Interface, a communications protocol       |  |

| SR                                      | slew rate                                                    |  |

| SRAM                                    | static random access memory                                  |  |

| SRES                                    | software reset                                               |  |

| SWD                                     | serial wire debug, a test protocol                           |  |

| SWV                                     | single-wire viewer                                           |  |

| TD transaction descriptor, see also DMA |                                                              |  |

#### Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                               |

|---------|---------------------------------------------------------------------------|

| THD     | total harmonic distortion                                                 |

| TIA     | transimpedance amplifier                                                  |

| TRM     | technical reference manual                                                |

| TTL     | transistor-transistor logic                                               |

| ТΧ      | transmit                                                                  |

| UART    | Universal Asynchronous Transmitter Receiver, a<br>communications protocol |

| UDB     | universal digital block                                                   |

| USB     | Universal Serial Bus                                                      |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port                 |

| VDAC    | voltage DAC, see also DAC, IDAC                                           |

| WDT     | watchdog timer                                                            |

| WOL     | write once latch, see also NVL                                            |

| WRES    | watchdog timer reset                                                      |

| XRES    | external reset I/O pin                                                    |

| XTAL    | crystal                                                                   |

## **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

## **16. Document Conventions**

- 16.1 Units of Measure

- Table 16-1. Units of Measure

| Symbol                   | Unit of Measure        |

|--------------------------|------------------------|

| °C                       | degrees Celsius        |

| dB                       | decibels               |

| fF                       | femtofarads            |

| Hz                       | hertz                  |

| KB                       | 1024 bytes             |

| kbps                     | kilobits per second    |

| Khr                      | kilohours              |

| kHz                      | kilohertz              |

| kΩ                       | kilohms                |

| ksps                     | kilosamples per second |

| LSB                      | least significant bit  |

| Mbps megabits per second |                        |

| MHz megahertz            |                        |

| MΩ                       | megaohms               |

| Msps                     | megasamples per second |

## 17. Revision History

| Rev. | ECN No. | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 571504  | See ECN            | HMT                | New datasheet for new device Part Number family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *A   | 754416  | See ECN            | HMT                | Prepare Preliminary for PR1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *B   | 2253366 | See ECN            | DSG                | Prepare Preliminary2 for PR3total rewrite.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *C   | 2350209 | See ECN            | DSG                | Minor change: Added "Confidential" watermark. Corrected typo on 68QFN pinout: pin 13 XREF to XRES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *D   | 2481747 | See ECN            | SFV                | Changed part numbers and datasheet title.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *E   | 2521877 | See ECN            | DSG                | Prelim3 release-extensive spec, writing, and formatting changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *F   | 2660161 | 02/16/09           | GDK                | Reorganized content to be consistent with the TRM. Added Xdata Space Access<br>SFRs and DAC sections. Updated Boost Converter section and Conversion<br>Signals section. Classified Ordering Information according to CPU speed;<br>added information on security features and ROHS compliance<br>Added a section on XRES Specifications under Electrical Specification.<br>Updated Analog Subsystem and CY8C35/55 Architecture block diagrams.<br>Updated Electrical Specifications. Renamed CyDesigner as PSoC Creator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |