Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

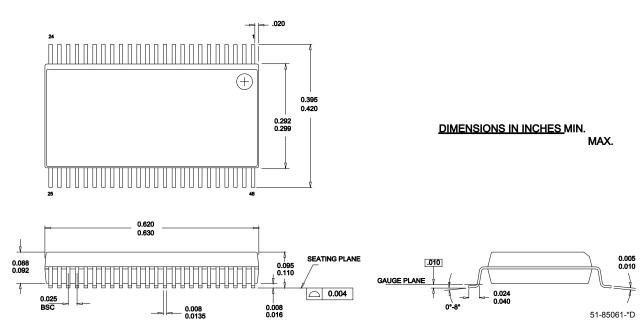

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866axi-038 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in real-time clock (RTC) applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C38 family supports a wide supply operating range from 1.71 V to 5.5 V. This allows operation from regulated supplies such as  $1.8 V \pm 5\%$ ,  $2.5 V \pm 10\%$ ,  $3.3 V \pm 10\%$ , or  $5.0 V \pm 10\%$ , or directly from a wide range of battery types. In addition, it provides an integrated high efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery or solar cell. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3-V supply for LCD glass drive. The boost's output is available on the Vboost pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a  $1-\mu$ A sleep mode with RTC. In the second mode, the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 24 of this datasheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for 'printf' style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 56 of this datasheet.

# 2. Pinouts

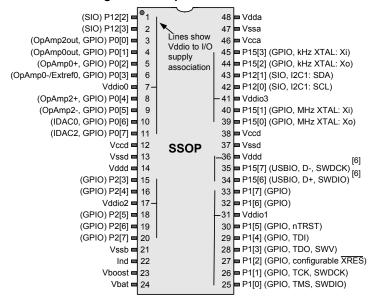

The Vddio pin that supplies a particular set of pins is indicated by the black lines drawn on the pinout diagrams in Figure 2-1 through Figure 2-4. Using the Vddio pins, a single PSoC can support multiple interface voltage levels, eliminating the need for off-chip level shifters. Each Vddio may sink up to 100 mA total to its associated I/O pins and opamps. On the 68-pin and 100-pin devices each set of Vddio associated pins may sink up to 100 mA. The 48-pin device may sink up to 100 mA total for all Vddio0 plus Vddio2 associated I/O pins and 100 mA total for all Vddio1 plus Vddio3 associated I/O pins.

#### Figure 2-1. 48-pin SSOP Part Pinout

Note6. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

### 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

#### Table 4-5. Jump Instructions

| Mnemonic             | Description                                                  | Bytes | Cycles |

|----------------------|--------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                     | 2     | 4      |

| LCALL addr16         | Long subroutine call                                         | 3     | 4      |

| RET                  | Return from subroutine                                       | 1     | 4      |

| RETI                 | Return from interrupt                                        | 1     | 4      |

| AJMP addr11          | Absolute jump                                                | 2     | 3      |

| LJMP addr16          | Long jump                                                    | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                               | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                  | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                               | 2     | 4      |

| CJNE A, Direct, rel  | Compare direct byte to accumulator and jump if not equal     | 3     | 5      |

| CJNE A, #data, rel   | Compare immediate data to accumulator and jump if not equal  | 3     | 4      |

| CJNE Rn, #data, rel  | Compare immediate data to register and jump if not equal     | 3     | 4      |

| CJNE @Ri, #data, rel | Compare immediate data to indirect RAM and jump if not equal | 3     | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                      | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                   | 3     | 5      |

| NOP                  | No operation                                                 | 1     | 1      |

### 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8-, 16-, 24-, and 32-bit addressing and data

#### Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

#### 4.4.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TD) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

#### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

#### Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.4.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location).

#### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

#### 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase 'subchains' can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

# PSoC<sup>®</sup> 3: CY8C38 Family Datasheet

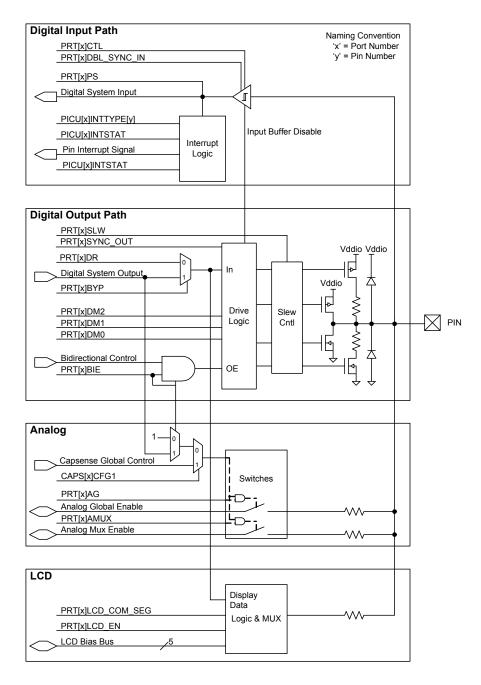

#### Figure 6-8. GPIO Block Diagram

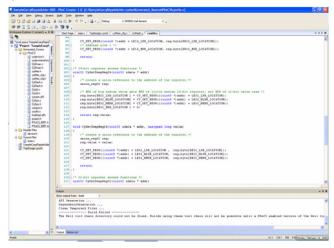

#### 7.1.4.4 Software Development

#### Figure 7-4. Code Editor

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM<sup>®</sup> Limited, Keil<sup>™</sup>, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView<sup>™</sup> compiler.

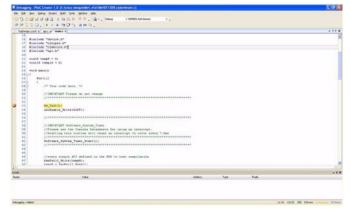

#### 7.1.4.5 Nonintrusive Debugging

#### Figure 7-5. PSoC Creator Debugger

With JTAG (4-wire) and SWD (2-wire) debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals—make for an unparalleled level of visibility into the system.

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

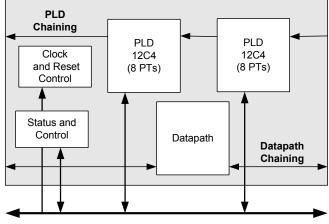

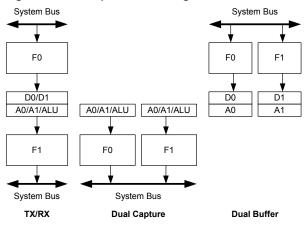

#### 7.2 Universal Digital Block

The UDB represents an evolutionary step to the next generation of PSoC embedded digital peripheral functionality. The architecture in first generation PSoC digital blocks provides coarse programmability in which a few fixed functions with a small number of options are available. The new UDB architecture is the optimal balance between configuration granularity and efficient implementation. A cornerstone of this approach is to provide the ability to customize the devices digital operation to match application requirements.

To achieve this, UDBs consist of a combination of uncommitted logic (PLD), structured logic (Datapath), and a flexible routing scheme to provide interconnect between these elements, I/O connections, and other peripherals. UDB functionality ranges from simple self contained functions that are implemented in one UDB, or even a portion of a UDB (unused resources are available for other functions), to more complex functions that require multiple UDBs. Examples of basic functions are timers, counters, CRC generators, PWMs, dead band generators, and communications functions, such as UARTs, SPI, and I<sup>2</sup>C. Also, the PLD blocks and connectivity provide full featured general purpose programmable logic within the limits of the available resources.

#### Figure 7-6. UDB Block Diagram

Routing Channel

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

#### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

#### 7.2.2.5 Built in CRC/PRS

The datapath has built-in support for single cycle CRC computation and PRS generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

## 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

#### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

#### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

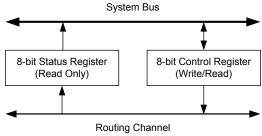

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

#### Figure 7-10. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

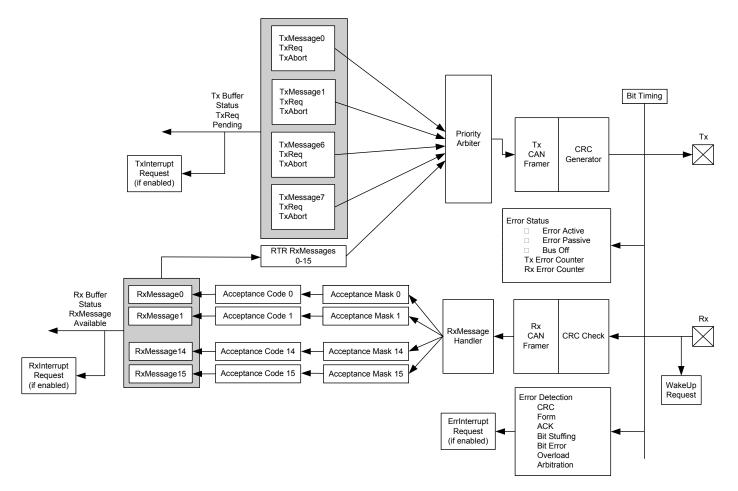

Figure 7-19. CAN Controller Block Diagram

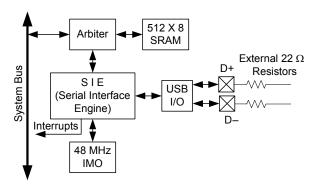

# 7.6 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 28.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual memory management with no DMA access

- Manual memory management with manual DMA access

Automatic memory management with automatic DMA

- access

- Internal 3.3-V regulator for transceiver

- Internal 48-MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB reset, suspend, and resume operations

- Bus-powered and self-powered modes

#### Figure 7-20. USB

# **PSoC<sup>®</sup> 3: CY8C38 Family Datasheet**

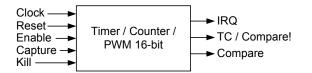

# 7.7 Timers, Counters, and PWMs

The timer/counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in UDBs as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The timer/counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The

Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-21. Timer/Counter/PWM

# 7.8 I<sup>2</sup>C

The I<sup>2</sup>C peripheral provides a synchronous two wire interface designed to interface the PSoC device with a two wire I<sup>2</sup>C serial communication bus. The bus is compliant with Philips 'The I<sup>2</sup>C Specification' version 2.1. Additional I<sup>2</sup>C interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

To eliminate the need for excessive CPU intervention and overhead, I<sup>2</sup>C specific support is provided for status detection and generation of framing bits. I<sup>2</sup>C operates as a slave, a master, or multimaster (Slave and Master). In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions. I<sup>2</sup>C interfaces through the DSI routing and allows direct connections to any GPIO or SIO pins.

$I^2C$  provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup functionality is required,  $I^2C$  pin connections are limited to the two special sets of SIO pins.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps (3.4 Mbps in UDBs)

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

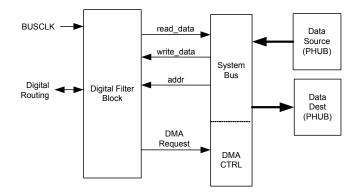

#### 7.9 Digital Filter Block

Some devices in the CY8C38 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one system clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes MCU bandwidth.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

# Figure 7-22. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

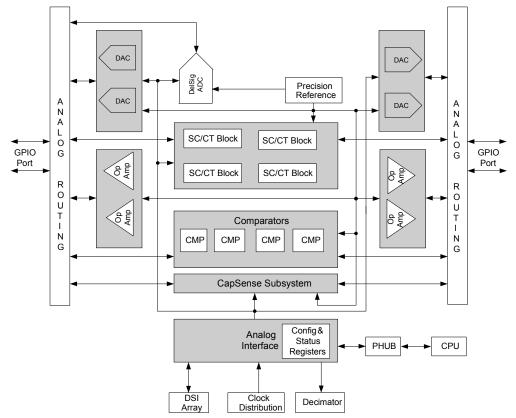

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

Figure 8-1. Analog Subsystem Block Diagram

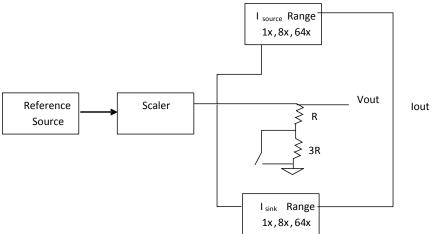

# Figure 8-12. DAC Block Diagram

#### 8.9.1 Current DAC

The current DAC (IDAC) can be configured for the ranges 0 to 32  $\mu$ A, 0 to 256  $\mu$ A, and 0 to 2.048 mA. The IDAC can be configured to source or sink current.

#### 8.9.2 Voltage DAC

For the voltage DAC (VDAC), the current DAC output is routed through resistors. The two ranges available for the VDAC are 0 to 1.024 V and 0 to 4.096 V. In voltage mode any load connected to the output of a DAC should be purely capacitive (the output of the VDAC is not buffered).

#### 8.10 Up/Down Mixer

In continuous time mode, the SC/CT block components are used to build an up or down mixer. Any mixing application contains an input signal frequency and a local oscillator frequency. The polarity of the clock, Fclk, switches the amplifier between inverting or noninverting gain. The output is the product of the input and the switching function from the local oscillator, with frequency components at the local oscillator plus and minus the signal frequency (Fclk + Fin and Fclk – Fin) and reduced-level frequency components at odd integer multiples of the local oscillator frequency. The local oscillator frequency is provided by the selected clock source for the mixer.

Continuous time up and down mixing works for applications with input signals and local oscillator frequencies up to 1 MHz.

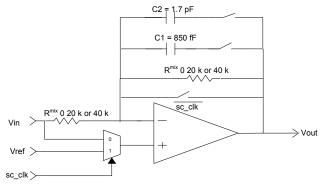

#### Figure 8-13. Mixer Configuration

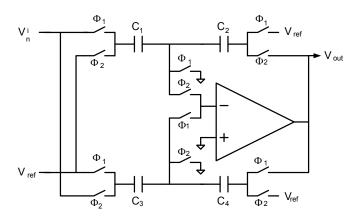

# 8.11 Sample and Hold

The main application for a sample and hold, is to hold a value stable while an ADC is performing a conversion. Some applications require multiple signals to be sampled simultaneously, such as for power calculations (V and I).

# Figure 8-14. Sample and Hold Topology ( $\Phi$ 1 and $\Phi$ 2 are opposite phases of a clock)

# **11.2 Device Level Specifications**

Specifications are valid for –40  $^{\circ}C \le T_A \le 85 ~^{\circ}C$  and  $T_J \le 100 ~^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.2.1 Device Level Specifications

# Table 11-2. DC Specifications

| Parameter                         | Description                                                                                                                                                         | Conditio                                                                                                                                                                                                                                                                                                                                                                    | ons        | Min  | Тур  | Max                              | Units |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|----------------------------------|-------|

| V <sub>DDA</sub>                  | Analog supply voltage and input to analog core regulator                                                                                                            | Analog core regulator er                                                                                                                                                                                                                                                                                                                                                    | nabled     | 1.8  | -    | 5.5                              | V     |

| V <sub>DDA</sub>                  | Analog supply voltage, analog regulator<br>bypassed                                                                                                                 | Analog core regulator di                                                                                                                                                                                                                                                                                                                                                    | sabled     | 1.71 | 1.8  | 1.89                             | V     |

| V <sub>DDD</sub>                  | Digital supply voltage relative to V <sub>SSD</sub>                                                                                                                 | Digital core regulator en                                                                                                                                                                                                                                                                                                                                                   | abled      | 1.8  | -    | V <sub>DDA</sub> <sup>[19]</sup> | V     |

| V <sub>DDD</sub>                  | Digital supply voltage, digital regulator bypassed                                                                                                                  | Digital core regulator dis                                                                                                                                                                                                                                                                                                                                                  | abled      | 1.71 | 1.8  | 1.89                             | V     |

| V <sub>DDIO</sub> <sup>[20]</sup> | I/O supply voltage relative to V <sub>SSIO</sub>                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                             |            | 1.71 | -    | V <sub>DDA</sub> <sup>[19]</sup> | V     |

| V <sub>CCA</sub>                  | Direct analog core voltage input (Analog regulator bypass)                                                                                                          | Analog core regulator di                                                                                                                                                                                                                                                                                                                                                    | sabled     | 1.71 | 1.8  | 1.89                             | V     |

| V <sub>CCD</sub>                  | Direct digital core voltage input (Digital regulator bypass)                                                                                                        | Digital core regulator dis                                                                                                                                                                                                                                                                                                                                                  | abled      | 1.71 | 1.8  | 1.89                             | V     |

| V <sub>BAT</sub>                  | Voltage supplied to boost converter                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                             |            | 0.5  | -    | 5.5                              | V     |

| I <sub>DD</sub> <sup>[21]</sup>   | Active Mode, V <sub>DD</sub> = 1.71 V–5.5 V                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                             |            | 1    | 1    |                                  |       |

|                                   | Bus clock off. Execute from CPU                                                                                                                                     | CPU at 3 MHz                                                                                                                                                                                                                                                                                                                                                                | T = -40 °C | -    | -    | -                                | mA    |

|                                   | instruction buffer. See "Flash Program<br>Memory" on page 18.                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                             | T = 25 °C  | -    | 0.8  | -                                | mA    |

|                                   | Memory on page 18.                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                             | T = 85 °C  | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 6 MHz                                                                                                                                                                                                                                                                                                                                                                | T = -40 °C | _    | -    | _                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 25 °C  | -    | 1.2  | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 85 °C  | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 12 MHz                                                                                                                                                                                                                                                                                                                                                               | T = -40 °C | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 25 °C  | -    | 2.0  | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 85 °C  | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     | $\begin{array}{c} T = 85 \ ^{\circ}\text{C} \\ CPU \text{ at } 12 \text{ MHz} \\ T = -40 \ ^{\circ}\text{C} \\ T = 25 \ ^{\circ}\text{C} \\ T = 85 \ ^{\circ}\text{C} \\ \hline T = 85 \ ^{\circ}\text{C} \\ \hline T = -40 \ ^{\circ}\text{C} \\ T = -40 \ ^{\circ}\text{C} \\ \hline T = 25 \ ^{\circ}\text{C} \\ \hline T = 25 \ ^{\circ}\text{C} \\ \hline \end{array}$ | -          | -    | -    | mA                               |       |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 25 °C  | -    | 3.5  | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 85 °C  | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 48 MHz                                                                                                                                                                                                                                                                                                                                                               | T = -40 °C | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 25 °C  | -    | 6.6  | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 85 °C  | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 62.6 MHz                                                                                                                                                                                                                                                                                                                                                             | T = -40 °C | -    | -    | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 25 °C  | -    | 9.0  | -                                | mA    |

|                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | T = 85 °C  | -    | -    | -                                | mA    |

|                                   | $V_{DD}$ = 3.3 V, T = 25 °C, IMO and bus clock<br>enabled, ILO = 1 kHz, CPU executing from<br>flash and accessing SRAM, all other<br>blocks off, all I/Os tied low. | CPU at 3 MHz                                                                                                                                                                                                                                                                                                                                                                |            | _    | 1.2  | _                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 6 MHz                                                                                                                                                                                                                                                                                                                                                                |            | -    | 1.8  | -                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 12 MHz                                                                                                                                                                                                                                                                                                                                                               |            | -    | 3.2  | -                                | mA    |

|                                   | · · · · · ·                                                                                                                                                         | CPU at 24 MHz                                                                                                                                                                                                                                                                                                                                                               |            | -    | 5.8  | -                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 48 MHz                                                                                                                                                                                                                                                                                                                                                               |            | -    | 12.1 | -                                | mA    |

|                                   |                                                                                                                                                                     | CPU at 62.6 MHz                                                                                                                                                                                                                                                                                                                                                             |            | -    | 15.6 | -                                | mA    |

Notes

The power supplies can be brought up in any sequence however once stable V<sub>DDA</sub> must be greater than or equal to all other supplies.

The V<sub>DDIO</sub> supply voltage must be greater than the maximum analog voltage on the associated GPIO pins. Maximum analog voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>.

The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find CPU current at frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

### Table 11-12. SIO AC Specifications (continued)

| Parameter | Description                                                                                               | Conditions                               | Min | Тур | Max | Units |  |

|-----------|-----------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|--|

|           | SIO output operating frequency                                                                            |                                          |     |     |     |       |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated<br>output (GPIO) mode, fast strong<br>drive mode           | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | _   | 33  | MHz   |  |

|           | 1.71 V < V <sub>DDIO</sub> < 3.3 V,<br>Unregulated output (GPIO) mode,<br>fast strong drive mode          | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | _   | 16  | MHz   |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated<br>output (GPIO) mode, slow strong<br>drive mode           | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 5   | MHz   |  |

| Fsioout   | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode        | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 4   | MHz   |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, fast strong drive<br>mode                    | Output continuously switching into 25 pF | -   | -   | 20  | MHz   |  |

|           | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Regulated<br>output mode, fast strong drive<br>mode                   | Output continuously switching into 25 pF | -   | -   | 10  | MHz   |  |

|           | $1.71 \text{ V} < \text{V}_{\text{DDIO}} < 5.5 \text{ V}$ , Regulated output mode, slow strong drive mode | Output continuously switching into 25 pF | -   | -   | 2.5 | MHz   |  |

| Ecicin    | SIO input operating frequency                                                                             |                                          |     |     |     |       |  |

| Fsioin    | 1.71 V <u>&lt;</u> V <sub>DDIO</sub> <u>&lt;</u> 5.5 V                                                    | 90/10% V <sub>DDIO</sub>                 | -   | -   | 66  | MHz   |  |

# 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 60.

# Table 11-13. USBIO DC Specifications

| Parameter       | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|-----------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi           | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | -   | 1.575          | kΩ    |

| Rusba           | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | -   | 3.090          | kΩ    |

| Vohusb          | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | -   | 3.6            | V     |

| Volusb          | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | -              | -   | 0.3            | V     |

| Vohgpio         | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 V$                 | 2.4            | -   | -              | V     |

| Volgpio         | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 V$                 | -              | -   | 0.3            | V     |

| Vdi             | Differential input sensitivity         | (D+) – (D–)                                        | _              | -   | 0.2            | V     |

| Vcm             | Differential input common mode range   | -                                                  | 0.8            | -   | 2.5            | V     |

| Vse             | Single ended receiver threshold        | -                                                  | 0.8            | -   | 2              | V     |

| Rps2            | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | -   | 7              | kΩ    |

| Rext            | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo              | USB driver output impedance            | Including Rext                                     | 28             | -   | 44             | Ω     |

| C <sub>IN</sub> | USB transceiver input capacitance      | -                                                  | -              | -   | 20             | pF    |

| I <sub>IL</sub> | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | _              | -   | 2              | nA    |

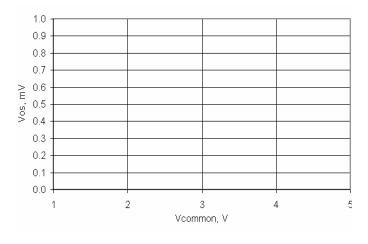

# Figure 11-4. Opamp Voffset vs Common Mode Voltage and Temperature, Power Mode = High

Figure 11-5. Opamp Output Voltage vs Load Current and Temperature, 25 °C, Vdda = 5V

# Table 11-20. 20-bit Delta-sigma ADC DC Specifications (continued)

| Parameter          | Description                                                                                             | Conditions           | Min | Тур | Max  | Units |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------|----------------------|-----|-----|------|-------|--|--|

| Vextref            | ADC external reference input voltage, see<br>also internal reference in Voltage<br>Reference on page 80 | Pins P0[3], P3[2]    | 0.9 | -   | 1.3  | V     |  |  |

| Current Co         | Current Consumption                                                                                     |                      |     |     |      |       |  |  |

| I <sub>DD_20</sub> | Current consumption, 20 bit <sup>[35]</sup>                                                             | 187 sps, unbuffered  | -   | -   | 1.25 | mA    |  |  |

| I <sub>DD_16</sub> | Current consumption, 16 bit <sup>[35]</sup>                                                             | 48 ksps, unbuffered  | -   | -   | 1.2  | mA    |  |  |

| I <sub>DD_12</sub> | Current consumption, 12 bit <sup>[35]</sup>                                                             | 192 ksps, unbuffered | _   | -   | 1.4  | mA    |  |  |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[35]</sup>                                                              |                      | -   | -   | 2.5  | mA    |  |  |

### Table 11-21. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | _   | _   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[35]</sup>                         | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V | _   | -   | 0.0032 | %       |

| 20-Bit Resol | ution Mode                                                        |                                              |     | •   | •      |         |

| SR20         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 7.8 | _   | 187    | sps     |

| BW20         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 40  | _      | Hz      |

| 16-Bit Resol | ution Mode                                                        |                                              |     | •   | •      |         |

| SR16         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 2   | _   | 48     | ksps    |

| BW16         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 11  | -      | kHz     |

| SINAD16int   | Signal to noise ratio, 16-bit, internal reference <sup>[35]</sup> | Range = ±1.024V, unbuffered                  | 81  | -   | -      | dB      |

| SINAD16ext   | Signal to noise ratio, 16-bit, external reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 84  | -   | -      | dB      |

| 12-Bit Resol | ution Mode                                                        |                                              |     | •   | •      |         |

| SR12         | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | -   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 44  | _      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         |                                              |     | •   | •      |         |

| SR8          | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | _   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 88  | -      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[35]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | -   | -      | dB      |

Notes

35. Based on device characterization (Not production tested).

#### 11.5.10 Programmable Gain Amplifier

The PGA is created using a SC/CT analog block; see the PGA component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, operating conditions are:

- Operating temperature = 25 °C for typical values

- Unless otherwise specified, all charts and graphs show typical values

#### Table 11-37. PGA DC Specifications

| Parameter | Description                                 | Conditions                                                                        | Min                    | Тур | Max                     | Units       |

|-----------|---------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-----|-------------------------|-------------|

| Vin       | Input voltage range                         | Power mode = minimum                                                              | Vssa                   | -   | Vdda                    | V           |

| Vos       | Input offset voltage                        | Power mode = high,<br>gain = 1                                                    | -                      | -   | 10                      | mV          |

| TCVos     | Input offset voltage drift with temperature | Power mode = high,<br>gain = 1                                                    | -                      | -   | ±30                     | µV/°C       |

| Ge1       | Gain error, gain = 1                        |                                                                                   | -                      | -   | ±0.15                   | %           |

| Ge16      | Gain error, gain = 16                       |                                                                                   | -                      | -   | ±2.5                    | %           |

| Ge50      | Gain error, gain = 50                       |                                                                                   | -                      | -   | ±5                      | %           |

| Vonl      | DC output nonlinearity                      | Gain = 1                                                                          | -                      | -   | ±0.01                   | % of<br>FSR |

| Cin       | Input capacitance                           |                                                                                   | _                      | _   | 7                       | pF          |

| Voh       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | V <sub>DDA</sub> -0.15 | -   | _                       | V           |

| Vol       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | -                      | -   | V <sub>SSA</sub> + 0.15 | V           |

| Vsrc      | Output voltage under load                   | lload = 250 µA, Vdda ≥ 2.7V, power mode = high                                    | -                      | -   | 300                     | mV          |

| ldd       | Operating current                           | Power mode = high                                                                 | -                      | 1.5 | 1.65                    | mA          |

| PSRR      | Power supply rejection ratio                |                                                                                   | 48                     | -   | _                       | dB          |

Figure 11-43. Voffset Histogram, 1000 Samples, Vdda = 5 V

# 11.5.12 LCD Direct Drive

#### Table 11-40. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                       | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| I <sub>CC</sub>     | LCD system operating current                                                        | Device sleep mode with wakeup at<br>400-Hz rate to refresh LCDs, bus<br>clock = 3 Mhz, Vddio = Vdda = 3 V,<br>4 commons, 16 segments, 1/4 duty<br>cycle, 50 Hz frame rate, no glass<br>connected | -   | 38                     | -    | μΑ    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                                | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | -   | 9.1 × V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                          | -   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                                  | I   | _                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | Vddio = 5.5V, strong drive mode                                                                                                                                                                  | 355 | -                      | 710  | μA    |

### Table 11-41. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

# 11.8.3 Interrupt Controller

# Table 11-71. Interrupt Controller AC Specifications

| Parameter | Description                                                           | Conditions                                                              | Min | Тур | Мах | Units   |

|-----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|---------|

|           | Delay from interrupt signal input to ISR code execution from ISR code | Includes worse case completion of longest instruction DIV with 6 cycles | -   | -   | 25  | Tcy CPU |

# 11.8.4 JTAG Interface

# Table 11-72. JTAG Interface AC Specifications<sup>[46]</sup>

| Parameter   | Description                  | Conditions                                            | Min        | Тур | Max                | Units |

|-------------|------------------------------|-------------------------------------------------------|------------|-----|--------------------|-------|

| f_TCK       | TCK frequency                | $3.3 \text{ V} \le \text{V}_{DDD} \le 5 \text{ V}$    | -          | -   | 14 <sup>[47]</sup> | MHz   |

|             |                              | $1.71 \text{ V} \le \text{V}_{DDD}$ < $3.3 \text{ V}$ | -          | -   | 7 <sup>[47]</sup>  | MHz   |

| T_TDI_setup | TDI setup before TCK high    |                                                       | (T/10) – 5 | -   | -                  | ns    |

| T_TMS_setup | TMS setup before TCK high    |                                                       | T/4        | -   | -                  |       |

| T_TDI_hold  | TDI, TMS hold after TCK high | T = 1/f_TCK                                           | T/4        | -   | -                  |       |

| T_TDO_valid | TCK low to TDO valid         | T = 1/f_TCK                                           | 2T/5       | -   | -                  |       |

| T_TDO_hold  | TDO hold after TCK high      | T = 1/f_TCK                                           | T/4        | -   | -                  |       |

|             | TCK to device outputs valid  |                                                       | _          | -   | 2T/5               |       |

### 11.8.5 SWD Interface

# Table 11-73. SWD Interface AC Specifications<sup>[46]</sup>

| Parameter    | Description                         | Conditions                                                  | Min  | Тур | Max                 | Units |

|--------------|-------------------------------------|-------------------------------------------------------------|------|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \le V_{DDD} \le 5~V$                                 | -    | _   | 14 <sup>[48]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$  | -    | _   | 7 <sup>[48]</sup>   | MHz   |

|              |                                     | 1.71 V $\leq$ V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins | -    | -   | 5.5 <sup>[48]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK                                               | T/4  | -   | -                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK                                               | T/4  | -   | -                   |       |

| T_SWDO_valid | SWDCK low to SWDIO output valid     | T = 1/f_SWDCK                                               | 2T/5 | _   | -                   |       |

| T_SWDO_hold  | SWDIO output hold after SWDCK high  | T = 1/f_SWDCK                                               | T/4  | I   | _                   |       |

#### 11.8.6 SWV Interface

# Table 11-74. SWV Interface AC Specifications<sup>[46]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | 1   | _   | 33  | Mbit  |

Notes

- 46. Based on device characterization (Not production tested).

- 47. f\_TCK must also be no more than 1/3 CPU clock frequency.

48. f\_SWDCK must also be no more than 1/3 CPU clock frequency.

#### Table 11-78. IMO AC Specifications (continued)