Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866axi-054 |

#### 1. Architectural Overview

Introducing the CY8C38 family of ultra low-power, flash Programmable System-on-Chip (PSoC®) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C38 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

Analog Interconnect Digital Interconnect System Wide **Digital System** Universal Digital Block Array (24x UDB) Resources 4 to 33 MHz UDB Xta for USB UDB 8-bit FS USB Osc UDB UDB UDB Clock Example UDB PHY 2.0 bit SPI Time 12-bit SPI Counter Tree UDB UDB UDB UDB UDB **PWM** Usage IMO 32768 KHz UDB RTC System Bus **CPU** System rogram & **Memory System** wnt Debug 8051or Interrupt EEPROM SRAM Program Cortex M3CP Wake Controlle Debug & Trace FLASH PHUR Boundary Scan ILO Clocking Sys GPIOS **Analog System** Digital LCD Direct ADC Opamp POR and 3 per 4 x SC/CT Blocks (TIA, PGA, Mixer etc Sleep Power 1 x Del Sig Temperatur ADC 1.8V LDC Sensor 4 x DAC SMP

Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C38 family. They are:

- 8051 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

- Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, low-power UDBs. PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/programmable logic device (PLD) functionality, together with a small state machine engine to support a wide variety of peripherals.

In addition to the flexibility of the UDB array, PSoC also provides configurable digital blocks targeted at specific functions. For the CY8C38 family these blocks can include four 16-bit timers, counters, and PWM blocks; I<sup>2</sup>C slave, master, and multimaster; FS USB; and Full CAN 2.0b.

# PSoC® 3: CY8C38 Family Datasheet

For more details on the peripherals see the "Example Peripherals" section on page 35 of this datasheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 34 of this datasheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 0.1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

- Digital filter block (DFB)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±2 LSB

- DNL less than ±1 LSB

- SINAD better than 84 dB in 16-bit mode

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors. The output of the ADC can optionally feed the programmable DFB through the DMA without CPU intervention. You can configure the DFB to perform IIR and FIR digital filters and several user-defined custom functions. The DFB can implement filters with up to 64 taps. It can perform a 48-bit multiply-accumulate (MAC) operation in one clock cycle.

Four high-speed voltage or current DACs support 8-bit output signals at an update rate of up to 8 Msps. They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths. In addition to the ADC, DACs, and DFB, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- □ Programmable gain amplifiers

- Mixers

- Other similar analog components

See the "Analog Subsystem" section on page 46 of this datasheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 67 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after POR.

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the Vddio pins. Every GPIO has analog I/O, LCD drive<sup>[4]</sup>, CapSense<sup>[5]</sup>, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow VOH to be set independently of Vddio when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 28 of this datasheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The internal main oscillator (IMO) is the master clock base for the system, and has 1-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 62 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs. The device provides a PLL to generate system clock frequencies up to 67 MHz from the IMO, external crystal, or external reference clock.

#### Notes

- 4. This feature on select devices only. See Ordering Information on page 105 for details.

- 5. GPIOs with opamp outputs are not recommended for use with CapSense.

It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in real-time clock (RTC) applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C38 family supports a wide supply operating range from 1.71 V to 5.5 V. This allows operation from regulated supplies such as 1.8 V  $\pm$  5%, 2.5 V  $\pm$ 10%, 3.3 V  $\pm$  10%, or 5.0 V  $\pm$  10%, or directly from a wide range of battery types. In addition, it provides an integrated high efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery or solar cell. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3-V supply for LCD glass drive. The boost's output is available on the Vboost pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a 1-µA sleep mode with RTC. In the second mode, the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 24 of this datasheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for 'printf' style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 56 of this datasheet.

#### 2. Pinouts

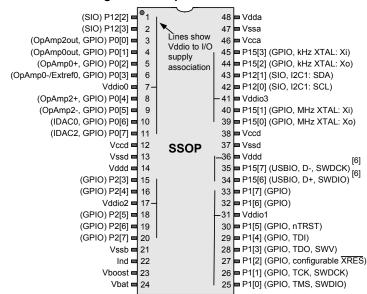

The Vddio pin that supplies a particular set of pins is indicated by the black lines drawn on the pinout diagrams in Figure 2-1 through Figure 2-4. Using the Vddio pins, a single PSoC can support multiple interface voltage levels, eliminating the need for off-chip level shifters. Each Vddio may sink up to 100 mA total to its associated I/O pins and opamps. On the 68-pin and 100-pin devices each set of Vddio associated pins may sink up to 100 mA. The 48-pin device may sink up to 100 mA total for all Vddio0 plus Vddio2 associated I/O pins and 100 mA total for all Vddio1 plus Vddio3 associated I/O pins.

Figure 2-1. 48-pin SSOP Part Pinout

#### Note

<sup>6.</sup> Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

Table 4-3. Data Transfer Instructions (continued)

| Mnemonic           | Description                                            | Bytes | Cycles |

|--------------------|--------------------------------------------------------|-------|--------|

| MOV Direct, Direct | Move direct byte to direct byte                        | 3     | 3      |

| MOV Direct, @Ri    | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV Direct, #data  | Move immediate data to direct byte                     | 3     | 3      |

| MOV @Ri, A         | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV @Ri, Direct    | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV @Ri, #data     | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV DPTR, #data16  | Load data pointer with 16 bit constant                 | 3     | 3      |

| MOVC A, @A+DPTR    | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC A, @A + PC    | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX A,@Ri         | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX A, @DPTR      | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX @Ri, A        | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX @DPTR, A      | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH Direct        | Push direct byte onto stack                            | 2     | 3      |

| POP Direct         | Pop direct byte from stack                             | 2     | 2      |

| XCH A, Rn          | Exchange register with accumulator                     | 1     | 2      |

| XCH A, Direct      | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH A, @Ri         | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD A, @Ri        | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

Table 4-4. Boolean Instructions

| Mnemonic     | Description                             | Bytes | Cycles |

|--------------|-----------------------------------------|-------|--------|

| CLR C        | Clear carry                             | 1     | 1      |

| CLR bit      | Clear direct bit                        | 2     | 3      |

| SETB C       | Set carry                               | 1     | 1      |

| SETB bit     | Set direct bit                          | 2     | 3      |

| CPL C        | Complement carry                        | 1     | 1      |

| CPL bit      | Complement direct bit                   | 2     | 3      |

| ANL C, bit   | AND direct bit to carry                 | 2     | 2      |

| ANL C, /bit  | AND complement of direct bit to carry   | 2     | 2      |

| ORL C, bit   | OR direct bit to carry                  | 2     | 2      |

| ORL C, /bit  | OR complement of direct bit to carry    | 2     | 2      |

| MOV C, bit   | Move direct bit to carry                | 2     | 2      |

| MOV bit, C   | Move carry to direct bit                | 2     | 3      |

| JC rel       | Jump if carry is set                    | 2     | 3      |

| JNC rel      | Jump if no carry is set                 | 2     | 3      |

| JB bit, rel  | Jump if direct bit is set               | 3     | 5      |

| JNB bit, rel | Jump if direct bit is not set           | 3     | 5      |

| JBC bit, rel | Jump if direct bit is set and clear bit | 3     | 5      |

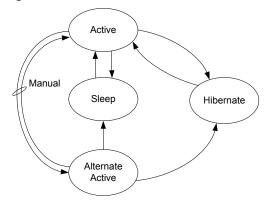

Figure 6-5. Power Mode Transitions

#### 6.2.1.1 Active Mode

Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled or disabled. When a resource is disabled, the digital clocks are gated, analog bias currents are disabled, and leakage currents are reduced as appropriate. User firmware can dynamically control subsystem power by setting and clearing bits in the active configuration template. The CPU can disable itself, in which case the CPU is automatically reenabled at the next wakeup event.

When a wakeup event occurs, the global mode is always returned to active, and the CPU is automatically enabled, regardless of its template settings. Active mode is the default global power mode upon boot.

#### 6.2.1.2 Alternate Active Mode

Alternate Active mode is very similar to Active mode. In alternate active mode, fewer subsystems are enabled, to reduce power consumption. One possible configuration is to turn off the CPU and flash, and run peripherals at full speed.

#### 6.2.1.3 Sleep Mode

Sleep mode reduces power consumption when a resume time of  $15 \mu s$  is acceptable. The wake time is used to ensure that the regulator outputs are stable enough to directly enter active mode.

#### 6.2.1.4 Hibernate Mode

In hibernate mode nearly all of the internal functions are disabled. Internal voltages are reduced to the minimal level to keep vital systems alive. Configuration state is preserved in hibernate mode and SRAM memory is retained. GPIOs configured as digital outputs maintain their previous values and external GPIO pin interrupt settings are preserved. The device can only return from hibernate mode in response to an external I/O interrupt. The resume time from hibernate mode is less than 100 µs.

#### 6.2.1.5 Wakeup Events

Wakeup events are configurable and can come from an interrupt or device reset. A wakeup event restores the system to active mode. Firmware enabled interrupt sources include internally generated interrupts, power supervisor, central timewheel, and I/O interrupts. Internal interrupt sources can come from a variety of peripherals, such as analog comparators and UDBs. The

central timewheel provides periodic interrupts to allow the system to wake up, poll peripherals, or perform real-time functions. Reset event sources include the external reset I/O pin (XRES), WDT, and precision reset (PRES).

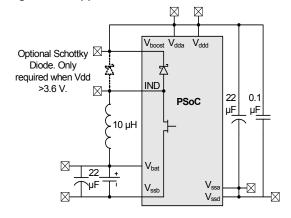

#### 6.2.2 Boost Converter

Applications that use a supply voltage of less than 1.71 V, such as solar or single cell battery supplies, may use the on-chip boost converter. The boost converter may also be used in any system that requires a higher operating voltage than the supply provides. For instance, this includes driving 5.0 V LCD glass in a 3.3 V system. The boost converter accepts an input voltage as low as 0.5 V. With one low cost inductor it produces a selectable output voltage sourcing enough current to operate the PSoC and other on-board components.

The boost converter accepts an input voltage from 0.5 V to 5.5 V (V<sub>BAT</sub>), and can start up with Vbat as low as 0.5 V. The converter provides a user configurable output voltage of 1.8 to 5.0 V (Vboost). Vbat is typically less than Vboost; if Vbat is greater than or equal to Vboost, then Vboost will be the same as Vbat. The block can deliver up to 50 mA (I<sub>BOOST</sub>) depending on configuration.

Four pins are associated with the boost converter: Vbat, Vssb, Vboost, and Ind. The boosted output voltage is sensed at the Vboost pin and must be connected directly to the chip's supply inputs. An inductor is connected between the Vbat and Ind pins. You can optimize the inductor value to increase the boost converter efficiency based on input voltage, output voltage, current and switching frequency. The External Schottky diode shown in Figure 6-6 is required only in cases when Vboost > 3.6 V

Figure 6-6. Application for Boost Converter

The switching frequency can be set to 100 kHz, 400 kHz, 2 MHz, or 32 kHz to optimize efficiency and component cost. The 100 kHz, 400 kHz, and 2 MHz switching frequencies are generated using oscillators internal to the boost converter block. When the 32-kHz switching frequency is selected, the clock is derived from a 32 kHz external crystal oscillator. The 32-kHz external clock is primarily intended for boost standby mode.

At 2 MHz the Vboost output is limited to 2  $\times$  Vbat, and at 400 kHz Vboost is limited to 4  $\times$  Vbat.

The boost converter can be operated in two different modes: active and standby. Active mode is the normal mode of operation where the boost regulator actively generates a regulated output

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt

Interrupt circuits are available to detect when Vdda and Vddd go outside a voltage range. For AHVI, Vdda is compared to a fixed trip level. For ALVI and DLVI, Vdda and Vddd are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply           | Normal<br>Voltage<br>Range | Available Trip<br>Settings               | Accuracy |

|-----------|------------------|----------------------------|------------------------------------------|----------|

| DLVI      | V <sub>DDD</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| ALVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| AHVI      | $V_{DDA}$        | 1.71 V-5.5 V               | 5.75 V                                   | ±2%      |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

#### 6.3.1.2 Other Reset Sources

#### ■ XRES – External reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

#### ■ SRFS – Software reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

#### ■ DRES – Digital logic reset

A logic signal can be routed from the UDBs or other digital peripheral source through the DSI to the Configurable XRES pin, P1[2], to generate a hardware-controlled reset. The pin must be placed in XRES mode. The response to a DRES is the same as after an IPOR reset.

#### ■ WRES – Watchdog timer reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

#### Note

14. GPIOs with opamp outputs are not recommended for use with CapSense.

#### 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the Vddio pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[14]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of V<sub>DDA</sub> and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- □ Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- □ Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[14]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating  $V_{DD}$ )

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- □ Highest drive strength for general purpose use

- Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- □ Digital output (CMOS) drive mode

- □ Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

# PSoC® 3: CY8C38 Family Datasheet

#### 7.1 Example Peripherals

The flexibility of the CY8C38 family's UDBs and analog blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog, however, users may also create their own custom components using PSoC Creator. Using PSoC Creator, users may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the datasheet, and the list is always growing. An example of a component available for use in CY8C38 family, but, not explicitly called out in this datasheet is the UART component.

#### 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- □ I<sup>2</sup>C

- □ UART

- □ SPI

- Functions

- EMIF

- □ PWMs

- □ Timers

- Counters

- Logic

- □ NOT

- □ OR

- XOR

- AND

#### 7.1.2 Example Analog Components

The following is a sample of the analog components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Amplifiers

- □ TIA

- □ PGA

- opamp

- ADC

- Delta-sigma

- DACs

- Current

- Voltage

- □ PWM

- Comparators

- Mixers

#### 7.1.3 Example System Function Components

The following is a sample of the system function components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, DFB taps, SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- CapSense

- LCD drive

- LCD control

- Filters

#### 7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

#### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

#### 7.2.2.5 Built in CRC/PRS

The datapath has built-in support for single cycle CRC computation and PRS generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

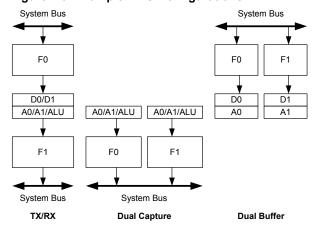

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

Figure 7-9. Example FIFO Configurations

#### 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

#### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

#### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

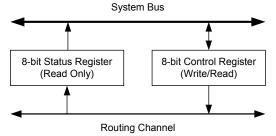

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

Figure 7-10. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

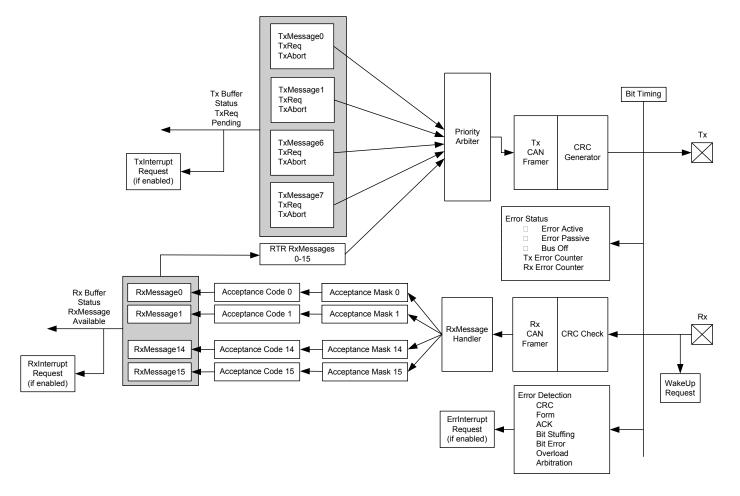

Figure 7-19. CAN Controller Block Diagram

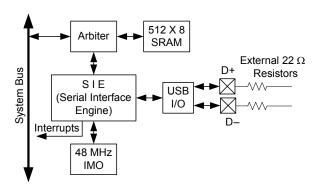

#### 7.6 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 28.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual memory management with no DMA access

- Manual memory management with manual DMA access

- Automatic memory management with automatic DMA access

- Internal 3.3-V regulator for transceiver

- Internal 48-MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB reset, suspend, and resume operations

- Bus-powered and self-powered modes

#### Figure 7-20. USB

# PSoC® 3: CY8C38 Family Datasheet

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to configure the various analog blocks to perform application specific functions (PGA, transimpedance amplifier, voltage DAC, current DAC, and so on). The tool also generates API interface libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

#### 8.1 Analog Routing

The CY8C38 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

#### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

#### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C38 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C38, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2 on page 48.

#### 11.3 Power Regulators

Specifications are valid for  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$  and  $T_J \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.3.1 Digital Core Regulator

#### Table 11-4. Digital Core Regulator DC Specifications

| Parameter | Description                | Conditions                                                                                                                                          | Min | Тур  | Max | Units |

|-----------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| $V_{DDD}$ | Input voltage              |                                                                                                                                                     | 1.8 | _    | 5.5 | V     |

| $V_{CCD}$ | Output voltage             |                                                                                                                                                     | -   | 1.80 | _   | V     |

|           | Regulator output capacitor | ±10%, X5R ceramic or better. The two V <sub>CCD</sub> pins must be shorted together, with as short a trace as possible, see Power System on page 24 | I   | 1    | _   | μF    |

#### 11.3.2 Analog Core Regulator

#### Table 11-5. Analog Core Regulator DC Specifications

| Parameter | Description                | Conditions                  | Min | Тур  | Max | Units |

|-----------|----------------------------|-----------------------------|-----|------|-----|-------|

| $V_{DDA}$ | Input voltage              |                             | 1.8 | _    | 5.5 | V     |

| $V_{CCA}$ | Output voltage             |                             | _   | 1.80 | _   | V     |

|           | Regulator output capacitor | ±10%, X5R ceramic or better | _   | 1    | _   | μF    |

#### 11.3.3 Inductive Boost Regulator.

#### Table 11-6. Inductive Boost Regulator DC Specifications

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 2.4 V,  $V_{OUT}$  = 2.7 V,  $I_{OUT}$  = 40 mA,  $F_{SW}$  = 400 kHz,  $L_{BOOST}$  = 22  $\mu$ H,  $C_{BOOST}$  = 22  $\mu$ F || 0.1  $\mu$ F

| Parameter        | Description                      | Conditions                                                                     | Min  | Тур | Max | Units |

|------------------|----------------------------------|--------------------------------------------------------------------------------|------|-----|-----|-------|

| V <sub>BAT</sub> | Input voltage                    | T=-35 °C to +65 °C                                                             | 0.5  | -   | 5.5 | V     |

|                  | Includes startup                 | Over entire temperature range                                                  | 0.68 | -   | 5.5 | V     |

| Гоит             | Load current <sup>[25, 26]</sup> | V <sub>BAT</sub> = 1.6 – 3.6 V, V <sub>OUT</sub> = 3.6 – 5.0 V, external diode |      | _   | 50  | mA    |

|                  |                                  | $V_{BAT}$ = 1.6 – 3.6 V, $V_{OUT}$ = 1.6 – 3.6 V, internal diode               | _    | -   | 75  | mA    |

|                  |                                  | $V_{BAT} = 0.8 - 1.6 \text{ V}, V_{OUT} = 1.6 - 3.6 \text{ V},$ internal diode | _    | _   | 30  | mA    |

|                  |                                  | V <sub>BAT</sub> = 0.8 – 1.6 V, V <sub>OUT</sub> = 3.6 – 5.0 V, external diode | _    | _   | 20  | mA    |

|                  |                                  | $V_{BAT} = 0.5 - 0.8 \text{ V}, V_{OUT} = 1.6 - 3.6 \text{ V},$ internal diode | _    | _   | 15  | mA    |

| I <sub>LPK</sub> | Inductor peak current            |                                                                                | _    | _   | 700 | mA    |

| IQ               | Quiescent current                | Boost active mode                                                              | _    | 200 | _   | μΑ    |

|                  |                                  | Boost standby mode, 32 khz external crystal oscillator, $I_{OUT}$ < 1 $\mu A$  | _    | 12  | _   | μΑ    |

<sup>25.</sup> For output voltages above 3.6 V, an external diode is required.

26. Maximum output current applies for output voltages ≤ 4x input voltage.

#### **Table 11-6. Inductive Boost Regulator DC Specifications** (continued)

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 2.4 V,  $V_{OUT}$  = 2.7 V,  $I_{OUT}$  = 40 mA,  $F_{SW}$  = 400 kHz,  $L_{BOOST}$  = 22  $\mu$ H,  $C_{BOOST}$  = 22  $\mu$ F || 0.1  $\mu$ F

| Parameter           | Description                             | Conditions                 | Min  | Тур  | Max  | Units |  |  |

|---------------------|-----------------------------------------|----------------------------|------|------|------|-------|--|--|

| V <sub>OUT</sub>    | Boost voltage range <sup>[27, 28]</sup> |                            |      |      |      |       |  |  |

|                     | 1.8 V                                   |                            | 1.71 | 1.80 | 1.89 | V     |  |  |

|                     | 1.9 V                                   |                            | 1.81 | 1.90 | 2.00 | V     |  |  |

|                     | 2.0 V                                   |                            | 1.90 | 2.00 | 2.10 | V     |  |  |

|                     | 2.4 V                                   |                            | 2.28 | 2.40 | 2.52 | V     |  |  |

|                     | 2.7 V                                   |                            | 2.57 | 2.70 | 2.84 | V     |  |  |

|                     | 3.0 V                                   |                            | 2.85 | 3.00 | 3.15 | V     |  |  |

|                     | 3.3 V                                   |                            | 3.14 | 3.30 | 3.47 | V     |  |  |

|                     | 3.6 V                                   |                            | 3.42 | 3.60 | 3.78 | V     |  |  |

|                     | 5.0 V                                   | External diode required    | 4.75 | 5.00 | 5.25 | V     |  |  |

| Reg <sub>LOAD</sub> | Load regulation                         |                            | _    | -    | 3.8  | %     |  |  |

| Reg <sub>LINE</sub> | Line regulation                         |                            | _    | _    | 4.1  | %     |  |  |

| ηουτ                | Efficiency                              | L <sub>BOOST</sub> = 10 μH | 70   | 85   | _    | %     |  |  |

|                     |                                         | L <sub>BOOST</sub> = 22 μH | 82   | 90   | _    | %     |  |  |

#### Table 11-7. Inductive Boost Regulator AC Specifications

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 2.4 V,  $V_{OUT}$  = 2.7 V,  $I_{OUT}$  = 40 mA,  $F_{SW}$  = 400 kHz,  $L_{BOOST}$  = 22  $\mu$ H,  $C_{BOOST}$  = 22  $\mu$ F || 0.1  $\mu$ F.

| Parameter           | Description                   | Conditions                                                                    | Min | Тур               | Max | Units |

|---------------------|-------------------------------|-------------------------------------------------------------------------------|-----|-------------------|-----|-------|

| V <sub>RIPPLE</sub> | Ripple voltage (peak-to-peak) | V <sub>OUT</sub> = 1.8 V, F <sub>SW</sub> = 400 kHz, I <sub>OUT</sub> = 10 mA | -   | _                 | 100 | mV    |

| F <sub>SW</sub>     | Switching frequency           |                                                                               | -   | 0.1, 0.4,<br>or 2 | _   | MHz   |

#### Table 11-8. Recommended External Components for Boost Circuit

| Parameter          | Description                                     | Conditions                                                       | Min | Тур | Max | Units |

|--------------------|-------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| L <sub>BOOST</sub> | Boost inductor                                  |                                                                  | 4.7 | 10  | 47  | μΗ    |

| C <sub>BOOST</sub> | Filter capacitor <sup>[27]</sup>                |                                                                  | 10  | 22  | 47  | μF    |

| I <sub>F</sub>     | External Schottky diode average forward current | External Schottky diode is required for V <sub>OUT</sub> > 3.6 V | 1   | 1   | ı   | A     |

| V <sub>R</sub>     |                                                 |                                                                  | 20  | _   | _   | V     |

#### Notes

Document Number: 001-11729 Rev. \*Q Page 64 of 117

<sup>27.</sup> Based on device characterization (Not production tested).

<sup>28.</sup> At boost frequency of 2 MHz, Vboost is limited to 2 x Vbat. At 400 kHz, Vboost is limited to 4 x Vbat.

# PSoC® 3: CY8C38 Family Datasheet

#### 11.4 Inputs and Outputs

Specifications are valid for  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$  and  $T_J \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.4.1 GPIO

#### Table 11-9. GPIO DC Specifications

| Parameter       | Description                                                   | Conditions                                               | Min                     | Тур | Max                     | Units |

|-----------------|---------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----|-------------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  | CMOS Input, PRT[×]CTL = 0                                | $0.7 \times V_{DDIO}$   | _   | _                       | V     |

| $V_{IL}$        | Input voltage low threshold                                   | CMOS Input, PRT[×]CTL = 0                                | _                       | -   | $0.3 \times V_{DDIO}$   | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[×]CTL = 1,<br>V <sub>DDIO</sub> < 2.7 V | 0.7 × V <sub>DDIO</sub> | _   | _                       | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[×]CTL = 1,<br>$V_{DDIO} \ge 2.7V$       | 2.0                     | _   | _                       | V     |

| $V_{IL}$        | Input voltage low threshold                                   | LVTTL Input, PRT[×]CTL = 1,<br>V <sub>DDIO</sub> < 2.7 V | _                       | _   | 0.3 × V <sub>DDIO</sub> | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7V$ | _                       | _   | 0.8                     | V     |

| V <sub>OH</sub> | Output voltage high                                           | $I_{OH}$ = 4 mA at 3.3 $V_{DDIO}$                        | V <sub>DDIO</sub> – 0.6 | _   | _                       | V     |

|                 |                                                               | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>          | V <sub>DDIO</sub> – 0.5 | _   | _                       | V     |

| $V_{OL}$        | Output voltage low                                            | $I_{OL}$ = 8 mA at 3.3 $V_{DDIO}$                        | _                       | -   | 0.6                     | V     |

|                 |                                                               | $I_{OL}$ = 4 mA at 1.8 $V_{DDIO}$                        | _                       | -   | 0.6                     | V     |

| Rpullup         | Pull-up resistor                                              |                                                          | 3.5                     | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                            |                                                          | 3.5                     | 5.6 | 8.5                     | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value)[29]                    | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | _   | 2                       | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[29]</sup>                             | GPIOs without opamp outputs                              | _                       | _   | 7                       | pF    |

|                 |                                                               | GPIOs with opamp outputs                                 | _                       | _   | 18                      | pF    |

| $V_{H}$         | Input voltage hysteresis (Schmitt-Trigger)[29]                |                                                          | _                       | 40  | _                       | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |                                                          | -                       | _   | 100                     | μΑ    |

| Rglobal         | Resistance pin to analog global bus                           | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | 320 | _                       | Ω     |

| Rmux            | Resistance pin to analog mux bus                              | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | 220 | -                       | Ω     |

#### Table 11-10. GPIO AC Specifications

| Parameter | Description                                                                             | Conditions                            | Min | Тур | Max                  | Units |

|-----------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|----------------------|-------|

| TriseF    | Rise time in Fast Strong Mode <sup>[29]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | _   | 12                   | ns    |

| TfallF    | Fall time in Fast Strong Mode <sup>[29]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | _   | 12                   | ns    |

| TriseS    | Rise time in Slow Strong Mode <sup>[29]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | _   | 60                   | ns    |

| TfallS    | Fall time in Slow Strong Mode <sup>[29]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | _   | 60                   | ns    |

|           | GPIO output operating frequency                                                         |                                       |     |     |                      |       |

|           | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | _   | 33                   | MHz   |

| Fgpioout  | 1.71 V $\leq$ V <sub>DDIO</sub> $<$ 3.3 V, fast strong drive mode                       | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | _   | 20                   | MHz   |

|           | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | _   | 12<br>12<br>60<br>60 | MHz   |

|           | 1.71 $V \le V_{DDIO} < 3.3 V$ , slow strong drive mode                                  | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | _   |                      | MHz   |

| Fgpioin   | GPIO input operating frequency                                                          |                                       | •   |     |                      | •     |

| т дріопт  | 1.71 V ≤ V <sub>DDIO</sub> ≤ 5.5 V                                                      | 90/10% V <sub>DDIO</sub>              | _   | _   | 66                   | MHz   |

Note

29. Based on device characterization (Not production tested).

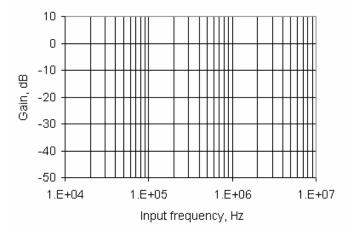

Table 11-38. PGA AC Specifications

| Parameter      | Description         | Conditions                                                     | Min | Тур | Max | Units     |

|----------------|---------------------|----------------------------------------------------------------|-----|-----|-----|-----------|

| BW1            | -3 dB bandwidth     | Power mode = high,<br>gain = 1, input = 100 mV<br>peak-to-peak | 6.7 | 8   | -   | MHz       |

| SR1            | Slew rate           | Power mode = high,<br>gain = 1, 20% to 80%                     | 3   | _   | -   | V/µs      |

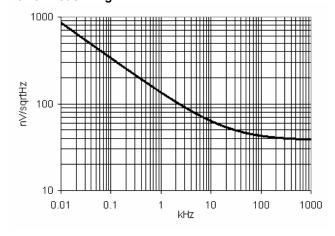

| e <sub>n</sub> | Input noise density | Power mode = high,<br>Vdda = 5 V, at 100 kHz                   | -   | 43  | ı   | nV/sqrtHz |

Figure 11-44. Gain vs. Frequency, at Different Gain Settings, Vdda = 3.3 V, Power Mode = High

Figure 11-46. Noise vs. Frequency, Vdda = 5 V, Power Mode = High

#### 11.5.11 Temperature Sensor

Table 11-39. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: -40 °C to +85 °C | 1   | ±5  | _   | °C    |

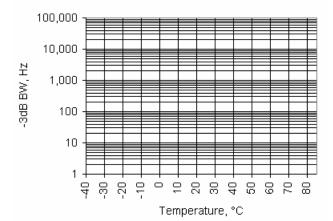

Figure 11-45. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High

Tcp/2 EM\_Clock Tceld Tcehd EM\_CEn Taddriv Taddrv EM\_Addr Address Tweld Twehd EM\_WEn Tdh EM\_Data Data Tadschd Tadscld EM\_ADSCn

Figure 11-51. Synchronous Write Cycle Timing

Table 11-66. Synchronous Write Cycle Specifications

| Parameter | Description                       | Conditions   | Min     | Тур | Max | Units |

|-----------|-----------------------------------|--------------|---------|-----|-----|-------|

| Т         | EMIF clock Period <sup>[45]</sup> | Vdda ≥ 3.3 V | 30.3    | _   | _   | nS    |

| Tcp/2     | EM_Clock pulse high               |              | T/2     | _   | _   | nS    |

| Tceld     | EM_CEn low to EM_Clock high       |              | 5       | _   | _   | nS    |

| Tcehd     | EM_Clock high to EM_CEn high      |              | T/2 – 5 | _   | _   | nS    |

| Taddrv    | EM_Addr valid to EM_Clock high    |              | 5       | _   | _   | nS    |

| Taddriv   | EM_Clock high to EM_Addr invalid  |              | T/2 – 5 | _   | _   | nS    |

| Tweld     | EM_WEn low to EM_Clock high       |              | 5       | _   | _   | nS    |

| Twehd     | EM_Clock high to EM_WEn high      |              | T/2 – 5 | _   | _   | nS    |

| Tds       | Data valid before EM_Clock high   |              | 5       | _   | _   | nS    |

| Tdh       | Data invalid after EM_Clock high  |              | Т       | _   | _   | nS    |

| Tadscld   | EM_ADSCn low to EM_Clock high     |              | 5       | _   | _   | nS    |

| Tadschd   | EM_Clock high to EM_ADSCn high    |              | T/2 – 5 | _   | _   | nS    |

#### Note

<sup>45.</sup> Limited by GPIO output frequency, see Table 11-10 on page 65.

#### 11.8 PSoC System Resources

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.8.1 POR with Brown Out

For brown out detect in regulated mode,  $V_{DDD}$  and  $V_{DDA}$  must be  $\geq 2.0$  V. Brown out detect is not available in externally regulated mode

Table 11-67. Precise Power On Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

|           | Precise POR (PPOR)   |              |      |     |      |       |

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | _   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | _   | 1.66 | V     |

#### Table 11-68. Power On Reset (POR) with Brown Out AC Specifications

| Parameter | Description   | Conditions | Min | Тур | Max | Units |

|-----------|---------------|------------|-----|-----|-----|-------|

| PRES_TR   | Response time |            | _   | _   | 0.5 | μs    |

#### 11.8.2 Voltage Monitors

#### Table 11-69. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Max  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            |      |      |      |       |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

#### Table 11-70. Voltage Monitors AC Specifications

| Parameter | Description   | Conditions | Min | Тур | Max | Units |

|-----------|---------------|------------|-----|-----|-----|-------|

|           | Response time |            | _   | _   | 1   | μs    |

Document Number: 001-11729 Rev. \*Q Page 100 of 117

#### 11.8.3 Interrupt Controller

#### Table 11-71. Interrupt Controller AC Specifications

| Parameter | Description                                                           | Conditions                                                              | Min | Тур | Max | Units   |

|-----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|---------|

|           | Delay from interrupt signal input to ISR code execution from ISR code | Includes worse case completion of longest instruction DIV with 6 cycles | -   | 1   | 25  | Tcy CPU |

#### 11.8.4 JTAG Interface

### Table 11-72. JTAG Interface AC Specifications<sup>[46]</sup>

| Parameter   | Description                  | Conditions                                           | Min        | Тур | Max                | Units |

|-------------|------------------------------|------------------------------------------------------|------------|-----|--------------------|-------|

| f_TCK       | TCK frequency                | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$ | _          | _   | 14 <sup>[47]</sup> | MHz   |

|             |                              | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                    | _          | _   | 7 <sup>[47]</sup>  | MHz   |

| T_TDI_setup | TDI setup before TCK high    |                                                      | (T/10) - 5 | -   | -                  | ns    |

| T_TMS_setup | TMS setup before TCK high    |                                                      | T/4        | -   | -                  |       |

| T_TDI_hold  | TDI, TMS hold after TCK high | T = 1/f_TCK                                          | T/4        | _   | _                  |       |

| T_TDO_valid | TCK low to TDO valid         | T = 1/f_TCK                                          | 2T/5       | -   | -                  |       |

| T_TDO_hold  | TDO hold after TCK high      | T = 1/f_TCK                                          | T/4        | -   | -                  |       |

|             | TCK to device outputs valid  |                                                      | _          | -   | 2T/5               |       |

#### 11.8.5 SWD Interface

### Table 11-73. SWD Interface AC Specifications<sup>[46]</sup>

| Parameter    | Description                         | Conditions                                                               | Min  | Тур | Max                 | Units |

|--------------|-------------------------------------|--------------------------------------------------------------------------|------|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$                     | _    | _   | 14 <sup>[48]</sup>  | MHz   |

|              |                                     | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                                        | -    | _   | 7 <sup>[48]</sup>   | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{DDD} < 3.3 \text{ V},$ SWD over USBIO pins | _    | _   | 5.5 <sup>[48]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK                                                            | T/4  | _   | _                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK                                                            | T/4  | _   | _                   |       |

| T_SWDO_valid | SWDCK low to SWDIO output valid     | T = 1/f_SWDCK                                                            | 2T/5 | _   | _                   |       |

| T_SWDO_hold  | SWDIO output hold after SWDCK high  | T = 1/f_SWDCK                                                            | T/4  | _   | _                   |       |

#### 11.8.6 SWV Interface

#### Table 11-74. SWV Interface AC Specifications<sup>[46]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | -   | -   | 33  | Mbit  |

#### Notes

46. Based on device characterization (Not production tested).

47. f\_TCK must also be no more than 1/3 CPU clock frequency.

48. f\_SWDCK must also be no more than 1/3 CPU clock frequency.

Document Number: 001-11729 Rev. \*Q

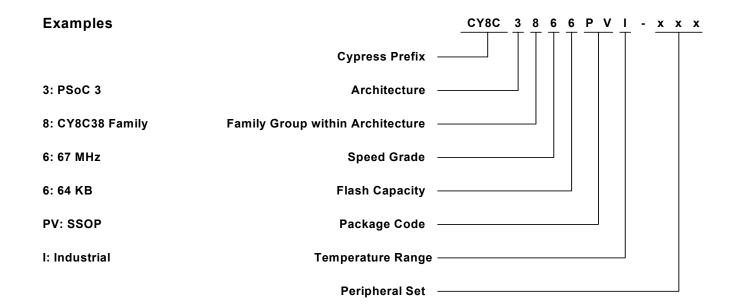

#### 12. Ordering Information

In addition to the features listed in Table 12-1, every CY8C38 device includes: a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C38 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

Table 12-1. CY8C38 Family with Single Cycle 8051

|                 |                 | <b>VCII</b> | Cor       | re .        |                   |                | Δn  | alog       |                                        |        |     |          |                      | Dic              | ital   |          |           | I/O  | [56] |       |              |                         |

|-----------------|-----------------|-------------|-----------|-------------|-------------------|----------------|-----|------------|----------------------------------------|--------|-----|----------|----------------------|------------------|--------|----------|-----------|------|------|-------|--------------|-------------------------|

|                 |                 | 1           | 1         | 1           | a)                | Π              |     | l          |                                        |        |     | 1        |                      | يا ت             | jitai  | 1        |           | 1,0  |      | 1     |              |                         |

| Part Number     | CPU Speed (MHz) | Flash (KB)  | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT<br>Analog Blocks <sup>[54]</sup> | Opamps | DFB | CapSense | UDBs <sup>[55]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O | GPIO | SIO  | USBIO | Package      | JTAG ID <sup>[57]</sup> |

| 32 KB Flash     |                 |             |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |       |              |                         |

| CY8C3865AXI-056 | 67              | 32          | 4         | 1           | _                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | _      | _        | 70        | 62   | 8    | 0     | 100-pin TQFP | 0×0E038069              |

| CY8C3865LTI-045 | 67              | 32          | 4         | 1           | _                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | -      | -        | 46        | 38   | 8    | 0     | 68-pin QFN   | 0×0E02D069              |

| CY8C3865LTI-058 | 67              | 32          | 4         | 1           | _                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | _      | _        | 29        | 25   | 4    | 0     | 48-pin QFN   | 0×0E03A069              |

| CY8C3865PVI-051 | 67              | 32          | 4         | 1           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin SSOP  | 0×0E033069              |

| CY8C3865AXI-015 | 67              | 32          | 4         | 1           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0×0E00F069              |

| CY8C3865LTI-032 | 67              | 32          | 4         | 1           | _                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | ~      | _        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0×0E020069              |

| CY8C3865LTI-061 | 67              | 32          | 4         | 1           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin QFN   | 0×0E03D069              |

| CY8C3865PVI-053 | 67              | 32          | 4         | 1           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin SSOP  | 0×0E035069              |

| CY8C3865AXI-018 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | -      | -        | 70        | 62   | 8    | 0     | 100-pin TQFP | 0×0E012069              |

| CY8C3865LTI-024 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | _      | _        | 46        | 38   | 8    | 0     | 68-pin QFN   | 0×0E018069              |

| CY8C3865LTI-059 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin QFN   | 0×0E03B069              |

| CY8C3865PVI-060 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin SSOP  | 0×0E03C069              |

| CY8C3865AXI-019 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0×0E013069              |

| CY8C3865LTI-014 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 20                   | 4                | ~      | -        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0×0E00E069              |

| CY8C3865LTI-062 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin QFN   | 0×0E03E069              |

| CY8C3865PVI-063 | 67              | 32          | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin SSOP  | 0×0E03F069              |

| 64 KB Flash     |                 |             |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |       |              |                         |

| CY8C3866AXI-054 | 67              | 64          | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 24                   | 4                | _      | -        | 70        | 62   | 8    | 0     | 100-pin TQFP | 0×0E036069              |

| CY8C3866LTI-020 | 67              | 64          | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ~        | 24                   | 4                | -      | -        | 46        | 38   | 8    | 0     | 68-pin QFN   | 0×0E014069              |

| CY8C3866LTI-064 | 67              | 64          | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 24                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin QFN   | 0×0E040069              |

| CY8C3866PVI-005 | 67              | 64          | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 24                   | 4                | _      | -        | 29        | 25   | 4    | 0     | 48-pin SSOP  | 0×0E005069              |