Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866lti-064 |

#### Notes

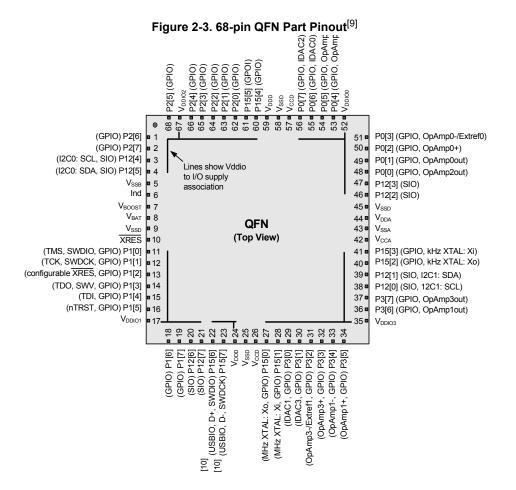

10. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

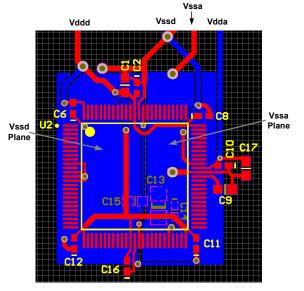

<sup>9.</sup> The center pad on the QFN package should be connected to digital ground (V<sub>SSD</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal.

Figure 2-6. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

#### 3. Pin Descriptions

IDAC0, IDAC1, IDAC2, IDAC3

Low resistance output pin for high current DACs (IDAC).

OpAmp0out, OpAmp1out, OpAmp2out, OpAmp3out

High current output of uncommitted opamp<sup>[12]</sup>.

Extref0, Extref1

External reference input to the analog system.

OpAmp0-, OpAmp1-, OpAmp2-, OpAmp3-

Inverting input to uncommitted opamp.

OpAmp0+, OpAmp1+, OpAmp2+, OpAmp3+

Noninverting input to uncommitted opamp.

#### **GPIO**

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[12]</sup>.

12C0: SCL, I2C1: SCL

I<sup>2</sup>C SCL line providing wake from sleep on an address match. Any I/O pin can be used for I<sup>2</sup>C SCL if wake from sleep is not required.

12C0: SDA, I2C1: SDA

I<sup>2</sup>C SDA line providing wake from sleep on an address match. Any I/O pin can be used for I<sup>2</sup>C SDA if wake from sleep is not required.

#### Ind

Inductor connection to boost pump.

#### Note

12. GPIOs with opamp outputs are not recommended for use with CapSense.

kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

MHz XTAL: Xo, MHz XTAL: Xi

4- to 33-MHz crystal oscillator pin.

#### nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

#### SIC

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

#### **SWDCK**

Serial wire debug clock programming and debug port connection.

#### **SWDIO**

Serial wire debug input and output programming and debug port connection.

#### SWV.

Single wire viewer debug output.

#### TCK

JTAG test clock programming and debug port connection.

#### TD

JTAG test data in programming and debug port connection.

#### TDO

JTAG test data out programming and debug port connection.

#### 4.4.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TD) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

#### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.4.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location).

#### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

#### 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase 'subchains' can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

Figure 6-1. Clocking Subsystem External IO 3-62 MHz 4-33 MHz 1,33,100 kHz 32 kHz ECO or DSI IMO ECO ILO 0-66 MHz 12-48 MHz CPU Doubler Clock CPU Clock Divider 24-67 MHz System PΠ Clock Mux Bus Clock Bus Clock Divider 16 bit Digital Clock Digital Clock Analog Clock Divider 16 bit Divider 16 bit Divider 16 bit Digital Clock Digital Clock Analog Clock Divider 16 bit Divider 16 bit Divider 16 bit 7 7 Analog Clock Digital Clock Digital Clock Divider 16 bit Divider 16 bit Divider 16 bit Analog Clock Digital Clock Digital Clock Divider 16 bit Divider 16 bit Divider 16 bit

#### 6.1.1 Internal Oscillators

#### 6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due to its  $\pm 1$ -percent accuracy. The IMO operates with no external components and outputs a stable clock. A factory trim for each frequency range is stored in the device. With the factory trim, tolerance varies from  $\pm 1$  percent at 3 MHz, up to  $\pm 7$  percent at 62 MHz. The IMO, in conjunction with the PLL, allows generation of CPU and system clocks up to the device's maximum frequency (see PLL). The IMO provides clock outputs at 3, 6, 12, 24, 48, and 62 MHz.

#### 6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the input clock. The doubler works for input frequency ranges of 6 to 24 MHz (providing 12 to 48 MHz at the output). It can be configured to use a clock from the IMO, MHzECO, or the DSI (external pin). The doubler is typically used to clock the USB.

#### 6.1.1.3 PLL

The PLL allows low-frequency, high-accuracy clocks to be multiplied to higher frequencies. This is a trade off between higher clock frequency and accuracy and, higher power consumption and increased startup time.

The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range of 24 to 67 MHz. Its input and feedback dividers supply 4032 discrete ratios to create almost any desired system clock frequency. The accuracy of the PLL output depends on the accuracy of the PLL input source. The most common PLL use is to multiply the IMO clock at 3 MHz, where it is most accurate, to generate the CPU and system clocks up to the device's maximum frequency.

The PLL achieves phase lock within 250 µs (verified by bit setting). It can be configured to use a clock from the IMO, MHzECO or DSI (external pin). The PLL clock source can be used until lock is complete and signaled with a lock bit. The lock signal can be routed through the DSI to generate an interrupt. Disable the PLL before entering low-power modes.

#### 6.1.1.4 Internal Low-Speed Oscillator

The ILO provides clock frequencies for low-power consumption, including the watchdog timer, and sleep timer. The ILO generates up to three different clocks: 1 kHz, 33 kHz, and 100 kHz. The 1-kHz clock (CLK1K) is typically used for a background 'heartbeat' timer. This clock inherently lends itself to low-power supervisory operations such as the watchdog timer and long sleep intervals using the central timewheel (CTW).

The central timewheel is a 1-kHz, free running, 13-bit counter clocked by the ILO. The central timewheel is always enabled, except in hibernate mode and when the CPU is stopped during debug on chip mode. It can be used to generate periodic interrupts for timing purposes or to wake the system from a low-power mode. Firmware can reset the central timewheel. Systems that require accurate timing should use the RTC capability instead of the central timewheel.

The 100-kHz clock (CLK100K) works as a low-power system clock to run the CPU. It can also generate time intervals such as fast sleep intervals using the fast timewheel. The fast timewheel is a 100-kHz, 5-bit counter clocked by the ILO that can also be used to wake the system. The fast timewheel settings are programmable, and the counter automatically resets when the terminal count is reached. This enables flexible, periodic wakeups of the CPU at a higher rate than is allowed using the central timewheel. The fast timewheel can generate an optional interrupt each time the terminal count is reached.

voltage. In standby mode, most boost functions are disabled, thus reducing power consumption of the boost circuit. The converter can be configured to provide low-power, low-current regulation in the standby mode. The external 32-kHz crystal can be used to generate inductor boost pulses on the rising and falling edge of the clock when the output voltage is less than the programmed value. This is called automatic thump mode (ATM).

The boost typically draws 200  $\mu A$  in active mode and 12  $\mu A$  in standby mode. The boost operating modes must be used in conjunction with chip power modes to minimize the total chip power consumption. Table 6-4 lists the boost power modes available in different chip power modes.

Table 6-4. Chip and Boost Power Modes Compatibility

| Chip Power Modes      | Boost Power Modes                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip – Active mode    | Boost can be operated in either active or standby mode.                                                                                                            |

| Chip – Sleep mode     | Boost can be operated in either active or standby mode. However, it is recommended to operate boost in standby mode for low-power consumption                      |

| Chip – Hibernate mode | Boost can only be operated in active mode. However, it is recommended not to use boost in chip hibernate mode due to high current consumption in boost active mode |

If the boost converter is not used in a given application, tie the Vbat, Vssb, and Vboost pins to ground and leave the Ind pin unconnected.

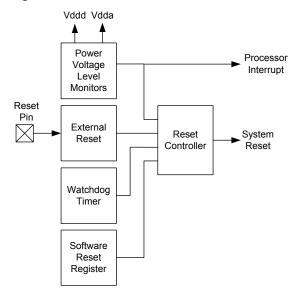

#### 6.3 Reset

CY8C38 has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring The analog and digital power voltages, Vdda, Vddd, Vcca, and Vccd are monitored in several different modes during power up, active mode, and sleep mode (buzzing). If any of the voltages goes outside predetermined ranges then a reset is generated. The monitors are programmable to generate an interrupt to the processor under certain conditions before reaching the reset thresholds.

- External The device <u>can</u> be reset fro<u>m an external</u> source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull-up to Vddio1. Vddd, Vdda, and Vddio1 must all have voltage applied before the part comes out of reset.

- Watchdog timer A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset.

- Software The device can be reset under program control.

Figure 6-7. Resets

The term **device reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register holds the source of the most recent reset or power voltage monitoring interrupt. The program may examine this register to detect and report exception conditions. This register is cleared after a power-on reset.

#### 6.3.1 Reset Sources

#### 6.3.1.1 Power Voltage Level Monitors

#### ■ IPOR – Initial power-on reset

At initial power on, IPOR monitors the power voltages  $V_{DDD}$  and  $V_{DDA}$ , both directly at the pins and at the outputs of the corresponding internal regulators. The trip level is not precise. It is set to approximately 1 volt, which is below the lowest specified operating voltage but high enough for the internal circuits to be reset and to hold their reset state. The monitor generates a reset pulse that is at least 100 ns wide. It may be much wider if one or more of the voltages ramps up slowly.

To save power the IPOR circuit is disabled when the internal digital supply is stable. Voltage supervision is then handed off to the precise low voltage reset (PRES) circuit. When the voltage is high enough for PRES to release, the IMO starts.

#### ■ PRES – Precise low voltage reset

This circuit monitors the outputs of the analog and digital internal regulators after power up. The regulator outputs are compared to a precise reference voltage. The response to a PRES trip is identical to an IPOR reset.

In normal operating mode, the program cannot disable the digital PRES circuit. The analog regulator can be disabled, which also disables the analog portion of the PRES. The PRES circuit is disabled automatically during sleep and hibernate modes, with one exception: During sleep mode the regulators are periodically activated (buzzed) to provide supervisory services and to reduce wakeup time. At these times the PRES circuit is also buzzed to allow periodic voltage monitoring.

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt

Interrupt circuits are available to detect when Vdda and Vddd go outside a voltage range. For AHVI, Vdda is compared to a fixed trip level. For ALVI and DLVI, Vdda and Vddd are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply           | Normal<br>Voltage<br>Range | Available Trip<br>Settings               | Accuracy |

|-----------|------------------|----------------------------|------------------------------------------|----------|

| DLVI      | V <sub>DDD</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| ALVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| AHVI      | $V_{DDA}$        | 1.71 V-5.5 V               | 5.75 V                                   | ±2%      |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

#### 6.3.1.2 Other Reset Sources

#### ■ XRES – External reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

#### ■ SRFS – Software reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

#### ■ DRES – Digital logic reset

A logic signal can be routed from the UDBs or other digital peripheral source through the DSI to the Configurable XRES pin, P1[2], to generate a hardware-controlled reset. The pin must be placed in XRES mode. The response to a DRES is the same as after an IPOR reset.

#### ■ WRES – Watchdog timer reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

#### Note

14. GPIOs with opamp outputs are not recommended for use with CapSense.

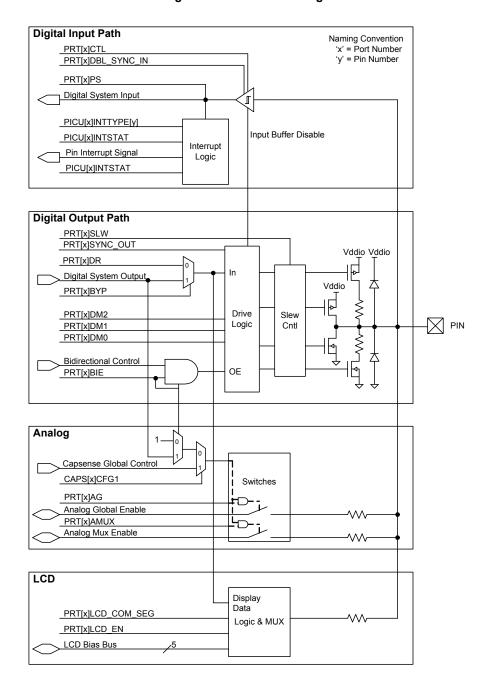

#### 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the Vddio pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[14]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of V<sub>DDA</sub> and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- □ Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- □ Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[14]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating  $V_{DD}$ )

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- □ Highest drive strength for general purpose use

- Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- □ Digital output (CMOS) drive mode

- □ Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

Figure 6-8. GPIO Block Diagram

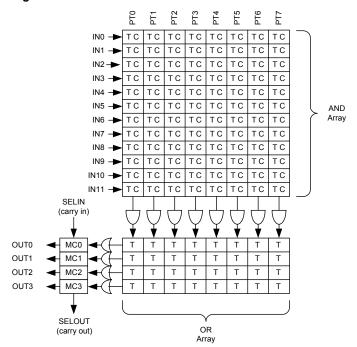

The main component blocks of the UDB are:

- PLD blocks There are two small PLDs per UDB. These blocks take inputs from the routing array and form registered or combinational sum-of-products logic. PLDs are used to implement state machines, state bits, and combinational logic equations. PLD configuration is automatically generated from graphical primitives.

- Datapath module This 8-bit wide datapath contains structured logic to implement a dynamically configurable ALU, a variety of compare configurations and condition generation. This block also contains input/output FIFOs, which are the primary parallel data interface between the CPU/DMA system and the UDB.

- Status and control module The primary role of this block is to provide a way for CPU firmware to interact and synchronize with UDB operation.

- Clock and reset module This block provides the UDB clocks and reset selection and control.

#### 7.2.1 PLD Module

The primary purpose of the PLD blocks is to implement logic expressions, state machines, sequencers, lookup tables, and decoders. In the simplest use model, consider the PLD blocks as a standalone resource onto which general purpose RTL is synthesized and mapped. The more common and efficient use model is to create digital functions from a combination of PLD and datapath blocks, where the PLD implements only the random logic and state portion of the function while the datapath (ALU) implements the more structured elements.

Figure 7-7. PLD 12C4 Structure

One 12C4 PLD block is shown in Figure 7-7. This PLD has 12 inputs, which feed across eight product terms. Each product term (AND function) can be from 1 to 12 inputs wide, and in a given product term, the true (T) or complement (C) of each input can be selected. The product terms are summed (OR function) to create the PLD outputs. A sum can be from 1 to 8 product terms wide. The 'C' in 12C4 indicates that the width of the OR gate (in this case 8) is constant across all outputs (rather than variable as in a 22V10 device). This PLA like structure gives maximum flexibility and insures that all inputs and outputs are permutable for ease of allocation by the software tools. There are two 12C4 PLDs in each UDB.

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

#### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

#### 7.2.2.5 Built in CRC/PRS

The datapath has built-in support for single cycle CRC computation and PRS generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

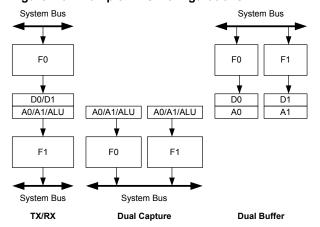

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

Figure 7-9. Example FIFO Configurations

#### 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

#### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

#### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

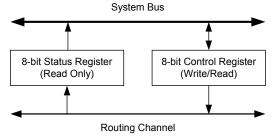

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

Figure 7-10. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

Vcca Vssa AMUXBUSI AMUXBUSR AGR[4] AGL[4] AGL[5] AGL[7] 3210 76543210 ExVrefR P0[7] COMPARATOR \*P15[1] GPXT \*P15[0] out CAPSENSE out ref refbuff refbuff in \* Vccd P4[7] \* Vssd Vccd \* Vddd Vssd USB IO \* P15[7] USB IO \* DAC1 VIDAC P15[6] DAC2 DAC3 DSM DSM refs P5[5] GPIO FxVrefR FxVrefl AMUXBUSL 01234567 0123 ANALOG ANALOG GLOBALS BUS 3210 76543210 ANALOG ANALOG BUS GLOBALS Vddio2\* AGL[3] AGR[3] AGL[2] AGR[2] AGL[1] AGR[1]

AGL[0] AGR[0]

AMUXBUSL AMUXBUS Mux Group Vddio1\* Switch Group Connection

Vssd

\* Denotes pins on all packages

LCD signals are not shown.

Vssb

Figure 8-2. CY8C38 Analog Interconnect

Switch Resistance

Small (~870 Ohms)

Large ( ~200 Ohms)

Rev #51

2-April-2010

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C38, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

#### 8.2 Delta-sigma ADC

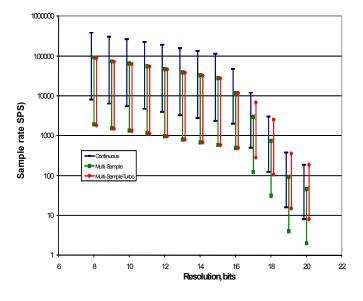

The CY8C38 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for both audio signal processing and measurement applications. The converter's nominal operation is 16 bits at 48 ksps. The ADC can be configured to output 20-bit resolution at data rates of up to 187 sps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

Table 8-1. Delta-sigma ADC Performance

| Bits | Maximum Sample Rate (sps) | SINAD (dB) |

|------|---------------------------|------------|

| 20   | 187                       | _          |

| 16   | 48 k                      | 84         |

| 12   | 192 k                     | 66         |

| 8    | 384 k                     | 43         |

Figure 8-3. Delta-sigma ADC Sample Rates, Range = ±1.024 V

#### 8.2.1 Functional Description

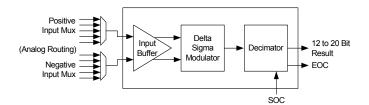

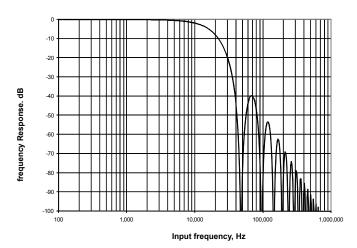

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is [(sin x)/x]<sup>4</sup>; a typical frequency response is shown in Figure 8-5.

Figure 8-4. Delta-sigma ADC Block Diagram

Figure 8-5. Delta-sigma ADC Frequency Response, Normalized to Output, Sample Rate = 48 kHz

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC)

#### PRELIMINARY

### PSoC® 3: CY8C38 Family Datasheet

asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

#### 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

#### 8.2.2.4 Multi Sample (Turbo)

The multi sample (turbo) mode operates identical to the Multi-sample mode for resolutions of 8 to 16 bits. For resolutions of 17 to 20 bits, the performance is about four times faster than the multi sample mode, because the ADC is only reset once at the end of conversion.

More information on output formats is provided in the Technical Reference Manual.

#### 8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital clock or UDB output can be used to drive this input. It can be used when the sampling period must be longer than the ADC conversion time or when the ADC must be synchronized to other hardware. This signal is optional and does not need to be connected if ADC is running in a continuous mode.

#### 8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion. This signal may be used to trigger either an interrupt or DMA request.

#### 8.3 Comparators

The CY8C38 family of devices contains four comparators in a device. Comparators have these features:

- Input offset factory trimmed to less than 5 mV

- Rail-to-rail common mode input range (V<sub>SSA</sub> to V<sub>DDA</sub>)

- Speed and power can be traded off by using one of three modes: fast, slow, or ultra low-power

- Comparator outputs can be routed to lookup tables to perform simple logic functions and then can also be routed to digital blocks

- The positive input of the comparators may be optionally passed through a low pass filter. Two filters are provided

- Comparator inputs can be connections to GPIO, DAC outputs and SC block outputs

#### 8.3.1 Input and Output Interface

The positive and negative inputs to the comparators come from the analog global buses, the analog mux line, the analog local bus and precision reference through multiplexers. The output from each comparator could be routed to any of the two input LUTs. The output of that LUT is routed to the UDB DSI.

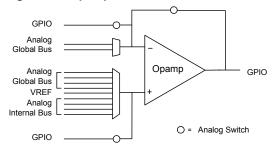

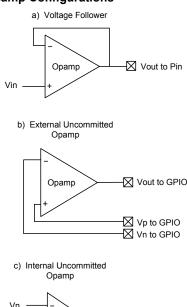

Figure 8-7. Opamp

The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or internal signals.

See Figure 8-8. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

Figure 8-8. Opamp Configurations

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

✓ Vout to Pin

GPIO Pin

Opamp

#### 8.5 Programmable SC/CT Blocks

The CY8C38 family of devices contains up to four switched capacitor/continuous time (SC/CT) blocks in a device. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters such as gain, amplifier polarity, V<sub>REF</sub> connection, and so on.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

The opamp and resistor array is programmable to perform various analog functions including

- Naked operational amplifier Continuous mode

- Unity-gain buffer Continuous mode

- PGA Continuous mode

- Transimpedance amplifier (TIA) Continuous mode

- Up/down mixer Continuous mode

- Sample and hold mixer (NRZ S/H) Switched cap mode

- First order analog to digital modulator Switched cap mode

#### 8.5.1 Naked Opamp

The Naked Opamp presents both inputs and the output for connection to internal or external signals. The opamp has a unity gain bandwidth greater than 6.0 MHz and output drive current up to 650  $\mu$ A. This is sufficient for buffering internal signals (such as DAC outputs) and driving external loads greater than 7.5 kohms.

#### 8.5.2 Unity Gain

The Unity Gain buffer is a Naked Opamp with the output directly connected to the inverting input for a gain of 1.00. It has a –3 dB bandwidth greater than 6.0 MHz.

#### 8.5.3 PGA

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-9. The schematic in Figure 8-9 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

To Internal Signals

Vp

Table 11-12. SIO AC Specifications (continued)

| Parameter | Description                                                                                      | Conditions                               | Min | Тур | Max | Units |  |  |

|-----------|--------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|--|--|

|           | SIO output operating frequency                                                                   |                                          |     |     |     |       |  |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated output (GPIO) mode, fast strong drive mode        | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 33  | MHz   |  |  |

|           | 1.71 V < V <sub>DDIO</sub> < 3.3 V,<br>Unregulated output (GPIO) mode,<br>fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | _   | 16  | MHz   |  |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated output (GPIO) mode, slow strong drive mode        | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | _   | 5   | MHz   |  |  |

| Fsioout   | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregulated output (GPIO) mode, slow strong drive mode       | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 4   | MHz   |  |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, fast strong drive mode                 | Output continuously switching into 25 pF | _   | -   | 20  | MHz   |  |  |

|           | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Regulated output mode, fast strong drive mode                | Output continuously switching into 25 pF | -   | -   | 10  | MHz   |  |  |

|           | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, slow strong drive mode                | Output continuously switching into 25 pF | -   | -   | 2.5 | MHz   |  |  |

| Fsioin    | SIO input operating frequency                                                                    |                                          | •   |     |     | •     |  |  |

| 1-210111  | 1.71 V ≤ V <sub>DDIO</sub> ≤ 5.5 V                                                               | 90/10% V <sub>DDIO</sub>                 | _   | _   | 66  | MHz   |  |  |

#### 11.4.3 USBIO

For operation in GPIO mode, the standard range for V<sub>DDD</sub> applies, see Device Level Specifications on page 60.

Table 11-13. USBIO DC Specifications

| Parameter       | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|-----------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi           | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | -   | 1.575          | kΩ    |

| Rusba           | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | _   | 3.090          | kΩ    |

| Vohusb          | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb          | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | _              | _   | 0.3            | V     |

| Vohgpio         | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | 2.4            | _   | _              | V     |

| Volgpio         | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | _              | _   | 0.3            | V     |

| Vdi             | Differential input sensitivity         | (D+) – (D–)                                        | _              | _   | 0.2            | V     |

| Vcm             | Differential input common mode range   | _                                                  | 8.0            | _   | 2.5            | V     |

| Vse             | Single ended receiver threshold        | -                                                  | 0.8            | _   | 2              | V     |

| Rps2            | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | _   | 7              | kΩ    |

| Rext            | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo              | USB driver output impedance            | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub> | USB transceiver input capacitance      | _                                                  | _              | _   | 20             | pF    |

| I <sub>IL</sub> | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | -              | _   | 2              | nA    |

#### 11.5.3 Voltage Reference

#### Table 11-25. Voltage Reference Specifications

See also ADC external reference specifications in Section 11.5.2.

| Parameter | Description                                       | Conditions       | Min              | Тур   | Max              | Units   |

|-----------|---------------------------------------------------|------------------|------------------|-------|------------------|---------|

| 112.      | Precision reference voltage                       | Initial trimming | 1.023<br>(-0.1%) | 1.024 | 1.025<br>(+0.1%) | V       |

|           | Temperature drift <sup>[36]</sup>                 |                  | _                | _     | 20               | ppm/°C  |

|           | Long term drift                                   |                  | _                | 100   | _                | ppm/Khr |

|           | Thermal cycling drift (stability) <sup>[36]</sup> |                  | _                | 100   | _                | ppm     |

#### 11.5.4 Analog Globals

#### Table 11-26. Analog Globals Specifications

| Parameter | Description                                                  | Conditions               | Min | Тур | Max  | Units |

|-----------|--------------------------------------------------------------|--------------------------|-----|-----|------|-------|

| Rppag     | Resistance pin-to-pin through analog global <sup>[37]</sup>  | V <sub>DDA</sub> = 3.0 V | _   | 939 | 1461 | Ω     |

| Rppmuxbus | Resistance pin-to-pin through analog mux bus <sup>[37]</sup> | V <sub>DDA</sub> = 3.0 V | _   | 721 | 1135 | Ω     |

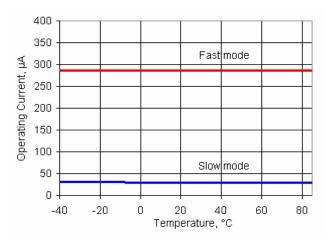

#### 11.5.5 Comparator

#### Table 11-27. Comparator DC Specifications

| Parameter         | Description                                       | Conditions                                 | Min              | Тур | Max                    | Units |

|-------------------|---------------------------------------------------|--------------------------------------------|------------------|-----|------------------------|-------|

| Vos               | Input offset voltage in fast mode                 | Factory trim, Vdda > 2.7 V,<br>Vin ≥ 0.5 V | -                |     | 10                     | mV    |

| 00                | Input offset voltage in slow mode                 | Factory trim, Vin ≥ 0.5 V                  | _                |     | 9                      | mV    |

| V <sub>OS</sub>   | Input offset voltage in fast mode <sup>[38]</sup> | Custom trim                                | _                | _   | 4                      | mV    |

|                   | Input offset voltage in slow mode <sup>[38]</sup> | Custom trim                                | _                | _   | 4                      | mV    |

| V <sub>OS</sub>   | Input offset voltage in ultra low-power mode      |                                            | -                | ±12 | -                      | mV    |

| V <sub>HYST</sub> | Hysteresis                                        | Hysteresis enable mode                     | _                | 10  | 32                     | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                         | High current / fast mode                   | V <sub>SSA</sub> | _   | V <sub>DDA</sub> – 0.1 | V     |

|                   |                                                   | Low current / slow mode                    | V <sub>SSA</sub> | _   | $V_{DDA}$              | V     |

|                   |                                                   | Ultra low power mode                       | V <sub>SSA</sub> | -   | V <sub>DDA</sub> – 0.9 | V     |

| CMRR              | Common mode rejection ratio                       |                                            | _                | 50  | -                      | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode <sup>[36]</sup>       |                                            | _                | -   | 400                    | μA    |

|                   | Low current mode/slow mode <sup>[36]</sup>        |                                            | _                | _   | 100                    | μA    |

|                   | Ultra low-power mode <sup>[36]</sup>              |                                            | -                | 6   | _                      | μA    |

#### Notes

Document Number: 001-11729 Rev. \*Q

Page 80 of 117

<sup>36.</sup> Based on device characterization (Not production tested).

<sup>37.</sup> The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

<sup>38.</sup> The recommended procedure for using a custom trim value for the on-chip comparators can be found in the TRM.

Figure 11-33. IDAC Operating Current vs Temperature, Range = 255  $\mu$ A, Code = 0, Source Mode

Figure 11-34. IDAC Operating Current vs Temperature, Range = 255 µA, Code = 0, Sink Mode

Table 11-30. IDAC AC Specifications

| Parameter           | Description              | Conditions                                                                                       | Min | Тур | Max | Units |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| F <sub>DAC</sub>    | Update rate              |                                                                                                  | _   | _   | 8   | Msps  |

| T <sub>SETTLE</sub> | Settling time to 0.5 LSB | Range = 31.875 $\mu$ A or 255 $\mu$ A, full scale transition, fast mode, 600 $\Omega$ 15-pF load | -   | _   | 125 | ns    |

#### 11.7.4 SRAM

#### Table 11-61. SRAM DC Specifications

| Parameter  | Description            | Conditions | Min | Тур | Max | Units |

|------------|------------------------|------------|-----|-----|-----|-------|

| $V_{SRAM}$ | SRAM retention voltage |            | 1.2 | -   | _   | V     |

#### Table 11-62. SRAM AC Specifications

| Parameter         | Description              | Conditions | Min | Тур | Max | Units |

|-------------------|--------------------------|------------|-----|-----|-----|-------|

| F <sub>SRAM</sub> | SRAM operating frequency |            | DC  | _   | 67  | MHz   |

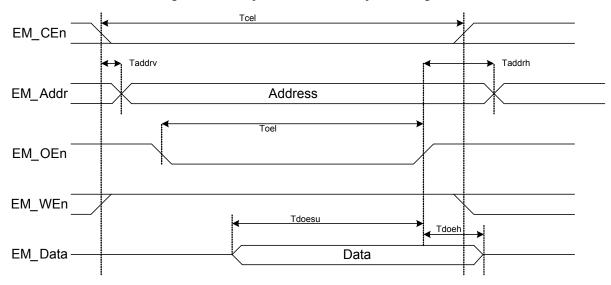

#### 11.7.5 External Memory Interface

Figure 11-48. Asynchronous Read Cycle Timing

#### 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T  $_{A}$   $\leq$  85 °C and T  $_{J}$   $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.9.1 32 kHz External Crystal

### Table 11-75. 32 kHz External Crystal DC Specifications<sup>[49]</sup>

| Parameter       | Description                  | Conditions     | Min | Тур  | Max | Units |

|-----------------|------------------------------|----------------|-----|------|-----|-------|

| I <sub>CC</sub> | Operating current            | Low-power mode | _   | 0.25 | 1.0 | μΑ    |

| CL              | External crystal capacitance |                | _   | 6    | _   | pF    |

| DL              | Drive level                  |                | _   | _    | 1   | μW    |

#### Table 11-76. 32 kHz External Crystal AC Specifications

| Parameter       | Description  | Conditions      | Min | Тур    | Max | Units |

|-----------------|--------------|-----------------|-----|--------|-----|-------|

| F               | Frequency    |                 | _   | 32.768 | _   | kHz   |

| T <sub>ON</sub> | Startup time | High power mode | _   | 1      | _   | S     |

#### 11.9.2 Internal Main Oscillator

#### Table 11-77. IMO DC Specifications

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|

|           | Supply current        |                                    |     | •   | •   | •     |

|           | 62.6 MHz              |                                    | _   | _   | 600 | μA    |

|           | 48 MHz                |                                    | _   | _   | 500 | μA    |

|           | 24 MHz – USB mode     | With oscillator locking to USB bus | _   | _   | 500 | μΑ    |

|           | 24 MHz – non USB mode |                                    | _   | _   | 300 | μA    |

|           | 12 MHz                |                                    | _   | _   | 200 | μA    |

|           | 6 MHz                 |                                    | _   | _   | 180 | μA    |

|           | 3 MHz                 |                                    | _   | _   | 150 | μΑ    |

#### Table 11-78. IMO AC Specifications

| Parameter        | Description                                 | Conditions                                                                  | Min        | Тур | Max  | Units |  |  |  |

|------------------|---------------------------------------------|-----------------------------------------------------------------------------|------------|-----|------|-------|--|--|--|

|                  | IMO frequency stability (with factory trim) |                                                                             |            |     |      |       |  |  |  |

|                  | 62.6 MHz                                    |                                                                             | <b>-</b> 7 | -   | 7    | %     |  |  |  |

|                  | 48 MHz                                      |                                                                             | <b>-</b> 5 | -   | 5    | %     |  |  |  |

| _                | 24 MHz – Non USB mode                       |                                                                             | -4         | -   | 4    | %     |  |  |  |

| F <sub>IMO</sub> | 24 MHz – USB mode                           | With oscillator locking to USB bus                                          | -0.25      | _   | 0.25 | %     |  |  |  |

|                  | 12 MHz                                      |                                                                             | -3         | _   | 3    | %     |  |  |  |

|                  | 6 MHz                                       |                                                                             | -2         | -   | 2    | %     |  |  |  |

|                  | 3 MHz                                       |                                                                             | -1         | _   | 1    | %     |  |  |  |

|                  | Startup time <sup>[49]</sup>                | From enable (during normal system operation) or wakeup from low-power state | -          | _   | 12   | μs    |  |  |  |

Document Number: 001-11729 Rev. \*Q Page 102 of 117

Note

49. Based on device characterization (Not production tested).

#### Table 11-78. IMO AC Specifications (continued)

| Parameter | Description                           | Conditions | Min | Тур | Max | Units |

|-----------|---------------------------------------|------------|-----|-----|-----|-------|

| Јр–р      | Jitter (peak to peak) <sup>[50]</sup> |            |     |     |     |       |

|           | F = 24 MHz                            |            | _   | 0.9 | -   | ns    |

|           | F = 3 MHz                             |            | _   | 1.6 | _   | ns    |

| Jperiod   | Jitter (long term) <sup>[50]</sup>    |            |     |     |     |       |

|           | F = 24 MHz                            |            | _   | 0.9 | -   | ns    |

|           | F = 3 MHz                             |            | -   | 12  | -   | ns    |

#### 11.9.3 Internal Low-Speed Oscillator

#### Table 11-79. ILO DC Specifications

| Parameter       | Description       | Conditions                 | Min | Тур | Max | Units |

|-----------------|-------------------|----------------------------|-----|-----|-----|-------|

|                 | Operating current | F <sub>OUT</sub> = 1 kHz   | -   | 0.3 | 1.7 | μΑ    |

| I <sub>CC</sub> |                   | F <sub>OUT</sub> = 33 kHz  | _   | 1.0 | 2.6 | μΑ    |

|                 |                   | F <sub>OUT</sub> = 100 kHz | -   | 1.0 | 2.6 | μΑ    |

|                 | Leakage current   | Power down mode            | -   | 2.0 | 15  | nA    |

#### Table 11-80. ILO AC Specifications

| Parameter        | Description                   | Conditions | Min | Тур | Max | Units |  |  |

|------------------|-------------------------------|------------|-----|-----|-----|-------|--|--|

|                  | Startup time, all frequencies | Turbo mode | _   | _   | 2   | ms    |  |  |

|                  | ILO frequencies (trimmed)     |            |     |     |     |       |  |  |

|                  | 100 kHz                       |            | 45  | 100 | 200 | kHz   |  |  |

| _                | 1 kHz                         |            | 0.5 | 1   | 2   | kHz   |  |  |

| F <sub>ILO</sub> | ILO frequencies (untrimmed)   |            |     | l.  | II. |       |  |  |

|                  | 100 kHz                       |            | 30  | 100 | 300 | kHz   |  |  |

|                  | 1 kHz                         |            | 0.3 | 1   | 3.5 | kHz   |  |  |

#### 11.9.4 External Crystal Oscillator

#### Table 11-81. ECO AC Specifications

| Parameter | Description             | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------|------------|-----|-----|-----|-------|

| F         | Crystal frequency range |            | 4   | -   | 33  | MHz   |

#### 11.9.5 External Clock Reference

#### Table 11-82. External Clock Reference AC Specifications<sup>[50]</sup>

| Parameter | Description              | Conditions                         | Min | Тур | Max | Units |

|-----------|--------------------------|------------------------------------|-----|-----|-----|-------|

|           | External frequency range |                                    | 0   | _   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30  | 50  | 70  | %     |

|           | Input edge rate          | V <sub>IL</sub> to V <sub>IH</sub> | 0.1 | _   | _   | V/ns  |

Note

Note

50. Based on device characterization (Not production tested).

Document Number: 001-11729 Rev. \*Q Page 103 of 117

#### **PRELIMINARY**

# PSoC® 3: CY8C38 Family Datasheet

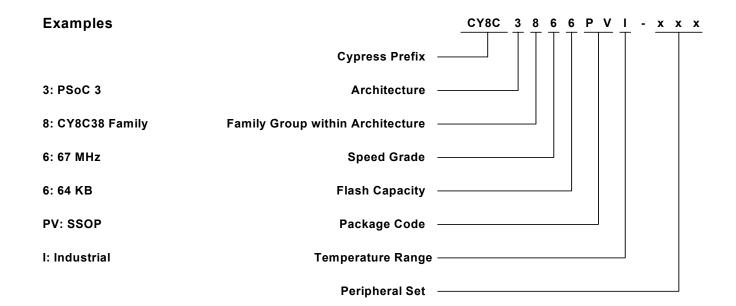

#### 12.1 Part Numbering Conventions

PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric (0, 1, 2, ..., 9, A, B, ..., Z) unless stated otherwise.

CY8Cabcdefg-xxx

■ a: Architecture

□ 3: PSoC 3□ 5: PSoC 5

■ b: Family group within architecture

□ 4: CY8C34 family

□ 6: CY8C36 family

■ 8: CY8C38 family

■ c: Speed grade

□ 4: 48 MHz

□ 6: 67 MHz

■ d: Flash capacity

□ 4: 16 KB

□ 5: 32 KB

□ 6: 64 KB

■ ef: Package code

Two character alphanumeric

■ AX: TQFP

LT: QFN

□ PV: SSOP

g: Temperature range

□ C: commercial

□ I: industrial

■ A: automotive

■ xxx: Peripheral set

■ Three character numeric

■ No meaning is associated with these three characters.

All devices in the PSoC 3 CY8C38 family comply to RoHS-6 specifications, demonstrating the commitment by Cypress to lead-free products. Lead (Pb) is an alloying element in solders that has resulted in environmental concerns due to potential toxicity. Cypress uses nickel-palladium-gold (NiPdAu) technology for the majority of leadframe-based packages.

A high-level review of the Cypress Pb-free position is available on our website. Specific package information is also available. Package Material Declaration Datasheets (PMDDs) identify all substances contained within Cypress packages. PMDDs also confirm the absence of many banned substances. The information in the PMDDs will help Cypress customers plan for recycling or other "end of life" requirements.