Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 48-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866pvi-005 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PSoC<sup>®</sup> 3: CY8C38 Family Datasheet

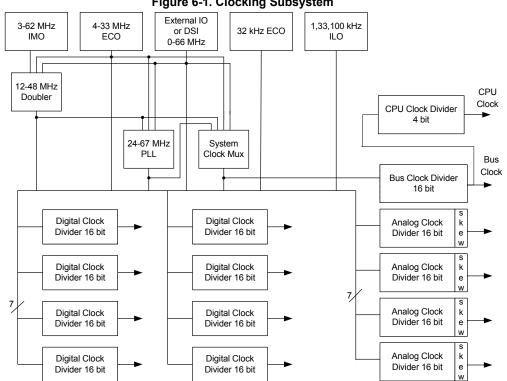

#### Figure 6-1. Clocking Subsystem

PRELIMINARY

#### 6.1.1 Internal Oscillators

#### 6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due to its ±1-percent accuracy. The IMO operates with no external components and outputs a stable clock. A factory trim for each frequency range is stored in the device. With the factory trim, tolerance varies from ±1 percent at 3 MHz, up to ±7 percent at 62 MHz. The IMO, in conjunction with the PLL, allows generation of CPU and system clocks up to the device's maximum frequency (see PLL). The IMO provides clock outputs at 3, 6, 12, 24, 48, and 62 MHz.

#### 6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the input clock. The doubler works for input frequency ranges of 6 to 24 MHz (providing 12 to 48 MHz at the output). It can be configured to use a clock from the IMO, MHzECO, or the DSI (external pin). The doubler is typically used to clock the USB.

#### 6.1.1.3 PLL

The PLL allows low-frequency, high-accuracy clocks to be multiplied to higher frequencies. This is a trade off between higher clock frequency and accuracy and, higher power consumption and increased startup time.

The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range of 24 to 67 MHz. Its input and feedback dividers supply 4032 discrete ratios to create almost any desired system clock frequency. The accuracy of the PLL output depends on the accuracy of the PLL input source. The most common PLL use is to multiply the IMO clock at 3 MHz, where it is most accurate, to generate the CPU and system clocks up to the device's maximum frequency.

The PLL achieves phase lock within 250 µs (verified by bit setting). It can be configured to use a clock from the IMO, MHzECO or DSI (external pin). The PLL clock source can be used until lock is complete and signaled with a lock bit. The lock signal can be routed through the DSI to generate an interrupt. Disable the PLL before entering low-power modes.

#### 6.1.1.4 Internal Low-Speed Oscillator

The ILO provides clock frequencies for low-power consumption, including the watchdog timer, and sleep timer. The ILO generates up to three different clocks: 1 kHz, 33 kHz, and 100 kHz. The 1-kHz clock (CLK1K) is typically used for a background 'heartbeat' timer. This clock inherently lends itself to low-power supervisory operations such as the watchdog timer and long sleep intervals using the central timewheel (CTW).

The central timewheel is a 1-kHz, free running, 13-bit counter clocked by the ILO. The central timewheel is always enabled, except in hibernate mode and when the CPU is stopped during debug on chip mode. It can be used to generate periodic interrupts for timing purposes or to wake the system from a low-power mode. Firmware can reset the central timewheel. Systems that require accurate timing should use the RTC capability instead of the central timewheel.

The 100-kHz clock (CLK100K) works as a low-power system clock to run the CPU. It can also generate time intervals such as fast sleep intervals using the fast timewheel. The fast timewheel is a 100-kHz, 5-bit counter clocked by the ILO that can also be used to wake the system. The fast timewheel settings are programmable, and the counter automatically resets when the terminal count is reached. This enables flexible, periodic wakeups of the CPU at a higher rate than is allowed using the central timewheel. The fast timewheel can generate an optional interrupt each time the terminal count is reached.

PRELIMINARY

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt

Interrupt circuits are available to detect when Vdda and Vddd go outside a voltage range. For AHVI, Vdda is compared to a fixed trip level. For ALVI and DLVI, Vdda and Vddd are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

# Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply           | Normal<br>Voltage<br>Range | Available Trip<br>Settings               | Accuracy |

|-----------|------------------|----------------------------|------------------------------------------|----------|

| DLVI      | V <sub>DDD</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| ALVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 1.70 V–5.45 V in<br>250 mV<br>increments | ±2%      |

| AHVI      | V <sub>DDA</sub> | 1.71 V–5.5 V               | 5.75 V                                   | ±2%      |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

- 6.3.1.2 Other Reset Sources

- XRES External reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

SRES – Software reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

DRES – Digital logic reset

A logic signal can be routed from the UDBs or other digital peripheral source through the DSI to the Configurable XRES pin, P1[2], to generate a hardware-controlled reset. The pin must be placed in XRES mode. The response to a DRES is the same as after an IPOR reset.

WRES – Watchdog timer reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

#### Note

14. GPIOs with opamp outputs are not recommended for use with CapSense.

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the Vddio pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[14]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of V<sub>DDA</sub> and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[14]</sup>

- □ Analog input and output capability

- □ Continuous 100 µA clamp current capability

- □ Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- $\square$  Hot swap capability (5 V tolerance at any operating V<sub>DD</sub>)

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

#### High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

#### High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (High Z) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pullup and pull-down are not available with SIO in regulated output mode.

Open drain, drives high and open drain, drives low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the  $I^2C$  bus signal lines.

Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pullup and pull-down are not available with SIO in regulated output mode.

#### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

#### 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

#### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

#### 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to '1' and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt. While level sensitive interrupts are not directly supported; UDB provide this functionality to the system when needed.

#### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog ( $V_{DDA}$ ) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine Vddio capability for a given port and pin. The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

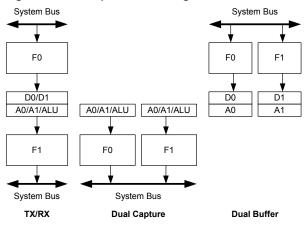

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

## 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

## 7.2.2.5 Built in CRC/PRS

The datapath has built-in support for single cycle CRC computation and PRS generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

## 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

## 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

## 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

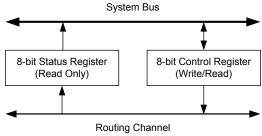

## 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

## Figure 7-10. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

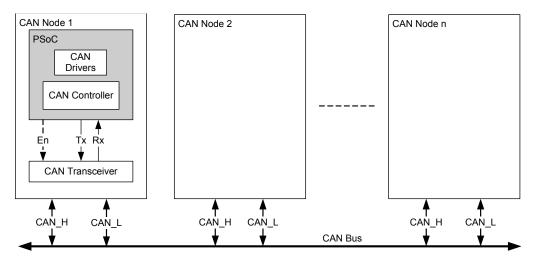

## 7.5 CAN

The CAN peripheral is a fully functional controller area network (CAN) supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level protocols without affecting the performance of the microcontroller CPU. Full configuration support is provided in PSoC Creator.

#### Figure 7-18. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- □ Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

CAN receive and transmit buffers status

- CAN controller error status including BusOff

- Receive path

- □ 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE, and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- a Automatic transmission request (RTR) response handler

- Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- Fixed priority

- Message transmissions abort capability

#### 7.5.2 Software Tools Support

- CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

Figure 7-19. CAN Controller Block Diagram

## 7.6 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 28.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual memory management with no DMA access

- Manual memory management with manual DMA access

Automatic memory management with automatic DMA

- access

- Internal 3.3-V regulator for transceiver

- Internal 48-MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB reset, suspend, and resume operations

- Bus-powered and self-powered modes

#### Figure 7-20. USB

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C38, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

## 8.2 Delta-sigma ADC

The CY8C38 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for both audio signal processing and measurement applications. The converter's nominal operation is 16 bits at 48 ksps. The ADC can be configured to output 20-bit resolution at data rates of up to 187 sps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

| Table 8-1. | Delta-sigma AD | C Performance |

|------------|----------------|---------------|

|------------|----------------|---------------|

| Bits | Maximum Sample Rate<br>(sps) | SINAD (dB) |

|------|------------------------------|------------|

| 20   | 187                          | -          |

| 16   | 48 k                         | 84         |

| 12   | 192 k                        | 66         |

| 8    | 384 k                        | 43         |

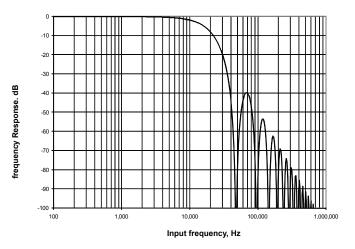

Figure 8-3. Delta-sigma ADC Sample Rates, Range = ±1.024 V

#### 8.2.1 Functional Description

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ ; a typical frequency response is shown in Figure 8-5.

#### Figure 8-4. Delta-sigma ADC Block Diagram

Figure 8-5. Delta-sigma ADC Frequency Response, Normalized to Output, Sample Rate = 48 kHz

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC)

asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

#### 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

#### 8.2.2.4 Multi Sample (Turbo)

The multi sample (turbo) mode operates identical to the Multi-sample mode for resolutions of 8 to 16 bits. For resolutions of 17 to 20 bits, the performance is about four times faster than the multi sample mode, because the ADC is only reset once at the end of conversion.

More information on output formats is provided in the Technical Reference Manual.

#### 8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital clock or UDB output can be used to drive this input. It can be used when the sampling period must be longer than the ADC conversion time or when the ADC must be synchronized to other hardware. This signal is optional and does not need to be connected if ADC is running in a continuous mode.

#### 8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion. This signal may be used to trigger either an interrupt or DMA request.

## 8.3 Comparators

The CY8C38 family of devices contains four comparators in a device. Comparators have these features:

- Input offset factory trimmed to less than 5 mV

- Rail-to-rail common mode input range (V<sub>SSA</sub> to V<sub>DDA</sub>)

- Speed and power can be traded off by using one of three modes: fast, slow, or ultra low-power

- Comparator outputs can be routed to lookup tables to perform simple logic functions and then can also be routed to digital blocks

- The positive input of the comparators may be optionally passed through a low pass filter. Two filters are provided

- Comparator inputs can be connections to GPIO, DAC outputs and SC block outputs

#### 8.3.1 Input and Output Interface

The positive and negative inputs to the comparators come from the analog global buses, the analog mux line, the analog local bus and precision reference through multiplexers. The output from each comparator could be routed to any of the two input LUTs. The output of that LUT is routed to the UDB DSI. PRELIMINARY

# 10. Development Support

The CY8C38 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

## 10.1 Documentation

A suite of documentation, supports the CY8C38 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component datasheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes:** PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

## 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

## 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C38 family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

## Table 11-6. Inductive Boost Regulator DC Specifications (continued)

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 2.4 V,  $V_{OUT}$  = 2.7 V,  $I_{OUT}$  = 40 mA,  $F_{SW}$  = 400 kHz,  $L_{BOOST}$  = 22 µH,  $C_{BOOST}$  = 22 µF || 0.1 µF

| Parameter           | Description                             | Conditions                 | Min  | Тур  | Мах  | Units |  |  |

|---------------------|-----------------------------------------|----------------------------|------|------|------|-------|--|--|

| V <sub>OUT</sub>    | Boost voltage range <sup>[27, 28]</sup> |                            |      |      |      |       |  |  |

|                     | 1.8 V                                   |                            | 1.71 | 1.80 | 1.89 | V     |  |  |

|                     | 1.9 V                                   |                            | 1.81 | 1.90 | 2.00 | V     |  |  |

|                     | 2.0 V                                   |                            | 1.90 | 2.00 | 2.10 | V     |  |  |

|                     | 2.4 V                                   |                            | 2.28 | 2.40 | 2.52 | V     |  |  |

|                     | 2.7 V                                   |                            | 2.57 | 2.70 | 2.84 | V     |  |  |

|                     | 3.0 V                                   |                            | 2.85 | 3.00 | 3.15 | V     |  |  |

|                     | 3.3 V                                   |                            | 3.14 | 3.30 | 3.47 | V     |  |  |

|                     | 3.6 V                                   |                            | 3.42 | 3.60 | 3.78 | V     |  |  |

|                     | 5.0 V                                   | External diode required    | 4.75 | 5.00 | 5.25 | V     |  |  |

| Reg <sub>LOAD</sub> | Load regulation                         |                            | -    | -    | 3.8  | %     |  |  |

| Reg <sub>LINE</sub> | Line regulation                         |                            | -    | -    | 4.1  | %     |  |  |

| ηουτ                | Efficiency                              | L <sub>BOOST</sub> = 10 μH | 70   | 85   | -    | %     |  |  |

|                     |                                         | L <sub>BOOST</sub> = 22 μH | 82   | 90   | -    | %     |  |  |

## Table 11-7. Inductive Boost Regulator AC Specifications

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 2.4 V,  $V_{OUT}$  = 2.7 V,  $I_{OUT}$  = 40 mA,  $F_{SW}$  = 400 kHz,  $L_{BOOST}$  = 22 µH,  $C_{BOOST}$  = 22 µF || 0.1 µF.

| Parameter           | Description                      | Conditions                                                                    | Min | Тур              | Мах | Units |

|---------------------|----------------------------------|-------------------------------------------------------------------------------|-----|------------------|-----|-------|

| V <sub>RIPPLE</sub> | Ripple voltage<br>(peak-to-peak) | V <sub>OUT</sub> = 1.8 V, F <sub>SW</sub> = 400 kHz, I <sub>OUT</sub> = 10 mA | -   | -                | 100 | mV    |

| F <sub>SW</sub>     | Switching frequency              |                                                                               | Ι   | 0.1,0.4,<br>or 2 | -   | MHz   |

#### Table 11-8. Recommended External Components for Boost Circuit

| Parameter          | Description                                     | Conditions                                                | Min | Тур | Max | Units |

|--------------------|-------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|-------|

| L <sub>BOOST</sub> | Boost inductor                                  |                                                           | 4.7 | 10  | 47  | μH    |

| C <sub>BOOST</sub> | Filter capacitor <sup>[27]</sup>                |                                                           | 10  | 22  | 47  | μF    |

| I <sub>F</sub>     | External Schottky diode average forward current | External Schottky diode is required for $V_{OUT}$ > 3.6 V | 1   | _   | _   | A     |

| V <sub>R</sub>     |                                                 |                                                           | 20  | _   | _   | V     |

Notes

27. Based on device characterization (Not production tested).

28. At boost frequency of 2 MHz, Vboost is limited to 2 x Vbat. At 400 kHz, Vboost is limited to 4 x Vbat.

## Table 11-20. 20-bit Delta-sigma ADC DC Specifications (continued)

| Parameter          | Description                                                                                             | Conditions           | Min | Тур | Max  | Units |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------|----------------------|-----|-----|------|-------|--|--|

| Vextref            | ADC external reference input voltage, see<br>also internal reference in Voltage<br>Reference on page 80 | Pins P0[3], P3[2]    | 0.9 | -   | 1.3  | V     |  |  |

| Current Co         | Current Consumption                                                                                     |                      |     |     |      |       |  |  |

| I <sub>DD_20</sub> | Current consumption, 20 bit <sup>[35]</sup>                                                             | 187 sps, unbuffered  | -   | -   | 1.25 | mA    |  |  |

| I <sub>DD_16</sub> | Current consumption, 16 bit <sup>[35]</sup>                                                             | 48 ksps, unbuffered  | -   | -   | 1.2  | mA    |  |  |

| I <sub>DD_12</sub> | Current consumption, 12 bit <sup>[35]</sup>                                                             | 192 ksps, unbuffered | _   | -   | 1.4  | mA    |  |  |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[35]</sup>                                                              |                      | -   | -   | 2.5  | mA    |  |  |

## Table 11-21. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | _   | _   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[35]</sup>                         | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V | _   | -   | 0.0032 | %       |

| 20-Bit Resol | ution Mode                                                        |                                              |     | •   | •      |         |

| SR20         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 7.8 | _   | 187    | sps     |

| BW20         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 40  | -      | Hz      |

| 16-Bit Resol | ution Mode                                                        |                                              |     |     |        |         |

| SR16         | Sample rate <sup>[35]</sup>                                       | Range = ±1.024 V, unbuffered                 | 2   | _   | 48     | ksps    |

| BW16         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 11  | _      | kHz     |

| SINAD16int   | Signal to noise ratio, 16-bit, internal reference <sup>[35]</sup> | Range = ±1.024V, unbuffered                  | 81  | -   | -      | dB      |

| SINAD16ext   | Signal to noise ratio, 16-bit, external reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 84  | -   | -      | dB      |

| 12-Bit Resol | ution Mode                                                        |                                              |     |     | •      |         |

| SR12         | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | _   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 44  | -      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[35]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         |                                              |     |     |        |         |

| SR8          | Sample rate, continuous, high power <sup>[35]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | _   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[35]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 88  | -      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[35]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | -   | -      | dB      |

Notes

35. Based on device characterization (Not production tested).

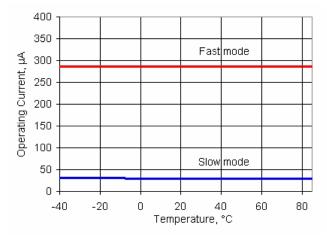

Figure 11-33. IDAC Operating Current vs Temperature, Range =  $255 \mu$ A, Code = 0, Source Mode

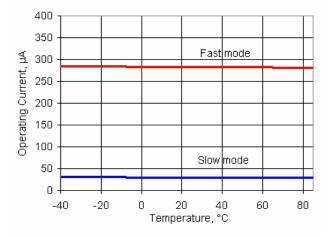

# Figure 11-34. IDAC Operating Current vs Temperature, Range = $255 \mu$ A, Code = 0, Sink Mode

## Table 11-30. IDAC AC Specifications

| Parameter           | Description | Conditions                                                                                             | Min | Тур | Max | Units |

|---------------------|-------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| F <sub>DAC</sub>    | Update rate |                                                                                                        | -   | -   | 8   | Msps  |

| T <sub>SETTLE</sub> | 0           | Range = 31.875 $\mu$ A or 255 $\mu$ A, full<br>scale transition, fast mode, 600 $\Omega$<br>15-pF load |     | _   | 125 | ns    |

## 11.5.12 LCD Direct Drive

## Table 11-40. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                       | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| I <sub>CC</sub>     | LCD system operating current                                                        | Device sleep mode with wakeup at<br>400-Hz rate to refresh LCDs, bus<br>clock = 3 Mhz, Vddio = Vdda = 3 V,<br>4 commons, 16 segments, 1/4 duty<br>cycle, 50 Hz frame rate, no glass<br>connected | -   | 38                     | -    | μΑ    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                                | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | -   | 9.1 × V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                          | -   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                                  | I   | _                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | Vddio = 5.5V, strong drive mode                                                                                                                                                                  | 355 | -                      | 710  | μA    |

## Table 11-41. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

## 11.6.8 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component datasheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

## Table 11-54. UDB AC Specifications

| Parameter              | Description                                                   | Conditions                                       | Min | Тур | Max | Units |

|------------------------|---------------------------------------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| Datapath Per           | formance                                                      |                                                  |     |     |     |       |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                  | -   | -   | 67  | MHz   |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                  | -   | -   | 67  | MHz   |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit<br>CRC/PRS in a UDB pair          |                                                  | -   | -   | 67  | MHz   |

| PLD Perform            | ance                                                          |                                                  |     |     |     |       |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass<br>PLD function in a UDB pair |                                                  | -   | -   | 67  | MHz   |

| Clock to Outp          | but Performance                                               |                                                  |     |     |     |       |

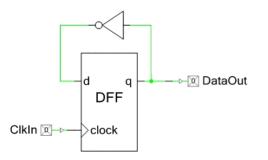

| <sup>t</sup> сlк_оит   | Propagation delay for clock in to data out, see Figure 11-47. | 25 °C, Vddd $\ge$ 2.7 V                          | -   | 20  | 25  | ns    |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-47. | Worst-case placement, routing, and pin selection | -   | _   | 55  | ns    |

#### Figure 11-47. Clock to Output Performance

PRELIMINARY

## 11.8 PSoC System Resources

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

## 11.8.1 POR with Brown Out

For brown out detect in regulated mode,  $V_{DDD}$  and  $V_{DDA}$  must be  $\geq$  2.0 V. Brown out detect is not available in externally regulated mode.

## Table 11-67. Precise Power On Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

|           | Precise POR (PPOR)   |              |      |     |      |       |

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | _   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | _   | 1.66 | V     |

#### Table 11-68. Power On Reset (POR) with Brown Out AC Specifications

| Parameter | Description   | Conditions | Min | Тур | Мах | Units |

|-----------|---------------|------------|-----|-----|-----|-------|

| PRES_TR   | Response time |            | -   | _   | 0.5 | μs    |

#### 11.8.2 Voltage Monitors

## Table 11-69. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Max  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            |      |      |      |       |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

## Table 11-70. Voltage Monitors AC Specifications

| Parameter | Description   | Conditions | Min | Тур | Мах | Units |

|-----------|---------------|------------|-----|-----|-----|-------|

|           | Response time |            | _   | 1   | 1   | μs    |

## 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.9.1 32 kHz External Crystal

## Table 11-75. 32 kHz External Crystal DC Specifications<sup>[49]</sup>

| Parameter       | Description                  | Conditions     | Min | Тур  | Max | Units |

|-----------------|------------------------------|----------------|-----|------|-----|-------|

| I <sub>CC</sub> | Operating current            | Low-power mode | -   | 0.25 | 1.0 | μΑ    |

| CL              | External crystal capacitance |                | -   | 6    | -   | pF    |

| DL              | Drive level                  |                | _   | _    | 1   | μW    |

## Table 11-76. 32 kHz External Crystal AC Specifications

| Parameter       | Description  | Conditions      | Min | Тур    | Мах | Units |

|-----------------|--------------|-----------------|-----|--------|-----|-------|

| F               | Frequency    |                 | -   | 32.768 | -   | kHz   |

| T <sub>ON</sub> | Startup time | High power mode | 1   | 1      | _   | S     |

## 11.9.2 Internal Main Oscillator

## Table 11-77. IMO DC Specifications

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|

|           | Supply current        |                                    |     |     |     |       |

|           | 62.6 MHz              |                                    | -   | -   | 600 | μA    |

|           | 48 MHz                |                                    | I   | -   | 500 | μA    |

|           | 24 MHz – USB mode     | With oscillator locking to USB bus | I   | _   | 500 | μA    |

|           | 24 MHz – non USB mode |                                    | I   | -   | 300 | μA    |

|           | 12 MHz                |                                    | I   | -   | 200 | μA    |

|           | 6 MHz                 |                                    | -   | _   | 180 | μA    |

|           | 3 MHz                 |                                    | -   | -   | 150 | μA    |

#### Table 11-78. IMO AC Specifications

| Parameter        | Description                                 | Conditions                                                                  | Min   | Тур | Max  | Units |  |  |  |

|------------------|---------------------------------------------|-----------------------------------------------------------------------------|-------|-----|------|-------|--|--|--|

|                  | IMO frequency stability (with factory trim) |                                                                             |       |     |      |       |  |  |  |

|                  | 62.6 MHz                                    |                                                                             | -7    | -   | 7    | %     |  |  |  |

|                  | 48 MHz                                      |                                                                             | -5    | -   | 5    | %     |  |  |  |

| E                | 24 MHz – Non USB mode                       |                                                                             | -4    | -   | 4    | %     |  |  |  |

| F <sub>IMO</sub> | 24 MHz – USB mode                           | With oscillator locking to USB bus                                          | -0.25 | -   | 0.25 | %     |  |  |  |

|                  | 12 MHz                                      |                                                                             | -3    | -   | 3    | %     |  |  |  |

|                  | 6 MHz                                       |                                                                             | -2    | -   | 2    | %     |  |  |  |

|                  | 3 MHz                                       |                                                                             | -1    | -   | 1    | %     |  |  |  |

|                  | Startup time <sup>[49]</sup>                | From enable (during normal system operation) or wakeup from low-power state | _     | -   | 12   | μs    |  |  |  |

Note 49. Based on device characterization (Not production tested).

## Table 11-78. IMO AC Specifications (continued)

| Parameter | Description                           | Conditions | Min | Тур | Max | Units |

|-----------|---------------------------------------|------------|-----|-----|-----|-------|

|           | Jitter (peak to peak) <sup>[50]</sup> | -          |     |     |     |       |

| Јр–р      | F = 24 MHz                            |            | _   | 0.9 | _   | ns    |

|           | F = 3 MHz                             |            | _   | 1.6 | _   | ns    |

|           | Jitter (long term) <sup>[50]</sup>    | -          |     |     | I   |       |

| Jperiod   | F = 24 MHz                            |            | -   | 0.9 | _   | ns    |

|           | F = 3 MHz                             |            | _   | 12  | -   | ns    |

## 11.9.3 Internal Low-Speed Oscillator

## Table 11-79. ILO DC Specifications

| Parameter       | Description       | Conditions                 | Min | Тур | Max | Units |

|-----------------|-------------------|----------------------------|-----|-----|-----|-------|

|                 | Operating current | F <sub>OUT</sub> = 1 kHz   | -   | 0.3 | 1.7 | μA    |

| I <sub>CC</sub> |                   | F <sub>OUT</sub> = 33 kHz  | -   | 1.0 | 2.6 | μA    |

|                 |                   | F <sub>OUT</sub> = 100 kHz | -   | 1.0 | 2.6 | μA    |

|                 | Leakage current   | Power down mode            | -   | 2.0 | 15  | nA    |

## Table 11-80. ILO AC Specifications

| Parameter        | Description                   | Conditions | Min | Тур | Max | Units |  |  |

|------------------|-------------------------------|------------|-----|-----|-----|-------|--|--|

|                  | Startup time, all frequencies | Turbo mode | -   | -   | 2   | ms    |  |  |

|                  | ILO frequencies (trimmed)     |            |     |     |     |       |  |  |

|                  | 100 kHz                       |            | 45  | 100 | 200 | kHz   |  |  |

| E                | 1 kHz                         |            | 0.5 | 1   | 2   | kHz   |  |  |

| F <sub>ILO</sub> | ILO frequencies (untrimmed)   |            |     |     |     |       |  |  |

|                  | 100 kHz                       |            | 30  | 100 | 300 | kHz   |  |  |

|                  | 1 kHz                         |            | 0.3 | 1   | 3.5 | kHz   |  |  |

## 11.9.4 External Crystal Oscillator

## Table 11-81. ECO AC Specifications

| Parameter | Description             | Conditions | Min | Тур | Мах | Units |

|-----------|-------------------------|------------|-----|-----|-----|-------|

| F         | Crystal frequency range |            | 4   | _   | 33  | MHz   |

## 11.9.5 External Clock Reference

## Table 11-82. External Clock Reference AC Specifications<sup>[50]</sup>

| Parameter       | Description              | Conditions                         | Min | Тур | Мах | Units |

|-----------------|--------------------------|------------------------------------|-----|-----|-----|-------|

|                 | External frequency range |                                    | 0   | _   | 33  | MHz   |

|                 | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30  | 50  | 70  | %     |

| Input edge rate |                          | V <sub>IL</sub> to V <sub>IH</sub> | 0.1 | -   | _   | V/ns  |

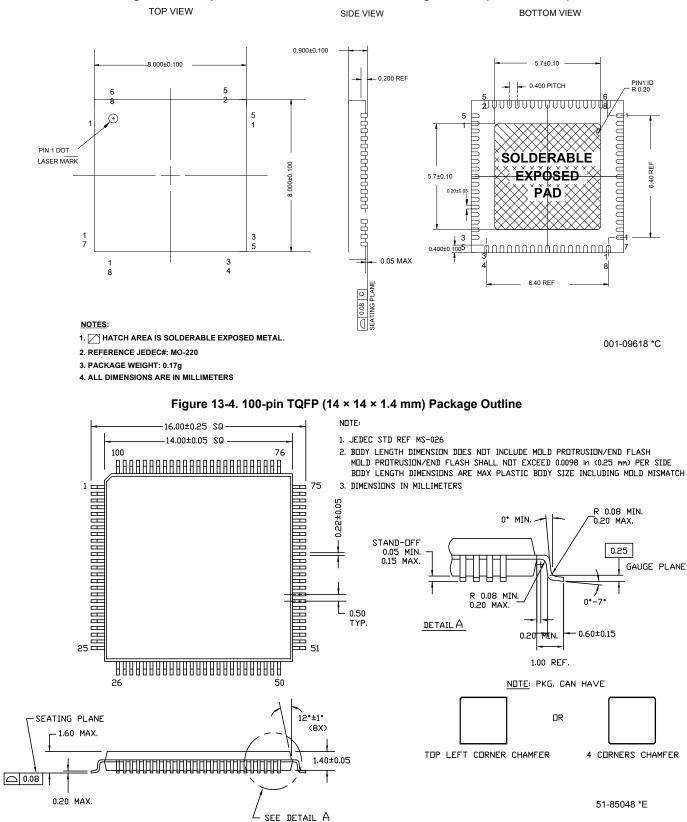

## Figure 13-3. 68-pin QFN 8×8 with 0.4 mm Pitch Package Outline (Sawn Version)

Page 110 of 117

## 14. Acronyms

## Table 14-1. Acronyms Used in this Document

| Acronym                     | Description                                                                                             |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| abus                        | analog local bus                                                                                        |  |  |

| ADC                         | analog-to-digital converter                                                                             |  |  |

| AG                          | analog global                                                                                           |  |  |

| АНВ                         | AMBA (advanced microcontroller bus archi-<br>tecture) high-performance bus, an ARM data<br>transfer bus |  |  |

| ALU                         | arithmetic logic unit                                                                                   |  |  |

| AMUXBUS                     | analog multiplexer bus                                                                                  |  |  |

| API                         | application programming interface                                                                       |  |  |

| APSR                        | application program status register                                                                     |  |  |

| ARM®                        | advanced RISC machine, a CPU architecture                                                               |  |  |

| ATM                         | automatic thump mode                                                                                    |  |  |

| BW                          | bandwidth                                                                                               |  |  |

| CAN                         | Controller Area Network, a communications protocol                                                      |  |  |

| CMRR                        | common-mode rejection ratio                                                                             |  |  |

| CPU                         | CPU central processing unit                                                                             |  |  |

| CRC                         | cyclic redundancy check, an error-checking protocol                                                     |  |  |

| DAC                         | digital-to-analog converter, see also IDAC, VDA                                                         |  |  |

| DFB                         | digital filter block                                                                                    |  |  |

| DIO                         | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                         |  |  |

| DMA                         | direct memory access, see also TD                                                                       |  |  |

| DNL                         | differential nonlinearity, see also INL                                                                 |  |  |

| DNU                         | do not use                                                                                              |  |  |

| DR                          | port write data registers                                                                               |  |  |

| DRES                        | digital logic reset                                                                                     |  |  |

| DSI                         | digital system interconnect                                                                             |  |  |

| DWT                         | data watchpoint and trace                                                                               |  |  |

| ECC                         | error correcting code                                                                                   |  |  |

| ECO                         | external crystal oscillator                                                                             |  |  |

| EEPROM                      | electrically erasable programmable read-only memory                                                     |  |  |

| EMI                         | electromagnetic interference                                                                            |  |  |

| EMIF                        | external memory interface                                                                               |  |  |

| EOC                         | end of conversion                                                                                       |  |  |

| EOF                         | end of frame                                                                                            |  |  |

| EPSR                        | execution program status register                                                                       |  |  |

| ESD electrostatic discharge |                                                                                                         |  |  |

| Acronym                  | Description                                            |  |  |

|--------------------------|--------------------------------------------------------|--|--|

| ETM                      | embedded trace macrocell                               |  |  |

| FIR                      | finite impulse response, see also IIR                  |  |  |

| FPB                      | flash patch and breakpoint                             |  |  |

| FS                       | full-speed                                             |  |  |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |  |  |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |  |  |

| IC                       | integrated circuit                                     |  |  |

| IDAC                     | current DAC, see also DAC, VDAC                        |  |  |

| IDE                      | integrated development environment                     |  |  |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |  |  |

| IIR                      | infinite impulse response, see also FIR                |  |  |

| ILO                      | internal low-speed oscillator, see also IMO            |  |  |

| IMO                      | internal main oscillator, see also ILO                 |  |  |

| INL                      | integral nonlinearity, see also DNL                    |  |  |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |  |  |

| IPOR                     | initial power-on reset                                 |  |  |

| IPSR                     | interrupt program status register                      |  |  |

| IRQ                      | interrupt request                                      |  |  |

| ITM                      | instrumentation trace macrocell                        |  |  |

| LCD                      | liquid crystal display                                 |  |  |

| LIN                      | Local Interconnect Network, a communications protocol. |  |  |

| LR                       | link register                                          |  |  |

| LUT                      | lookup table                                           |  |  |

| LVD                      | low-voltage detect, see also LVI                       |  |  |

| LVI                      | low-voltage interrupt, see also HVI                    |  |  |

| LVTTL                    | low-voltage transistor-transistor logic                |  |  |

| MAC                      | multiply-accumulate                                    |  |  |

| MCU                      | microcontroller unit                                   |  |  |

| MISO                     | master-in slave-out                                    |  |  |

| NC                       | no connect                                             |  |  |

| NMI                      | nonmaskable interrupt                                  |  |  |

| NRZ                      | non-return-to-zero                                     |  |  |

| NVIC                     | nested vectored interrupt controller                   |  |  |

| NVL                      | nonvolatile latch, see also WOL                        |  |  |

| opamp                    | operational amplifier                                  |  |  |

| PAL                      | programmable array logic, see also PLD                 |  |  |

| PC                       | program counter                                        |  |  |

PCB

printed circuit board

## Table 14-1. Acronyms Used in this Document (continued)

# 17. Revision History

| Rev. | ECN No. | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 571504  | See ECN            | HMT                | New datasheet for new device Part Number family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |