Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                 |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 48-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866pvi-047 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in real-time clock (RTC) applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C38 family supports a wide supply operating range from 1.71 V to 5.5 V. This allows operation from regulated supplies such as  $1.8 V \pm 5\%$ ,  $2.5 V \pm 10\%$ ,  $3.3 V \pm 10\%$ , or  $5.0 V \pm 10\%$ , or directly from a wide range of battery types. In addition, it provides an integrated high efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery or solar cell. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3-V supply for LCD glass drive. The boost's output is available on the Vboost pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a  $1-\mu$ A sleep mode with RTC. In the second mode, the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 24 of this datasheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for 'printf' style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 56 of this datasheet.

## 2. Pinouts

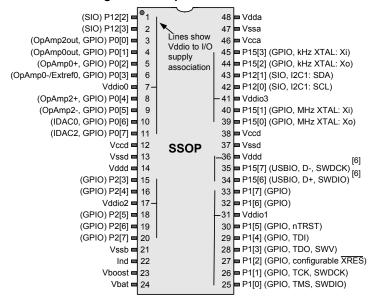

The Vddio pin that supplies a particular set of pins is indicated by the black lines drawn on the pinout diagrams in Figure 2-1 through Figure 2-4. Using the Vddio pins, a single PSoC can support multiple interface voltage levels, eliminating the need for off-chip level shifters. Each Vddio may sink up to 100 mA total to its associated I/O pins and opamps. On the 68-pin and 100-pin devices each set of Vddio associated pins may sink up to 100 mA. The 48-pin device may sink up to 100 mA total for all Vddio0 plus Vddio2 associated I/O pins and 100 mA total for all Vddio1 plus Vddio3 associated I/O pins.

### Figure 2-1. 48-pin SSOP Part Pinout

Note6. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

## TMS

JTAG test mode select programming and debug port connection.

## USBIO, D+

Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from  $V_{DDD}$  instead of from a Vddio. Pins are Do Not Use (DNU) on devices without USB.

## USBIO, D-

Provides D– connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from  $V_{DDD}$  instead of from a Vddio. Pins are Do Not Use (DNU) on devices without USB.

## Vboost

Power sense connection to boost pump.

## Vbat

Battery supply to boost pump.

## Vcca

Output of analog core regulator and input to analog core. Requires a 1- $\mu F$  capacitor to  $V_{SSA}.$  Regulator output not for external use.

## Vccd

Output of digital core regulator and input to digital core. The two  $V_{CCD}$  pins must be shorted together, with the trace between them as short as possible, and a 1-µF capacitor to  $V_{SSD}$ ; see Power System on page 24. Regulator output not for external use.

## Vdda

Supply for all analog peripherals and analog core regulator. Vdda must be the highest voltage present on the device. All other supply pins must be less than or equal to Vdda.

## Vddd

Supply for all digital peripherals and digital core regulator. Vddd must be less than or equal to Vdda.

## Vssa

Ground for all analog peripherals.

## Vssb

Ground connection for boost pump.

## Vssd

Ground for all digital logic and I/O pins.

## Vddio0, Vddio1, Vddio2, Vddio3

Supply for I/O pins. Each Vddio must be tied to a valid operating voltage (1.71 V to 5.5 V), and must be less than or equal to Vdda. If the I/O pins associated with Vddio0, Vddio2, or Vddio3 are not used then that Vddio should be tied to ground (Vssd or Vssa).

## XRES (and configurable XRES)

External reset pin. Active low with internal pull-up. In 48-pin <u>SSOP</u> parts and 48-pin QFN parts, P1[2] may be configured as XRES. In all other parts the pin is configured as a GPIO.

## 4. CPU

## 4.1 8051 CPU

The CY8C38 devices use a single cycle 8051 CPU, which is fully compatible with the original MCS-51 instruction set. The CY8C38 family uses a pipelined RISC architecture, which executes most instructions in 1 to 2 cycles to provide peak performance of up to 33 MIPS with an average of 2 cycles per instruction. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor.

The 8051 CPU subsystem includes these features:

- Single cycle 8051 CPU

- Up to 64 KB of flash memory, up to 2 KB of EEPROM, and up to 8 KB of SRAM

- Programmable nested vector interrupt controller

- DMA controller

- Peripheral HUB (PHUB)

- External memory interface (EMIF)

## 4.2 Addressing Modes

The following addressing modes are supported by the 8051:

- Direct Addressing: The operand is specified by a direct 8-bit address field. Only the internal RAM and the SFRs can be accessed using this mode.

- Indirect Addressing: The instruction specifies the register which contains the address of the operand. The registers R0 or R1 are used to specify the 8-bit address, while the data pointer (DPTR) register is used to specify the 16-bit address.

- Register Addressing: Certain instructions access one of the registers (R0 to R7) in the specified register bank. These instructions are more efficient because there is no need for an address field.

- Register Specific Instructions: Some instructions are specific to certain registers. For example, some instructions always act on the accumulator. In this case, there is no need to specify the operand.

- Immediate Constants: Some instructions carry the value of the constants directly instead of an address.

- Indexed Addressing: This type of addressing can be used only for a read of the program memory. This mode uses the Data Pointer as the base and the accumulator value as an offset to read a program memory.

- Bit Addressing: In this mode, the operand is one of 256 bits.

## 4.3 Instruction Set

The 8051 instruction set is highly optimized for 8-bit handling and Boolean operations. The types of instructions supported include:

- Arithmetic instructions

- Logical instructions

- Data transfer instructions

- Boolean instructions

- Program branching instructions

## 4.3.1 Instruction Set Summary

## 4.3.1.1 Arithmetic Instructions

Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions. Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations. Table 4-1 lists the different arithmetic instructions.

#### Table 4-1. Arithmetic Instructions

| Mnemonic       | Description                                          | Bytes | Cycles |

|----------------|------------------------------------------------------|-------|--------|

| ADD A,Rn       | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct   | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri      | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data    | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn      | Add register to accumulator with carry               | 1     | 1      |

| ADDC A,Direct  | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri     | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data   | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn      | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A, Direct | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri     | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data   | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A          | Increment accumulator                                | 1     | 1      |

| INC Rn         | Increment register                                   | 1     | 2      |

| INC Direct     | Increment direct byte                                | 2     | 3      |

| INC @Ri        | Increment indirect RAM                               | 1     | 3      |

| DEC A          | Decrement accumulator                                | 1     | 1      |

| DEC Rn         | Decrement register                                   | 1     | 2      |

| DEC Direct     | Decrement direct byte                                | 2     | 3      |

| DEC @Ri        | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR       | Increment data pointer                               | 1     | 1      |

| MUL            | Multiply accumulator and B                           | 1     | 2      |

| DIV            | Divide accumulator by B                              | 1     | 6      |

| DAA            | Decimal adjust accumulator                           | 1     | 3      |

## 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

| Table 4-2. | Logical | Instructions |

|------------|---------|--------------|

|------------|---------|--------------|

|     | Mnemonic  | Bytes                             | Cycles |   |

|-----|-----------|-----------------------------------|--------|---|

| ANL | A,Rn      | AND register to accumulator       | 1      | 1 |

| ANL | A,Direct  | AND direct byte to accumulator    | 2      | 2 |

| ANL | A,@Ri     | AND indirect RAM to accumulator   | 1      | 2 |

| ANL | A,#data   | AND immediate data to accumulator | 2      | 2 |

| ANL | Direct, A | AND accumulator to direct byte    | 2      | 3 |

## 6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

#### Table 6-2. Power Modes

Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and Real Time Clock functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 on page 26 illustrates the allowable transitions between power modes

| Power Modes         | Description                                                                                                                                                                                                                    | <b>Entry Condition</b>                     | Wakeup Source                                           | Active Clocks         | Regulator                                                                                                                         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all<br>peripherals available<br>(programmable)                                                                                                                                                      | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off                  | Manual register<br>entry                   | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                                          | Manual register<br>entry                   | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | ILO/kHzECO            | Both digital and analog<br>regulators buzzed.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used. |

| Hibernate           | All subsystems automatically<br>disabled<br>Lowest power consuming mode<br>with all peripherals and internal<br>regulators disabled, except<br>hibernate regulator is enabled<br>Configuration and memory<br>contents retained | Manual register<br>entry                   | PICU                                                    |                       | Only hibernate regulator<br>active.                                                                                               |

#### Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(typ)       | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|------------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | -              | 1.2 mA <sup>[13]</sup> | Yes               | All                  | All                 | All                        | -                                                       | All               |

| Alternate<br>Active | -              | -                      | User<br>defined   | All                  | All                 | All                        | -                                                       | All               |

| Sleep               | <15 µs         | 1 µA                   | No                | l <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | XRES, LVD,<br>WDR |

| Hibernate           | <100 µs        | 200 nA                 | No                | None                 | None                | None                       | PICU                                                    | XRES              |

Note

13. Bus clock off. Execute from CPU instruction buffer at 6 MHz. See Table 11-2 on page 60.

# PSoC<sup>®</sup> 3: CY8C38 Family Datasheet

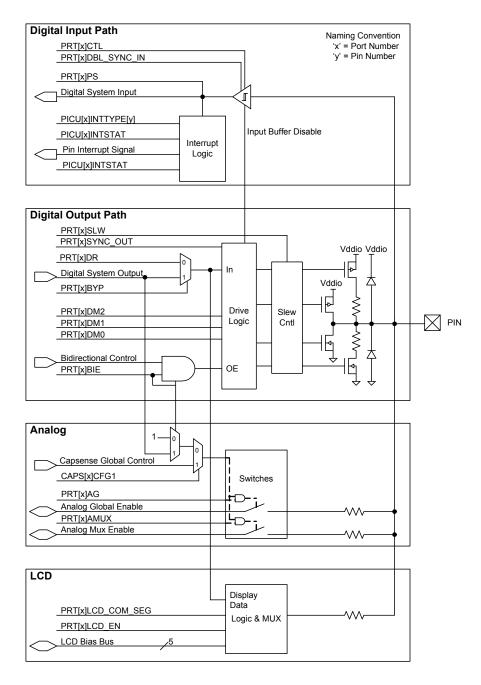

## Figure 6-8. GPIO Block Diagram

## 6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage tolerance feature at any operating  $\mathsf{V}_{\text{DD}}.$

- There are no current limitations for the SIO pins as they present a high impedance load to the external circuit where Vddio ≤ V<sub>IN</sub> ≤ 5.5 V.

- The GPIO pins must be limited to 100 µA using a current limiting resistor. GPIO pins clamp the pin voltage to approximately one diode above the Vddio supply where Vddio ≤ V<sub>IN</sub> ≤ V<sub>DDA</sub>.

- In case of a GPIO pin configured for analog input/output, the analog voltage on the pin must not exceed the Vddio supply voltage to which the GPIO belongs.

A common application for this feature is connection to a bus such as I<sup>2</sup>C where different devices are running from different supply voltages. In the I<sup>2</sup>C case, the PSoC chip is configured into the Open Drain, Drives Low mode for the SIO pin. This allows an external pull-up to pull the I<sup>2</sup>C bus voltage above the PSoC pin supply. For example, the PSoC chip could operate at 1.8 V, and an external device could run from 5 V. Note that the SIO pin's V<sub>IH</sub> and V<sub>IL</sub> levels are determined by the associated Vddio supply pin. The I/O pin must be configured into a high impedance drive mode, open drain low drive mode, or pull-down drive mode, for over voltage tolerance to work properly. Absolute maximum ratings for the device must be observed for all I/O pins.

### 6.4.16 Reset Configuration

While reset is active all I/Os are reset to and held in the High Impedance Analog state. After reset is released, the state can be reprogrammed on a port-by-port basis to pull-down or pull-up. To ensure correct reset operation, the port reset configuration data is stored in special nonvolatile registers. The stored reset data is automatically transferred to the port reset configuration registers at reset release.

### 6.4.17 Low-Power Functionality

In all low-power modes the I/O pins retain their state until the part is awakened and changed or reset. To awaken the part, use a pin interrupt, because the port interrupt logic continues to function in all low-power modes.

## 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in Pinouts on page 5. The special features are:

- Digital

- □ 4- to 33-MHz crystal oscillator

- 32.768-kHz crystal oscillator

- Wake from sleep on I<sup>2</sup>C address match. Any pin can be used for I<sup>2</sup>C if wake from sleep is not required.

- □ JTAG interface pins

- BWD interface pins

- □ SWV interface pins

- External reset

- Analog

- Opamp inputs and outputs

- High current IDAC outputs

- External reference inputs

## 6.4.19 JTAG Boundary Scan

The device supports standard JTAG boundary scan chains on all I/O pins for board level test.

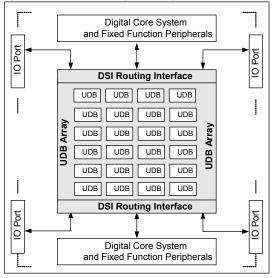

## 7. Digital Subsystem

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. You do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

The main components of the digital programmable system are:

- UDB These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal digital block array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the Digital System Interconnect.

- Digital system interconnect (DSI) Digital signals from UDBs, fixed function peripherals, I/O pins, interrupts, DMA, and other system core signals are attached to the digital system interconnect to implement full featured device connectivity. The DSI allows any digital function to any pin or other feature routability when used with the universal digital block array.

### Figure 7-1. CY8C38 Digital Programmable Architecture

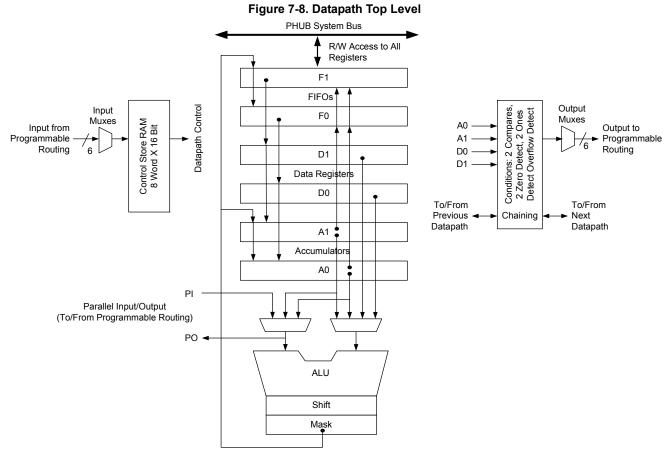

## 7.2.2 Datapath Module

The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators and many others.

## 7.2.2.1 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

| Table 7-1. | Working | Datapath | Registers |

|------------|---------|----------|-----------|

|------------|---------|----------|-----------|

| Name      | Function       | Description                                                                                                                                                                                                                 |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                                  |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                                                 |

| F0 and F1 | FIFOs          | These are the primary interface<br>to the system bus. They can be a<br>data source for the data registers<br>and accumulators or they can<br>capture data from the<br>accumulators or ALU. Each FIFO<br>is four bytes deep. |

## 7.2.2.2 Dynamic Datapath Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word × 16-bit configuration RAM, which stores eight unique 16-bit wide configurations. The address input to this RAM controls the sequence, and can be routed from any block connected to the UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

## ALU

The ALU performs eight general purpose functions. They are: Increment

- Decrement

- Add

- Subtract

- Logical AND

- Logical OR

- Logical XOR

- Pass, used to pass a value through the ALU to the shift register, mask, or another UDB register.

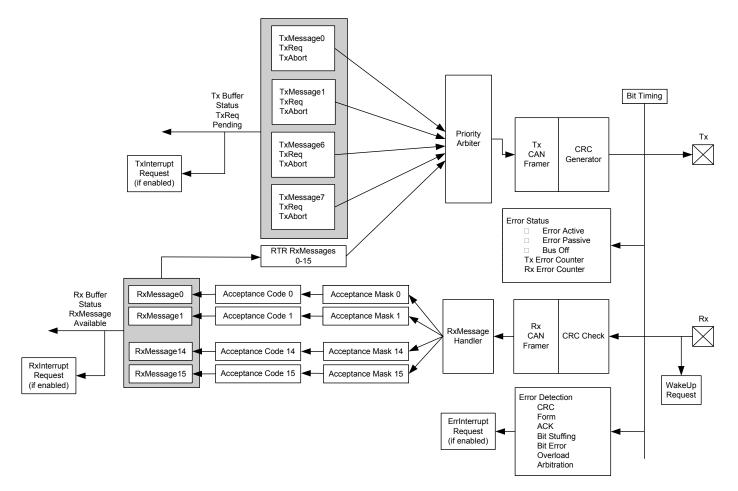

Figure 7-19. CAN Controller Block Diagram

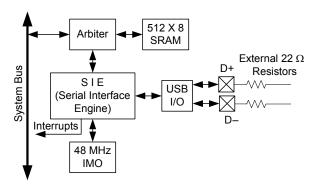

## 7.6 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 28.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual memory management with no DMA access

- Manual memory management with manual DMA access

Automatic memory management with automatic DMA

- access

- Internal 3.3-V regulator for transceiver

- Internal 48-MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB reset, suspend, and resume operations

- Bus-powered and self-powered modes

### Figure 7-20. USB

## 8.11.1 Down Mixer

The SC/CT block can be used as a mixer to down convert an input signal. This circuit is a high bandwidth passive sample network that can sample input signals up to 14 MHz. This sampled value is then held using the opamp with a maximum clock rate of 4 MHz. The output frequency is at the difference between the input frequency and the highest integer multiple of the Local Oscillator that is less than the input.

#### 8.11.2 First Order Modulator - SC Mode

A first order modulator is constructed by placing the SC/CT block in an integrator mode and using a comparator to provide a 1-bit feedback to the input. Depending on this bit, a reference voltage is either subtracted or added to the input signal. The block output is the output of the comparator and not the integrator in the modulator case. The signal is downshifted and buffered and then processed by a decimator to make a delta-sigma converter or a counter to make an incremental converter. The accuracy of the sampled data from the first-order modulator is determined from several factors.

The main application for this modulator is for a low-frequency ADC with high accuracy. Applications include strain gauges, thermocouples, precision voltage, and current measurement.

## 9. Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are fully compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because you cannot access the device later. Because all programming, debug, and test interfaces are disabled when device security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

#### Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

## 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG clock frequency can be up to 8 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers, whichever is least. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as General Purpose I/O (GPIO) instead. The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

### 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D– pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output. SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8 µs (key window) after reset, that pin pair (JTAG or USB) receives a predetermined sequence of 1s and 0s. SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

## 10. Development Support

The CY8C38 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

## 10.1 Documentation

A suite of documentation, supports the CY8C38 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component datasheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes:** PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

## 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

## 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C38 family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

## Table 11-6. Inductive Boost Regulator DC Specifications (continued)

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 2.4 V,  $V_{OUT}$  = 2.7 V,  $I_{OUT}$  = 40 mA,  $F_{SW}$  = 400 kHz,  $L_{BOOST}$  = 22 µH,  $C_{BOOST}$  = 22 µF || 0.1 µF

| Parameter           | Description                             | Conditions                 | Min  | Тур  | Max  | Units |  |  |

|---------------------|-----------------------------------------|----------------------------|------|------|------|-------|--|--|

| V <sub>OUT</sub>    | Boost voltage range <sup>[27, 28]</sup> |                            |      |      |      |       |  |  |

|                     | 1.8 V                                   |                            | 1.71 | 1.80 | 1.89 | V     |  |  |

|                     | 1.9 V                                   |                            | 1.81 | 1.90 | 2.00 | V     |  |  |

|                     | 2.0 V                                   |                            | 1.90 | 2.00 | 2.10 | V     |  |  |

|                     | 2.4 V                                   |                            | 2.28 | 2.40 | 2.52 | V     |  |  |

|                     | 2.7 V                                   |                            | 2.57 | 2.70 | 2.84 | V     |  |  |

|                     | 3.0 V                                   |                            | 2.85 | 3.00 | 3.15 | V     |  |  |

|                     | 3.3 V                                   |                            | 3.14 | 3.30 | 3.47 | V     |  |  |

|                     | 3.6 V                                   |                            | 3.42 | 3.60 | 3.78 | V     |  |  |

|                     | 5.0 V                                   | External diode required    | 4.75 | 5.00 | 5.25 | V     |  |  |

| Reg <sub>LOAD</sub> | Load regulation                         |                            | -    | -    | 3.8  | %     |  |  |

| Reg <sub>LINE</sub> | Line regulation                         |                            | -    | -    | 4.1  | %     |  |  |

| ηουτ                | Efficiency                              | L <sub>BOOST</sub> = 10 μH | 70   | 85   | -    | %     |  |  |

|                     |                                         | L <sub>BOOST</sub> = 22 μH | 82   | 90   | _    | %     |  |  |

## Table 11-7. Inductive Boost Regulator AC Specifications

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 2.4 V,  $V_{OUT}$  = 2.7 V,  $I_{OUT}$  = 40 mA,  $F_{SW}$  = 400 kHz,  $L_{BOOST}$  = 22 µH,  $C_{BOOST}$  = 22 µF || 0.1 µF.

| Parameter           | Description                      | Conditions                                                                    | Min | Тур              | Мах | Units |

|---------------------|----------------------------------|-------------------------------------------------------------------------------|-----|------------------|-----|-------|

| V <sub>RIPPLE</sub> | Ripple voltage<br>(peak-to-peak) | V <sub>OUT</sub> = 1.8 V, F <sub>SW</sub> = 400 kHz, I <sub>OUT</sub> = 10 mA | -   | -                | 100 | mV    |

| F <sub>SW</sub>     | Switching frequency              |                                                                               | Ι   | 0.1,0.4,<br>or 2 | -   | MHz   |

### Table 11-8. Recommended External Components for Boost Circuit

| Parameter          | Description                                     | Conditions                                                | Min | Тур | Max | Units |

|--------------------|-------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|-------|

| L <sub>BOOST</sub> | Boost inductor                                  |                                                           | 4.7 | 10  | 47  | μH    |

| C <sub>BOOST</sub> | Filter capacitor <sup>[27]</sup>                |                                                           | 10  | 22  | 47  | μF    |

| I <sub>F</sub>     | External Schottky diode average forward current | External Schottky diode is required for $V_{OUT}$ > 3.6 V | 1   | _   | _   | A     |

| V <sub>R</sub>     |                                                 |                                                           | 20  | _   | _   | V     |

Notes

27. Based on device characterization (Not production tested).

28. At boost frequency of 2 MHz, Vboost is limited to 2 x Vbat. At 400 kHz, Vboost is limited to 4 x Vbat.

## 11.5.2 Delta-sigma ADC

Unless otherwise specified, operating conditions are:

- Operation in continuous sample mode

- fclk = 3.072 MHz for resolution = 16 to 20 bits; fclk = 6.144 MHz for resolution = 8 to 15 bits

- Reference = 1.024 V internal reference bypassed on P3.2 or P0.3

- Unless otherwise specified, all charts and graphs show typical values

## Table 11-20. 20-bit Delta-sigma ADC DC Specifications

| Parameter | Description                                                       | Conditions                                                           | Min              | Тур                 | Max                  | Units  |

|-----------|-------------------------------------------------------------------|----------------------------------------------------------------------|------------------|---------------------|----------------------|--------|

|           | Resolution                                                        |                                                                      | 8                | -                   | 20                   | bits   |

|           | Number of channels, single ended                                  |                                                                      | -                | -                   | No. of<br>GPIO       | -      |

|           | Number of channels, differential                                  | Differential pair is formed using a pair of GPIOs.                   | _                | -                   | No. of<br>GPIO/2     | -      |

|           | Monotonic                                                         | Yes                                                                  | -                | -                   | -                    | -      |

| Ge        | Gain error                                                        | Buffered, buffer gain = 1, modulator<br>gain = 1, 16-bit mode, 25 °C | -                | -                   | ±0.2                 | %      |

| Gd        | Gain drift                                                        | Buffered, buffer gain = 1, modulator<br>gain = 1, 16-bit mode        | -                | -                   | 50                   | ppm/°C |

| Vos       | Input offset voltage                                              | Buffered                                                             | 1                | -                   | ±0.1                 | mV     |

| TCVos     | ADC TC input offset voltage                                       | Temperature coefficient, input offset voltage                        | _                | -                   | 55                   | µV/°C  |

|           | Input voltage range, single ended <sup>[33]</sup>                 |                                                                      | V <sub>SSA</sub> | -                   | V <sub>DDA</sub>     | V      |

|           | Input voltage range, differential unbuf-<br>fered <sup>[33]</sup> |                                                                      | $V_{SSA}$        | -                   | V <sub>DDA</sub>     | V      |

|           | Input voltage range, differential,<br>buffered <sup>[33]</sup>    |                                                                      | $V_{SSA}$        | -                   | V <sub>DDA</sub> – 1 | V      |

| PSRRb     | Power supply rejection ratio, buffered <sup>[33]</sup>            | Buffer gain = 1, 16-bit,<br>Range = ±1.024 V                         | 90               | -                   | -                    | dB     |

| CMRRb     | Common mode rejection ratio, buffered <sup>[33]</sup>             | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V                         | 85               | -                   | -                    | dB     |

| INL20     | Integral non linearity <sup>[33]</sup>                            | Range = ±1.024 V, unbuffered                                         | -                | -                   | ±32                  | LSB    |

| DNL20     | Differential non linearity <sup>[33]</sup>                        | Range = ±1.024 V, unbuffered                                         | -                | -                   | ±1                   | LSB    |

| INL16     | Integral non linearity <sup>[33]</sup>                            | Range = ±1.024 V, unbuffered                                         | -                | -                   | ±2                   | LSB    |

| DNL16     | Differential non linearity <sup>[33]</sup>                        | Range = ±1.024 V, unbuffered                                         | -                | -                   | ±1                   | LSB    |

| INL12     | Integral non linearity <sup>[33]</sup>                            | Range = ±1.024 V, unbuffered                                         | -                | -                   | ±1                   | LSB    |

| DNL12     | Differential non linearity <sup>[33]</sup>                        | Range = ±1.024 V, unbuffered                                         | -                | -                   | ±1                   | LSB    |

| INL8      | Integral non linearity <sup>[33]</sup>                            | Range = ±1.024 V, unbuffered                                         | Ι                | -                   | ±1                   | LSB    |

| DNL8      | Differential non linearity <sup>[33]</sup>                        | Range = ±1.024 V, unbuffered                                         | -                | -                   | ±1                   | LSB    |

| Rin_Buff  | ADC input resistance                                              | Input buffer used                                                    | 10               | -                   | -                    | MΩ     |

| Rin_ADC16 | ADC input resistance                                              | Input buffer bypassed, 16-bit, Range<br>= ±1.024 V                   | _                | 74 <sup>[34]</sup>  | -                    | kΩ     |

| Rin_ADC12 | ADC input resistance                                              | Input buffer bypassed, 12 bit, Range<br>= ±1.024 V                   | _                | 148 <sup>[34]</sup> | -                    | kΩ     |

| Cin_G1    | ADC input capacitance <sup>[33]</sup>                             | Gain = 1                                                             | _                | 5                   | -                    | pF     |

#### Notes

By using switched capacitors at the ADC input an effective input resistance is created. Holding the gain and number of bits constant, the resistance is proportional to the inverse of the clock frequency. This value is calculated, not measured. For more information see the Technical Reference Manual.

<sup>33.</sup> Based on device characterization (not production tested).

## 11.5.3 Voltage Reference

## Table 11-25. Voltage Reference Specifications

See also ADC external reference specifications in Section 11.5.2.

| Parameter        | Description                                       | Conditions       | Min              | Тур   | Max              | Units   |

|------------------|---------------------------------------------------|------------------|------------------|-------|------------------|---------|

| V <sub>REF</sub> | Precision reference voltage                       | Initial trimming | 1.023<br>(–0.1%) | 1.024 | 1.025<br>(+0.1%) | V       |

|                  | Temperature drift <sup>[36]</sup>                 |                  | -                | -     | 20               | ppm/°C  |

|                  | Long term drift                                   |                  | -                | 100   | -                | ppm/Khr |

|                  | Thermal cycling drift (stability) <sup>[36]</sup> |                  | -                | 100   | -                | ppm     |

## 11.5.4 Analog Globals

## Table 11-26. Analog Globals Specifications

| Parameter | Description                                                  | Conditions               | Min | Тур | Max  | Units |

|-----------|--------------------------------------------------------------|--------------------------|-----|-----|------|-------|

| Rppag     | Resistance pin-to-pin through analog global <sup>[37]</sup>  | V <sub>DDA</sub> = 3.0 V | _   | 939 | 1461 | Ω     |

| Rppmuxbus | Resistance pin-to-pin through analog mux bus <sup>[37]</sup> | V <sub>DDA</sub> = 3.0 V | -   | 721 | 1135 | Ω     |

## 11.5.5 Comparator

## Table 11-27. Comparator DC Specifications

| Parameter         | Description                                       | Conditions                                 | Min              | Тур | Max                    | Units |

|-------------------|---------------------------------------------------|--------------------------------------------|------------------|-----|------------------------|-------|

| V <sub>OS</sub>   | Input offset voltage in fast mode                 | Factory trim, Vdda > 2.7 V,<br>Vin ≥ 0.5 V | -                |     | 10                     | mV    |

|                   | Input offset voltage in slow mode                 | Factory trim, Vin $\ge 0.5 \text{ V}$      | -                |     | 9                      | mV    |

| V                 | Input offset voltage in fast mode <sup>[38]</sup> | Custom trim                                | -                | _   | 4                      | mV    |

| V <sub>OS</sub>   | Input offset voltage in slow mode <sup>[38]</sup> | Custom trim                                | -                | _   | 4                      | mV    |

| V <sub>OS</sub>   | Input offset voltage in ultra<br>low-power mode   |                                            | -                | ±12 | -                      | mV    |

| V <sub>HYST</sub> | Hysteresis                                        | Hysteresis enable mode                     | -                | 10  | 32                     | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                         | High current / fast mode                   | V <sub>SSA</sub> | _   | V <sub>DDA</sub> – 0.1 | V     |

|                   |                                                   | Low current / slow mode                    | V <sub>SSA</sub> | _   | V <sub>DDA</sub>       | V     |

|                   |                                                   | Ultra low power mode                       | V <sub>SSA</sub> | _   | V <sub>DDA</sub> - 0.9 | V     |

| CMRR              | Common mode rejection ratio                       |                                            | -                | 50  | -                      | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode <sup>[36]</sup>       |                                            | -                | _   | 400                    | μA    |

|                   | Low current mode/slow mode <sup>[36]</sup>        |                                            | -                | -   | 100                    | μA    |

|                   | Ultra low-power mode <sup>[36]</sup>              |                                            | -                | 6   | -                      | μA    |

#### Notes

- 36. Based on device characterization (Not production tested).

- 37. The resistance of the analog global and analog mux bus is high if  $V_{DDA} \le 2.7$  V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

- 38. The recommended procedure for using a custom trim value for the on-chip comparators can be found in the TRM.

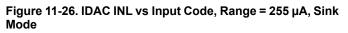

Table 11-29. IDAC DC Specifications (continued)

| Parameter       | Description                 | Conditions                                   | Min | Тур | Max | Units |

|-----------------|-----------------------------|----------------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Operating current, code = 0 | Slow mode, source mode, range =<br>31.875 μA | -   | -   | 44  | μA    |

|                 |                             | Slow mode, source mode, range = 255 μA,      | -   | -   | 33  | μA    |

|                 |                             | Slow mode, source mode, range = 2.04 mA      | _   | -   | 33  | μA    |

|                 |                             | Slow mode, sink mode, range =<br>31.875 μΑ   | -   | -   | 36  | μA    |

|                 |                             | Slow mode, sink mode, range =<br>255 μA      | -   | -   | 33  | μA    |

|                 |                             | Slow mode, sink mode, range = 2.04 mA        | -   | -   | 33  | μA    |

|                 |                             | Fast mode, source mode, range =<br>31.875 μΑ | -   | -   | 310 | μA    |

|                 |                             | Fast mode, source mode, range = 255 μA       | -   | -   | 305 | μA    |

|                 |                             | Fast mode, source mode, range = 2.04 mA      | -   | -   | 305 | μA    |

|                 |                             | Fast mode, sink mode, range =<br>31.875 μΑ   | -   | -   | 310 | μA    |

|                 |                             | Fast mode, sink mode, range = 255 $\mu$ A    | -   | -   | 300 | μA    |

|                 |                             | Fast mode, sink mode, range = 2.04 mA        | _   | -   | 300 | μA    |

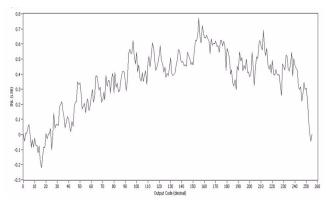

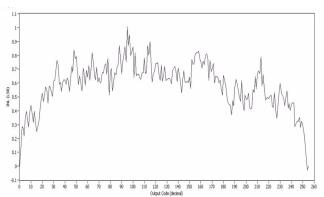

# Figure 11-25. IDAC INL vs Input Code, Range = 255 $\mu$ A, Source Mode

## 11.5.10 Programmable Gain Amplifier

The PGA is created using a SC/CT analog block; see the PGA component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, operating conditions are:

- Operating temperature = 25 °C for typical values

- Unless otherwise specified, all charts and graphs show typical values

## Table 11-37. PGA DC Specifications

| Parameter | Description                                 | Conditions                                                                        | Min                    | Тур | Max                     | Units       |

|-----------|---------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-----|-------------------------|-------------|

| Vin       | Input voltage range                         | Power mode = minimum                                                              | Vssa                   | -   | Vdda                    | V           |

| Vos       | Input offset voltage                        | Power mode = high,<br>gain = 1                                                    | -                      | -   | 10                      | mV          |

| TCVos     | Input offset voltage drift with temperature | Power mode = high,<br>gain = 1                                                    | -                      | -   | ±30                     | µV/°C       |

| Ge1       | Gain error, gain = 1                        |                                                                                   | -                      | -   | ±0.15                   | %           |

| Ge16      | Gain error, gain = 16                       |                                                                                   | -                      | -   | ±2.5                    | %           |

| Ge50      | Gain error, gain = 50                       |                                                                                   | -                      | -   | ±5                      | %           |

| Vonl      | DC output nonlinearity                      | Gain = 1                                                                          | -                      | -   | ±0.01                   | % of<br>FSR |

| Cin       | Input capacitance                           |                                                                                   | _                      | _   | 7                       | pF          |

| Voh       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | V <sub>DDA</sub> -0.15 | -   | _                       | V           |

| Vol       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | -                      | -   | V <sub>SSA</sub> + 0.15 | V           |

| Vsrc      | Output voltage under load                   | lload = 250 µA, Vdda ≥ 2.7V, power mode = high                                    | -                      | -   | 300                     | mV          |

| ldd       | Operating current                           | Power mode = high                                                                 | -                      | 1.5 | 1.65                    | mA          |

| PSRR      | Power supply rejection ratio                |                                                                                   | 48                     | -   | _                       | dB          |

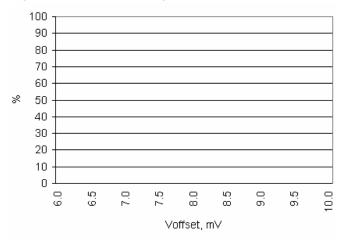

Figure 11-43. Voffset Histogram, 1000 Samples, Vdda = 5 V

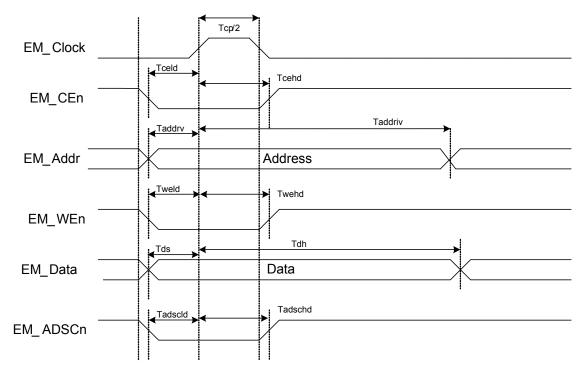

Figure 11-51. Synchronous Write Cycle Timing

## Table 11-66. Synchronous Write Cycle Specifications

| Parameter | Description                       | Conditions       | Min     | Тур | Max | Units |

|-----------|-----------------------------------|------------------|---------|-----|-----|-------|

| Т         | EMIF clock Period <sup>[45]</sup> | Vdda $\ge$ 3.3 V | 30.3    | _   | -   | nS    |

| Tcp/2     | EM_Clock pulse high               |                  | T/2     | -   | -   | nS    |

| Tceld     | EM_CEn low to EM_Clock high       |                  | 5       | -   | -   | nS    |

| Tcehd     | EM_Clock high to EM_CEn high      |                  | T/2 – 5 | -   | -   | nS    |

| Taddrv    | EM_Addr valid to EM_Clock high    |                  | 5       | -   | -   | nS    |

| Taddriv   | EM_Clock high to EM_Addr invalid  |                  | T/2 – 5 | -   | -   | nS    |

| Tweld     | EM_WEn low to EM_Clock high       |                  | 5       | -   | -   | nS    |

| Twehd     | EM_Clock high to EM_WEn high      |                  | T/2 – 5 | -   | -   | nS    |

| Tds       | Data valid before EM_Clock high   |                  | 5       | -   | -   | nS    |

| Tdh       | Data invalid after EM_Clock high  |                  | Т       | -   | -   | nS    |

| Tadscld   | EM_ADSCn low to EM_Clock high     |                  | 5       | -   | -   | nS    |

| Tadschd   | EM_Clock high to EM_ADSCn high    |                  | T/2 – 5 | _   | -   | nS    |

## 11.9.6 Phase-Locked Loop

## Table 11-83. PLL DC Specifications

| Parameter       | Description           | Conditions               | Min | Тур | Max | Units |

|-----------------|-----------------------|--------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | PLL operating current | In = 3 MHz, Out = 67 MHz | _   | 400 | _   | μA    |

|                 |                       | In = 3 MHz, Out = 24 MHz | -   | 200 | _   | μA    |

#### Table 11-84. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Мах | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[51]</sup>        |                     | 1   | -   | 48  | MHz   |

|             | PLL intermediate frequency <sup>[52]</sup> | Output of prescaler | 1   | -   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[51]</sup>       |                     | 24  | -   | 67  | MHz   |

|             | Lock time at startup                       |                     | -   | -   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[53]</sup>               |                     | -   | -   | 250 | ps    |

Notes

51. This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL. 52. PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16. 53. Based on device characterization (Not production tested).

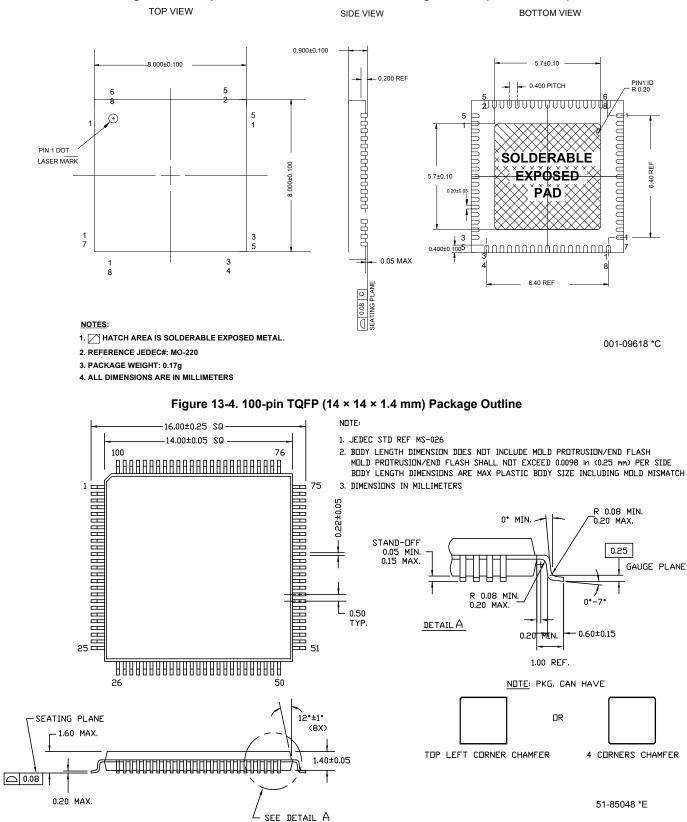

## Figure 13-3. 68-pin QFN 8×8 with 0.4 mm Pitch Package Outline (Sawn Version)

Page 110 of 117

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |

|-------------------|--------------------------------------------------------------|

| PGA               | programmable gain amplifier                                  |

| PHUB              | peripheral hub                                               |

| PHY               | physical layer                                               |

| PICU              | port interrupt control unit                                  |

| PLA               | programmable logic array                                     |

| PLD               | programmable logic device, see also PAL                      |

| PLL               | phase-locked loop                                            |

| PMDD              | package material declaration datasheet                       |

| POR               | power-on reset                                               |

| PRES              | precise power-on reset                                       |

| PRS               | pseudo random sequence                                       |

| PS                | port read data register                                      |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |

| PSRR              | power supply rejection ratio                                 |

| PWM               | pulse-width modulator                                        |

| RAM               | random-access memory                                         |

| RISC              | reduced-instruction-set computing                            |

| RMS               | root-mean-square                                             |

| RTC               | real-time clock                                              |

| RTL               | register transfer language                                   |

| RTR               | remote transmission request                                  |

| RX                | receive                                                      |

| SAR               | successive approximation register                            |

| SC/CT             | switched capacitor/continuous time                           |

| SCL               | I <sup>2</sup> C serial clock                                |

| SDA               | I <sup>2</sup> C serial data                                 |

| S/H               | sample and hold                                              |

| SINAD             | signal to noise and distortion ratio                         |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |

| SOC               | start of conversion                                          |

| SOF               | start of frame                                               |

| SPI               | Serial Peripheral Interface, a communications protocol       |

| SR                | slew rate                                                    |

| SRAM              | static random access memory                                  |

| SRES              | software reset                                               |

| SWD               | serial wire debug, a test protocol                           |

| SWV               | single-wire viewer                                           |

| TD                | transaction descriptor, see also DMA                         |

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                               |

|---------|---------------------------------------------------------------------------|

| THD     | total harmonic distortion                                                 |

| TIA     | transimpedance amplifier                                                  |

| TRM     | technical reference manual                                                |

| TTL     | transistor-transistor logic                                               |

| ТΧ      | transmit                                                                  |

| UART    | Universal Asynchronous Transmitter Receiver, a<br>communications protocol |

| UDB     | universal digital block                                                   |

| USB     | Universal Serial Bus                                                      |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port                 |

| VDAC    | voltage DAC, see also DAC, IDAC                                           |

| WDT     | watchdog timer                                                            |

| WOL     | write once latch, see also NVL                                            |

| WRES    | watchdog timer reset                                                      |

| XRES    | external reset I/O pin                                                    |

| XTAL    | crystal                                                                   |

## **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

## **16. Document Conventions**

- 16.1 Units of Measure

- Table 16-1. Units of Measure

| Symbol | Unit of Measure        |

|--------|------------------------|

| °C     | degrees Celsius        |

| dB     | decibels               |

| fF     | femtofarads            |

| Hz     | hertz                  |

| KB     | 1024 bytes             |

| kbps   | kilobits per second    |

| Khr    | kilohours              |

| kHz    | kilohertz              |

| kΩ     | kilohms                |

| ksps   | kilosamples per second |

| LSB    | least significant bit  |

| Mbps   | megabits per second    |

| MHz    | megahertz              |

| MΩ     | megaohms               |

| Msps   | megasamples per second |