Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                    |

|-------------------------|-----------------------------------------------------------|

| Туре                    | Floating Point                                            |

| Interface               | SCI, SPI                                                  |

| Clock Rate              | 16MHz                                                     |

| Non-Volatile Memory     | -                                                         |

| On-Chip RAM             | -                                                         |

| Voltage - I/O           | -                                                         |

| Voltage - Core          | 5.00V                                                     |

| Operating Temperature   | 0°C ~ 70°C (TA)                                           |

| Mounting Type           | Surface Mount                                             |

| Package / Case          | 68-LCC (J-Lead)                                           |

| Supplier Device Package | 68-PLCC                                                   |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68882ei16a |

|                         |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

uses a subset of the general purpose coprocessor interface supported by the MC68020 or MC68030. Features of the interface implemented in the MC68882 are as follows:

- The main processor(s) and MC68882 communicate via standard M68000 bus cycles.

- The main processor(s) and MC68882 communications are not dependent upon the architecture of the individual devices (e.g., instruction pipes or caches, addressing modes).

- The main processor(s) and MC68882 may operate at different clock speeds.

- MC68882 instructions utilize all addressing modes provided by the main processor.

- All effective addresses are calculated by the main processor at the request of the coprocessor.

- All data transfers are performed by the main processor at the request of the MC68882.

- Overlapped (concurrent) instruction execution enhances throughput while maintaining the programmer's model of sequential instruction execution.

- Coprocessor detection of exceptions which require a trap to be taken are serviced by the main processor at the request of the MC68882.

- Support of virtual memory/virtual machine systems is provided via the FSAVE and FRESTORE instructions.

- Up to eight coprocessors may reside in a system simultaneously. Multiple coprocessors of the same type are allowed.

- Systems may use software emulation of the MC68882 without reassembling or relinking user software.

MC68020 or MC68030 programmer can view the MC68882 registers as though the registers are resident in the MC68020 or MC68030. Thus, a MC68020 or MC68030 and an MC68882 device pair functions as one processor with eight integer data registers, eight address registers, and eight floating-point data registers supporting seven floating-point and integer data types.

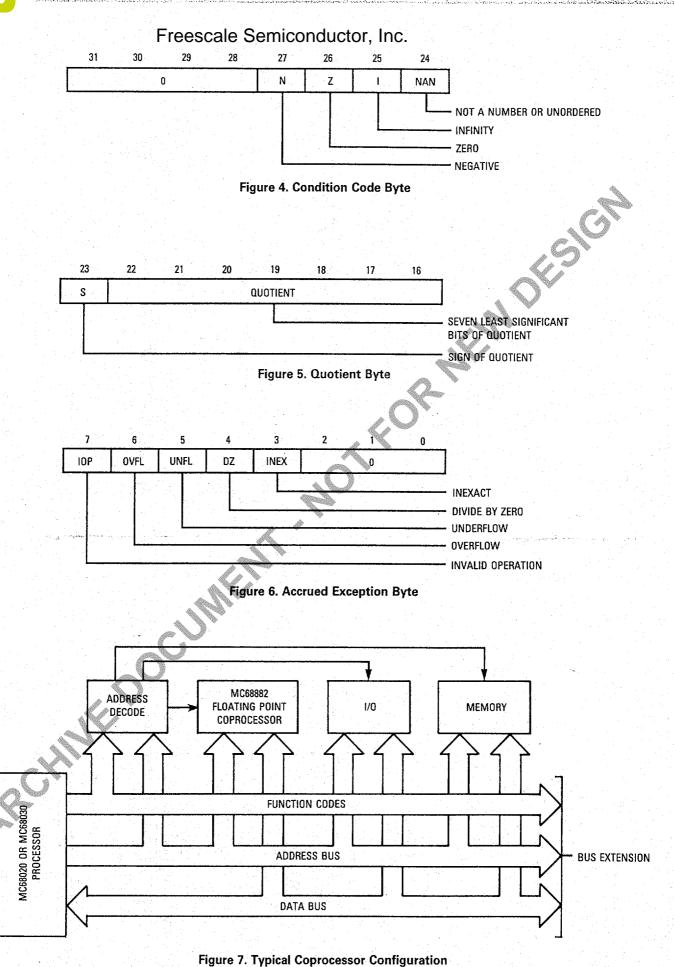

The MC68882 programming model is shown in Figures 1 through 6 and consists of the following:

- Eight 80-bit floating-point data registers (FP0-FP7). These registers are analogous to the integer data registers (D0-D7) and are completely general purpose (i.e., any instruction can use any register).

- A 32-bit control register that contains enable bits for each class of exception trap, and mode bits to set the user-selectable rounding and precision modes.

- A 32-bit status register that contains floating-point condition codes, quotient bits, and exception status information.

- A 32-bit instruction address register that contains the main processor memory address of the last floating-point instruction that was executed. This address is used in exception handling to locate the instruction that caused the exception.

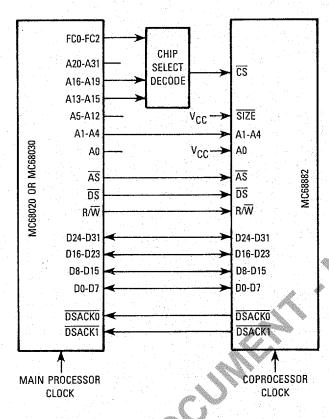

The connection between the MC68020 or MC68030 and the MC68882 is a simple extension of the M68000 bus interface. The MC68882 is connected as a coprocessor to the MC68020 or MC68030, and the selection of the MC68882 is based on a chip select which is decoded from the MC68020 or MC68030 function codes and address bus. Figure 7 illustrates the MPU/coprocessor configuration.

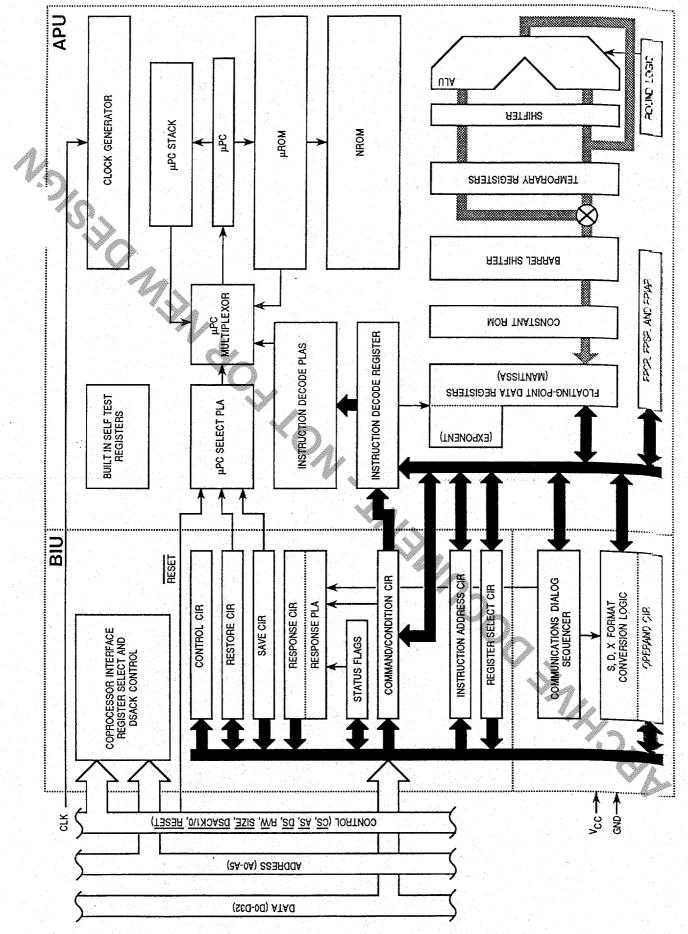

As shown in Figure 8, the MC68882 is internally divided into three processing elements: the bus interface unit

#### Freescale Semiconductor, Inc. 0 63 79 FP0 FP1 FP2 FP3 FLOATING POINT FP4 DATA REGISTERS FP5 FP6 FP7 31 23 15 7 0 Mode Control Exception Enable CONTROL REGISTER 0 FPGR Condition Code Exception Status Accrued Exception STATUS REGISTER **FPSB** Quotient INSTRUCTION ADDRESS FPIAR REGISTER Figure 1. MC68882 Programming Model 12 11 10 8 15 14 13 q OVFL UNFL INEX1 BSUN SNAN OPERR DZ INEX2 **INEXACT DECIMAL INPUT** INEXACT OPERATION **DIVIDE BY ZERO** UNDERFLOW OVERFLOW **OPERAND ERROR** SIGNALLING NOT A NUMBER **BRANCH/SET ON UNORDERED** Figure 2. Exception Status/Enable Byte C.A. 5 0 7 4 3 2 PREC 0 RND 8-01 **ROUNDING MODE:** 00 TO NEAREST **TOWARD ZERO** 01 TOWARD MINUS INFINITY 10 TOWARD PLUS INFINITY 11 **ROUNDING PRECISION:** 00 EXTENDED SINGLE 01 DOUBLE 10 (UNDEFINED, RESERVED) 11 Figure 3. Mode Control Byte

DC.

С.

MOTOROLA 4

MC68882 BR509/Rev. 3

(BIU), the conversion unit (CU), and the arithmetic processing unit (APU). The BIU communicates with the MC68020 or MC68030, the CU performs data conversion for binary real data formats, and the APU executes all MC68882 instructions.

The BIU contains the coprocessor interface registers (CIRs). In addition to these registers, the register select and DSACK timing control logic is contained in the BIU. Finally, the status flags used to monitor the status of communications with the main processor are contained in the BIU.

The CU contains special purpose hardware that performs data format conversions between binary real data formats to and from the internal extended format. The CU relieves the APU of a significant work load and allows the MC68882 to execute data movement and preparation functions concurrently with arithmetic and transcendental calculations.

The eight 80-bit floating-point data registers (FP0-FP7) and the 32-bit control, status, and instruction address registers (FPCR, FPSR and FPIAR) are located in the APU. In addition to these registers, the APU contains a high-speed 67-bit arithmetic unit used for both mantissa and exponent calculations, a barrel shifter that can shift from 1 bit to 67 bits in one machine cycle, and ROM constants (for use by the internal algorithms or user programs).

The control section of the APU contains the clock generator, a two-level microcode sequencer, the microcode ROM, and self-test circuitry. The built-in self-test capabilities of the MC68882 enhance reliability and ease manufacturing requirements; however, these diagnostic functions are not accessible outside of the special test environment supported by VLSI test equipment.

#### **BUS INTERFACE UNIT**

All communications between the MC68020 or MC68030 and the MC68882 occur via standard M68000 Family bus transfers. The MC68882 is designed to operate on 8-, 16-, or 32-bit data buses.

The MC68882 contains a number of coprocessor interface registers (CIRs) that are addressed in the same manner as memory by the main processor. The M68000 Family coprocessor interface is implemented via a protocol of reading and writing to these registers by the main processor. The MC68020 and MC68030 implement this general purpose coprocessor interface protocol in hardware and microcode.

When the MC68020 or MC68030 detects a general type MC68882 instruction, the MC68020 or MC68030 writes the instruction to the memory-mapped command CIR and reads the response CIR. In this response, the BIU encodes requests for any additional action required of the MC68020 or MC68030 on behalf of the MC68882. For example, the response may request that the MC68020 or MC68030 fetch an operand from the evaluated effective address and transfer the operand to the operand CIR. Once the MC68020 or MC68020 or MC68030 fulfills the coprocessor request(s), the MC68020 or MC68030 is free to fetch and execute subsequent instructions.

The only difference between a coprocessor bus transfer and any other bus transfer is that the MC68020 or MC68030 issues a CPU address space function code during the cycle. (The function codes are generated by the M68000 Family processors to identify eight separate address spaces.) Thus, the memory-mapped coprocessor interface registers do not infringe upon instruction or data address spaces. The MC68020 or MC68030 places a coprocessor ID field from the coprocessor instruction onto three of the upper address lines during coprocessor accesses. This ID, along with the CPU address space function code, is decoded to select one of eight coprocessors in the system.

Since the coprocessor interface protocol is based solely on bus transfers, the protocol is easily emulated by software when the MC68882 is used as a peripheral with any processor capable of memory-mapped I/O over an M68000 style bus. When used as a peripheral processor with the 8-bit MC68008, the 16-bit MC68000, or the MC68010, all MC68882 instructions are trapped by the main processor to an exception handler at execution time. Thus, the software emulation of the coprocessor interface protocol can be totally transparent to the user. The MC68882 can provide a performance option for MC68000-based designs by changing the main processors to the MC68020 or MC68030. The software migrates without change to the next generation equipment using the MC68020 or MC68030.

Since the bus is asynchronous, the MC68882 need not run at the same clock speed as the main processor. Total system performance may therefore be customized. For a given CPU performance requirement, the floating-point performance can be selected to meet particular price/ performance specifications, running the MC68882 at slower (or faster) clock speeds than the MPU clock.

#### COPROCESSOR INTERFACE

The M68000 Family coprocessor interface is an integral part of the MC68882 and MC68020 or MC68030 designs. The interface partitions MPU and coprocessor operations so that the MC68020 or MC68030 does not have to completely decode coprocessor instructions, and the MC68882 does not have to duplicate main processor functions (such as effective address evaluation). This partitioning provides an orthogonal extension of the instruction set by permitting MC68882 instructions to utilize all MC68020 or MC68030 addressing modes and to generate execution time exception traps. Thus, from the programmer's view, the MPU and coprocessor appear to be integrated onto a single chip.

While the execution of the great majority of MC68882 instructions may be overlapped with the execution of MC68020 or MC68030 instructions, concurrency is completely transparent to the programmer. The MC68020 and MC68030 single-step and program flow (trace) modes are fully supported by the MC68882 and the M68000 Family coprocessor interface.

While the M68000 Family coprocessor interface permits coprocessors to be bus masters, the MC68882 is never a bus master. The MC68882 requests that the MC68020 or MC68030 fetch all operands and store all results. In this manner, the MC68020 and MC68030 32bit data bus provides high speed transfer of floating-point operands and results while simplifying the design of the MC68882.

Freescale Semiconductor, Inc.

For More Information On This Product

DC.

Figure 8. MC68882 Simplified Block Diagram

Since the coprocessor interface is based solely upon bus cycles (to and from CPU space) and the MC68882 is never a bus master, the MC68882 can be placed on either the logical or physical side of the system memory management unit in an MC68020-based system. Since the memory management unit of the MC68030 is on-chip, the MC68882 is always on the physical side of the memory management unit in an MC68030 system.

The virtual machine architecture of the MC68020 or MC68030 is supported by the coprocessor interface and the MC68882 through the FSAVE and FRESTORE instructions. If the MC68020 or MC68030 detects a page fault and/or a task time out, the MC68020 or MC68030 can force the MC68882 to stop whatever operation is in progress at any time and save the MC68882 internal state in memory. During the execution of a floating-point instruction, the MC68882 can stop at predetermined points as well as at the completion of the instruction.

The size of the saved internal state of the MC68882 is dependent upon the state of the APU at the time the FSAVE is executed. If the MC68882 is in the reset state when the FSAVE instruction is received, only one word of state is transferred to memory, which may be examined by the operating system to determine that the coprocessor programmer's model is empty. If the coprocessor is in the idle state when the save instruction is received, only a few words of internal state are transferred to memory. If executing an instruction in the busy state, it may be necessary to save the entire internal state of the machine. Instructions completing execution in less time than it takes to save the larger state in mid-instruction are allowed to complete execution and then save the idle state. Thus, the size of the saved internal state is kept to a minimum. The ability to utilize several internal state sizes greatly reduces the average context switching time.

The FRESTORE instruction permits reloading of an internal state that was saved earlier and continues any operation that was previously suspended. An FRESTORE of the null state frame re-establishes default register values, a function identical to the MC68882 hardware reset.

#### MC68882 PERFORMANCE ENHANCEMENTS

The high performance of the MC68882 is the result of the MC68882's ability to execute multiple floating-point instructions concurrently. The direct result of concurrency is to utilize the Arithmetic Processing Unit (APU) more efficiently by decreasing its idle time.

When the MC68882 receives an instruction, the BIU, along with the CU, can initiate the instruction, fetch the necessary operands, and convert them to the internal extended format even though the APU is busy completing execution of a previous instruction. Although the MC68881 can only instruct the main processor to wait if the APU is busy, the MC68882 CU can proceed with the next instruction. When the APU is finally ready to perform the calculation, it can do so immediately without incurring delay due to data movement and preparation functions.

Another factor in obtaining increased performance in the MC68882 is the optimized FMOVE instructions for binary real data formats. These FMOVE instructions execute twice as fast as the corresponding FMOVE instructions of the MC68881. The FMOVE instructions are also potentially fully concurrent and, therefore, can be completely executed during the execution of a previous instruction.

The MC68882 also has a more optimized coprocessor interface than the MC68881. If an arithmetic instruction has data formats of Single, Double or Extended, the dialogs are designed to increase the potential overlap with subsequent instructions. This overlap can significantly decrease the effective instruction execution time.

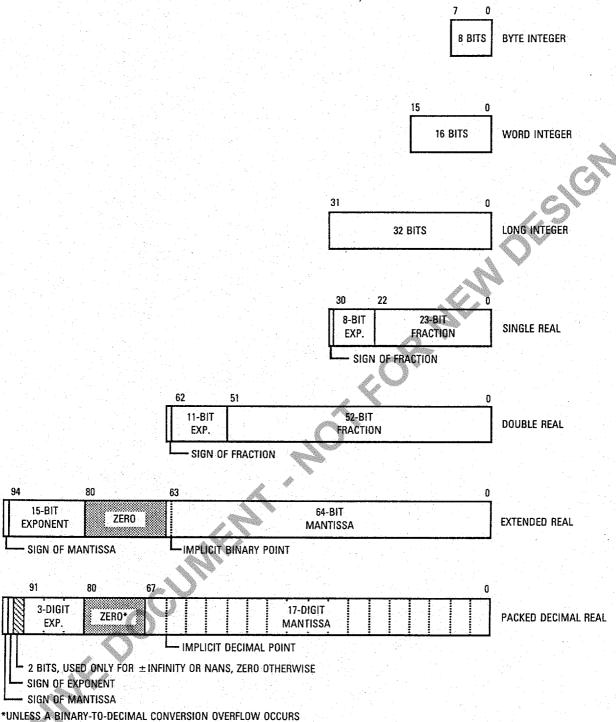

## **OPERAND DATA FORMATS**

The MC68882 supports the following data formats:

Byte Integer (B) Word Integer (W) Long Word Integer (L) Single Precision Real (S) Double Precision Real (D) Extended Precision Real (X)

Packed Decimal String Real (P) The capital letters contained in parentheses denote suffixes added to instructions in the assembly language source specifying the data format to be used.

#### **INTEGER DATA FORMATS**

The three integer data formats (byte, word, and long word) are the standard twos complement data formats supported in the M68000 Family architecture. Whenever an integer is used in a floating-point operation, the integer is automatically converted by the MC68882 to an extended precision floating-point number before being used. For example, to add an integer constant of five to the number contained in floating-point data register 3 (FP3), the following instruction can be used:

#### FADD.W #5,FP3

(The Motorola assembler syntax "#" is used to denote immediate addressing.)

The ability to effectively use integers in floating-point operations saves user memory since an integer representation of a number, if representable, is usually smaller than the equivalent floating-point representation.

#### FLOATING-POINT DATA FORMATS

The floating-point data formats, single precision (32bits) and double precision (64-bits), are defined by the IEEE standard. These data formats are the main floatingpoint formats and should be used for most calculations involving real numbers. Table 1 lists the exponent and mantissa size for single, double, and extended precision. The exponent is biased, and the mantissa is in sign and magnitude form. Since single and double precision require normalized numbers, the most-significant bit of the mantissa is implied as a one and is not included, thus giving one extra bit of precision.

The extended precision data format is also in conformance with the IEEE standard, but the standard does not specify this format to the bit level whereas it does for single and double precision. The memory format on the MC68882 consists of 96 bits (three long words). Only 80 bits are actually used; the other 16 bits are for future

Table 1. Exponent and Mantissa Sizes

| Data<br>Format | Exponent<br>Bits | Mantissa<br>Bits | Bias  |

|----------------|------------------|------------------|-------|

| Single         | 8                | 23(+1)           | 127   |

| Double         | 11               | 52(+1)           | 1023  |

| Extended       | 15               | 64               | 16383 |

expandability and for long-word alignment of floatingpoint data structures. Extended format has a 15-bit exponent, a 64-bit mantissa, and a 1-bit mantissa sign.

Extended precision numbers are intended for use as temporary variables, intermediate values, or in areas where extra precision is needed. For example, a compiler might select extended precision arithmetic for evaluation of the right side of an equation with mixed sized data and then convert the answer to the data type on the left side of the equation. It is anticipated that extended precision data will not be stored in large arrays due to the amount of memory required by each value.

#### PACKED DECIMAL STRING REAL DATA FORMAT

The packed decimal data format allows packed BCD strings to be transferred to and from the MC68882. The strings consist of a 3-digit base 10 exponent and a 17digit base 10 mantissa. Both the exponent and mantissa have a separate sign bit. All digits are packed BCD; an entire string fits in 96 bits (three long words). As is the case with all data formats when packed BCD strings are supplied to the MC68882, the strings are automatically converted to extended precision real values. This conversion allows packed BCD numbers to be used as inputs to any operation. For example:

#### FADD.P #-6.023E + 24,FP5

BCD numbers can be output from the MC68882 in a format readily used for printing by a program generated by a high-level language compiler. For example:

FMOVE.P FP3, BUFFER{#-5}

This instruction converts the floating-point data register 3 (FP3) contents into a packed BCD string with five digits to the right of the decimal point (FORTRAN F format).

#### DATA FORMAT SUMMARY

All data formats described above are supported orthogonally by all arithmetic and transcendental operations and by all appropriate MC68020 or MC68030 addressing modes. For example, all of the following are legal instructions:

| FADD.B | #0,FP0              |

|--------|---------------------|

| FADD.W | D2,FP3              |

| FADD.L | BIGINT, FP7         |

| FADD.S | #3.14159,FP5        |

| FADD.D | (SP) + ,FP6         |

| FADD.X | [(TEMP_PTR,A7)],FP3 |

| FADD.P | #1.23E25,FP0        |

|        |                     |

Most on-chip calculations are performed in the extended precision format, and the eight floating-point data registers always contain extended precision values. All operands used are converted to extended precision by the MC68882 before a specific operation is performed, and all results are in extended precision. The use of extended precision ensures maximum accuracy without sacrificing performance. Refer to Figure 9 for a summary of the memory formats for the seven data formats supported by the MC68882.

The MC68882 instruction set is organized into six major classes:

- Moves between the MC68882 and memory or the MC68020 or MC68030 (in and out),

- 2. Move multiple registers (in and out),

- 3. Monadic operations,

- 4. Dyadic operations,

- 5. Branch, set, or trap conditionally, and

- 6. Miscellaneous.

### MOVES

On all moves from memory (or from an MC68020 or MC68030 data register) to the MC68882, data is converted from the source data format to the internal extended precision format. On all moves from the MC68882 to memory (or to an MC68020 or MC68030 data register), data is converted from the internal extended precision format to the destination data format. Note that data movement instructions perform arithmetic operations, since the result is always rounded to the precision selected in the FPCR mode control byte. The result is rounded using the selected rounding mode and is checked for overflow and underflow.

The syntax for the move is:

|      | FMOVE. <fmt></fmt> | <ea>,FPn</ea>  | Move to MC68882     |

|------|--------------------|----------------|---------------------|

|      | FMOVE. <fmt></fmt> | FPm, <ea></ea> | Move from MC68882   |

|      | FMOVE.X            | FPm,FPn        | Move within MC68882 |

| wher | e:                 |                |                     |

<ea> is an MC68020 or MC68030 effective address operand.

.< fmt> is the data format size.

FPm and FPn are floating-point data registers.

#### MOVE MULTIPLE REGISTERS

The floating-point move multiple instructions on the MC68882 are much like the integer counterparts on the M68000 Family processors. Any set of the floating-point registers FP0 through FP7 can be moved to or from memory with one instruction. These registers are always moved as 96-bit extended data with no conversion (hence no possibility of conversion errors). Some examples of the move multiple instruction are as follows:

| FMOVEM                  | <pre>(ea&gt;,FP0-FP3/FP7</pre> |

|-------------------------|--------------------------------|

| FMOVEM                  | FP2/FP4/FP6, <ea></ea>         |

| م سم من بم سمي بافتسا م | Instructions are used          |

The move multiple instructions are useful during context switches and interrupts to save or restore the state

For More Information On This Product,

DC.

Freescale Semiconductor, I

## Freescale Semiconductor, Inc.

Figure 9. MC68882 Data Format Summary

of a program. These moves are also useful at the start and end of a procedure to save and restore the register set of the calling routine. In order to reduce procedure call overhead, the list of registers to be saved or restored can be contained in a data register thus enabling runtime optimization by allowing a called routine to save as few registers as possible. Note that no rounding or overflow/underflow checking is performed by these operations.

#### MONADIC OPERATIONS

Monadic operations have one operand. This operand may be in a floating-point data register, memory, or in an MC68020 or MC68030 data register. The result is always stored in a floating-point data register. For example, the syntax for square root is:

| FSQRT. <fmt></fmt> | <ea>,FPn</ea> | or, |

|--------------------|---------------|-----|

| FSORT.X            | FPm,FPn       | or, |

| FSQRT.X            | FPn           |     |

Go to: www.freescale.com

# Freescale Semiconductor, Inc. Table 3. Coprocessor Interface ADDRESS STROBE (7)

Begister Selection

| Register Selection |        |       |       |                     |  |  |  |

|--------------------|--------|-------|-------|---------------------|--|--|--|

| A4-A0              | Offset | Width | Туре  | Register            |  |  |  |

| 0000x              | \$00   | 16    | Read  | Response            |  |  |  |

| 0001x              | \$02   | 16    | Write | Control             |  |  |  |

| 0010x              | \$04   | 16    | Read  | Save                |  |  |  |

| 0011x              | \$06   | 16    | R/W   | Restore             |  |  |  |

| 0100x              | \$08   | 16    | ····  | (Reserved)          |  |  |  |

| 0101x              | \$0A   | 16    | Write | Command             |  |  |  |

| 0110x              | \$0C   | 16    |       | (Reserved)          |  |  |  |

| 0111x              | \$0E   | 16    | Write | Condition           |  |  |  |

| 100xx              | \$10   | 32    | R/W   | Operand             |  |  |  |

| 1010x              | \$14   | 16    | Read  | Register Select     |  |  |  |

| 1011x              | \$16   | 16    |       | (Reserved)          |  |  |  |

| 110xx              | \$18   | 32    | Read  | Instruction Address |  |  |  |

| 111xx              | \$1C   | 32    | R/W   | Operand Address     |  |  |  |

|                    |        | 1 A 4 | 100 C |                     |  |  |  |

When the MC68882 is configured to operate over an 8bit data bus, the A0 pin is used as an address signal for byte accesses of the coprocessor interface registers. When the MC68882 is configured to operate over a 16- or 32bit system data bus, both the A0 and the SIZE pins are strapped high and/or low as listed in Table 4.

#### Table 4. System Data Bus Size Configuration

| A0   | SIZE | Data Bus |

|------|------|----------|

|      | Low  | 8-Bit    |

| Low  | High | 16-Bit   |

| High | High | 32-Bit   |

#### DATA BUS (D0 through D31)

This 32-bit, bidirectional, three-state bus serves as the general purpose data path between the MC68020/MC68030 and the MC68882. Regardless of whether the MC68882 is operated as a coprocessor or a peripheral processor, all inter-processor transfers of instruction information, operand data, status information, and requests for service occur as standard M68000 bus cycles.

The MC68882 will operate over an 8-, 16-, or 32-bit system data bus. Depending upon the system data bus configuration, both the A0 and SIZE pins are configured specifically for the applicable bus configuration. (Refer to ADDRESS BUS (A0 through A4) and SIZE (SIZE) for further details).

#### SIZE (SIZE)

This active-low input signal is used in conjunction with the A0 pin to configure the MC68882 for operation over an 8-, 16-, or 32-bit system data bus. When the MC68882 is configured to operate over a 16- or 32-bit system data bus, both the SIZE and A0 pins are strapped high and/or low as listed in Table 4.

## ADDRESS STROBE (AS)

This active-low input signal indicates that there is a valid address on the address bus, and both the chip select  $\overline{(CS)}$  and read/write  $(R/\overline{W})$  signal lines are valid.

#### CHIP SELECT (CS)

This active-low input signal enables the main processor access to the MC68882 coprocessor interface registers. When operating the MC68882 as a peripheral processor, the chip select decode is system dependent (i.e., like the chip select on any peripheral).

#### READ/WRITE (R/W)

This input signal indicates the direction of a bus transaction (read/write) by the main processor. A logic high (1) indicates a read from the MC68882, and a logic low (0) indicates a write to the MC68882. The R/W signal must be valid when  $\overline{\text{AS}}$  is asserted.

#### DATA STROBE (DS)

This active-low input signal indicates that there is valid data on the data bus during a write bus cycle.

### DATA TRANSFER AND SIZE ACKNOWLEDGE (DSACK0, DSACK1)

These active-low, three-state output signals indicate the completion of a bus cycle to the main processor. The MC68882 asserts both the DSACK0 and DSACK1 signals upon assertion of CS.

If the bus cycle is a main processor read, the MC68882 asserts DSACK0 and DSACK1 signals to indicate that the informatin on the data bus is valid. (Both DSACK signals may be asserted in advance of the valid data being placed on the bus.) If the bus cycle is a main processor write to the MC68882, DSACK0 and DSACK1 are used to acknowledge acceptance of the data by the MC68882.

The MC68882 also uses DSACK0 and DSACK1 signals to dynamically indicate to the MC68020/MC68030 the "port" size (system data bus width) on a cycle-by-cycle basis. Depending upon which of the two DSACK pins are asserted in a given bus cycle, the MC68020/MC68030 assumes data has been transferred to/from an 8-, 16-, or 32-bit wide data port. Table 5 lists the DSACK assertions that are used by the MC68882 for the various bus cycles over the various system data bus configurations.

Table 5 indicates that all accesses over a 32-bit bus where A4 equals zero are to 16-bit registers. The MC68882 implements all 16-bit coprocessor interface registers on data lines D16-D31 (to eliminate the need for on-chip multiplexers); however, the MC68020/MC68030 expects 16-bit registers that are located in a 32-bit port at odd word addresses (A1 = 1) to be implemented on data lines D0-D15. For accesses to these registers when configured for 32-bit bus operation, the MC68882 generates DSACK signals as listed in Table 5 to inform the MC68020/ MC68030 of valid data on D16-D31 instead of D0-D15.

An external holding resistor is required to maintain both DSACK0 and DSACK1 high between bus cycles. In order to reduce the signal rise time, the DSACK0 and DSACK1 lines are actively pulled up (negated) by the

MC68882 BR509/Rev. 3

| . [ | Data bus | A4 | DSACK1 | <b>DSACKO</b> | Comments                                         |

|-----|----------|----|--------|---------------|--------------------------------------------------|

|     | 32-Bit   | 1. | Low    | Low           | Valid Data on D31-D0                             |

|     | 32-Bit   | 0  | Low    | High          | Valid Data on D31-D16                            |

| ĺ   | 16-Bit   | x  | Low    | High          | Valid Data on D31-D16 or D15-D0                  |

| :   | 8-Bit    | x  | High   | Low           | Valid Data on D31-D24, D23-D16, D15-D8, or D7-D0 |

|     | All      | x  | High   | High          | Insert Wait States in Current Bus Cycle          |

#### Freescale Semiconductor, Inc. Table 5. DSACK Assertions

MC68882 following the rising edge of  $\overline{AS}$  or  $\overline{DS}$ , and both DSACK lines are then three-stated (placed in the high-impedance state) to avoid interference with the next bus cycle.

#### RESET (RESET)

This active-low input signal causes the MC68882 to initialize the floating-point data registers to non-signaling not-a-numbers (NANs) and clears the floating-point control, status, and instruction address registers.

When performing a power-up reset, external circuitry should keep the RESET line asserted for a minimum of four clock cycles after V<sub>CC</sub> is within tolerance. This assures correct initialization of the MC68882 when power is applied. For compatibility with all M68000 Family devices, 100 milliseconds should be used as the minimum.

When performing a reset of the MC68882 after V<sub>CC</sub> has been within tolerance for more than the initial power-up time, the  $\overrightarrow{\text{RESET}}$  line must have an asserted pulse width which is greater than two clock cycles. For compatibility with all M68000 Family devices, 10 clock cycles should be used as the minimum.

#### CLOCK (CLK)

The MC68882 clock input is a TTL-compatible signal that is internally buffered for development of the internal clock signals. The clock input should be a constant frequency square wave with no stretching or shaping techniques required. The clock should not be gated off at any time and must conform to minimum and maximum period and pulse width times.

#### SENSE DEVICE (SENSE)

This pin may be used optionally as an additional GND pin or as as indicator to external hardware that the MC68882 is present in the system. This signal is internally connected to the GND of the die, but it is not necessary to connect it to the external ground for correct device operation. If a pullup resistor (which should be larger than 10 kohm) is connected to this pin location, external hardware may sense the presence of the MC68882 in a system.

#### POWER (VCC and GND)

These pins provide the supply voltage and system reference level for the internal circuitry of the MC68882. Care should be taken to reduce the noise level on these pins with apropriate capacitive decoupling.

#### NO CONNECT (NC)

One pin of the MC68882 package is designated as a no connect (NC). This pin position is reserved for future use by Motorola, and should not be used for signal routing or connected to  $V_{CC}$  or GND.

#### SIGNAL SUMMARY

Table 6 provides a summary of all the MC68882 signals described in the above paragraphs.

| Signal Name                        | Mnemonic       | Input/Output | Active State | Three State |

|------------------------------------|----------------|--------------|--------------|-------------|

| Address Bus                        | A0-A4          | Input        | High         |             |

| Data Bus                           | D0-D13         | Input/Output | High         | Yes         |

| Size                               | SIZE           | Input        | Low          |             |

| Address Strobe                     | ĀS             | Input        | Low          |             |

| Chip Select                        |                | Input        | Low          |             |

| Read/Write                         | R/W            | Input        | High/Low     |             |

| Data Strobe                        | DS             | Input        | Low          |             |

| Data Transfer and Size Acknowledge | DSACK0, DSACK1 | Output       | Low          | Yes         |

| Reset                              | RESET          | Input        | Low          |             |

| Clock                              | CLK            | Input        |              | ·           |

| Sense Device                       | SENSE          | Input/Output | Low          | No          |

| Power Input                        | Vcc            | Input        |              |             |

| Ground                             | GND            | Input        |              |             |

#### Table 6. Signal Summary

Freescale Semiconductor, I

For More Information On This Product Go to: www.freescale.com

## MC68882/MC68010 OR MC68030 INTERFACING

The following paragraphs describe how to connect the MC68882 to an MC68020 or MC68030 for coprocessor operation via an 8-, 16-, or 32-bit data bus.

INTERFACING METHODS

#### 32-Bit Data Bus Coprocessor Connection

Figure 11 illustrates the coprocessor interface connection of an MC68882 to an MC68020/MC68030 via a 32-bit data bus. The MC68882 is configured to operate over a 32-bit data bus when both the A0 and SIZE pins are connected to  $V_{CC}$ .

Figure 11. 32-Bit Data Bus Coprocessor Connection

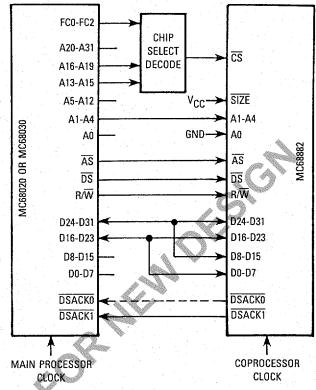

#### **16-Bit Data Bus Coprocessor Connection**

Figure 12 illustrates the coprocessor interface connection of an MC68882 to an MC68020/MC68030 via a 16-bit data bus. The MC68882 is configured to operate over a 16-bit 5 data bus when the SIZE pin is connected to V<sub>CC</sub>, and the A0 pin is connected to GND. The sixteen leastsignificant data pins (D0-D15) must be connected to the sixteen most-significant data pins (D16-D31) when the MC68882 is configured to operate over a 16-bit data bus (i.e., connect D0 to D16, D1 to D17, ... and D15 to D31). The DSACK pins of the two devices are directly connected, although it is not necessary to connect the DSACKO pin since the MC68882 never asserts it in this configuration.

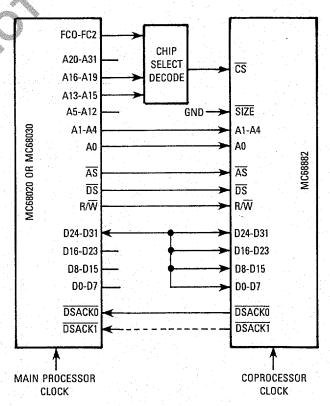

#### 8-Bit Data Bus Coprocessor Connection

Figure 13 illustrates the connect of an MC68882 to an MC68020/MC68030 as a coprocessor over an 8-bit data

Figure 12. 16-Bit Data Bus Coprocessor Connection

Figure 13. 8-Bit Data Bus Coprocessor Connection

bus. The MC68882 is configured to operate over an 8-bit data bus when the SIZE pin is connected to GND. The twenty-four least-significant data pins (D0-D23) must be connected to the eight most-significant data pins (D24-

D31) when the MC68882 is configured to operate over an 8-bit data bus (i.e., connect D0 to D8, D16 and D24; D1 to D9, D17, and D25; ... and D7 to D15, D23 and D31). The DSACK pins of the two devices are directly connected, although it is not necessary to connect the DSACK1 pin since the MC68882 never asserts it in this configuration.

#### MC68882-MC68000/MC68008/MC68010 INTERFACING

The following paragraphs describe how to connect the MC68882 to an MC68000, MC68008, or MC68010 processor for opertion as a peripheral via an 8- or 16-bit data bus.

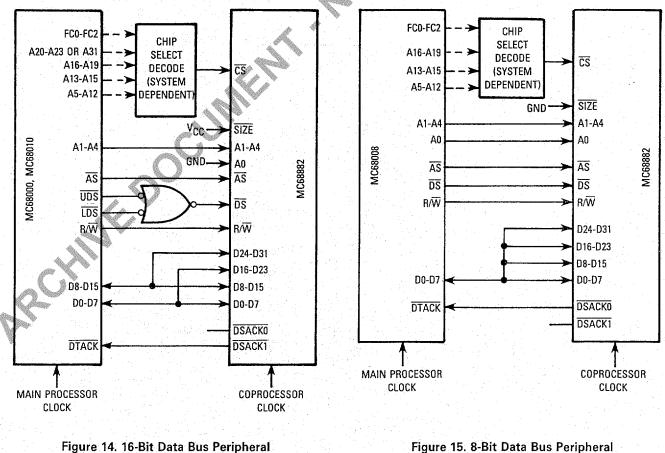

#### **16-Bit Data Bus Peripheral Processor Connection**

Figure 14 illustrates the connection of an MC68882 to an MC68000 or MC68010 as a peripheral processor over a 16-bit data bus. The MC68882 is configured to operate over a 16-bit data bus when the SIZE pin is connected to V<sub>CC</sub>, and the A0 pin is connected to GND. The sixteen least-significant data pins (D0-D15) must be connected to the sixteen most-significant data pins (D16-D31) when the MC68882 is configured to operate over a 16-bit data bus (i.e., connect D0 to D16, D1 to D17, ... and D15 to D31). The DSACK1 pin of the MC68882 is connected to the main processor, and the DSACK0 pin is not used. When connected as a peripheral processor, the MC68882 chip select  $(\overline{CS})$  decode is system dependent. If the MC68000 is used as the main processor, the MC68882  $\overline{CS}$ must be decoded in the supervisor or user data spaces. However, if the MC68010 is used for the main processor, the MOVES instruction may be used to emulate any CPU space access that the MC68020/MC68030 generates for coprocessor communications. Thus, the  $\overline{CS}$  decode logic for such systems may be the same as in an MC68020/ MC68030 system, such that the MC68882 will not use any part of the data address spaces.

#### 8-Bit Data Bus Peripheral Processor Connection

Figure 15 illustrates the connection of an MC68882 to an MC68008 as a peripheral processor over an 8-bit data bus. The MC68882 is configured to operate over an 8-bit data bus when the SIZE pin is connected to GND. The eight least-significant data pins (D0-D7) must be connected to the twenty-four most-significant pins (D8-D31) when the MC68882 is configured to operate over an 8bit data bus (i.e., connect D0 to D8, D16, and D24; D1 to D9, D17, and D25; . . and D7 to D15, D23, and D31). The DSACK0 pin of the MC68882 is connected to the DTACK pin of the MC68008, and the DSACK1 pin is not used.

When connected as a peripheral processor, the MC68882 chip select  $(\overline{CS})$  decode is system dependent, and the  $\overline{CS}$  must be decoded in the supervisor or user data spaces.

Processor Connection

Processor Connection

### ELECTRICAL SPECIFICATIONS

#### MAXIMUM RATINGS

| Rating                | Symbol           | Value        | Unit |

|-----------------------|------------------|--------------|------|

| Supply Voltage        | Vcc              | -0.3 to +7.0 | V    |

| Input Voltage         | Vin              | -0.3 to +7.0 | V.   |

| Operating Temperature | TA               | 0 to 70      | ٦°   |

| Storage Temperature   | T <sub>stg</sub> | -55 to +150  | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or V<sub>CC</sub>).

#### **THERMAL CHARACTERISTICS**

| Characteristic                                                          | Symbol     | Value    | Rating |

|-------------------------------------------------------------------------|------------|----------|--------|

| Thermal Resistance — Ceramic<br>Junction to Ambient<br>Junction to Case | θJC<br>θJC | 33<br>15 | °C/W   |

#### POWER CONSIDERATIONS

The average chip-junction temperature, TJ, in °C can be obtained from:  $T_{J} = T_{A} + (P_{D} \cdot \theta_{JA})$

where:

(1)

TA

= Ambient Temperature, °C = Package Thermal Resistance, θJΑ

Junction-to-Ambient, °C/W

PD = PINT + PI/O

PINT = ICC × VCC, Watts — Chip Internal Power

PI/O = Power Dissipation on Input and Output

Pins — User Determined

For most applications PI/O<PINT and can be neglected. The following is an approximate relationship between PD and TJ (if PI/O is

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

(2)

Solving equations (1) and (2) for K gives  $K = P_{D} \cdot (T_{A} + 273^{\circ}C) + \theta_{JA} \cdot P_{D}^{2}$ (3)

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring PD (at equilibrium) for a known TA. Using this value of K, the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

The total thermal resistance of a package ( $\theta_{JA}$ ) can be separated into two components, BJC and BCA, representing the barrier to heat flow from the semiconductor junction to the package (case) surface ( $\theta_{JC}$ ) and from the case to the outside ambient ( $\theta_{CA}$ ). These terms are related by the equation:

| $\theta_{JA} = \theta_{JC} + \theta_{CA} \tag{4}$                                           |

|---------------------------------------------------------------------------------------------|

| θJC is device related and cannot be influenced by the                                       |

| user. However, $\theta_{CA}$ is user dependent and can be min-                              |

| imized by such thermal management techniques as heat                                        |

| sinks, ambient air cooling, and thermal convention. Thus,                                   |

| good thermal management on the part of the user can                                         |

| significantly reduce $\theta_{CA}$ so that $\theta_{JA}$ approximately equals               |

| $\theta_{JC}$ . Substitution of $\theta_{JC}$ for $\theta_{JA}$ in equation (1) will result |

| in a lower semiconductor junction temperature.                                              |

|                                                                                             |

Values for thermal resistance presented in this document, unless estimated, were derived using the procedure described in Motorola Reliability Report 7843, "Thermal Resistance Measurement Method for MC68XX Microcomponent Devices," and are provided for design purposes only. Thermal measurements are complex and dependent on procedure and setup. User derived values for thermal resistance may differ.

| DC ELECTRICAL CHARACTERISTICS ( $V_{CC}$ = 5.0 Vdc ± 5%; GND = 0 Vdc; $T_A$ = 0°C to | 70°C)           |                                       |      |           |

|--------------------------------------------------------------------------------------|-----------------|---------------------------------------|------|-----------|

| Characteristic                                                                       | Symbol          | Min                                   | Max  | Unit      |

| Input High Voltage                                                                   | VIH             | 2.0                                   | Vcc  | • • V • • |

| Input Low Voltage                                                                    | VIL             | GND -0.5                              | 0.8  | V         |

| Input Leakage Current @ 5.25 V CLK, RESET, R/W, A0-A4, CS, DS, AS, SIZE              | l <sub>in</sub> |                                       | 10   | μA        |

| Hi-Z (Off State) Input Current @ 2.4 V/0.4 V DSACK0, DSACK1, D0-D31                  | ITSI            |                                       | 20   | μA        |

| Output High Voltage ( $I_{OH}$ = -400 $\mu$ A) DSACK0, DSACK1, D0-D31                | VOH             | 2.4                                   |      | V         |

| Output Low Voltage (IOL = 5.3 mA) DSACK0, DSACK1, D0-D31                             | VOL             | - 1                                   | 0.5  | V         |

| Output Low Current (V <sub>OL</sub> =GND) SENSE                                      | IOL             | —                                     | 500  | μA        |

| Power Dissipation                                                                    | PD              | · · · · · · · · · · · · · · · · · · · | 0.75 | W         |

| Capacitance* (V <sub>in</sub> =0, T <sub>A</sub> =25°C, f=1 MHz)                     | C <sub>in</sub> |                                       | 20   | pF        |

| Output Load Capacitance                                                              | CL              | —                                     | 130  | pF        |

\*Capacitance is periodically sampled rather than 100% tested.

For More Information On This Product,

MOTOROLA 16

MC68882 BR509/Rev. 3

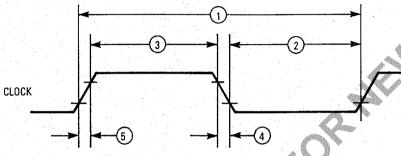

### AC ELECTRICAL CHARACTERISTICS --- CLOCK INPUT

(V<sub>CC</sub> = 5.0 Vdc  $\pm$  5%; GND = 0 Vdc; T<sub>A</sub> = 0 to 70°C; refer to Figure 16)

|     | Characteristic                                              | 16.67 MHz |       | 20 MHz |          | 25 MHz   |     | 33.33 MHz |       |      |

|-----|-------------------------------------------------------------|-----------|-------|--------|----------|----------|-----|-----------|-------|------|

| Num |                                                             | Min       | Max   | Min    | Max      | Min      | Max | Min       | Max   | Unit |

|     | Frequency of Operation                                      | 8         | 16.67 | 12.5   | 20       | 12.5     | 25  | 16.7      | 33.33 | MHz  |

| 1   | Cycle Time                                                  | 60        | 125   | 50     | 80       | 40       | 80  | 30        | 60    | ns   |

| 2,3 | Clock Pulse Width (Measured from 1.5 V to 1.5 V for 33 MHz) | 24        | 95    | 20     | 54       | 15       | 59  | • •14     | 66    | ns   |

| 4,5 | Rise and Fall Times                                         |           | 5     |        | 5        | <u> </u> | 4   | —         | 3     | ns   |

|     |                                                             |           |       | 2      | <b>•</b> | Ê        |     | 54        |       |      |

|     | сьоск                                                       | 7         |       |        |          | $X \lor$ | ¢   |           |       |      |

#### NOTE:

1. Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside, and pass through, the range such that the rise or fall will be linear between 0.8 volts and 2.0 volts.

#### Figure 16. Clock Input Timing Diagram

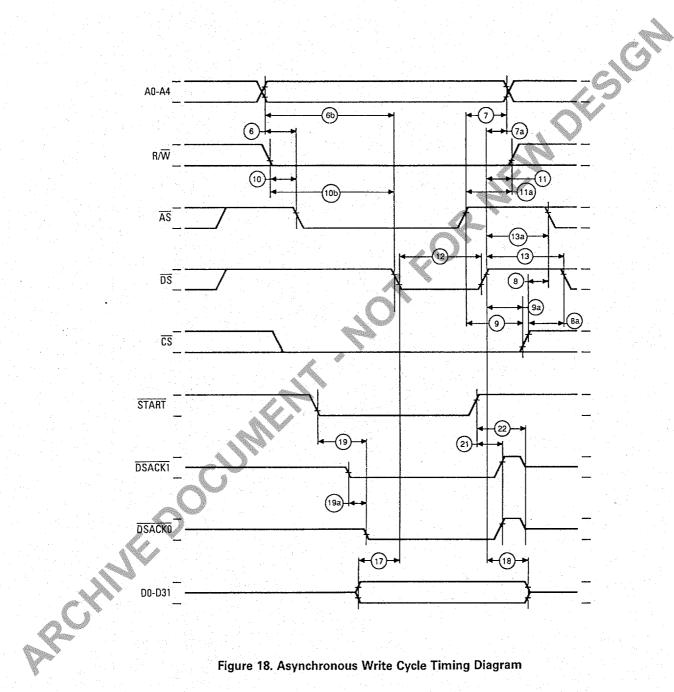

### AC ELECTRICAL SPECIFICATIONS - READ AND WRITE CYCLES

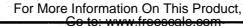

$(V_{CC}=5.0 \text{ Vdc} \pm 5\%; \text{ GND} = 0 \text{ Vdc}; T_A = 0 \text{ to } 70^{\circ}\text{C}$ , refer to Figures 17, 18, and 19)

|                 | Characteristic                                                    | 16.67 | MHz                      | 20 MHz |            | 25 MHz |     | 33.33 MHz |               |      |

|-----------------|-------------------------------------------------------------------|-------|--------------------------|--------|------------|--------|-----|-----------|---------------|------|

| Num             |                                                                   | Min   | Max                      | Min    | Max        | Min    | Max | Min       | Max           | Unit |

| 6 <sup>5</sup>  | Address Valid to AS Asserted                                      | 15    |                          | 10     | —          | 5      | —   | 5         | —             | ns   |

| 6A <sup>5</sup> | Address Valid to DS Asserted (Read)                               | 15    |                          | 10     |            | 5      | -   | 5         | ·             | ns   |

| 6B <sup>5</sup> | Address Valid to DS Asserted (Write)                              | 50    |                          | 50     | —          | 35     | _   | 26        | <u> </u>      | ns   |

| 7 <sup>6</sup>  | AS Negated to Address Invalid                                     | 10    |                          | 10     | —          | 5      |     | 5         |               | ns   |

| 7A <sup>6</sup> | DS Negated to Address Invalid                                     | 10    | -                        | 10     | ······     | 5      |     | 5         |               | ns   |

| 89              | CS Negated to AS Asserted                                         | 0     | <u> </u>                 | 0      | <u> </u>   | 0      | —   | -0        | -             | ns   |

| 8A <sup>9</sup> | $\overline{CS}$ Negated to $\overline{DS}$ Asserted (Read)        | 0     | -                        | 0      | -          | 0      |     | 0         | · _           | ns   |

| 8B              | CS Asserted to DS Asserted (Write)                                | 30    |                          | 25     |            | 20     |     | 15        | ·             | ns   |

| 9               | AS Negated to CS Negated                                          | 10    | <sup>••</sup> • <u> </u> | 10     |            | 5      | —   | 5         |               | ns   |

| 9A              | DS Negated to CS Negated                                          | 10    |                          | 10     | ·          | 5      | —   | 5         |               | ns   |

| 10              | $R/\overline{W}$ High to $\overline{AS}$ Asserted (Read)          | 15    |                          | 10     | _          | 5      |     | 5         | —             | ns   |

| 10A             | $R/\overline{W}$ High to $\overline{DS}$ Asserted (Read)          | 15    |                          | 10     | <u> </u>   | 5      | -   | 5         | , <sup></sup> | ns   |

| 10B             | R/W Low to DS Asserted (Write)                                    | 35    | <u> </u>                 | 30     | 2 <u>-</u> | 25     |     | 25        |               | ns   |

| 11              | AS Negated to R/W Low (Read) or AS Negated to R/W High (Write)    | 10    | _                        | 10     | _          | 5      |     | 5         |               | ns   |

| 11A             | DS Negated to R/W Low (Read) or DS Negated to<br>R/W High (Write) | 10    |                          | 10     |            | 5      | —   | 5         | -<br>-<br>-   | ns   |

- Continued -

For More Information On This Product

MC68882 BR509/Rev. 3 - 1. Cont

nc.

Freescale Semiconductor, I

DC.

MC68882 BR509/Rev. 3 Go to: www.freescale.com

MOTOROLA 21

eion de l

1

$(F_{ij})$

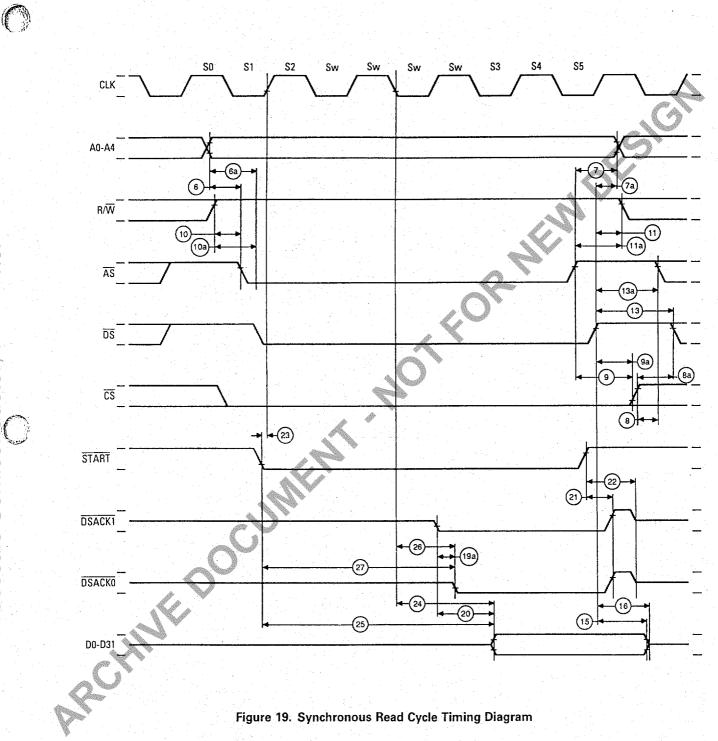

#### NOTES:

- 1. This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2. This output timing is applicable to all parameters specified relative to the falling edge of the clock.

- 3. This input timing is applicable to all parameters specified relative to the rising edge of the clock.

- 4. This input timing is applicable to all parameters specified relative to the falling edge of the clock.

- 5. This timing is applicable to all parameters specified relative to the assertion/negation of another signal.

### LEGEND:

- A. Maximum output delay specification.B. Minimum output hold time.

- C. Minimum input setup time specification.

- D. Minimum input hold time specification.

- E. Signal valid to signal valid specification (maximum or minimum).

- F. Signal valid to signal invalid specification (maximum or minimum).

#### Figure 20. Drive Levels and Test Points for AC Specifications

For More Information On This Product

DC.

MOTOROLA 22

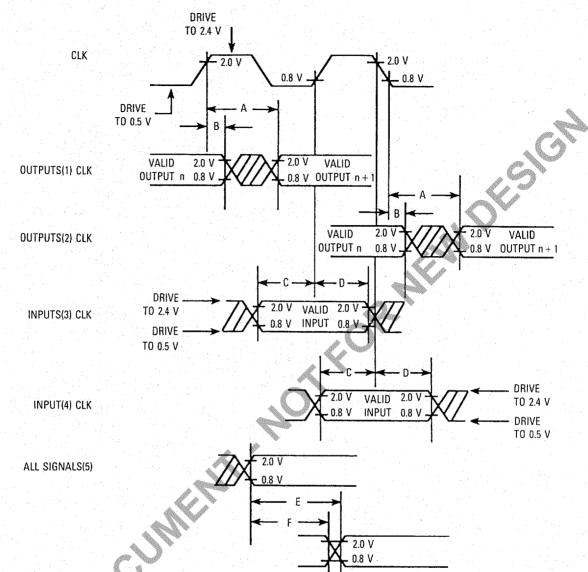

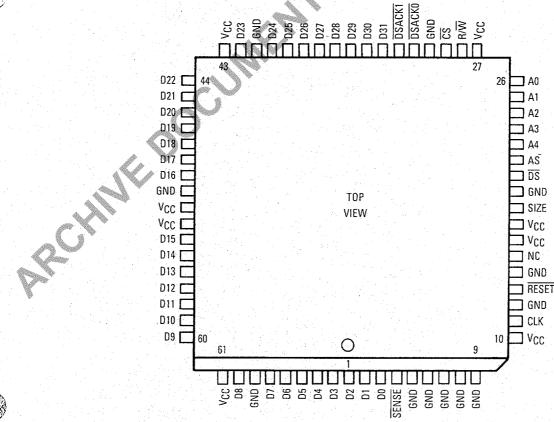

## Freescale Semiconductor, Inc. PIN ASSIGNMENTS AND MECHANICAL DATA

**PIN ASSIGNMENTS**

**PIN GRID ARRAY**

DC.

MC68882 BR509/Rev. 3 Go to: www.freescale.com

-

## Freescale Semiconductor, Inc.

승규는 것이 가지 않는 것이 없다.

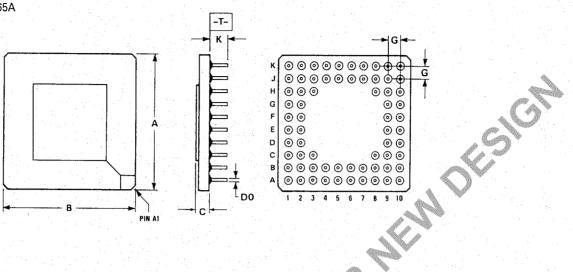

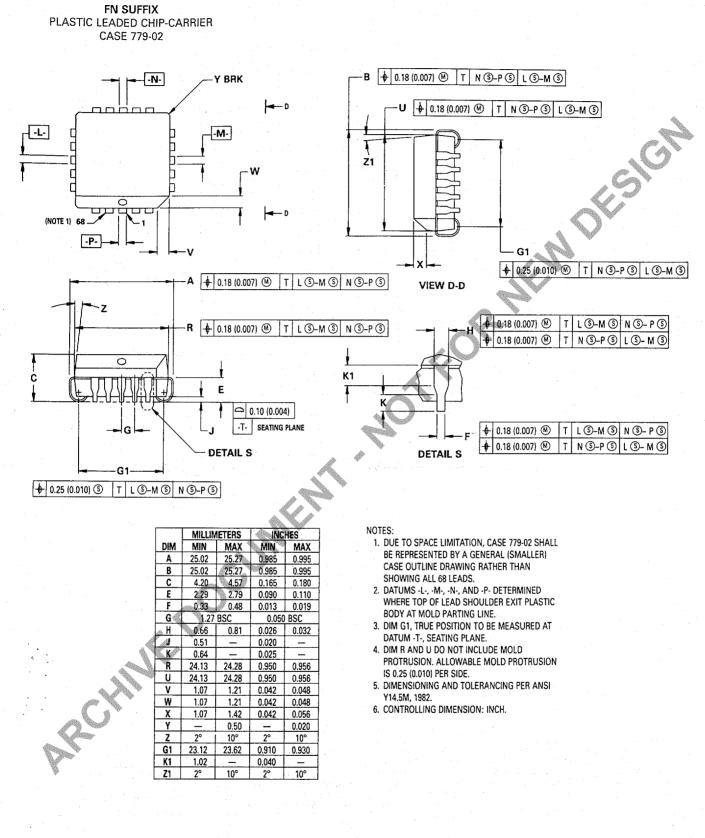

#### **MECHANICAL DATA**

#### **RC SUFFIX PIN GRID ARRAY** CASE 765A

| A second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                   |          |       |       |            |                   | 1.1                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|----------|-------|-------|------------|-------------------|--------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | MILLIN            | AETERS   | INC   | HES   | ]          |                   | NOTES:                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DIM      | MIN               | MAX      | MIN   | MAX   | 1          |                   | 1. DIN<br>DAT            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A        | 26.67             | 27.17    | 1.050 | 1.070 |            |                   | 2. POS                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | В        | 26.67             | 27.17    | 1.050 | 1.070 |            |                   | 3. DIN                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C C      | 1.91              | 2.66     | 0.075 | 0.105 |            | Ran di<br>Galeria | 3. Diiv<br>Y14<br>4. COI |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D        | 0.43              | 0.55     | 0.017 | 0.022 |            |                   |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | G G      |                   | BSC      | 0.100 |       |            |                   | - Alexandre              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ĸ        | 4.32              | 4.82     | 0.170 | 0.190 |            |                   |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | l        |                   | 1.02     | 0.170 |       | ]          | A                 | Ø                        |

| and an annual state of the stat |          |                   |          |       |       | 1. A       | A.                |                          |