Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 100MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 80K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 17x10b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-TFBGA                                                                |

| Supplier Device Package    | 100-TFBGA (9x9)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4n16ca-cu |

Table 4-4. SAM4N8/16 100-ball VFBGA Pinout

| A1  | ADVREFP              |  |  |  |

|-----|----------------------|--|--|--|

| A2  | VDDPLL               |  |  |  |

| А3  | PB9/PGMCK/XIN        |  |  |  |

| A4  | PB8/XOUT             |  |  |  |

| A5  | JTAGSEL              |  |  |  |

| A6  | PB11                 |  |  |  |

| A7  | PB10                 |  |  |  |

| A8  | PC20                 |  |  |  |

| A9  | PC19                 |  |  |  |

| A10 | TDO/TRACESWO/<br>PB5 |  |  |  |

| B1  | GND                  |  |  |  |

| B2  | PC25                 |  |  |  |

| В3  | PB14                 |  |  |  |

| B4  | PB13/DAC0            |  |  |  |

| B5  | PC23                 |  |  |  |

| В6  | PC21                 |  |  |  |

| В7  | TCK/SWCLK/PB7        |  |  |  |

| В8  | PA31                 |  |  |  |

| В9  | PC18                 |  |  |  |

| B10 | PC17                 |  |  |  |

| C1  | PB0/AD4              |  |  |  |

| C2  | PC29/AD13            |  |  |  |

| C3  | PC24                 |  |  |  |

| C4  | ERASE/PB12           |  |  |  |

| C5  | VDDCORE              |  |  |  |

| all VFBGA Pinout |               |  |  |  |

|------------------|---------------|--|--|--|

| C6               | PC9           |  |  |  |

| C7               | TMS/SWDIO/PB6 |  |  |  |

| C8               | PA1/PGMEN1    |  |  |  |

| C9               | PA0/PGMEN0    |  |  |  |

| C10              | PC16          |  |  |  |

| D1               | PB1/AD5       |  |  |  |

| D2               | PC30          |  |  |  |

| D3               | PC31          |  |  |  |

| D4               | PC22          |  |  |  |

| D5               | PC5           |  |  |  |

| D6               | PA29          |  |  |  |

| D7               | PA30/AD14     |  |  |  |

| D8               | GND           |  |  |  |

| D9               | PC14          |  |  |  |

| D10              | PC11          |  |  |  |

| E1               | VDDIN         |  |  |  |

| E2               | PB3/AD7       |  |  |  |

| E3               | PB2/AD6       |  |  |  |

| E4               | GND           |  |  |  |

| E5               | GND           |  |  |  |

| E6               | GND           |  |  |  |

| E7               | VDDIO         |  |  |  |

| E8               | PC10          |  |  |  |

| E9               | PA2/PGMEN2    |  |  |  |

| E10              | PA3           |  |  |  |

| F1  | VDDOUT         |  |  |  |

|-----|----------------|--|--|--|

| F2  | PA18/PGMD6/AD1 |  |  |  |

| F3  | PA17/PGMD5/AD0 |  |  |  |

| F4  | GND            |  |  |  |

| F5  | GND            |  |  |  |

| F6  | PC26           |  |  |  |

| F7  | PA4/PGMNCMD    |  |  |  |

| F8  | PA28           |  |  |  |

| F9  | TST            |  |  |  |

| F10 | PC8            |  |  |  |

| G1  | PC15/AD11      |  |  |  |

| G2  | PA19/PGMD7/AD2 |  |  |  |

| G3  | PA21/PGMD9/AD8 |  |  |  |

| G4  | PA15/PGMD3     |  |  |  |

| G5  | PC3            |  |  |  |

| G6  | PA10/PGMM2     |  |  |  |

| G7  | PC1            |  |  |  |

| G8  | PC28           |  |  |  |

| G9  | NRST           |  |  |  |

| G10 | PA27           |  |  |  |

| H1  | PC13/AD10      |  |  |  |

| H2  | PA22/AD9       |  |  |  |

| Н3  | PC27           |  |  |  |

| H4  | PA14/PGMD2     |  |  |  |

| H5  | PC4            |  |  |  |

|     |                |  |  |  |

| H6  | PA12/PGMD0              |  |  |  |

|-----|-------------------------|--|--|--|

| H7  | PA9/PGMM1               |  |  |  |

| Н8  | VDDCORE                 |  |  |  |

| Н9  | PA6/PGMNOE              |  |  |  |

| H10 | PA5/PGMRDY              |  |  |  |

| J1  | PA20/AD3                |  |  |  |

| J2  | PC12/AD12               |  |  |  |

| J3  | PA16/PGMD4              |  |  |  |

| J4  | PC6                     |  |  |  |

| J5  | PA24                    |  |  |  |

| J6  | PA25                    |  |  |  |

| J7  | PA11/PGMM3              |  |  |  |

| J8  | VDDCORE                 |  |  |  |

| J9  | VDDCORE                 |  |  |  |

| J10 | TDI/PB4                 |  |  |  |

| K1  | PA23                    |  |  |  |

| K2  | PC0                     |  |  |  |

| K3  | PC7                     |  |  |  |

| K4  | PA13/PGMD1              |  |  |  |

| K5  | PA26                    |  |  |  |

| K6  | PC2                     |  |  |  |

| K7  | VDDIO                   |  |  |  |

| K8  | VDDIO                   |  |  |  |

| K9  | PA8/XOUT32/<br>PGMM0    |  |  |  |

| K10 | PA7/XIN32/<br>PGMNVALID |  |  |  |

# 4.10 48-lead LQFP and QFN Pinout

Table 4-6. 48-pin SAM4N8 Pinout

|    | <u> </u>       |

|----|----------------|

| 1  | ADVREFP        |

| 2  | GND            |

| 3  | PB0/AD4        |

| 4  | PB1/AD5        |

| 5  | PB2/AD6        |

| 6  | PB3/AD7        |

| 7  | VDDIN          |

| 8  | VDDOUT         |

| 9  | PA17/PGMD5/AD0 |

| 10 | PA18/PGMD6/AD1 |

| 11 | PA19/PGMD7/AD2 |

| 12 | PA20/AD3       |

| 13 | VDDIO               |

|----|---------------------|

| 14 | PA16/PGMD4          |

| 15 | PA15/PGMD3          |

| 16 | PA14/PGMD2          |

| 17 | PA13/PGMD1          |

| 18 | VDDCORE             |

| 19 | PA12/PGMD0          |

| 20 | PA11/PGMM3          |

| 21 | PA10/PGMM2          |

| 22 | PA9/PGMM1           |

| 23 | PA8/XOUT32/PGMM0    |

| 24 | PA7/XIN32/PGMNVALID |

| 25 | TDI/PB4     |

|----|-------------|

| 26 | PA6/PGMNOE  |

| 27 | PA5/PGMRDY  |

| 28 | PA4/PGMNCMD |

| 29 | NRST        |

| 30 | TST         |

| 31 | PA3         |

| 32 | PA2/PGMEN2  |

| 33 | VDDIO       |

| 34 | GND         |

| 35 | PA1/PGMEN1  |

| 36 | PA0/PGMEN0  |

| 37 | TDO/TRACESWO/PB5 |  |  |  |  |

|----|------------------|--|--|--|--|

| 38 | JTAGSEL          |  |  |  |  |

| 39 | TMS/SWDIO/PB6    |  |  |  |  |

| 40 | TCK/SWCLK/PB7    |  |  |  |  |

| 41 | VDDCORE          |  |  |  |  |

| 42 | ERASE/PB12       |  |  |  |  |

| 43 | PB10             |  |  |  |  |

| 44 | PB11             |  |  |  |  |

| 45 | XOUT/PB8         |  |  |  |  |

| 46 | XIN/P/PB9/GMCK   |  |  |  |  |

| 47 | VDDIO            |  |  |  |  |

| 48 | VDDPLL           |  |  |  |  |

Note: The bottom pad of the QFN package must be connected to ground.

# 6. Input/Output Lines

The SAM4N8/16 has several kinds of input/output (I/O) lines such as general purpose I/Os (GPIO) and system I/Os. GPIOs can have alternate functionality due to multiplexing capabilities of the PIO controllers. The same PIO line can be used whether in I/O mode or by the multiplexed peripheral. System I/Os include pins such as test pins, oscillators, erase or analog inputs.

# 6.1 General Purpose I/O Lines

GPIO lines are managed by PIO controllers. All I/Os have several input or output modes such as pull-up or pull-down, input Schmitt triggers, multi-drive (open-drain), glitch filters, debouncing or input change interrupt. Programming of these modes is performed independently for each I/O line through the PIO controller user interface. For more details, refer to Section 27. "Parallel Input/Output (PIO) Controller".

Some GPIOs can have alternate function as analog input. When the GPIO is set in analog mode, all digital features of the I/O are disabled.

The input/output buffers of the PIO lines are supplied through VDDIO power supply rail.

The SAM4N8/16 embeds high-speed pads. See Section 36.10 "AC Characteristics" for more details.

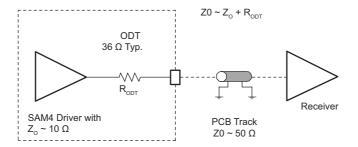

Each I/O line also embeds an ODT (On-Die Termination) (see Figure 6-1). It consists of an internal series resistor termination scheme for impedance matching between the driver output (SAM4N) and the PCB track impedance, preventing signal reflection. The series resistor helps to reduce IOs switching current (di/dt) thereby reducing in turn, EMI. It also decreases overshoot and undershoot (ringing) due to inductance of interconnect between devices or between boards. In conclusion, ODT helps diminish signal integrity issues.

Figure 6-1. On-die Termination

# 10. Peripherals

# 10.1 Peripheral Identifiers

Table 10-1 defines the peripheral identifiers of the SAM4N8/16. A peripheral identifier is required for the control of the peripheral interrupt with the Nested Vectored Interrupt Controller and for the control of the peripheral clock with the Power Management Controller.

Table 10-1. Peripheral Identifiers

| Instance ID | Instance Name | NVIC<br>Interrupt | PMC<br>Clock Control | Instance Description                                      |  |

|-------------|---------------|-------------------|----------------------|-----------------------------------------------------------|--|

| 0           | SUPC          | Х                 |                      | Supply Controller                                         |  |

| 1           | RSTC          | Х                 |                      | Reset Controller                                          |  |

| 2           | RTC           | Х                 |                      | Real-time Clock                                           |  |

| 3           | RTT           | Х                 |                      | Real-time Timer                                           |  |

| 4           | WDT           | Х                 |                      | Watchdog Timer                                            |  |

| 5           | PMC           | Х                 |                      | Power Management Controller                               |  |

| 6           | EFC           | Х                 |                      | Enhanced Flash Controller                                 |  |

| 7           | _             | _                 | _                    | Reserved                                                  |  |

| 8           | UART0         | Х                 | Х                    | Universal Asynchronous Receiver Transmitter 0             |  |

| 9           | UART1         | Х                 | Х                    | Universal Asynchronous Receiver Transmitter 1             |  |

| 10          | UART2         | Х                 | Х                    | Universal Asynchronous Receiver Transmitter 2             |  |

| 11          | PIOA          | Х                 | Х                    | Parallel I/O Controller A                                 |  |

| 12          | PIOB          | Х                 | Х                    | Parallel I/O Controller B                                 |  |

| 13          | PIOC          | Х                 | Х                    | Parallel I/O Controller C                                 |  |

| 14          | USART0        | Х                 | Х                    | Universal Synchronous Asynchronous Receiver Transmitter 0 |  |

| 15          | USART1        | Х                 | Х                    | Universal Synchronous Asynchronous Receiver Transmitter 1 |  |

| 16          | UART3         | Х                 | Х                    | Universal Asynchronous Receiver Transmitter 3             |  |

| 17          | USART2        | Х                 | Х                    | Universal Synchronous Asynchronous Receiver Transmitter 2 |  |

| 18          | -             | _                 | _                    | Reserved                                                  |  |

| 19          | TWI0          | Х                 | Х                    | Two-wire Interface 0                                      |  |

| 20          | TWI1          | Х                 | Х                    | Two-wire Interface 1                                      |  |

| 21          | SPI           | Х                 | Х                    | Serial Peripheral Interface                               |  |

| 22          | TWI2          | Х                 | Х                    | Two-wire Interface 2                                      |  |

| 23          | TC0           | Х                 | Х                    | Timer Counter Channel 0                                   |  |

| 24          | TC1           | Х                 | Х                    | Timer Counter Channel 1                                   |  |

| 25          | TC2           | Х                 | Х                    | Timer Counter Channel 2                                   |  |

| 26          | TC3           | Х                 | Х                    | Timer Counter Channel 3                                   |  |

| 27          | TC4           | Х                 | Х                    | Timer Counter Channel 4                                   |  |

| 28          | TC5           | Х                 | Х                    | Timer Counter Channel 5                                   |  |

#### 11.6.4.1 ADR

Load PC-relative address.

#### **Syntax**

```

ADR{cond} Rd, label

```

where:

cond is an optional condition code, see "Conditional Execution".

Rd is the destination register.

label is a PC-relative expression. See "PC-relative Expressions".

# Operation

ADR determines the address by adding an immediate value to the PC, and writes the result to the destination register.

ADR produces position-independent code, because the address is PC-relative.

If ADR is used to generate a target address for a BX or BLX instruction, ensure that bit[0] of the address generated is set to 1 for correct execution.

Values of *label* must be within the range of –4095 to +4095 from the address in the PC.

Note: The user might have to use the .W suffix to get the maximum offset range or to generate addresses that are not word-aligned. See "Instruction Width Selection".

#### Restrictions

Rd must not be SP and must not be PC.

### Condition Flags

This instruction does not change the flags.

#### Examples

```

ADR R1, TextMessage ; Write address value of a location labelled as ; TextMessage to R1

```

# 11.9 System Control Block (SCB)

The System Control Block (SCB) provides system implementation information, and system control. This includes configuration, control, and reporting of the system exceptions.

Ensure that the software uses aligned accesses of the correct size to access the system control block registers:

- Except for the SCB\_CFSR and SCB\_SHPR1-SCB\_SHPR3 registers, it must use aligned word accesses

- For the SCB\_CFSR and SCB\_SHPR1-SCB\_SHPR3 registers, it can use byte or aligned halfword or word accesses.

The processor does not support unaligned accesses to system control block registers.

In a fault handler, to determine the true faulting address:

- Read and save the MMFAR or SCB\_BFAR value.

- 2. Read the MMARVALID bit in the MMFSR subregister, or the BFARVALID bit in the BFSR subregister. The SCB\_MMFAR or SCB\_BFAR address is valid only if this bit is 1.

The software must follow this sequence because another higher priority exception might change the SCB\_MMFAR or SCB\_BFAR value. For example, if a higher priority handler preempts the current fault handler, the other fault might change the SCB\_MMFAR or SCB\_BFAR value.

# 17.5 Supply Controller (SUPC) User Interface

The User Interface of the Supply Controller is part of the System Controller User Interface.

## 17.5.1 System Controller (SYSC) User Interface

Table 17-1. System Controller Registers

| Offset    | System Controller Peripheral    | Name      |  |

|-----------|---------------------------------|-----------|--|

| 0x00-0x0c | Reset Controller                | RSTC      |  |

| 0x10-0x2C | Supply Controller               | SUPC      |  |

| 0x30-0x3C | Real Time Timer                 | RTT       |  |

| 0x50-0x5C | Watchdog Timer                  | WDT       |  |

| 0x60-0x8C | Real Time Clock                 | RTC       |  |

| 0x90-0xDC | General Purpose Backup Register | GPBR      |  |

| 0xE0      | Reserved                        |           |  |

| 0xE4      | Write Protect Mode Register     | SYSC_WPMR |  |

| 0xE8-0xF8 | Reserved                        |           |  |

# 17.5.2 Supply Controller (SUPC) User Interface

Table 17-2. Register Mapping

| Offset | Register                                       | Name      | Access     | Reset       |

|--------|------------------------------------------------|-----------|------------|-------------|

| 0x00   | Supply Controller Control Register             | SUPC_CR   | Write-only | N/A         |

| 0x04   | Supply Controller Supply Monitor Mode Register | SUPC_SMMR | Read-write | 0x0000_0000 |

| 0x08   | Supply Controller Mode Register                | SUPC_MR   | Read-write | 0x0000_5A00 |

| 0x0C   | Supply Controller Wake-up Mode Register        | SUPC_WUMR | Read-write | 0x0000_0000 |

| 0x10   | Supply Controller Wake-up Inputs Register      | SUPC_WUIR | Read-write | 0x0000_0000 |

| 0x14   | Supply Controller Status Register              | SUPC_SR   | Read-only  | 0x0000_0000 |

| 0x18   | Reserved                                       |           |            |             |

# 22. Bus Matrix (MATRIX)

## 22.1 Description

The Bus Matrix implements a multi-layer AHB that enables parallel access paths between multiple AHB masters and slaves in a system, which increases the overall bandwidth. Bus Matrix interconnects 3 AHB Masters to 4 AHB Slaves. The normal latency to connect a master to a slave is one cycle except for the default master of the accessed slave which is connected directly (zero cycle latency).

The Bus Matrix user interface also provides a Chip Configuration User Interface with Registers that allow to support application specific features.

### 22.2 Embedded Characteristics

#### 22.2.1 Matrix Masters

The Bus Matrix of the SAM4N product manages 3 masters, which means that each master can perform an access concurrently with others, to an available slave.

Each master has its own decoder, which is defined specifically for each master. In order to simplify the addressing, all the masters have the same decodings.

Table 22-1. List of Bus Matrix Masters

| Master 0 | Cortex-M4 Instruction/Data      |

|----------|---------------------------------|

| Master 1 | Cortex-M4 System                |

| Master 2 | Peripheral DMA Controller (PDC) |

#### 22.2.2 Matrix Slaves

The Bus Matrix of the SAM4N product manages 4 slaves. Each slave has its own arbiter, allowing a different arbitration per slave.

Table 22-2. List of Bus Matrix Slaves

| Slave 0 | Internal SRAM     |

|---------|-------------------|

| Slave 1 | Internal ROM      |

| Slave 2 | Internal Flash    |

| Slave 3 | Peripheral Bridge |

# 23.5.4 Transmit Counter Register

Name: PERIPH\_TCR

Access: Read-write

| 31 | 30    | 29 | 28 | 27 | 26 | 25 | 24 |  |

|----|-------|----|----|----|----|----|----|--|

| _  | _     | _  | _  | _  | _  | _  | _  |  |

| 23 | 22    | 21 | 20 | 19 | 18 | 17 | 16 |  |

| _  | _     | -  | -  | _  | _  | -  | _  |  |

| 15 | 14    | 13 | 12 | 11 | 10 | 9  | 8  |  |

|    | TXCTR |    |    |    |    |    |    |  |

| 7  | 6     | 5  | 4  | 3  | 2  | 1  | 0  |  |

|    | TXCTR |    |    |    |    |    |    |  |

## • TXCTR: Transmit Counter Register

TXCTR must be set to transmit buffer size.

When a half duplex peripheral is connected to the PDC, RXCTR = TXCTR.

0 = Stops peripheral data transfer to the transmitter

1- 65535 = Starts peripheral data transfer if corresponding channel is active

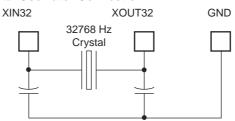

## 24.4.2 Slow Clock Crystal Oscillator

The Clock Generator integrates a 32768 Hz low-power oscillator. In order to use this oscillator, the XIN32 and XOUT32 pins must be connected to a 32768 Hz crystal. Two external capacitors must be wired as shown in Figure 24-2. More details are given in the section "DC Characteristics" of the product datasheet.

Note that the user is not obliged to use the Slow Clock Crystal and can use the RC oscillator instead.

Figure 24-2. Typical Slow Clock Crystal Oscillator Connection

The user can select the crystal oscillator to be the source of the slow clock, as it provides a more accurate frequency. The command is made by writing the Supply Controller Control Register (SUPC\_CR) with the XTALSEL bit at 1. This results in a sequence which first configures the PIO lines multiplexed with XIN32 and XOUT32 to be driven by the oscillator, then enables the crystal oscillator and then disables the RC oscillator to save power. The switch of the slow clock source is glitch free. The OSCSEL bit of the Supply Controller Status Register (SUPC\_SR) tracks the oscillator frequency downstream. It must be read in order to be informed when the switch sequence, initiated when a new value is written in MOSCSEL bit of CKGR\_MOR, is done.

Coming back on the RC oscillator is only possible by shutting down the VDDIO power supply. If the user does not need the crystal oscillator, the XIN32 and XOUT32 pins can be left unconnected since by default the XIN32 and XOUT32 system I/O pins are in PIO input mode with pull-up after reset.

The user can also set the crystal oscillator in bypass mode instead of connecting a crystal. In this case, the user has to provide the external clock signal on XIN32. The input characteristics of the XIN32 pin are given in the product electrical characteristics section. In order to set the bypass mode, the OSCBYPASS bit of the Supply Controller Mode Register (SUPC\_MR) needs to be set at 1.

The user can set the Slow Clock Crystal Oscillator in bypass mode instead of connecting a crystal. In this case, the user has to provide the external clock signal on XIN32. The input characteristics of the XIN32 pin under these conditions are given in the product electrical characteristics section.

The programmer has to be sure to set the OSCBYPASS bit in the Supply Controller Mode Register (SUPC\_MR) and XTALSEL bit in the Supply Controller Control Register (SUPC\_CR).

# 27.7 Parallel Input/Output Controller (PIO) User Interface

Each I/O line controlled by the PIO Controller is associated with a bit in each of the PIO Controller User Interface registers. Each register is 32 bits wide. If a parallel I/O line is not defined, writing to the corresponding bits has no effect. Undefined bits read zero. If the I/O line is notmultiplexed with any peripheral, the I/O line is controlled by the PIO Controller and PIO\_PSR returns 1 systematically.

Table 27-2. Register Mapping

| Offset | Register                                 | Name     | Access                                       | Reset       |

|--------|------------------------------------------|----------|----------------------------------------------|-------------|

| 0x0000 | PIO Enable Register                      | PIO_PER  | Write-only                                   | -           |

| 0x0004 | PIO Disable Register                     | PIO_PDR  | Write-only                                   | _           |

| 0x0008 | PIO Status Register                      | PIO_PSR  | Read-only                                    | (1)         |

| 0x000C | Reserved                                 | _        | _                                            | _           |

| 0x0010 | Output Enable Register                   | PIO_OER  | Write-only                                   | _           |

| 0x0014 | Output Disable Register                  | PIO_ODR  | Write-only                                   | -           |

| 0x0018 | Output Status Register                   | PIO_OSR  | Read-only                                    | 0x0000 0000 |

| 0x001C | Reserved                                 | _        | _                                            | _           |

| 0x0020 | Glitch Input Filter Enable Register      | PIO_IFER | Write-only                                   | -           |

| 0x0024 | Glitch Input Filter Disable Register     | PIO_IFDR | Write-only                                   | -           |

| 0x0028 | Glitch Input Filter Status Register      | PIO_IFSR | Read-only                                    | 0x0000 0000 |

| 0x002C | Reserved                                 | _        | _                                            | _           |

| 0x0030 | Set Output Data Register                 | PIO_SODR | Write-only                                   | _           |

| 0x0034 | Clear Output Data Register               | PIO_CODR | Write-only                                   |             |

| 0x0038 | Output Data Status Register              | PIO_ODSR | Read-only<br>or <sup>(2)</sup><br>Read-write | _           |

| 0x003C | Pin Data Status Register                 | PIO_PDSR | Read-only                                    | (3)         |

| 0x0040 | Interrupt Enable Register                | PIO_IER  | Write-only                                   | _           |

| 0x0044 | Interrupt Disable Register               | PIO_IDR  | Write-only                                   | _           |

| 0x0048 | Interrupt Mask Register                  | PIO_IMR  | Read-only                                    | 0x00000000  |

| 0x004C | Interrupt Status Register <sup>(4)</sup> | PIO_ISR  | Read-only                                    | 0x00000000  |

| 0x0050 | Multi-driver Enable Register             | PIO_MDER | Write-only                                   | _           |

| 0x0054 | Multi-driver Disable Register            | PIO_MDDR | Write-only                                   | _           |

| 0x0058 | Multi-driver Status Register             | PIO_MDSR | Read-only                                    | 0x00000000  |

| 0x005C | Reserved                                 | _        | _                                            | _           |

| 0x0060 | Pull-up Disable Register                 | PIO_PUDR | Write-only                                   | _           |

| 0x0064 | Pull-up Enable Register                  | PIO_PUER | Write-only                                   | _           |

| 0x0068 | Pad Pull-up Status Register              | PIO_PUSR | Read-only                                    | (1)         |

| 0x006C | Reserved                                 | _        | _                                            | _           |

## · ARBLST: Arbitration Lost (clear on read)

This bit is only used in Master mode.

0: Arbitration won.

1: Arbitration lost. Another master of the TWI bus has won the multi-master arbitration. TXCOMP is set at the same time.

#### SCLWS: Clock Wait State (automatically set / reset)

This bit is only used in Slave mode.

0 = The clock is not stretched.

1 = The clock is stretched. TWI\_THR / TWI\_RHR buffer is not filled / emptied before the emission / reception of a new character.

SCLWS behavior can be seen in Figure 29-28 on page 558 and Figure 29-29 on page 559.

### EOSACC: End Of Slave Access (clear on read)

This bit is only used in Slave mode.

0 = A slave access is being performing.

1 = The Slave Access is finished. End Of Slave Access is automatically set as soon as SVACC is reset.

EOSACC behavior can be seen in Figure 29-30 on page 559 and Figure 29-31 on page 560

#### ENDRX: End of RX buffer

0 = The Receive Counter Register has not reached 0 since the last write in TWI\_RCR or TWI\_RNCR.

1 = The Receive Counter Register has reached 0 since the last write in TWI\_RCR or TWI\_RNCR.

#### . ENDTX: End of TX buffer

0 = The Transmit Counter Register has not reached 0 since the last write in TWI\_TCR or TWI\_TNCR.

1 = The Transmit Counter Register has reached 0 since the last write in TWI\_TCR or TWI\_TNCR.

### • RXBUFF: RX Buffer Full

0 = TWI\_RCR or TWI\_RNCR have a value other than 0.

1 = Both TWI\_RCR and TWI\_RNCR have a value of 0.

#### • TXBUFE: TX Buffer Empty

0 = TWI\_TCR or TWI\_TNCR have a value other than 0.

1 = Both TWI\_TCR and TWI\_TNCR have a value of 0.

Table 31-11 gives the maximum time-out period for some standard baud rates.

Table 31-11. Maximum Time-out Period

| Baud Rate | Bit Time | Time-out |

|-----------|----------|----------|

| bit/sec   | μs       | ms       |

| 600       | 1 667    | 109 225  |

| 1 200     | 833      | 54 613   |

| 2 400     | 417      | 27 306   |

| 4 800     | 208      | 13 653   |

| 9 600     | 104      | 6 827    |

| 14400     | 69       | 4 551    |

| 19200     | 52       | 3 413    |

| 28800     | 35       | 2 276    |

| 38400     | 26       | 1 704    |

| 56000     | 18       | 1 170    |

| 57600     | 17       | 1 138    |

| 200000    | 5        | 328      |

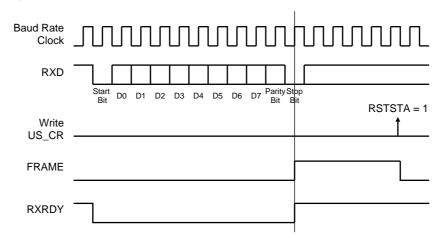

#### 31.7.3.9 Framing Error

The receiver is capable of detecting framing errors. A framing error happens when the stop bit of a received character is detected at level 0. This can occur if the receiver and the transmitter are fully desynchronized.

A framing error is reported on the FRAME bit of the Channel Status Register (US\_CSR). The FRAME bit is asserted in the middle of the stop bit as soon as the framing error is detected. It is cleared by writing the Control Register (US\_CR) with the RSTSTA bit to 1.

Figure 31-15. Framing Error Status

#### 31.7.3.10Transmit Break

The user can request the transmitter to generate a break condition on the TXD line. A break condition drives the TXD line low during at least one complete character. It appears the same as a 0x00 character sent with the parity and the stop bits to 0. However, the transmitter holds the TXD line at least during one character until the user requests the break condition to be removed.

# 31.8.10 USART Interrupt Mask Register (SPI\_MODE)

Name: US\_IMR (SPI\_MODE)

**Address:** 0x40024010 (0), 0x40028010 (1), 0x4002C010 (2)

Access: Read-only

| 31 | 30 | 29   | 28     | 27     | 26   | 25      | 24    |

|----|----|------|--------|--------|------|---------|-------|

| _  | _  | _    | _      | _      | -    | -       | _     |

| 23 | 22 | 21   | 20     | 19     | 18   | 17      | 16    |

| _  | _  | _    | _      | _      | -    | -       | _     |

| 15 | 14 | 13   | 12     | 11     | 10   | 9       | 8     |

| _  | _  | _    | RXBUFF | TXBUFE | UNRE | TXEMPTY | _     |

| 7  | 6  | 5    | 4      | 3      | 2    | 1       | 0     |

| _  | _  | OVRE | ENDTX  | ENDRX  | _    | TXRDY   | RXRDY |

This configuration is relevant only if USART\_MODE=0xE or 0xF in "USART Mode Register" on page 633.

• RXRDY: RXRDY Interrupt Mask

• TXRDY: TXRDY Interrupt Mask

OVRE: Overrun Error Interrupt Mask

• TXEMPTY: TXEMPTY Interrupt Mask

• UNRE: SPI Underrun Error Interrupt Mask

0: The corresponding interrupt is not enabled.

1: The corresponding interrupt is enabled.

## • ETRGS: External Trigger Status (cleared on read)

- 0: External trigger has not occurred since the last read of the Status Register.

- 1: External trigger has occurred since the last read of the Status Register.

#### ENDRX: End of Receiver Transfer (cleared by writing TC\_RCR or TC\_RNCR)

- 0: The Receive Counter Register has not reached 0 since the last write in TC\_RCR<sup>(1)</sup> or TC\_RNCR<sup>(1)</sup>.

- 1: The Receive Counter Register has reached 0 since the last write in TC\_RCR or TC\_RNCR.

## RXBUFF: Reception Buffer Full (cleared by writing TC\_RCR or TC\_RNCR)

- 0: TC\_RCR or TC\_RNCR have a value other than 0.

- 1: Both TC\_RCR and TC\_RNCR have a value of 0.

- Note: 1. TC\_RCR and TC\_RNCR are PDC registers.

## CLKSTA: Clock Enabling Status

- 0: Clock is disabled.

- 1: Clock is enabled.

#### MTIOA: TIOA Mirror

- 0: TIOA is low. If TC\_CMRx.WAVE = 0, this means that TIOA pin is low. If TC\_CMRx.WAVE = 1, this means that TIOA is driven low.

- 1: TIOA is high. If TC\_CMRx.WAVE = 0, this means that TIOA pin is high. If TC\_CMRx.WAVE = 1, this means that TIOA is driven high.

#### • MTIOB: TIOB Mirror

- 0: TIOB is low. If TC\_CMRx.WAVE = 0, this means that TIOB pin is low. If TC\_CMRx.WAVE = 1, this means that TIOB is driven low.

- 1: TIOB is high. If TC\_CMRx.WAVE = 0, this means that TIOB pin is high. If TC\_CMRx.WAVE = 1, this means that TIOB is driven high.

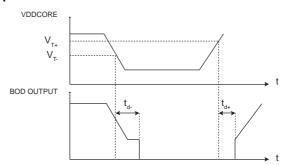

Table 36-4. Core Power Supply Brownout Detector Characteristics

| Symbol               | Parameter                                  | Conditions                                    | Min  | Тур | Max  | Unit |

|----------------------|--------------------------------------------|-----------------------------------------------|------|-----|------|------|

| V <sub>T-</sub>      | Supply Falling Threshold                   | After trimming                                | 0.98 | 1.0 | 1.04 | V    |

| V <sub>hys</sub>     | Hysteresis Voltage                         | _                                             |      |     | 110  | mV   |

| V <sub>T+</sub>      | Supply Rising Threshold                    | _                                             | 0.8  | 1.0 | 1.08 | V    |

| t <sub>RST</sub>     | Reset Period                               | V <sub>DDIO</sub> rising from 0 to 1.2V ± 10% | 90   | -   | 320  | μs   |

| I <sub>DDON</sub>    | Comment Consumption on VDDCODE             | Brownout Detector enabled                     |      |     | 24   |      |

| I <sub>DDOFF</sub>   | Current Consumption on VDDCORE             | Brownout Detector disabled                    |      |     | 2    | μA   |

| I <sub>DD33ON</sub>  | Comment Consumption on VIDDIO              | Brownout Detector enabled                     |      |     | 24   |      |

| I <sub>DD33OFF</sub> | Current Consumption on VDDIO               | Brownout Detector disabled                    |      |     | 2    | μA   |

| t <sub>d-</sub>      | V <sub>T-</sub> Detection Propagation Time | VDDCORE = $V_{T+}$ to ( $V_{T-}$ - 100 mV)    |      | 200 | 300  | ns   |

| t <sub>START</sub>   | Startup Time                               | From disabled state to enabled state          |      |     | 300  | μs   |

Figure 36-1. Core Brownout Output Waveform

Table 36-5. VDDIO Supply Monitor

| Symbol                   | Parameter                      | Conditions                           | Min  | Тур  | Max  | Unit |

|--------------------------|--------------------------------|--------------------------------------|------|------|------|------|

| V <sub>T</sub>           | Supply Monitor Threshold       | 16 selectable steps                  | 1.6  |      | 3.4  | V    |

| V <sub>T(accuracy)</sub> | Threshold Level Accuracy       | -40 to +85°C                         | -1   |      | +1   | %    |

| V <sub>hys</sub>         | Hysteresis Voltage             |                                      |      | 30   | 40   | mV   |

|                          |                                | All temperatures, enabled            |      |      |      |      |

| $I_{DDON}$               |                                | Normal mode                          |      |      | 40   | μΑ   |

|                          | Company Compounding on VDDCODE | Standby mode                         |      |      | 2    | μΑ   |

|                          | Current Consumption on VDDCORE | 25°C, disabled                       |      |      |      |      |

| $I_{\text{DDOFF}}$       |                                | Normal mode                          | 15.9 | 18.6 | 32   | μΑ   |

|                          |                                | Standby mode                         | 5.9  | 7.0  | 10.3 | nA   |

| t <sub>START</sub>       | Startup Time                   | From disabled state to enabled state |      |      | 300  | μs   |

## 36.10 AC Characteristics

### 36.10.1 Master Clock Characteristics

Table 36-40. Master Clock Waveform Parameters

| Symbol                     | Parameter              | Conditions      | Min | Max | Unit    |

|----------------------------|------------------------|-----------------|-----|-----|---------|

| 1/(t <sub>CPMCK</sub> ) Ma | Master Clock Frequency | VDDCORE @ 1.20V |     | 100 | MHz     |

|                            |                        | VDDCORE @ 1.08V |     | 80  | IVII IZ |

#### 36.10.2 I/O Characteristics

Criteria used to define the maximum frequency of the I/Os:

- Output duty cycle (40%–60%)

- Minimum output swing: 100 mV to VDDIO 100 mV

- Minimum output swing: 100 mV to VDDIO 100 mV

- Addition of rising and falling time inferior to 75% of the period

Table 36-41. I/O Characteristics

| Symbol                 | Parameter                                           | Co    | onditions          | Min  | Max | Unit   |

|------------------------|-----------------------------------------------------|-------|--------------------|------|-----|--------|

| Гээ э.Мэээ <b>4</b>    | Dia Constant (1) Marrian Contant Frances            | 10 pF |                    |      | 70  | N41.1- |

| FreqMax1               | Pin Group 1 <sup>(1)</sup> Maximum Output Frequency | 25 pF |                    |      | 35  | MHz    |

| Dudanaiald             | Die Oeser 4 (1) Hiele Level Dule - Width            | 10 pF |                    | 7.2  |     |        |

| PulseminH <sub>1</sub> | Pin Group 1 <sup>(1)</sup> High Level Pulse Width   | 25 pF |                    | 14.2 |     | ns     |

| Dudanaini              | Die Oesen 4 (1) Level en el Dule e Mielle           | 10 pF |                    | 7.2  |     |        |

| PulseminL <sub>1</sub> | Pin Group 1 <sup>(1)</sup> Low Level Pulse Width    | 25 pF |                    | 14.2 |     | – ns   |

| F===M===0              | Dia Occasional (2) Marriagona Octavit Francisco     | 10 pF |                    |      | 70  | NAL 1- |

| FreqMax2               | Pin Group 2 <sup>(2)</sup> Maximum Output Frequency | 25 pF |                    |      | 35  | MHz    |

| D                      | D: 0 (2) 11: 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1      | 10 pF |                    | 7.2  |     | ns     |

| PulseminH <sub>2</sub> | Pin Group 2 (2) High Level Pulse Width              | 25pF  |                    | 14.2 |     |        |

| D                      | D: 0 0(2) 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     | 10 pF |                    | 7.2  |     |        |

| PulseminL <sub>2</sub> | Pin Group 2 (2) Low Level Pulse Width               | 25 pF |                    | 14.2 |     | – ns   |

| F M 0                  | Dia Constant Francisco                              | 10 pF | \/ 4.00\/          |      | 70  | NAL 1- |

| FreqMax3               | Pin Group 3 <sup>(3)</sup> Maximum Output Frequency | 25 pF | $V_{DDIO} = 1.62V$ |      | 35  | - MHz  |

| Dudanaiald             | Dia Consum 2 (3) Hints I amed Dulan Wildle          | 10 pF |                    | 7.2  |     | ns     |

| PulseminH <sub>3</sub> | Pin Group 3 <sup>(3)</sup> High Level Pulse Width   | 25 pF |                    | 14.2 |     |        |

| Dulgaraini             | Pin Group 3 (3) Low Level Pulse Width               | 10 pF | <del>-</del>       | 7.2  |     |        |

| PulseminL <sub>3</sub> | Pin Group 3 (4) Low Level Pulse Width               | 25 pF |                    | 14.2 |     | ns     |

| Franklay4              | Dia Craus 4(4)NAcrimo no Critario Francisco         | 10 pF |                    |      | 70  | NAL 1- |

| FreqMax4               | Pin Group 4 <sup>(4)</sup> Maximum Output Frequency | 25 pF |                    |      | 35  | MHz    |

| Dulgaraigh             | Die Craus 4(4) High Lavel Dulas Middle              | 10 pF |                    | 7.2  |     |        |

| PulseminH <sub>4</sub> | Pin Group 4 <sup>(4)</sup> High Level Pulse Width   | 25pF  |                    | 14.2 |     | ns     |

| Dulaamial              | Pin Group 4 <sup>(4)</sup> Low Level Pulse Width    | 10 pF | †                  | 7.2  |     | ne     |

| PulseminL <sub>4</sub> | Fin Group 4.7 Low Level Pulse Width                 | 25 pF |                    | 14.2 |     | ns     |

| ErogMov <i>E</i>       | Pin Group 5 <sup>(5)</sup> Maximum Output Frequency | 10 pF |                    |      | 70  | NALI-  |

| FreqMax5               | Fin Group 5 Maximum Output Frequency                | 25 pF |                    |      | 35  | MHz    |

## 36.10.3 SPI Characteristics

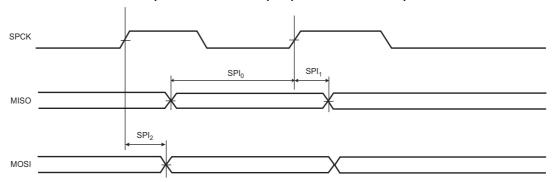

Figure 36-14. SPI Master Mode with (CPOL = NCPHA = 0) or (CPOL = NCPHA = 1)

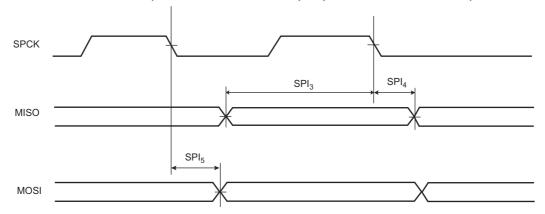

Figure 36-15. SPI Master Mode with (CPOL = 0 and NCPHA = 1) or (CPOL = 1 and NCPHA = 0)

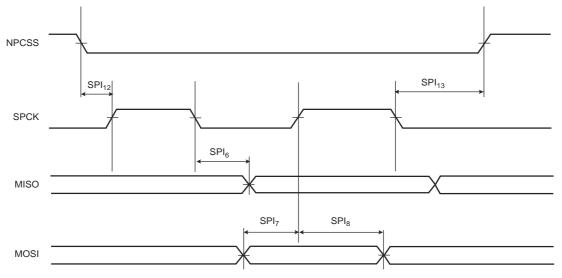

Figure 36-16. SPI Slave Mode with (CPOL = 0 and NCPHA = 1) or (CPOL = 1 and NCPHA = 0)

# Table 41-1. SAM4N Datasheet Rev. 11158B Revision History (Continued)

| Issue Date | Comments                                                                                                                                                                                                                                           |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Section 32. "Timer Counter (TC)" (cont'd)                                                                                                                                                                                                          |

|            | Section 32.7.5 "TC Counter Value Register": added notation "IMPORTANT: For 16-bit channels, CV field size is limited to register bits 15:0"                                                                                                        |

|            | Section 32.7.6 "TC Register A": added notation "IMPORTANT: For 16-bit channels, RA field size is limited to register bits 15:0"                                                                                                                    |

|            | Section 32.7.7 "TC Register B": added notation "IMPORTANT: For 16-bit channels, RB field size is limited to register bits 15:0"                                                                                                                    |

|            | Section 32.7.8 "TC Register C": added notation "IMPORTANT: For 16-bit channels, RC field size is limited to register bits 15:0"                                                                                                                    |

|            | Section 32.7.9 "TC Status Register": updated bit descriptions                                                                                                                                                                                      |

|            | Section 32.7.14 "TC Block Mode Register": removed FILTER bit (register bit 19 now reserved); corrected TC2XC2S field configuration values: value 2 is TIOA0 (was TIOA1); value 3 is TIOA1 (was TIOA2)                                              |

|            | Section 32.7.20 "TC Write Protection Mode Register": modified register name (was "TC Write Protect Mode Register"); updated WPEN bit description (replaced list of protectable registers with link to Section 32.6.18 "Register Write Protection") |

|            | Section 36. "SAM4N Electrical Characteristics"                                                                                                                                                                                                     |

|            | Updated and harmonized parameter symbols                                                                                                                                                                                                           |

|            | Table 36-2 "DC Characteristics": replaced two footnotes with single footnote                                                                                                                                                                       |

|            | Table 36-3 "1.2V Voltage Regulator Characteristics": replaced two footnotes with single footnote in V <sub>DDIN</sub> conditions; deleted "Cf. External Capacitor Requirements" from CD <sub>IN</sub> and CD <sub>OUT</sub> conditions             |

|            | Table 36-4 "Core Power Supply Brownout Detector Characteristics": added parameter "Reset Period"                                                                                                                                                   |

|            | Table 36-7 "Zero-Power-On Reset Characteristics": modified parameter name "Reset Time-out Period" to "Reset Period"                                                                                                                                |

|            | Table 36-20 "4/8/12 MHz RC Oscillators Characteristics": updated Startup Time conditions                                                                                                                                                           |

| 23-Mar-15  | Table 36-21 "32.768 kHz Crystal Oscillator Characteristics": added parameter "Allowed Crystal Capacitance Load"                                                                                                                                    |

|            | Table 36-23 "3 to 20 MHz Crystal Oscillator Characteristics": added "pF" unit for "Internal Load Capacitance" parameter; deleted all footnotes                                                                                                     |

|            | Section 36.3.3 "Active Mode Power Consumption": updated conditions (VDDCORE and ambient temperature) for "CoreMark Active Power Consumption" tables and for Figure 36-9 "SAM4N8/16 Active Power Consumption with VDDCORE @ 1.2V, TA = 25°C"        |

|            | Figure 36-10 "32.768 kHz Crystal Oscillator Schematics": added caption "C <sub>crystal</sub> " to diagram                                                                                                                                          |

|            | Updated Figure 36-12 "XIN Clock Timing"                                                                                                                                                                                                            |

|            | Table 36-27 "PLL Characteristics": changed parameter "Start-up Time" to "Settling Time"                                                                                                                                                            |

|            | Figure 36-13 "Simplified Acquisition Path": renamed caption "Csample" to "C <sub>i</sub> "; renamed caption "12-bit ADC Core" to "12-bit ADC"                                                                                                      |

|            | Figure 36-19 "USART SPI Slave Mode (Mode 1 or 2)": inserted correct diagram (was previously TWI diagram)                                                                                                                                           |

|            | Figure 36-20 "Two-wire Serial Bus Timing": inserted correct diagram (was previously USART diagram)                                                                                                                                                 |

|            | Section 36.10.3.1 "Maximum SPI Frequency": updated contents under "Master Write Mode" and "Master Read Mode"                                                                                                                                       |

|            | Added Table 36-34 "Programmable Voltage Reference Selection Values"                                                                                                                                                                                |

|            | Table 36-38 "Voltage Reference Characteristics": in bias current consumption, corrected conditions "Voltage reference OFF, ADC ON OR ADC ON" to "Voltage reference Off, ADC On or DAC On"                                                          |

|            | Table 36-39 "Temperature Sensor Characteristics": deleted "After TSON = 1" from Startup Time conditions                                                                                                                                            |

|            | Table 36-42 "SPI Timings": removed footnotes defining 1.8V and 3.3V domains (this information is now found at the beginning of Section 36.10.3.2 "SPI Timings")                                                                                    |

|            | Table 36-43 "USART SPI Timings": removed footnotes defining 1.8V and 3.3V domains (this information is now found at the beginning of Section 36.10.4.1 "USART SPI TImings")                                                                        |

|            | Table 36-44 "Two-wire Serial Bus Requirements": added parameter "Bus free time between a STOP and START condition"                                                                                                                                 |

|     | 23.5                         | Peripheral DMA Controller (PDC) User Interface                                           | 378                      |

|-----|------------------------------|------------------------------------------------------------------------------------------|--------------------------|

| 24. | Cloc                         | k Generator                                                                              | 389                      |

|     | 24.1                         | Description                                                                              | 389                      |

|     | 24.2                         | Embedded Characteristics                                                                 | 389                      |

|     | 24.3                         | Block Diagram                                                                            | 390                      |

|     | 24.4                         | Slow Clock                                                                               | 390                      |

|     | 24.5                         | Main Clock                                                                               | 392                      |

|     | 24.6                         | Divider and PLL Block                                                                    | 395                      |

| 25. | Pow                          | er Management Controller (PMC)                                                           | 397                      |

|     | 25.1                         | Description                                                                              | 397                      |

|     | 25.2                         | Embedded Characteristics                                                                 | 397                      |

|     | 25.3                         | Block Diagram                                                                            | 398                      |

|     | 25.4                         | Master Clock Controller                                                                  | 398                      |

|     | 25.5                         | Processor Clock Controller                                                               | 399                      |

|     | 25.6                         | SysTick Clock                                                                            | 399                      |

|     | 25.7                         | Peripheral Clock Controller                                                              | 399                      |

|     | 25.8                         | Free Running Processor Clock                                                             | 399                      |

|     | 25.9                         | Programmable Clock Output Controller                                                     | 400                      |

|     | 25.10                        | Fast Start-up                                                                            | 400                      |

|     | 25.11                        |                                                                                          |                          |

|     | 25.12                        | Slow Crystal Clock Frequency Monitor                                                     | 402                      |

|     | 25.13                        | Programming Sequence                                                                     | 402                      |

|     | 25.14                        | Clock Switching Details                                                                  | 405                      |

|     | 25.15                        | Write Protection Registers                                                               | 407                      |

|     | 25.16                        | Power Management Controller (PMC) User Interface                                         | 408                      |

| 26. | Chip                         | Identifier (CHIPID)                                                                      | 432                      |

|     | 26.1                         | Description                                                                              | 432                      |

|     | 26.2                         | Embedded Characteristics                                                                 | 432                      |

|     | 26.3                         | Chip Identifier (CHIPID) User Interface                                                  | 433                      |

| 27. | Para                         | ıllel Input/Output (PIO) Controller                                                      | 439                      |

|     | 27.1                         | Description                                                                              | 439                      |

|     | 27.2                         | Embedded Characteristics                                                                 | 439                      |

|     | 27.3                         | Block Diagram                                                                            |                          |

|     | 27.4                         | Product Dependencies                                                                     | 441                      |

|     | 27.5                         | Functional Description                                                                   | 442                      |

|     | 27.6                         | I/O Lines Programming Example                                                            | 450                      |

|     | 27.7                         | Parallel Input/Output Controller (PIO) User Interface                                    |                          |

| 28. | Seria                        | al Peripheral Interface (SPI)                                                            | 502                      |

|     | 28.1                         | Description                                                                              |                          |

|     |                              |                                                                                          | 502                      |

|     | 28.2                         | Embedded Characteristics                                                                 |                          |

|     | _                            | Embedded Characteristics                                                                 | 502                      |

|     | 28.2                         | Embedded Characteristics                                                                 | 502<br>503               |

|     | 28.2<br>28.3                 | Embedded Characteristics  Block Diagram  Application Block Diagram                       | 502<br>503<br>503        |

|     | 28.2<br>28.3<br>28.4         | Embedded Characteristics  Block Diagram.  Application Block Diagram  Signal Description. | 502<br>503<br>503        |

|     | 28.2<br>28.3<br>28.4<br>28.5 | Embedded Characteristics  Block Diagram  Application Block Diagram                       | 502<br>503<br>504<br>504 |