#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 100MHz                                                                   |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 47                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 11x10b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4n8ba-mur |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 11-11. Faults

| Fault                                                            | Handler             | Bit Name                | Fault Status Register                                  |  |  |

|------------------------------------------------------------------|---------------------|-------------------------|--------------------------------------------------------|--|--|

| Bus error on a vector read                                       |                     | VECTTBL                 |                                                        |  |  |

| Fault escalated to a hard fault                                  | Hard fault          | FORCED                  | "Hard Fault Status Register"                           |  |  |

| MPU or default memory map mismatch:                              |                     | -                       | -                                                      |  |  |

| on instruction access                                            |                     | IACCVIOL                |                                                        |  |  |

| on data access                                                   | Memory              | DACCVIOL <sup>(2)</sup> |                                                        |  |  |

| during exception stacking                                        | management<br>fault | MSTKERR                 | "MMFSR: Memory Management Fault<br>Status Subregister" |  |  |

| during exception unstacking                                      |                     | MUNSKERR                |                                                        |  |  |

| during lazy floating-point state preservation                    |                     | MLSPERR                 |                                                        |  |  |

| Bus error:                                                       |                     | -                       | -                                                      |  |  |

| during exception stacking                                        |                     | STKERR                  |                                                        |  |  |

| during exception unstacking                                      |                     | UNSTKERR                |                                                        |  |  |

| during instruction prefetch                                      | Bus fault           | IBUSERR                 | "DECD, Due Fould Status Cubra sister"                  |  |  |

| during lazy floating-point state preservation                    |                     | LSPERR                  | "BFSR: Bus Fault Status Subregister"                   |  |  |

| Precise data bus error                                           |                     | PRECISERR               |                                                        |  |  |

| Imprecise data bus error                                         |                     | IMPRECISERR             |                                                        |  |  |

| Attempt to access a coprocessor                                  |                     | NOCP                    |                                                        |  |  |

| Undefined instruction                                            |                     | UNDEFINSTR              |                                                        |  |  |

| Attempt to enter an invalid instruction set state <sup>(1)</sup> |                     | INVSTATE                | "IIFSD: Lloogo Foult Status Subracistar"               |  |  |

| Invalid EXC_RETURN value                                         | Usage fault         | INVPC                   | "UFSR: Usage Fault Status Subregister"                 |  |  |

| Illegal unaligned load or store                                  |                     | UNALIGNED               |                                                        |  |  |

| Divide By 0                                                      |                     | DIVBYZERO               |                                                        |  |  |

Notes: 1. Occurs on an access to an XN region even if the processor does not include an MPU or the MPU is disabled.

2. Attempt to use an instruction set other than the Thumb instruction set, or return to a non load/store-multiple instruction with ICI continuation.

## Fault Escalation and Hard Faults

All faults exceptions except for hard fault have configurable exception priority, see "System Handler Priority Registers". The software can disable the execution of the handlers for these faults, see "System Handler Control and State Register".

Usually, the exception priority, together with the values of the exception mask registers, determines whether the processor enters the fault handler, and whether a fault handler can preempt another fault handler, as described in "Exception Model".

| Mnemonic                         | Operands               | Description                                | Flags   |

|----------------------------------|------------------------|--------------------------------------------|---------|

| SMULBB, SMULBT<br>SMULTB, SMULTT | {Rd,} Rn, Rm           | Signed Multiply (halfwords)                | -       |

| SMULL                            | RdLo, RdHi, Rn, Rm     | Signed Multiply (32 x 32), 64-bit result   | -       |

| SMULWB, SMULWT                   | {Rd,} Rn, Rm           | Signed Multiply word by halfword           | -       |

| SMUSD, SMUSDX                    | {Rd,} Rn, Rm           | Signed dual Multiply Subtract              | -       |

| SSAT                             | Rd, #n, Rm {,shift #s} | Signed Saturate                            | Q       |

| SSAT16                           | Rd, #n, Rm             | Signed Saturate 16                         | Q       |

| SSAX                             | {Rd,} Rn, Rm           | Signed Subtract and Add with Exchange      | GE      |

| SSUB16                           | {Rd,} Rn, Rm           | Signed Subtract 16                         | -       |

| SSUB8                            | {Rd,} Rn, Rm           | Signed Subtract 8                          | -       |

| STM                              | Rn{!}, reglist         | Store Multiple registers, increment after  | -       |

| STMDB, STMEA                     | Rn{!}, reglist         | Store Multiple registers, decrement before | -       |

| STMFD, STMIA                     | Rn{!}, reglist         | Store Multiple registers, increment after  | -       |

| STR                              | Rt, [Rn, #offset]      | Store Register word                        | -       |

| STRB, STRBT                      | Rt, [Rn, #offset]      | Store Register byte                        | -       |

| STRD                             | Rt, Rt2, [Rn, #offset] | Store Register two words                   | -       |

| STREX                            | Rd, Rt, [Rn, #offset]  | Store Register Exclusive                   | -       |

| STREXB                           | Rd, Rt, [Rn]           | Store Register Exclusive byte              | -       |

| STREXH                           | Rd, Rt, [Rn]           | Store Register Exclusive halfword          | -       |

| STRH, STRHT                      | Rt, [Rn, #offset]      | Store Register halfword                    | -       |

| STRT                             | Rt, [Rn, #offset]      | Store Register word                        | -       |

| SUB, SUBS                        | {Rd,} Rn, Op2          | Subtract                                   | N,Z,C,V |

| SUB, SUBW                        | {Rd,} Rn, #imm12       | Subtract                                   | N,Z,C,V |

| SVC                              | #imm                   | Supervisor Call                            | -       |

| SXTAB                            | {Rd,} Rn, Rm,{,ROR #}  | Extend 8 bits to 32 and add                | -       |

| SXTAB16                          | {Rd,} Rn, Rm,{,ROR #}  | Dual extend 8 bits to 16 and add           | -       |

| SXTAH                            | {Rd,} Rn, Rm,{,ROR #}  | Extend 16 bits to 32 and add               | -       |

| SXTB16                           | {Rd,} Rm {,ROR #n}     | Signed Extend Byte 16                      | -       |

| SXTB                             | {Rd,} Rm {,ROR #n}     | Sign extend a byte                         | -       |

| SXTH                             | {Rd,} Rm {,ROR #n}     | Sign extend a halfword                     | -       |

| ТВВ                              | [Rn, Rm]               | Table Branch Byte                          | -       |

| ТВН                              | [Rn, Rm, LSL #1]       | Table Branch Halfword                      | -       |

| TEQ                              | Rn, Op2                | Test Equivalence                           | N,Z,C   |

| TST                              | Rn, Op2                | Test                                       | N,Z,C   |

| UADD16                           | {Rd,} Rn, Rm           | Unsigned Add 16                            | GE      |

| UADD8                            | {Rd,} Rn, Rm           | Unsigned Add 8                             | GE      |

| USAX                             | {Rd,} Rn, Rm           | Unsigned Subtract and Add with Exchange    | GE      |

# Table 11-13. Cortex-M4 Instructions (Continued)

The Compare operations are identical to subtracting, for CMP, or adding, for CMN, except that the result is discarded. See the instruction descriptions for more information.

Note: Most instructions update the status flags only if the S suffix is specified. See the instruction descriptions for more information.

### Condition Code Suffixes

The instructions that can be conditional have an optional condition code, shown in syntax descriptions as {cond}. Conditional execution requires a preceding IT instruction. An instruction with a condition code is only executed if the condition code flags in the APSR meet the specified condition. Table 11-16 shows the condition codes to use.

A conditional execution can be used with the IT instruction to reduce the number of branch instructions in code.

Table 11-16 also shows the relationship between condition code suffixes and the N, Z, C, and V flags.

| Suffix      | Flags              | Meaning                                                  |

|-------------|--------------------|----------------------------------------------------------|

| EQ          | Z = 1              | Equal                                                    |

| NE          | Z = 0              | Not equal                                                |

| CS or<br>HS | C = 1              | Higher or same, unsigned ≥                               |

| CC or<br>LO | C = 0              | Lower, unsigned <                                        |

| MI          | N = 1              | Negative                                                 |

| PL          | N = 0              | Positive or zero                                         |

| VS          | V = 1              | Overflow                                                 |

| VC          | V = 0              | No overflow                                              |

| ні          | C = 1 and Z = 0    | Higher, unsigned >                                       |

| LS          | C = 0  or  Z = 1   | Lower or same, unsigned $\leq$                           |

| GE          | N = V              | Greater than or equal, signed $\geq$                     |

| LT          | N != V             | Less than, signed <                                      |

| GT          | Z = 0 and $N = V$  | Greater than, signed >                                   |

| LE          | Z = 1 and N != V   | Less than or equal, signed $\leq$                        |

| AL          | Can have any value | Always. This is the default when no suffix is specified. |

Table 11-16.Condition Code Suffixes

#### Absolute Value

The example below shows the use of a conditional instruction to find the absolute value of a number. R0 = ABS(R1).

| MOVS  | R0, R1     | ; R0 = R1, setting flags                    |

|-------|------------|---------------------------------------------|

| IT    | MI         | ; IT instruction for the negative condition |

| RSBMI | R0, R1, #0 | ; If negative, R0 = -R1                     |

#### Compare and Update Value

The example below shows the use of conditional instructions to update the value of R4 if the signed values R0 is greater than R1 and R2 is greater than R3.

| CMP   | R0, R1 | ; Compare R0 and R1, setting flags                    |  |

|-------|--------|-------------------------------------------------------|--|

| ITT   | GT     | ; IT instruction for the two GT conditions            |  |

| CMPGT | R2, R3 | ; If 'greater than', compare R2 and R3, setting flags |  |

| MOVGT | R4, R5 | ; If still 'greater than', do R4 = R5                 |  |

### 11.6.5.20 UHSUB16 and UHSUB8

Unsigned Halving Subtract 16 and Unsigned Halving Subtract 8

Syntax

op{cond}{Rd,} Rn, Rm

where:

| ор   | is any of:                                                                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------|

|      | UHSUB16 Performs two unsigned 16-bit integer additions, halves the results, and writes the results to the destination register. |

|      | UHSUB8 Performs four unsigned 8-bit integer additions, halves the results, and writes the results to the destination register.  |

| cond | is an optional condition code, see "Conditional Execution" .                                                                    |

| Rd   | is the destination register.                                                                                                    |

| Rn   | is the first register holding the operand.                                                                                      |

| Rm   | is the second register holding the operand.                                                                                     |

### Operation

Use these instructions to add 16-bit and 8-bit data and then to halve the result before writing the result to the destination register:

The UHSUB16 instruction:

- 1. Subtracts each halfword of the second operand from the corresponding halfword of the first operand.

- 2. Shuffles each halfword result to the right by one bit, halving the data.

- 3. Writes each unsigned halfword result to the corresponding halfwords in the destination register.

The UHSUB8 instruction:

- 1. Subtracts each byte of second operand from the corresponding byte of the first operand.

- 2. Shuffles each byte result by one bit to the right, halving the data.

- 3. Writes the unsigned byte results to the corresponding byte of the destination register.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not change the flags.

Examples

| UHSUB16 | R1, | R0  |    | ; Subtracts halfwords in R0 from corresponding halfword of    |

|---------|-----|-----|----|---------------------------------------------------------------|

|         |     |     |    | ; R1 and writes halved result to corresponding halfword in R1 |

| UHSUB8  | R4, | R0, | R5 | ; Subtracts bytes of R5 from corresponding byte in R0 and     |

|         |     |     |    | ; writes halved result to corresponding byte in R4.           |

Atmel

#### 11.6.6.1 MUL, MLA, and MLS

Multiply, Multiply with Accumulate, and Multiply with Subtract, using 32-bit operands, and producing a 32-bit result. Syntax

MUL{S}{cond} {Rd,} Rn, Rm ; Multiply

MLA{cond} Rd, Rn, Rm, Ra ; Multiply with accumulate

MLS{cond} Rd, Rn, Rm, Ra ; Multiply with subtract

where:

cond is an optional condition code, see "Conditional Execution" .

S is an optional suffix. If S is specified, the condition code flags are updated on the result of the operation, see "Conditional Execution".

Rd is the destination register. If *Rd* is omitted, the destination register is *Rn*.

Rn, Rm are registers holding the values to be multiplied.

Ra is a register holding the value to be added or subtracted from.

Operation

The MUL instruction multiplies the values from *Rn* and *Rm*, and places the least significant 32 bits of the result in *Rd*.

The MLA instruction multiplies the values from *Rn* and *Rm*, adds the value from *Ra*, and places the least significant 32 bits of the result in *Rd*.

The MLS instruction multiplies the values from *Rn* and *Rm*, subtracts the product from the value from *Ra*, and places the least significant 32 bits of the result in *Rd*.

The results of these instructions do not depend on whether the operands are signed or unsigned.

Restrictions

In these instructions, do not use SP and do not use PC.

If the S suffix is used with the MUL instruction:

- Rd, Rn, and Rm must all be in the range R0 to R7

- Rd must be the same as Rm

- The cond suffix must not be used.

**Condition Flags**

If S is specified, the MUL instruction:

- Updates the N and Z flags according to the result

- Does not affect the C and V flags.

Examples

```

MULR10, R2, R5; Multiply, R10 = R2 x R5MLAR10, R2, R1, R5; Multiply with accumulate, R10 = (R2 x R1) + R5MULSR0, R2, R2; Multiply with flag update, R0 = R2 x R2MULLTR2, R3, R2; Conditionally multiply, R2 = R3 x R2MLSR4, R5, R6, R7; Multiply with subtract, R4 = R7 - (R5 x R6)

```

Atmel

| 11.9.1.5 Ap<br>Name:<br>Access:<br>Reset: | plication Interrupt a<br>SCB_AIRCR<br>Read-write<br>0x000000000 | nd Reset Co | ontrol Register |           |             |                   |           |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------|-------------|-----------------|-----------|-------------|-------------------|-----------|--|--|--|

| 31                                        | 30                                                              | 29          | 28              | 27        | 26          | 25                | 24        |  |  |  |

|                                           | VECTKEYSTAT/VECTKEY                                             |             |                 |           |             |                   |           |  |  |  |

| 23                                        | 22                                                              | 21          | 20              | 19        | 18          | 17                | 16        |  |  |  |

|                                           |                                                                 |             | VECTKEYSTA      | T/VECTKEY |             |                   |           |  |  |  |

| 15                                        | 14                                                              | 13          | 12              | 11        | 10          | 9                 | 8         |  |  |  |

| ENDIANNES                                 | SS                                                              |             | -               |           |             | PRIGROUP          |           |  |  |  |

| 7                                         | 6                                                               | 5           | 4               | 3         | 2           | 1                 | 0         |  |  |  |

|                                           |                                                                 | _           |                 |           | SYSRESETREQ | VECTCLRACTI<br>VE | VECTRESET |  |  |  |

The SCB\_AIRCR register provides priority grouping control for the exception model, endian status for data accesses, and reset control of the system. To write to this register, write 0x5FA to the VECTKEY field, otherwise the processor ignores the write.

## • VECTKEYSTAT: Register Key

Read:

Reads as 0xFA05.

## • VECTKEY: Register Key

Write:

Writes 0x5FA to VECTKEY, otherwise the write is ignored.

## • ENDIANNESS: Data Endianness

0: Little-endian.

1: Big-endian.

| 11.9.1.9 S | ystem Handler Priorit | y Register 1 |    |    |    |    |    |  |

|------------|-----------------------|--------------|----|----|----|----|----|--|

| Name:      | SCB_SHPR1             |              |    |    |    |    |    |  |

| Access:    | Read-write            |              |    |    |    |    |    |  |

| Reset:     | 0x00000000            |              |    |    |    |    |    |  |

| 31         | 30                    | 29           | 28 | 27 | 26 | 25 | 24 |  |

|            |                       |              | -  |    |    |    |    |  |

| 23         | 22                    | 21           | 20 | 19 | 18 | 17 | 16 |  |

|            |                       |              | PR | _6 |    |    |    |  |

| 15         | 14                    | 13           | 12 | 11 | 10 | 9  | 8  |  |

| PRI_5      |                       |              |    |    |    |    |    |  |

| 7          | 6                     | 5            | 4  | 3  | 2  | 1  | 0  |  |

|            |                       |              | PR | _4 |    |    |    |  |

## • PRI\_6: Priority

Priority of system handler 6, UsageFault.

## • PRI\_5: Priority

Priority of system handler 5, BusFault.

## • PRI\_4: Priority

Priority of system handler 4, MemManage.

## 25.16.8 PMC Clock Generator Main Clock Frequency Register

| Name:    | CKGR_MCFR  |    |        |     |    |    |          |  |  |  |

|----------|------------|----|--------|-----|----|----|----------|--|--|--|

| Address: | 0x400E0424 |    |        |     |    |    |          |  |  |  |

| Access:  | Read-Write |    |        |     |    |    |          |  |  |  |

| 31       | 30         | 29 | 28     | 27  | 26 | 25 | 24       |  |  |  |

| _        | -          | _  | -      | -   | -  | _  | -        |  |  |  |

|          |            |    |        |     |    |    |          |  |  |  |

| 23       | 22         | 21 | 20     | 19  | 18 | 17 | 16       |  |  |  |

| -        | -          | —  | RCMEAS | -   | -  | _  | MAINFRDY |  |  |  |

|          |            |    | -      | -   |    |    |          |  |  |  |

| 15       | 14         | 13 | 12     | 11  | 10 | 9  | 8        |  |  |  |

|          | MAINF      |    |        |     |    |    |          |  |  |  |

| 7        | 6          | 5  | 4      | 3   | 2  | 1  | 0        |  |  |  |

|          |            |    | MA     | INF |    |    |          |  |  |  |

This register can only be written if the WPEN bit is cleared in "PMC Write Protect Mode Register" .

## • MAINF: Main Clock Frequency

Gives the number of Main Clock cycles within 16 Slow Clock periods.

## • MAINFRDY: Main Clock Ready

0 = MAINF value is not valid or the Main Oscillator is disabled or a measure has just been started by means of RCMEAS.

1 = The Main Oscillator has been enabled previously and MAINF value is available.

Note: To ensure that a correct value is read on the MAINF bitfield, the MAINFRDY flag must be read at 1 then another read access must be performed on the register to get a stable value on the MAINF bitfield.

## • RCMEAS: RC Oscillator Frequency Measure (write-only)

## 0 = No effect.

1 = Restarts measuring of the main RC frequency. MAINF will carry the new frequency as soon as a low to high transition occurs on the MAINFRDY flag.

The measure is performed on the main frequency (i.e. not limited to RC oscillator only), but if the main clock frequency source is the fast crystal oscillator, the restart of measuring is not needed because of the well known stability of crystal oscillators.

## 25.16.14 PMC Status Register

| Name:    | PMC_SR     |          |     |        |         |         |          |

|----------|------------|----------|-----|--------|---------|---------|----------|

| Address: | 0x400E0468 |          |     |        |         |         |          |

| Access:  | Read-only  |          |     |        |         |         |          |

| 31       | 30         | 29       | 28  | 27     | 26      | 25      | 24       |

| _        | -          | -        | _   | -      | _       | _       | _        |

| 23       | 22         | 21       | 20  | 19     | 18      | 17      | 16       |

| —        | -          | XT32KERR | FOS | CFDS   | CFDEV   | MOSCRCS | MOSCSELS |

| 15       | 14         | 13       | 12  | 11     | 10      | 9       | 8        |

| _        | —          | -        | _   | —      | PCKRDY2 | PCKRDY1 | PCKRDY0  |

| 7        | 6          | 5        | 4   | 3      | 2       | 1       | 0        |

| OSCSELS  | -          | -        | _   | MCKRDY | _       | LOCKA   | MOSCXTS  |

## MOSCXTS: Main XTAL Oscillator Status

0 = Main XTAL oscillator is not stabilized.

1 = Main XTAL oscillator is stabilized.

## LOCKA: PLLA Lock Status

- 0 = PLLA is not locked

- 1 = PLLA is locked.

## MCKRDY: Master Clock Status

- 0 = Master Clock is not ready.

- 1 = Master Clock is ready.

### OSCSELS: Slow Clock Oscillator Selection

- 0 = Internal slow clock RC oscillator is selected.

- 1 = External slow clock 32 kHz oscillator is selected.

### PCKRDYx: Programmable Clock Ready Status

- 0 = Programmable Clock x is not ready.

- 1 = Programmable Clock x is ready.

## • MOSCSELS: Main Oscillator Selection Status

- 0 = Selection is in progress.

- 1 = Selection is done.

### MOSCRCS: Main On-Chip RC Oscillator Status

- 0 = Main on-chip RC oscillator is not stabilized.

- 1 = Main on-chip RC oscillator is stabilized.

## CFDEV: Clock Failure Detector Event

- 0 = No clock failure detection of the main on-chip RC oscillator clock has occurred since the last read of PMC\_SR.

- 1 = At least one clock failure detection of the main on-chip RC oscillator clock has occurred since the last read of PMC\_SR.

These Additional Modes are:

- Rising Edge Detection

- Falling Edge Detection

- Low Level Detection

- High Level Detection

In order to select an Additional Interrupt Mode:

- The type of event detection (Edge or Level) must be selected by writing in the set of registers; PIO\_ESR (Edge Select Register) and PIO\_LSR (Level Select Register) which enable respectively, the Edge and Level Detection. The current status of this selection is accessible through the PIO\_ELSR (Edge/Level Status Register).

- The Polarity of the event detection (Rising/Falling Edge or High/Low Level) must be selected by writing in the set of registers; PIO\_FELLSR (Falling Edge /Low Level Select Register) and PIO\_REHLSR (Rising Edge/High Level Select Register) which allow to select Falling or Rising Edge (if Edge is selected in the PIO\_ELSR) Edge or High or Low Level Detection (if Level is selected in the PIO\_ELSR). The current status of this selection is accessible through the PIO\_FRLHSR (Fall/Rise - Low/High Status Register).

When an input Edge or Level is detected on an I/O line, the corresponding bit in PIO\_ISR (Interrupt Status Register) is set. If the corresponding bit in PIO\_IMR is set, the PIO Controller interrupt line is asserted. The interrupt signals of the thirty-two channels are ORed-wired together to generate a single interrupt signal to the interrupt controller.

When the software reads PIO\_ISR, all the interrupts are automatically cleared. This signifies that all the interrupts that are pending when PIO\_ISR is read must be handled. When an Interrupt is enabled on a "Level", the interrupt is generated as long as the interrupt source is not cleared, even if some read accesses in PIO\_ISR are performed.

## 27.7.9 PIO Input Filter Status Register

Name: PIO\_IFSR

Address: 0x400E0E28 (PIOA), 0x400E1028 (PIOB), 0x400E1228 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Input Filer Status

0: The input glitch filter is disabled on the I/O line.

1: The input glitch filter is enabled on the I/O line.

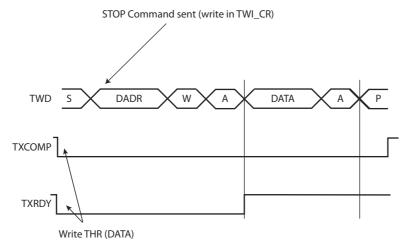

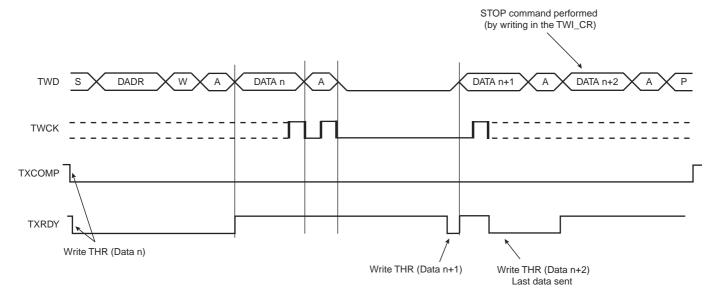

After a Master Write transfer, the Serial Clock line is stretched (tied low) while no new data is written in the TWI\_THR or until a STOP command is performed.

See Figure 29-6, Figure 29-7, and Figure 29-8.

### Figure 29-6. Master Write with One Data Byte

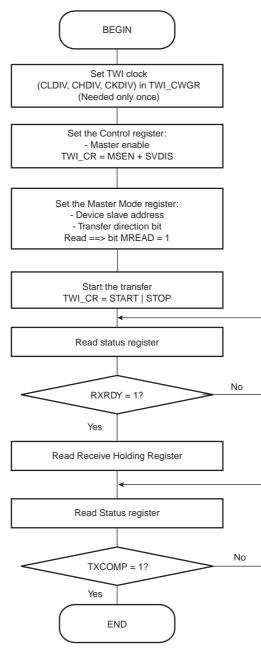

Figure 29-18. TWI Read Operation with Single Data Byte without Internal Address

### 31.7.7.2 Baud Rate

In SPI Mode, the baudrate generator operates in the same way as in USART synchronous mode: See "Baud Rate in Synchronous Mode or SPI Mode" on page 604. However, there are some restrictions:

In SPI Master Mode:

- The external clock SCK must not be selected (USCLKS ≠ 0x3), and the bit CLKO must be set to "1" in the Mode Register (US\_MR), in order to generate correctly the serial clock on the SCK pin.

- To obtain correct behavior of the receiver and the transmitter, the value programmed in CD must be superior or equal to 6.

- If the internal clock divided (MCK/DIV) is selected, the value programmed in CD must be even to ensure a 50:50 mark/space ratio on the SCK pin, this value can be odd if the internal clock is selected (MCK).

In SPI Slave Mode:

- The external clock (SCK) selection is forced regardless of the value of the USCLKS field in the Mode Register (US\_MR). Likewise, the value written in US\_BRGR has no effect, because the clock is provided directly by the signal on the USART SCK pin.

- To obtain correct behavior of the receiver and the transmitter, the external clock (SCK) frequency must be at least 6 times lower than the system clock.

### 31.7.7.3 Data Transfer

Up to 9 data bits are successively shifted out on the TXD pin at each rising or falling edge (depending of CPOL and CPHA) of the programmed serial clock. There is no Start bit, no Parity bit and no Stop bit.

The number of data bits is selected by the CHRL field and the MODE 9 bit in the Mode Register (US\_MR). The 9 bits are selected by setting the MODE 9 bit regardless of the CHRL field. The MSB data bit is always sent first in SPI Mode (Master or Slave).

Four combinations of polarity and phase are available for data transfers. The clock polarity is programmed with the CPOL bit in the Mode Register. The clock phase is programmed with the CPHA bit. These two parameters determine the edges of the clock signal upon which data is driven and sampled. Each of the two parameters has two possible states, resulting in four possible combinations that are incompatible with one another. Thus, a master/slave pair must use the same parameter pair values to communicate. If multiple slaves are used and fixed in different configurations, the master must reconfigure itself each time it needs to communicate with a different slave.

| Table 31-14. SPI Bus | Protocol Mode |

|----------------------|---------------|

|----------------------|---------------|

| SPI Bus Protocol Mode | CPOL | СРНА |

|-----------------------|------|------|

| 0                     | 0    | 1    |

| 1                     | 0    | 0    |

| 2                     | 1    | 1    |

| 3                     | 1    | 0    |

## 31.8.15 USART Baud Rate Generator Register

| Name:    | US_BRGR         |                                                |    |    |    |    |    |  |

|----------|-----------------|------------------------------------------------|----|----|----|----|----|--|

| Address: | 0x40024020 (0), | 0x40024020 (0), 0x40028020 (1), 0x4002C020 (2) |    |    |    |    |    |  |

| Access:  | Read-write      |                                                |    |    |    |    |    |  |

| 31       | 30              | 29                                             | 28 | 27 | 26 | 25 | 24 |  |

| -        | -               | -                                              | -  | _  | -  | _  | —  |  |

| 23       | 22              | 21                                             | 20 | 19 | 18 | 17 | 16 |  |

| —        | -               | —                                              | -  | _  |    | FP |    |  |

| 15       | 14              | 13                                             | 12 | 11 | 10 | 9  | 8  |  |

|          |                 |                                                | C  | D  |    |    |    |  |

| 7        | 6               | 5                                              | 4  | 3  | 2  | 1  | 0  |  |

|          |                 |                                                | C  | D  |    |    |    |  |

This register can only be written if the WPEN bit is cleared in "USART Write Protect Mode Register" on page 655.

## • CD: Clock Divider

|            | SYNC = 0<br>CD OVER = 0 OVER = 1      |                                      | SYNC = 1<br>or<br>USART_MODE = SPI<br>(Master or Slave) | USART_MODE =                                   |

|------------|---------------------------------------|--------------------------------------|---------------------------------------------------------|------------------------------------------------|

| CD         |                                       |                                      |                                                         | ISO7816                                        |

| 0          |                                       | Baud Rate                            | Clock Disabled                                          |                                                |

| 1 to 65535 | Baud Rate =<br>Selected Clock/(16*CD) | Baud Rate =<br>Selected Clock/(8*CD) | Baud Rate =<br>Selected Clock /CD                       | Baud Rate = Selected<br>Clock/(FI_DI_RATIO*CD) |

## • FP: Fractional Part

0: Fractional divider is disabled.

1 - 7: Baud rate resolution, defined by FP x 1/8.

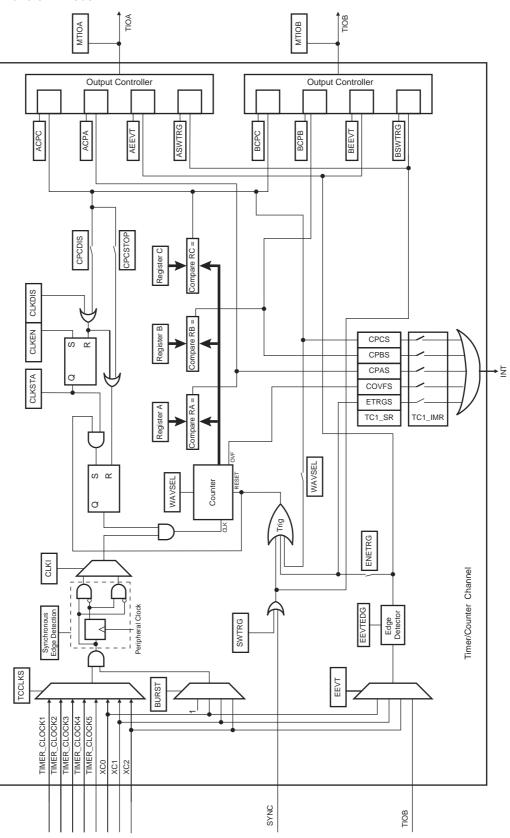

Figure 32-7. Waveform Mode

## 32.7.3 TC Channel Mode Register: Waveform Mode

| Name: | TC_CMRx [x=02] (WAVEFORM_MODE) |

|-------|--------------------------------|

|-------|--------------------------------|

Access: Read/Write

| 31     | 30      | 29   | 28     | 27   | 26 | 25     | 24   |

|--------|---------|------|--------|------|----|--------|------|

| BSV    | VTRG    | BE   | EVT    | BC   | PC | BC     | PB   |

| 23     | 22      | 21   | 20     | 19   | 18 | 17     | 16   |

| ASV    | VTRG    | AE   | EVT    | AC   | PC | AC     | PA   |

| 15     | 14      | 13   | 12     | 11   | 10 | 9      | 8    |

| WAVE   | WAV     | 'SEL | ENETRG | EE   | VT | EEV    | FEDG |

| 7      | 6       | 5    | 4      | 3    | 2  | 1      | 0    |

| CPCDIS | CPCSTOP | BL   | JRST   | CLKI |    | TCCLKS |      |

This register can only be written if the WPEN bit is cleared in the TC Write Protection Mode Register.

## • TCCLKS: Clock Selection

| Value | Name         | Description                                              |

|-------|--------------|----------------------------------------------------------|

| 0     | TIMER_CLOCK1 | Clock selected: internal MCK/2 clock signal (from PMC)   |

| 1     | TIMER_CLOCK2 | Clock selected: internal MCK/8 clock signal (from PMC)   |

| 2     | TIMER_CLOCK3 | Clock selected: internal MCK/32 clock signal (from PMC)  |

| 3     | TIMER_CLOCK4 | Clock selected: internal MCK/128 clock signal (from PMC) |

| 4     | TIMER_CLOCK5 | Clock selected: internal SLCK clock signal (from PMC)    |

| 5     | XC0          | Clock selected: XC0                                      |

| 6     | XC1          | Clock selected: XC1                                      |

| 7     | XC2          | Clock selected: XC2                                      |

## • CLKI: Clock Invert

0: Counter is incremented on rising edge of the clock.

1: Counter is incremented on falling edge of the clock.

## • BURST: Burst Signal Selection

| Value | Name | Description                                   |

|-------|------|-----------------------------------------------|

| 0     | NONE | The clock is not gated by an external signal. |

| 1     | XC0  | XC0 is ANDed with the selected clock.         |

| 2     | XC1  | XC1 is ANDed with the selected clock.         |

| 3     | XC2  | XC2 is ANDed with the selected clock.         |

## • CPCSTOP: Counter Clock Stopped with RC Compare

0: Counter clock is not stopped when counter reaches RC.

1: Counter clock is stopped when counter reaches RC.

## • POSEN: Position Enabled

0: Disable position.

1: Enables the position measure on channel 0 and 1.

### • SPEEDEN: Speed Enabled

0: Disabled.

1: Enables the speed measure on channel 0, the time base being provided by channel 2.

## QDTRANS: Quadrature Decoding Transparent

0: Full quadrature decoding logic is active (direction change detected).

1: Quadrature decoding logic is inactive (direction change inactive) but input filtering and edge detection are performed.

## • EDGPHA: Edge on PHA Count Mode

- 0: Edges are detected on PHA only.

- 1: Edges are detected on both PHA and PHB.

## • INVA: Inverted PHA

0: PHA (TIOA0) is directly driving the QDEC.

1: PHA is inverted before driving the QDEC.

## • INVB: Inverted PHB

0: PHB (TIOB0) is directly driving the QDEC.

1: PHB is inverted before driving the QDEC.

### • INVIDX: Inverted Index

0: IDX (TIOA1) is directly driving the QDEC.

1: IDX is inverted before driving the QDEC.

## • SWAP: Swap PHA and PHB

0: No swap between PHA and PHB.

1: Swap PHA and PHB internally, prior to driving the QDEC.

## • IDXPHB: Index Pin is PHB Pin

0: IDX pin of the rotary sensor must drive TIOA1.

1: IDX pin of the rotary sensor must drive TIOB0.

## • MAXFILT: Maximum Filter

1-63: Defines the filtering capabilities.

Pulses with a period shorter than MAXFILT+1 peripheral clock cycles are discarded.

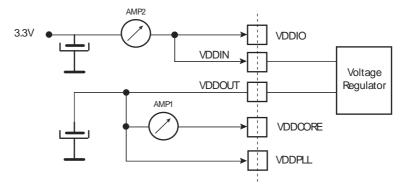

| Symbol                   | Parameter                               | Conditions                                                                                                                                            | Min  | Тур      | Мах       | Unit |

|--------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-----------|------|

| V <sub>DDIN</sub>        | DC Input Voltage Range                  | (4)                                                                                                                                                   | 1.62 | 3.3      | 3.6       | V    |

| V <sub>DDOUT</sub>       | DC Output Voltage                       | Normal Mode<br>Standby Mode                                                                                                                           | 1.08 | 1.2<br>0 | 1.32      | V    |

| V <sub>O(accuracy)</sub> | Output Voltage Accuracy                 | I <sub>Load</sub> = 0.8 mA to 80 mA (after trimming)                                                                                                  | -3   |          | 3         | %    |

| I <sub>LOAD</sub>        | Maximum DC Output Current               | $V_{DDIN} \ge 1.8V$<br>$V_{DDIN} < 1.8V$                                                                                                              |      |          | 120<br>40 | mA   |

| I <sub>LOAD-START</sub>  | Maximum Peak Current during<br>Startup  | (3)                                                                                                                                                   |      | 370      | 400       | mA   |

| V <sub>DROPOUT</sub>     | Dropout Voltage                         | $V_{DDIN} = 1.6V; I_{Load} = Max$                                                                                                                     |      | 400      |           | mV   |

| V <sub>LINE</sub>        | Line Regulation                         | $V_{\text{DDIN}}$ from 2.7V to 3.6V; $I_{\text{Load}}\text{Max}$                                                                                      |      | 10       | 30        | mV   |

| V <sub>LINE-TR</sub>     | Transient Line Regulation               | $V_{DDIN}$ from 2.7V to 3.6V; $t_r = t_f = 5 \ \mu s$ ; $I_{Load}$ Max                                                                                |      | 50       | 150       | mV   |

| V <sub>LOAD</sub>        | Load Regulation                         | $V_{\text{DDIN}} \ge 1.8$ V; I <sub>Load</sub> = 10% to 90% Max                                                                                       |      | 20       | 40        | mV   |

| $V_{LOAD-TR}$            | Transient Load Regulation               | $V_{\text{DDIN}} \! \geq \! 1.8 \text{V}; \; I_{\text{Load}} \! = \! 10\% \text{ to } 90\% \text{ Max}; \\ t_r \! = \! t_f \! = \! 5 \; \mu \text{s}$ |      | 50       | 150       | mV   |

|                          |                                         | Normal Mode; @ I <sub>Load</sub> = 0 mA                                                                                                               |      | 5        |           |      |

| Ι <sub>Q</sub>           | Quiescent Current                       | Normal Mode; @ I <sub>Load</sub> = 80 mA                                                                                                              |      | 500      |           | μA   |

|                          |                                         | Standby Mode                                                                                                                                          |      | 0.02     | 1         | -    |

| CD <sub>IN</sub>         | Input Decoupling Capacitor              | (1)                                                                                                                                                   |      | 4.7      |           | μF   |

| 0.5                      |                                         | (2)                                                                                                                                                   |      | 2.2      |           | μF   |

| CD <sub>OUT</sub>        | Output Decoupling Capacitor             | ESR                                                                                                                                                   | 0.1  |          | 10        | Ω    |

| t <sub>on</sub>          | Turn on Time<br>Standby to Normal Mode  | $CD_{OUT}$ = 2.2 µF, V <sub>DDOUT</sub> reaches 1.2V (± 3%)                                                                                           |      | 300      |           | μs   |

| t <sub>off</sub>         | Turn off Time<br>Normal to Standby Mode | CD <sub>OUT</sub> = 2.2 μF                                                                                                                            |      |          | 40        | ms   |

#### Table 36-3. 1.2V Voltage Regulator Characteristics

Notes: 1. A 4.7 μF or higher ceramic capacitor must be connected between VDDIN and the closest GND pin of the device. This large decoupling capacitor is mandatory to reduce start-up current, improving transient response and noise rejection.

2. To ensure stability, an external 2.2 μF output capacitor, CD<sub>OUT</sub> must be connected between the VDDOUT and the closest GND pin of the device. The ESR (Equivalent Series Resistance) of the capacitor must be in the range 0.1 to 10 Ω. Solid tantalum, and multilayer ceramic capacitors are all suitable as output capacitor. A 100 nF bypass capacitor between VDDOUT and the closest GND pin of the device helps decreasing output noise and improves the load transient response.

3. Defined as the current needed to charge external bypass/decoupling capacitor network.

4. Refer to Section 5.2.2 "VDDIO Versus VDDIN"

## 36.3.2 Sleep and Wait Mode Current Consumption

The Wait mode and Sleep mode configuration and measurements are defined below.

### Figure 36-5. Measurement Setup for Sleep Mode

### 36.3.2.1 Sleep Mode

- Core Clock OFF

- Master Clock (MCK) running at various frequencies with PLLA or the fast RC oscillator

- Fast start-up through pins WKUP0–15

- Current measurement as shown in figure Figure 36-5

- All peripheral clocks deactivated

- T<sub>A</sub> = 25°C

Table 36-10 gives current consumption in typical conditions.

#### Table 36-10. Typical Current Consumption for Sleep Mode

| Conditions                                      | VDDCORE Consumption (AMP1) | Total Consumption (AMP2) | Unit |

|-------------------------------------------------|----------------------------|--------------------------|------|

| Figure 36-5 @ 25 °C MCK = 48 MHz                | 2.41                       | 3.28                     | m ^  |

| There is no activity on the I/Os of the device. | 2.41                       | 3.20                     | mA   |