Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                   |

|----------------------------|----------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                          |

| Core Size                  | 32-Bit Single-Core                                       |

| Speed                      | 100MHz                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT               |

| Number of I/O              | 79                                                       |

| Program Memory Size        | 512KB (512K x 8)                                         |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | -                                                        |

| RAM Size                   | 64K x 8                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                             |

| Data Converters            | A/D 17x10b; D/A 1x10b                                    |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                        |

| Mounting Type              | Surface Mount                                            |

| Package / Case             | 100-TFBGA                                                |

| Supplier Device Package    | 100-TFBGA (9x9)                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atsam4n8ca-cu |

|                            |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Signals Description

Table 3-1 gives details on signal names classified by peripheral.

| Signal Name    | Function                                       | Туре        | Active<br>Level | Voltage<br>Reference | Comments                                            |  |  |  |  |  |

|----------------|------------------------------------------------|-------------|-----------------|----------------------|-----------------------------------------------------|--|--|--|--|--|

| Power Supplies |                                                |             |                 |                      |                                                     |  |  |  |  |  |

| VDDIO          | Peripherals I/O Lines Power Supply             | Power       |                 |                      | 1.62V to 3.6V                                       |  |  |  |  |  |

| VDDIN          | Voltage Regulator, ADC and DAC Power<br>Supply | Power       |                 |                      | 1.6V to 3.6V                                        |  |  |  |  |  |

| VDDOUT         | Voltage Regulator Output                       | Power       |                 |                      | 1.2V Output                                         |  |  |  |  |  |

| VDDPLL         | Oscillator Power Supply                        | Power       |                 |                      | 1.08V to 1.32V                                      |  |  |  |  |  |

| VDDCORE        | Core Chip Power Supply                         | Power       |                 |                      | 1.08V to 1.32V<br>Connected externally to<br>VDDOUT |  |  |  |  |  |

| GND            | Ground                                         | Ground      |                 |                      |                                                     |  |  |  |  |  |

|                | Clocks, Oscillat                               | ors and PL  | Ls              |                      |                                                     |  |  |  |  |  |

| XIN            | Main Oscillator Input                          | Input       |                 | VDDIO                |                                                     |  |  |  |  |  |

| XOUT           | Main Oscillator Output                         | Output      |                 |                      |                                                     |  |  |  |  |  |

| XIN32          | Slow Clock Oscillator Input                    | Input       |                 | VDDIO                |                                                     |  |  |  |  |  |

| XOUT32         | Slow Clock Oscillator Output                   | Output      |                 |                      |                                                     |  |  |  |  |  |

| PCK0–PCK2      | Programmable Clock Output                      | Output      |                 |                      |                                                     |  |  |  |  |  |

|                | ICE and                                        | JTAG        |                 |                      |                                                     |  |  |  |  |  |

| ТСК            | Test Clock                                     | Input       |                 | VDDIO                | No pull-up resistor                                 |  |  |  |  |  |

| TDI            | Test Data In                                   | Input       |                 | VDDIO                | No pull-up resistor                                 |  |  |  |  |  |

| TDO            | Test Data Out                                  | Output      |                 | VDDIO                |                                                     |  |  |  |  |  |

| TRACESWO       | Trace Asynchronous Data Out                    | Output      |                 | VDDIO                |                                                     |  |  |  |  |  |

| SWDIO          | Serial Wire Input/Output                       | I/O         |                 | VDDIO                |                                                     |  |  |  |  |  |

| SWCLK          | Serial Wire Clock                              | Input       |                 | VDDIO                |                                                     |  |  |  |  |  |

| TMS            | Test Mode Select                               | Input       |                 | VDDIO                | No pull-up resistor                                 |  |  |  |  |  |

| JTAGSEL        | JTAG Selection                                 | Input       | High            | VDDIO                | Pull-down resistor                                  |  |  |  |  |  |

|                | Flash Me                                       | emory       |                 |                      |                                                     |  |  |  |  |  |

| ERASE          | Flash and NVM Configuration Bits Erase Command | Input       | High            | VDDIO                | Pull-down (15 k $\Omega$ ) resistor                 |  |  |  |  |  |

|                | Reset/                                         | Test        |                 |                      |                                                     |  |  |  |  |  |

| NRST           | Microcontroller Reset                          | I/O         | Low             | VDDIO                | Pull-up resistor                                    |  |  |  |  |  |

| TST            | Test Mode Select                               | Input       |                 | VDDIO                | Pull-down resistor                                  |  |  |  |  |  |

|                | Universal Asynchronous Rec                     | eiver Trans | smitter - L     | JARTx                |                                                     |  |  |  |  |  |

| URXDx          | UART Receive Data                              | Input       |                 |                      |                                                     |  |  |  |  |  |

| UTXDx          | UART Transmit Data                             | Output      |                 |                      |                                                     |  |  |  |  |  |

#### 11.4.1.4 General-purpose Registers

R0-R12 are 32-bit general-purpose registers for data operations.

#### 11.4.1.5 Stack Pointer

The *Stack Pointer* (SP) is register R13. In Thread mode, bit[1] of the CONTROL register indicates the stack pointer to use:

- 0 = Main Stack Pointer (MSP). This is the reset value.

- 1 = Process Stack Pointer (PSP).

On reset, the processor loads the MSP with the value from address 0x00000000.

## 11.4.1.6 Link Register

The *Link Register* (LR) is register R14. It stores the return information for subroutines, function calls, and exceptions. On reset, the processor loads the LR value 0xFFFFFFF.

### 11.4.1.7 Program Counter

The *Program Counter* (PC) is register R15. It contains the current program address. On reset, the processor loads the PC with the value of the reset vector, which is at address 0x00000004. Bit[0] of the value is loaded into the EPSR T-bit at reset and must be 1.

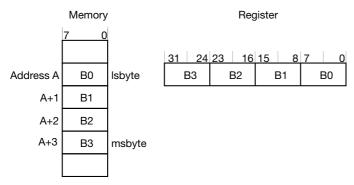

Figure 11-6. *Little-endian Format*

### 11.4.2.7 Synchronization Primitives

The Cortex-M4 instruction set includes pairs of *synchronization primitives*. These provide a non-blocking mechanism that a thread or process can use to obtain exclusive access to a memory location. The software can use them to perform a guaranteed read-modify-write memory update sequence, or for a semaphore mechanism.

A pair of synchronization primitives comprises:

A Load-exclusive Instruction, used to read the value of a memory location, requesting exclusive access to that location.

A Store-Exclusive instruction, used to attempt to write to the same memory location, returning a status bit to a register. If this bit is:

- 0: It indicates that the thread or process gained exclusive access to the memory, and the write succeeds,

- 1: It indicates that the thread or process did not gain exclusive access to the memory, and no write is performed.

The pairs of Load-Exclusive and Store-Exclusive instructions are:

- The word instructions LDREX and STREX

- The halfword instructions LDREXH and STREXH

- The byte instructions LDREXB and STREXB.

The software must use a Load-Exclusive instruction with the corresponding Store-Exclusive instruction.

To perform an exclusive read-modify-write of a memory location, the software must:

- 1. Use a Load-Exclusive instruction to read the value of the location.

- 2. Update the value, as required.

- 3. Use a Store-Exclusive instruction to attempt to write the new value back to the memory location

- 4. Test the returned status bit. If this bit is:

0: The read-modify-write completed successfully.

1: No write was performed. This indicates that the value returned at step 1 might be out of date. The software must retry the read-modify-write sequence.

The software can use the synchronization primitives to implement a semaphore as follows:

- 1. Use a Load-Exclusive instruction to read from the semaphore address to check whether the semaphore is free.

- 2. If the semaphore is free, use a Store-Exclusive instruction to write the claim value to the semaphore address.

- 3. If the returned status bit from step 2 indicates that the Store-Exclusive instruction succeeded then the software has claimed the semaphore. However, if the Store-Exclusive instruction failed, another process might have claimed the semaphore after the software performed the first step.

## 11.6.4.6 LDM and STM

Load and Store Multiple registers.

Syntax

op{addr\_mode}{cond} Rn{!}, reglist

where:

op

is one of:

LDM Load Multiple registers.

STM Store Multiple registers.

addr\_mode is any one of the following:

IA Increment address After each access. This is the default.

DB Decrement address Before each access.

cond is an optional condition code, see "Conditional Execution".

Rn is the register on which the memory addresses are based.

! is an optional writeback suffix.

If ! is present, the final address, that is loaded from or stored to, is written back into Rn.

reglist is a list of one or more registers to be loaded or stored, enclosed in braces. It can contain register ranges. It must be comma separated if it contains more than one register or register range, see "Examples".

LDM and LDMFD are synonyms for LDMIA. LDMFD refers to its use for popping data from Full Descending stacks.

LDMEA is a synonym for LDMDB, and refers to its use for popping data from Empty Ascending stacks.

STM and STMEA are synonyms for STMIA. STMEA refers to its use for pushing data onto Empty Ascending stacks.

STMFD is s synonym for STMDB, and refers to its use for pushing data onto Full Descending stacks

Operation

LDM instructions load the registers in reglist with word values from memory addresses based on Rn.

STM instructions store the word values in the registers in reglist to memory addresses based on Rn.

For LDM, LDMIA, LDMFD, STM, STMIA, and STMEA the memory addresses used for the accesses are at 4-byte intervals ranging from Rn to Rn + 4 \* (n-1), where n is the number of registers in *reglist*. The accesses happens in order of increasing register numbers, with the lowest numbered register using the lowest memory address and the highest number register using the highest memory address. If the writeback suffix is specified, the value of Rn + 4 \* (n-1) is written back to Rn.

For LDMDB, LDMEA, STMDB, and STMFD the memory addresses used for the accesses are at 4-byte intervals ranging from Rn to Rn - 4 \* (n-1), where n is the number of registers in *reglist*. The accesses happen in order of decreasing register numbers, with the highest numbered register using the highest memory address and the lowest number register using the lowest memory address. If the writeback suffix is specified, the value of Rn - 4 \* (n-1) is written back to Rn.

The PUSH and POP instructions can be expressed in this form. See "PUSH and POP" for details.

Restrictions

In these instructions:

- Rn must not be PC

- reglist must not contain SP

- In any STM instruction, *reglist* must not contain PC

#### 11.6.5.17 UASX and USAX

Add and Subtract with Exchange and Subtract and Add with Exchange.

Syntax

$op\{cond\}$  {Rd}, Rn, Rm

where:

| ор     | is one of:                                                   |

|--------|--------------------------------------------------------------|

|        | UASX Add and Subtract with Exchange.                         |

|        | USAX Subtract and Add with Exchange.                         |

| cond   | is an optional condition code, see "Conditional Execution" . |

| Rd     | is the destination register.                                 |

| Rn, Rm | are registers holding the first and second operands.         |

Operation

The UASX instruction:

- 1. Subtracts the top halfword of the second operand from the bottom halfword of the first operand.

- 2. Writes the unsigned result from the subtraction to the bottom halfword of the destination register.

- 3. Adds the top halfword of the first operand with the bottom halfword of the second operand.

- 4. Writes the unsigned result of the addition to the top halfword of the destination register.

The USAX instruction:

- 1. Adds the bottom halfword of the first operand with the top halfword of the second operand.

- 2. Writes the unsigned result of the addition to the bottom halfword of the destination register.

- 3. Subtracts the bottom halfword of the second operand from the top halfword of the first operand.

- 4. Writes the unsigned result from the subtraction to the top halfword of the destination register.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not affect the condition code flags.

#### Examples

| UASX | R0, R4 | , R5 | ; | Adds top halfword of R4 to bottom halfword of R5 and    |

|------|--------|------|---|---------------------------------------------------------|

|      |        |      | ; | writes to top halfword of R0                            |

|      |        |      | ; | Subtracts bottom halfword of R5 from top halfword of R0 |

|      |        |      | ; | and writes to bottom halfword of R0                     |

| USAX | R7, R3 | , R2 | ; | Subtracts top halfword of R2 from bottom halfword of R3 |

|      |        |      | ; | and writes to bottom halfword of R7                     |

|      |        |      | ; | Adds top halfword of R3 to bottom halfword of R2 and    |

|      |        |      | ; | writes to top halfword of R7.                           |

#### 11.6.8.3 SXTA and UXTA

Signed and Unsigned Extend and Add

Syntax

op{cond} {Rd,} Rn, Rm {, ROR #n}

op{cond} {Rd,} Rn, Rm {, ROR #n}

where:

| 00     | is one of:                                                          |

|--------|---------------------------------------------------------------------|

| ор     |                                                                     |

|        | SXTAB Sign extends an 8-bit value to a 32-bit value and add.        |

|        | SXTAH Sign extends a 16-bit value to a 32-bit value and add.        |

|        | SXTAB16 Sign extends two 8-bit values to two 16-bit values and add. |

|        | UXTAB Zero extends an 8-bit value to a 32-bit value and add.        |

|        | UXTAH Zero extends a 16-bit value to a 32-bit value and add.        |

|        | UXTAB16 Zero extends two 8-bit values to two 16-bit values and add. |

| cond   | is an optional condition code, see "Conditional Execution" .        |

| Rd     | is the destination register.                                        |

| Rn     | is the first operand register.                                      |

| Rm     | is the register holding the value to rotate and extend.             |

| ROR #n | is one of:                                                          |

|        | ROR #8 Value from <i>Rm</i> is rotated right 8 bits.                |

|        | ROR #16 Value from Rm is rotated right 16 bits.                     |

ROR #24 Value from Rm is rotated right 24 bits.

If ROR #*n* is omitted, no rotation is performed.

#### Operation

These instructions do the following:

- 1. Rotate the value from *Rm* right by 0, 8, 16 or 24 bits.

- 2. Extract bits from the resulting value:

- SXTAB extracts bits[7:0] from *Rm* and sign extends to 32 bits.

- UXTAB extracts bits[7:0] from *Rm* and zero extends to 32 bits.

- SXTAH extracts bits[15:0] from *Rm* and sign extends to 32 bits.

- UXTAH extracts bits[15:0] from *Rm* and zero extends to 32 bits.

- SXTAB16 extracts bits[7:0] from *Rm* and sign extends to 16 bits, and extracts bits [23:16] from *Rm* and sign extends to 16 bits.

- UXTAB16 extracts bits[7:0] from *Rm* and zero extends to 16 bits, and extracts bits [23:16] from *Rm* and zero extends to 16 bits.

- 3. Adds the signed or zero extended value to the word or corresponding halfword of *Rn* and writes the result in *Rd*.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not affect the flags.

Examples

#### 11.6.11.9 SEV

Send Event.

Syntax

$SEV{cond}$

where:

cond is an optional condition code, see "Conditional Execution".

## Operation

SEV is a hint instruction that causes an event to be signaled to all processors within a multiprocessor system. It also sets the local event register to 1, see "Power Management".

### **Condition Flags**

This instruction does not change the flags.

### Examples

SEV ; Send Event

## 11.11.1 MPU Access Permission Attributes

This section describes the MPU access permission attributes. The access permission bits (TEX, C, B, S, AP, and XN) of the MPU\_RASR control the access to the corresponding memory region. If an access is made to an area of memory without the required permissions, then the MPU generates a permission fault.

The table below shows the encodings for the TEX, C, B, and S access permission bits.

|      |      | ,                | -, -,            | and 5 Encounty                     |                  |                                                      |

|------|------|------------------|------------------|------------------------------------|------------------|------------------------------------------------------|

| TEX  | С    | В                | S                | Memory Type                        | Shareability     | Other Attributes                                     |

|      | 0    | 0                | x <sup>(1)</sup> | Strongly-<br>ordered               | Shareable        | -                                                    |

|      |      | 1                | x <sup>(1)</sup> | Device                             | Shareable        | -                                                    |

| b000 |      | 0                | 0                | Normal                             | Not<br>shareable | Outer and inner write-through. No write allocate.    |

|      |      |                  | 1                |                                    | Shareable        | white anocate.                                       |

|      | 1    | 1                | 0                | Normal                             | Not<br>shareable | Outer and inner write-back. No write allocate.       |

|      |      |                  | 1                |                                    | Shareable        | anocate.                                             |

|      | 0    | ) 0              | 0                | Normal                             | Not<br>shareable |                                                      |

|      |      |                  | 1                |                                    | Shareable        |                                                      |

|      |      | 1                | x <sup>(1)</sup> | Reserved encoding                  |                  | -                                                    |

| b001 |      | 0                | x <sup>(1)</sup> | Implementation defined attributes. |                  | -                                                    |

|      | 1    | 1                | 0                | Normal                             | Not<br>shareable | Outer and inner write-back. Write and read allocate. |

|      |      |                  | 1                |                                    | Shareable        | Teau anocate.                                        |

|      | 0    | 0                | x <sup>(1)</sup> | Device                             | Not<br>shareable | Nonshared Device.                                    |

| b010 | b010 |                  | x <sup>(1)</sup> | Reserved encodi                    | ng               | -                                                    |

|      | 1    | x <sup>(1)</sup> | x <sup>(1)</sup> | Reserved encoding                  |                  | -                                                    |

| b1B  | A    | A                | 0                | Normal                             | Not<br>shareable |                                                      |

|      | В    |                  | 1                |                                    | Shareable        |                                                      |

Table 11-36. TEX, C, B, and S Encoding

Note: 1. The MPU ignores the value of this bit.

Table 11-37 shows the cache policy for memory attribute encodings with a TEX value is in the range 4-7.

Table 11-37. Cache Policy for Memory Attribute Encoding

| Encoding, AA or BB | Corresponding Cache Policy          |  |  |  |  |

|--------------------|-------------------------------------|--|--|--|--|

| 00                 | Non-cacheable                       |  |  |  |  |

| 01                 | Write back, write and read allocate |  |  |  |  |

| 10                 | Write through, no write allocate    |  |  |  |  |

| 11                 | Write back, no write allocate       |  |  |  |  |

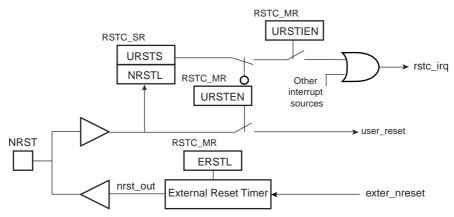

## 13.4 Functional Description

## 13.4.1 Reset Controller Overview

The Reset Controller is made up of an NRST Manager and a Reset State Manager. It runs at Slow Clock and generates the following reset signals:

- proc\_nreset: Processor reset line. It also resets the Watchdog Timer

- periph\_nreset: Affects the whole set of embedded peripherals

- nrst\_out: Drives the NRST pin

These reset signals are asserted by the Reset Controller, either on external events or on software action. The Reset State Manager controls the generation of reset signals and provides a signal to the NRST Manager when an assertion of the NRST pin is required.

The NRST Manager shapes the NRST assertion during a programmable time, thus controlling external device resets.

The Reset Controller Mode Register (RSTC\_MR), allowing the configuration of the Reset Controller, is powered with VDDIO, so that its configuration is saved as long as VDDIO is on.

#### 13.4.2 NRST Manager

After power-up, NRST is an output during the ERSTL time period defined in the RSTC\_MR. When ERSTL has elapsed, the pin behaves as an input and all the system is held in reset if NRST is tied to GND by an external signal.

The NRST Manager samples the NRST input pin and drives this pin low when required by the Reset State Manager. Figure 13-2 shows the block diagram of the NRST Manager.

#### Figure 13-2. NRST Manager

#### 13.4.2.1 NRST Signal or Interrupt

The NRST Manager samples the NRST pin at Slow Clock speed. When the line is detected low, a User Reset is reported to the Reset State Manager.

However, the NRST Manager can be programmed to not trigger a reset when an assertion of NRST occurs. Writing the bit URSTEN at 0 in RSTC\_MR disables the User Reset trigger.

The level of the pin NRST can be read at any time in the bit NRSTL (NRST level) in RSTC\_SR. As soon as the pin NRST is asserted, the bit URSTS in RSTC\_SR is set. This bit clears only when RSTC\_SR is read.

The Reset Controller can also be programmed to generate an interrupt instead of generating a reset. To do so, the bit URSTIEN in RSTC\_MR must be written at 1.

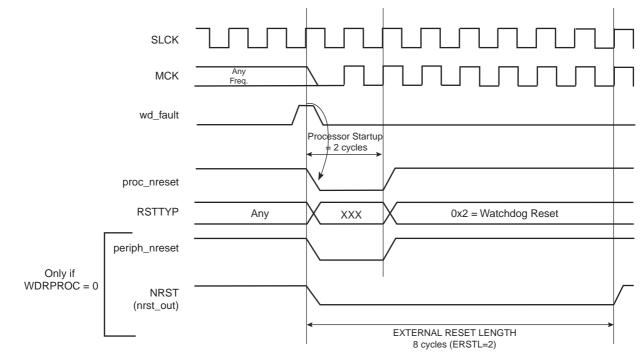

#### 13.4.4.5 Watchdog Reset

The Watchdog Reset is entered when a watchdog fault occurs. This state lasts 3 Slow Clock cycles.

When in Watchdog Reset, assertion of the reset signals depends on the WDRPROC bit in WDT\_MR:

- If WDRPROC is 0, the Processor Reset and the Peripheral Reset are asserted. The NRST line is also asserted, depending on the programming of the field ERSTL. However, the resulting low level on NRST does not result in a User Reset state.

- If WDRPROC = 1, only the processor reset is asserted.

The Watchdog Timer is reset by the proc\_nreset signal. As the watchdog fault always causes a processor reset if WDRSTEN is set, the Watchdog Timer is always reset after a Watchdog Reset, and the Watchdog is enabled by default and with a period set to a maximum.

When the WDRSTEN in WDT\_MR bit is reset, the watchdog fault has no impact on the reset controller.

#### Figure 13-6. Watchdog Reset

## 15.6.9 RTC Interrupt Enable Register

| Name:    | RTC_IER    |         |       |       |       |       |       |

|----------|------------|---------|-------|-------|-------|-------|-------|

| Address: | 0x400E1480 |         |       |       |       |       |       |

| Access:  | Write-only |         |       |       |       |       |       |

| 31       | 30         | 29      | 28    | 27    | 26    | 25    | 24    |

| _        | -          | -       | _     | _     | _     | _     | _     |

| 23       | 22         | 21      | 20    | 19    | 18    | 17    | 16    |

| _        | -          | _       | _     | -     | -     | -     | -     |

| 15       | 14         | 13      | 12    | 11    | 10    | 9     | 8     |

| _        | -          | _       | _     | _     | _     | _     | _     |

| 7        | 6          | 5       | 4     | 3     | 2     | 1     | 0     |

| _        | _          | TDERREN | CALEN | TIMEN | SECEN | ALREN | ACKEN |

### • ACKEN: Acknowledge Update Interrupt Enable

0 = No effect.

1 = The acknowledge for update interrupt is enabled.

## • ALREN: Alarm Interrupt Enable

0 = No effect.

1 = The alarm interrupt is enabled.

## • SECEN: Second Event Interrupt Enable

0 = No effect.

1 = The second periodic interrupt is enabled.

## • TIMEN: Time Event Interrupt Enable

0 = No effect.

1 = The selected time event interrupt is enabled.

## • CALEN: Calendar Event Interrupt Enable

0 = No effect.

1 = The selected calendar event interrupt is enabled.

## • TDERREN: Time and/or Date Error Interrupt Enable

- 0 = No effect.

- 1 = The time and date error interrupt is enabled.

# 18.3 General Purpose Backup Registers (GPBR) User Interface

| Offset | Register                          | Name      | Access     | Reset |

|--------|-----------------------------------|-----------|------------|-------|

| 0x0    | General Purpose Backup Register 0 | SYS_GPBR0 | Read-write | _     |

|        |                                   |           |            |       |

| 0x1C   | General Purpose Backup Register 7 | SYS_GPBR7 | Read-write | _     |

## Table 18-1. Register Mapping

When DLYBCT equals zero, no delay between consecutive transfers is inserted and the clock keeps its duty cycle over the character transfers.

Otherwise, the following equation determines the delay:

Delay Between Consecutive Transfers =  $\frac{32 \times DLYBCT}{MCK}$

#### 29.8.7.1 Data Transmit with the PDC

- 1. Initialize the transmit PDC (memory pointers, transfer size 1).

- 2. Configure the master (DADR, CKDIV, etc.) or slave mode.

- 3. Start the transfer by setting the PDC TXTEN bit.

- 4. Wait for the PDC ENDTX Flag either by using the polling method or ENDTX interrupt.

- 5. Disable the PDC by setting the PDC TXTDIS bit.

- 6. Wait for the TXRDY flag in TWI\_SR register

- 7. Set the STOP command in TWI\_CR.

- 8. Write the last character in TWI\_THR

- 9. (Optional) Wait for the TXCOMP flag in TWI\_SR register before disabling the peripheral clock if required

## 29.8.7.2 Data Receive with the PDC

The PDC transfer size must be defined with the buffer size minus 2. The two remaining characters must be managed without PDC to ensure that the exact number of bytes are received whatever the system bus latency conditions encountered during the end of buffer transfer period.

In slave mode, the number of characters to receive must be known in order to configure the PDC.

- 1. Initialize the receive PDC (memory pointers, transfer size 2).

- 2. Configure the master (DADR, CKDIV, etc.) or slave mode.

- 3. Set the PDC RXTEN bit.

- 4. (Master Only) Write the START bit in the TWI\_CR register to start the transfer

- 5. Wait for the PDC ENDRX Flag either by using polling method or ENDRX interrupt.

- 6. Disable the PDC by setting the PDC RXTDIS bit.

- 7. Wait for the RXRDY flag in TWI\_SR register

- 8. Set the STOP command in TWI\_CR

- 9. Read the penultimate character in TWI\_RHR

- 10. Wait for the RXRDY flag in TWI\_SR register

- 11. Read the last character in TWI\_RHR

- 12. (Optional) Wait for the TXCOMP flag in TWI\_SR register before disabling the peripheral clock if required

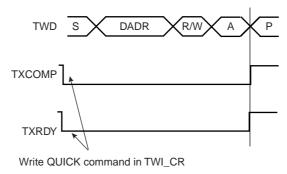

## 29.8.8 SMBUS Quick Command (Master Mode Only)

The TWI interface can perform a Quick Command:

- 1. Configure the master mode (DADR, CKDIV, etc.).

- 2. Write the MREAD bit in the TWI\_MMR register at the value of the one-bit command to be sent.

- 3. Start the transfer by setting the QUICK bit in the TWI\_CR.

## Figure 29-14. SMBUS Quick Command

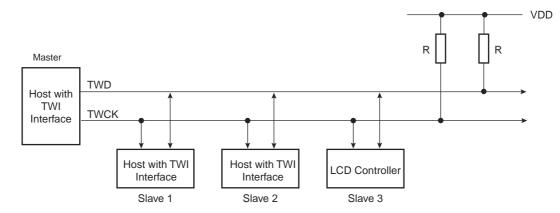

## 29.10 Slave Mode

### 29.10.1 Definition

The Slave Mode is defined as a mode where the device receives the clock and the address from another device called the master.

In this mode, the device never initiates and never completes the transmission (START, REPEATED\_START and STOP conditions are always provided by the master).

#### 29.10.2 Application Block Diagram

#### Figure 29-24. Slave Mode Typical Application Block Diagram

#### 29.10.3 Programming Slave Mode

The following fields must be programmed before entering Slave mode:

- 1. SADR (TWI\_SMR): The slave device address is used in order to be accessed by master devices in read or write mode.

- 2. MSDIS (TWI\_CR): Disable the master mode.

- 3. SVEN (TWI\_CR): Enable the slave mode.

As the device receives the clock, values written in TWI\_CWGR are not taken into account.

#### 29.10.4 Receiving Data

After a Start or Repeated Start condition is detected and if the address sent by the Master matches with the Slave address programmed in the SADR (Slave ADdress) field, SVACC (Slave ACCess) flag is set and SVREAD (Slave READ) indicates the direction of the transfer.

SVACC remains high until a STOP condition or a repeated START is detected. When such a condition is detected, EOSACC (End Of Slave ACCess) flag is set.

#### 29.10.4.1Read Sequence

In the case of a Read sequence (SVREAD is high), TWI transfers data written in the TWI\_THR (TWI Transmit Holding Register) until a STOP condition or a REPEATED\_START + an address different from SADR is detected. Note that at the end of the read sequence TXCOMP (Transmission Complete) flag is set and SVACC reset.

As soon as data is written in the TWI\_THR, TXRDY (Transmit Holding Register Ready) flag is reset, and it is set when the shift register is empty and the sent data acknowledged or not. If the data is not acknowledged, the NACK flag is set.

Note that a STOP or a repeated START always follows a NACK.

See Figure 29-25 on page 556.

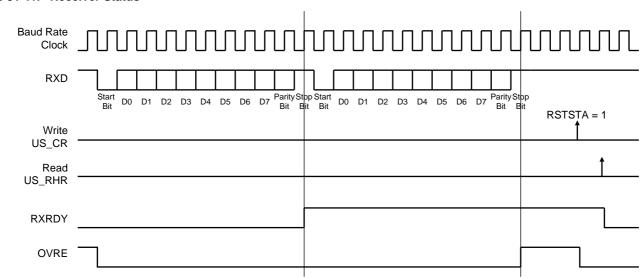

#### 31.7.3.4 Receiver Operations

When a character reception is completed, it is transferred to the Receive Holding Register (US\_RHR) and the RXRDY bit in the Status Register (US\_CSR) rises. If a character is completed while the RXRDY is set, the OVRE (Overrun Error) bit is set. The last character is transferred into US\_RHR and overwrites the previous one. The OVRE bit is cleared by writing the Control Register (US\_CR) with the RSTSTA (Reset Status) bit to 1.

#### Figure 31-11. Receiver Status

#### 31.7.3.5 Parity

The USART supports five parity modes selected by programming the PAR field in the Mode Register (US\_MR). The PAR field also enables the Multidrop mode, see "Multidrop Mode" on page 610. Even and odd parity bit generation and error detection are supported.

If even parity is selected, the parity generator of the transmitter drives the parity bit to 0 if a number of 1s in the character data bit is even, and to 1 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If odd parity is selected, the parity generator of the transmitter drives the parity bit to 1 if a number of 1s in the character data bit is even, and to 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit to 1 if a number of 1s in the character data bit is even, and to 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If the mark parity is used, the parity generator of the transmitter drives the parity bit to 1 for all characters. The receiver parity checker reports an error if the parity bit is sampled to 0. If the space parity checker reports an error if the parity bit is sampled to 1. If parity bit to 0 for all characters. The receiver parity checker reports an error if the parity bit is sampled to 1. If parity is disabled, the transmitter does not generate any parity bit and the receiver does not report any parity error.

Table 31-9 shows an example of the parity bit for the character 0x41 (character ASCII "A") depending on the configuration of the USART. Because there are two bits to 1, 1 bit is added when a parity is odd, or 0 is added when a parity is even.

| Character | Hexa | Binary    | Parity Bit | Parity Mode |  |

|-----------|------|-----------|------------|-------------|--|

| A         | 0x41 | 0100 0001 | 1          | Odd         |  |

| A         | 0x41 | 0100 0001 | 0          | Even        |  |

| А         | 0x41 | 0100 0001 | 1          | Mark        |  |

| А         | 0x41 | 0100 0001 | 0 Space    |             |  |

| A         | 0x41 | 0100 0001 | None       | None        |  |

Table 31-9.Parity Bit Examples

# Atmel

## 31.8.22 USART Write Protect Status Register

| Name:<br>Address: | US_WPSR<br>0x400240E8 (0), 0x400280E8 (1), 0x4002C0E8 (2) |    |     |      |    |    |      |  |  |

|-------------------|-----------------------------------------------------------|----|-----|------|----|----|------|--|--|

| Access:           | Read-only                                                 |    |     |      |    |    |      |  |  |

| Reset:            | See Table 31-15                                           | 5  |     |      |    |    |      |  |  |

| 31                | 30 29 28 27 26 25 24                                      |    |     |      |    |    |      |  |  |

| —                 | —                                                         | —  | —   | —    | —  | —  | —    |  |  |

| 23                | 22                                                        | 21 | 20  | 19   | 18 | 17 | 16   |  |  |

|                   |                                                           |    | WPV | 'SRC |    |    |      |  |  |

| 15                | 14                                                        | 13 | 12  | 11   | 10 | 9  | 8    |  |  |

|                   | WPVSRC                                                    |    |     |      |    |    |      |  |  |

| 7                 | 6                                                         | 5  | 4   | 3    | 2  | 1  | 0    |  |  |

|                   | _                                                         |    |     |      |    |    | WPVS |  |  |

### • WPVS: Write Protect Violation Status

0 = No Write Protect Violation has occurred since the last read of the US\_WPSR register.

1 = A Write Protect Violation has occurred since the last read of the US\_WPSR register. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

### • WPVSRC: Write Protect Violation Source

When WPVS is active, this field indicates the write-protected register (through address offset or code) in which a write access has been attempted.

Note: Reading US\_WPSR automatically clears all fields.

## • ETRGS: External Trigger Status (cleared on read)

0: External trigger has not occurred since the last read of the Status Register.

1: External trigger has occurred since the last read of the Status Register.

## • ENDRX: End of Receiver Transfer (cleared by writing TC\_RCR or TC\_RNCR)

0: The Receive Counter Register has not reached 0 since the last write in TC\_RCR<sup>(1)</sup> or TC\_RNCR<sup>(1)</sup>.

1: The Receive Counter Register has reached 0 since the last write in TC\_RCR or TC\_RNCR.

## • RXBUFF: Reception Buffer Full (cleared by writing TC\_RCR or TC\_RNCR)

0: TC\_RCR or TC\_RNCR have a value other than 0.

1: Both TC\_RCR and TC\_RNCR have a value of 0.

Note: 1. TC\_RCR and TC\_RNCR are PDC registers.

## CLKSTA: Clock Enabling Status

0: Clock is disabled.

1: Clock is enabled.

## • MTIOA: TIOA Mirror

0: TIOA is low. If TC\_CMRx.WAVE = 0, this means that TIOA pin is low. If TC\_CMRx.WAVE = 1, this means that TIOA is driven low.

1: TIOA is high. If TC\_CMRx.WAVE = 0, this means that TIOA pin is high. If TC\_CMRx.WAVE = 1, this means that TIOA is driven high.

## • MTIOB: TIOB Mirror

0: TIOB is low. If TC\_CMRx.WAVE = 0, this means that TIOB pin is low. If TC\_CMRx.WAVE = 1, this means that TIOB is driven low.

1: TIOB is high. If TC\_CMRx.WAVE = 0, this means that TIOB pin is high. If TC\_CMRx.WAVE = 1, this means that TIOB is driven high.

## 34.7.18 ADC Channel Data Register

| Name:    | ADC_CDRx [x=016] |    |    |      |    |    |    |

|----------|------------------|----|----|------|----|----|----|

| Address: | 0x40038050       |    |    |      |    |    |    |

| Access:  | Read-write       |    |    |      |    |    |    |

| 31       | 30               | 29 | 28 | 27   | 26 | 25 | 24 |

| —        | -                | —  | —  | _    | _  | _  | -  |

| 23       | 22               | 21 | 20 | 19   | 18 | 17 | 16 |

| -        | -                | —  | -  | -    | —  | _  | -  |

| 15       | 14               | 13 | 12 | 11   | 10 | 9  | 8  |

| _        | _                | —  | _  | DATA |    |    |    |

| 7        | 6                | 5  | 4  | 3    | 2  | 1  | 0  |

|          |                  |    | DA | ATA  |    |    |    |

## • DATA: Converted Data

The analog-to-digital conversion data is placed into this register at the end of a conversion and remains until a new conversion is completed. The Convert Data Register (CDR) is only loaded if the corresponding analog channel is enabled.

## 34.7.20 ADC Write Protect Mode Register

| Name:    | ADC_WPMR   |    |    |     |    |    |      |

|----------|------------|----|----|-----|----|----|------|

| Address: | 0x400380E4 |    |    |     |    |    |      |

| Access:  | Read-write |    |    |     |    |    |      |

| 31       | 30         | 29 | 28 | 27  | 26 | 25 | 24   |

|          |            |    | WP | KEY |    |    |      |

| 23       | 22         | 21 | 20 | 19  | 18 | 17 | 16   |

|          |            |    | WP | KEY |    |    |      |

| 15       | 14         | 13 | 12 | 11  | 10 | 9  | 8    |

|          |            |    | WP | KEY |    |    |      |

| 7        | 6          | 5  | 4  | 3   | 2  | 1  | 0    |

| -        | -          | -  | -  | —   | -  | —  | WPEN |

## • WPEN: Write Protect Enable

0 = Disables the Write Protect if WPKEY corresponds to 0x414443 ("ADC" in ASCII).

1 = Enables the Write Protect if WPKEY corresponds to 0x414443 ("ADC" in ASCII).

Protects the registers:

- "ADC Mode Register" on page 755

- "ADC Channel Sequence 1 Register" on page 757

- "ADC Channel Sequence 2 Register" on page 758

- "ADC Channel Enable Register" on page 759

- "ADC Channel Disable Register" on page 760

- "ADC Temperature Sensor Mode Register" on page 768

- "ADC Temperature Compare Window Register" on page 769

- "ADC Extended Mode Register" on page 771

- "ADC Compare Window Register" on page 773

- "ADC Analog Control Register" on page 775

#### • WPKEY: Write Protect KEY

| Value    | Name   | Description                                                                                            |

|----------|--------|--------------------------------------------------------------------------------------------------------|

| 0x414443 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit.<br>Always reads as 0 |