#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 100MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 512KB (512K × 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 17x10b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-TFBGA                                                                |

| Supplier Device Package    | 100-TFBGA (9x9)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4n8ca-cur |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 10-1.

Peripheral Identifiers (Continued)

| Instance ID | Instance Name | NVIC<br>Interrupt | PMC<br>Clock Control | Instance Description                   |

|-------------|---------------|-------------------|----------------------|----------------------------------------|

| 29          | ADC           | Х                 | Х                    | Analog-to-Digital Converter            |

| 30          | DACC          | х                 | х                    | Digital-to-Analog Converter Controller |

| 31          | PWM           | х                 | х                    | Pulse Width Modulation                 |

### 11.6.3.8 Instruction Width Selection

There are many instructions that can generate either a 16-bit encoding or a 32-bit encoding depending on the operands and destination register specified. For some of these instructions, the user can force a specific instruction size by using an instruction width suffix. The .W suffix forces a 32-bit instruction encoding. The .N suffix forces a 16-bit instruction encoding.

If the user specifies an instruction width suffix and the assembler cannot generate an instruction encoding of the requested width, it generates an error.

Note: In some cases, it might be necessary to specify the .W suffix, for example if the operand is the label of an instruction or literal data, as in the case of branch instructions. This is because the assembler might not automatically generate the right size encoding.

To use an instruction width suffix, place it immediately after the instruction mnemonic and condition code, if any. The example below shows instructions with the instruction width suffix.

> BCS.W label ; creates a 32-bit instruction even for a short ; branch ADDS.W R0, R0, R1 ; creates a 32-bit instruction even though the same ; operation can be done by a 16-bit instruction

### 11.6.7.6 UQASX and UQSAX

Saturating Add and Subtract with Exchange and Saturating Subtract and Add with Exchange, unsigned. Syntax

```

op\{cond\} {Rd}, Rm, Rn

```

where:

| type   | is one of:                                                   |

|--------|--------------------------------------------------------------|

|        | UQASX Add and Subtract with Exchange and Saturate.           |

|        | UQSAX Subtract and Add with Exchange and Saturate.           |

| cond   | is an optional condition code, see "Conditional Execution" . |

| Rd     | is the destination register.                                 |

| Rn, Rm | are registers holding the first and second operands.         |

Operation

The UQASX instruction:

- 1. Adds the bottom halfword of the source operand with the top halfword of the second operand.

- 2. Subtracts the bottom halfword of the second operand from the top highword of the first operand.

- 3. Saturates the results of the sum and writes a 16-bit unsigned integer in the range  $0 \le x \le 2^{16} 1$ , where *x* equals 16, to the top halfword of the destination register.

- 4. Saturates the result of the subtraction and writes a 16-bit unsigned integer in the range  $0 \le x \le 2^{16} 1$ , where *x* equals 16, to the bottom halfword of the destination register.

The UQSAX instruction:

- 1. Subtracts the bottom halfword of the second operand from the top highword of the first operand.

- 2. Adds the bottom halfword of the first operand with the top halfword of the second operand.

- 3. Saturates the result of the subtraction and writes a 16-bit unsigned integer in the range  $0 \le x \le 2^{16} 1$ , where *x* equals 16, to the top halfword of the destination register.

- 4. Saturates the results of the addition and writes a 16-bit unsigned integer in the range  $0 \le x \le 2^{16} 1$ , where x equals 16, to the bottom halfword of the destination register.

### Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not affect the condition code flags.

### Examples

| UQASX | R7, R4, R2 | ; Adds top halfword of R4 with bottom halfword of R2,       |

|-------|------------|-------------------------------------------------------------|

|       |            | ; saturates to 16 bits, writes to top halfword of R7        |

|       |            | ; Subtracts top halfword of R2 from bottom halfword of      |

|       |            | ; R4, saturates to 16 bits, writes to bottom halfword of R7 |

| UQSAX | R0, R3, R5 | ; Subtracts bottom halfword of R5 from top halfword of R3,  |

|       |            | ; saturates to 16 bits, writes to top halfword of R0        |

|       |            | ; Adds bottom halfword of R4 to top halfword of R5          |

|       |            | ; saturates to 16 bits, writes to bottom halfword of R0.    |

### 11.6.11.2 CPS

Change Processor State.

Syntax

CPSeffect iflags

where:

effect is one of:

IE Clears the special purpose register.

ID Sets the special purpose register.

iflags is a sequence of one or more flags:

- i Set or clear PRIMASK.

- f Set or clear FAULTMASK.

### Operation

CPS changes the PRIMASK and FAULTMASK special register values. See "Exception Mask Registers" for more information about these registers.

### Restrictions

The restrictions are:

- Use CPS only from privileged software, it has no effect if used in unprivileged software

- CPS cannot be conditional and so must not be used inside an IT block.

### **Condition Flags**

This instruction does not change the condition flags.

### Examples

```

CPSID i ; Disable interrupts and configurable fault handlers (set PRIMASK)

CPSID f ; Disable interrupts and all fault handlers (set FAULTMASK)

CPSIE i ; Enable interrupts and configurable fault handlers (clear PRIMASK)

CPSIE f ; Enable interrupts and fault handlers (clear FAULTMASK)

```

| 11.8.3.2 In | terrupt Clear-enable | Registers |     |     |    |    |    |  |  |  |

|-------------|----------------------|-----------|-----|-----|----|----|----|--|--|--|

| Name:       | NVIC_ICERx [x=07]    |           |     |     |    |    |    |  |  |  |

| Access:     | Read-write           |           |     |     |    |    |    |  |  |  |

| Reset:      | 0x000000000          |           |     |     |    |    |    |  |  |  |

| 31          | 30                   | 29        | 28  | 27  | 26 | 25 | 24 |  |  |  |

|             |                      |           | CLR | ENA |    |    |    |  |  |  |

| 23          | 22                   | 21        | 20  | 19  | 18 | 17 | 16 |  |  |  |

|             |                      |           | CLR | ENA |    |    |    |  |  |  |

| 15          | 14                   | 13        | 12  | 11  | 10 | 9  | 8  |  |  |  |

|             | CLRENA               |           |     |     |    |    |    |  |  |  |

| 7           | 6                    | 5         | 4   | 3   | 2  | 1  | 0  |  |  |  |

|             |                      |           | CLR | ENA |    |    |    |  |  |  |

These registers disable interrupts, and show which interrupts are enabled.

## CLRENA: Interrupt Clear-enable

Write:

0: No effect.

1: Disables the interrupt.

Read:

0: Interrupt disabled.

1: Interrupt enabled.

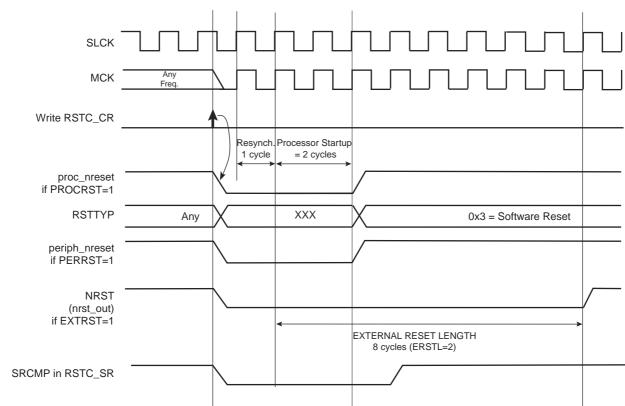

### 13.4.4.4 Software Reset

The Reset Controller offers several commands used to assert the different reset signals. These commands are performed by writing the Control Register (RSTC\_CR) with the following bits at 1:

- PROCRST: Writing PROCRST at 1 resets the processor and the watchdog timer

- PERRST: Writing PERRST at 1 resets all the embedded peripherals including the memory system, and, in particular, the Remap Command. The Peripheral Reset is generally used for debug purposes.

Except for debug purposes, PERRST must always be used in conjunction with PROCRST (PERRST and PROCRST set both at 1 simultaneously).

- EXTRST: Writing EXTRST at 1 asserts low the NRST pin during a time defined by the field ERSTL in the Mode Register (RSTC\_MR).

The software reset is entered if at least one of these bits is set by the software. All these commands can be performed independently or simultaneously. The software reset lasts 3 Slow Clock cycles.

The internal reset signals are asserted as soon as the register write is performed. This is detected on the Master Clock (MCK). They are released when the software reset is left, i.e.; synchronously to SLCK.

If EXTRST is set, the nrst\_out signal is asserted depending on the programming of the field ERSTL. However, the resulting falling edge on NRST does not lead to a User Reset.

If and only if the PROCRST bit is set, the Reset Controller reports the software status in the field RSTTYP of the Status Register (RSTC\_SR). Other Software Resets are not reported in RSTTYP.

As soon as a software operation is detected, the bit SRCMP (Software Reset Command in Progress) is set in the Status Register (RSTC\_SR). It is cleared as soon as the software reset is left. No other software reset can be performed while the SRCMP bit is set, and writing any value in RSTC\_CR has no effect.

### Figure 13-5. Software Reset

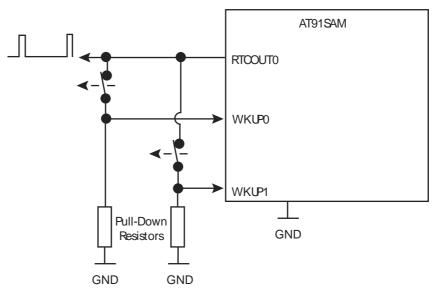

Low Power Debouncer (Push-to-Break switch, pull-down resistors) Figure 17-6.

The debouncing parameters can be adjusted and are shared (except the wake-up input polarity) by both debouncers. The number of successive identical samples to wake up the core can be configured from 2 up to 8 in the LPDBC field of SUPC\_WUMR. The period of time between 2 samples can be configured by programming the TPERIOD field in the RTC\_MR register.

Power parameters can be adjusted by modifying the period of time in the THIGH field in RTC MR.

The wake-up polarity of the inputs can be independently configured by writing WKUPT0 and WKUPT1 fields in SUPC\_WUMR.

In order to determine which wake-up pin triggers the core wake-up or simply which debouncer triggers an event (even if there is no wake-up, so when VDDCORE is powered on), a status flag is associated for each low power debouncer. These 2 flags can be read in the SUPC\_SR.

A debounce event can perform an immediate clear (0 delay) on first half the general purpose backup registers (GPBR). The LPDBCCLR bit must be set to 1 in SUPC\_MR.

Please note that it is not mandatory to use the RTCOUT pins when using the WKUP0/WKUP1 pins as tampering inputs (TMP0/TMP1) in backup mode or any other modes. Using RTCOUT0 pins provides a "sampling mode" to further reduce the power consumption in low power modes. However the RTC must be configured in the same manner as RTCOUT0 is used in order to create a sampling point for the debouncer logic.

Figure 17-7 shows how to use WKUP0/WKUP1 without RTCOUT pins.

# 22. Bus Matrix (MATRIX)

# 22.1 Description

The Bus Matrix implements a multi-layer AHB that enables parallel access paths between multiple AHB masters and slaves in a system, which increases the overall bandwidth. Bus Matrix interconnects 3 AHB Masters to 4 AHB Slaves. The normal latency to connect a master to a slave is one cycle except for the default master of the accessed slave which is connected directly (zero cycle latency).

The Bus Matrix user interface also provides a Chip Configuration User Interface with Registers that allow to support application specific features.

# 22.2 Embedded Characteristics

### 22.2.1 Matrix Masters

The Bus Matrix of the SAM4N product manages 3 masters, which means that each master can perform an access concurrently with others, to an available slave.

Each master has its own decoder, which is defined specifically for each master. In order to simplify the addressing, all the masters have the same decodings.

### Table 22-1. List of Bus Matrix Masters

| Master 0 | Cortex-M4 Instruction/Data      |

|----------|---------------------------------|

| Master 1 | Cortex-M4 System                |

| Master 2 | Peripheral DMA Controller (PDC) |

### 22.2.2 Matrix Slaves

The Bus Matrix of the SAM4N product manages 4 slaves. Each slave has its own arbiter, allowing a different arbitration per slave.

### Table 22-2. List of Bus Matrix Slaves

| Slave 0 | Internal SRAM     |

|---------|-------------------|

| Slave 1 | Internal ROM      |

| Slave 2 | Internal Flash    |

| Slave 3 | Peripheral Bridge |

The following list gives an overview of how status register flags behave depending on the counters' values:

- ENDRX flag is set when the PERIPH\_RCR register reaches zero.

- RXBUFF flag is set when both PERIPH\_RCR and PERIPH\_RNCR reach zero.

- ENDTX flag is set when the PERIPH\_TCR register reaches zero.

- TXBUFE flag is set when both PERIPH\_TCR and PERIPH\_TNCR reach zero.

These status flags are described in the Peripheral Status Register.

### 23.4.4 Data Transfers

The serial peripheral triggers its associated PDC channels' transfers using transmit enable (TXEN) and receive enable (RXEN) flags in the transfer control register integrated in the peripheral's user interface.

When the peripheral receives an external data, it sends a Receive Ready signal to its PDC receive channel which then requests access to the Matrix. When access is granted, the PDC receive channel starts reading the peripheral Receive Holding Register (RHR). The read data are stored in an internal buffer and then written to memory.

When the peripheral is about to send data, it sends a Transmit Ready to its PDC transmit channel which then requests access to the Matrix. When access is granted, the PDC transmit channel reads data from memory and puts them to Transmit Holding Register (THR) of its associated peripheral. The same peripheral sends data according to its mechanism.

### 23.4.5 PDC Flags and Peripheral Status Register

Each peripheral connected to the PDC sends out receive ready and transmit ready flags and the PDC sends back flags to the peripheral. All these flags are only visible in the Peripheral Status Register.

Depending on the type of peripheral, half or full duplex, the flags belong to either one single channel or two different channels.

### 23.4.5.1 Receive Transfer End

This flag is set when PERIPH\_RCR register reaches zero and the last data has been transferred to memory.

It is reset by writing a non zero value in PERIPH\_RCR or PERIPH\_RNCR.

### 23.4.5.2 Transmit Transfer End

This flag is set when PERIPH\_TCR register reaches zero and the last data has been written into peripheral THR. It is reset by writing a non zero value in PERIPH\_TCR or PERIPH\_TNCR.

### 23.4.5.3 Receive Buffer Full

This flag is set when PERIPH\_RCR register reaches zero with PERIPH\_RNCR also set to zero and the last data has been transferred to memory.

It is reset by writing a non zero value in PERIPH\_TCR or PERIPH\_TNCR.

### 23.4.5.4 Transmit Buffer Empty

This flag is set when PERIPH\_TCR register reaches zero with PERIPH\_TNCR also set to zero and the last data has been written into peripheral THR.

It is reset by writing a non zero value in PERIPH\_TCR or PERIPH\_TNCR.

Atmel

| Value | Name | Description |

|-------|------|-------------|

| 13    | 256K | 256 Kbytes  |

| 14    | 96K  | 96 Kbytes   |

| 15    | 512K | 512 Kbytes  |

# • ARCH: Architecture Identifier

| Value | Name         | Description                          |

|-------|--------------|--------------------------------------|

| 0x19  | AT91SAM9xx   | AT91SAM9xx Series                    |

| 0x29  | AT91SAM9XExx | AT91SAM9XExx Series                  |

| 0x34  | AT91x34      | AT91x34 Series                       |

| 0x37  | CAP7         | CAP7 Series                          |

| 0x39  | CAP9         | CAP9 Series                          |

| 0x3B  | CAP11        | CAP11 Series                         |

| 0x40  | AT91x40      | AT91x40 Series                       |

| 0x42  | AT91x42      | AT91x42 Series                       |

| 0x45  | AT91SAM4SH2  | AT91SAM4SH2 Series                   |

| 0x55  | AT91x55      | AT91x55 Series                       |

| 0x60  | AT91SAM7Axx  | AT91SAM7Axx Series                   |

| 0x61  | AT91SAM7AQxx | AT91SAM7AQxx Series                  |

| 0x63  | AT91x63      | AT91x63 Series                       |

| 0x64  | SAM4CxxC     | SAM4CxC Series (100-pin version)     |

| 0x66  | SAM4CxxE     | SAM4CxE Series (144-pin version)     |

| 0x70  | AT91SAM7Sxx  | AT91SAM7Sxx Series                   |

| 0x71  | AT91SAM7XCxx | AT91SAM7XCxx Series                  |

| 0x72  | AT91SAM7SExx | AT91SAM7SExx Series                  |

| 0x73  | AT91SAM7Lxx  | AT91SAM7Lxx Series                   |

| 0x75  | AT91SAM7Xxx  | AT91SAM7Xxx Series                   |

| 0x76  | AT91SAM7SLxx | AT91SAM7SLxx Series                  |

| 0x80  | SAM3UxC      | SAM3UxC Series (100-pin version)     |

| 0x81  | SAM3UxE      | SAM3UxE Series (144-pin version)     |

| 0x83  | SAM3AxC      | SAM3AxC Series (100-pin version)     |

| 0x84  | SAM3XxC      | SAM3XxC Series (100-pin version)     |

| 0x85  | SAM3XxE      | SAM3XxE Series (144-pin version)     |

| 0x86  | SAM3XxG      | SAM3XxG Series (208/217-pin version) |

| 0x92  | AT91x92      | AT91x92 Series                       |

| 0x93  | SAM4NxA      | SAM4NxA Series (48-pin version)      |

| 0x94  | SAM4NxB      | SAM4NxB Series (64-pin version)      |

| 0x95  | SAM4NxC      | SAM4NxC Series (100-pin version)     |

| 0x99  | SAM3SDxB     | SAM3SDxB Series (64-pin version)     |

## 27.7.1 PIO Enable Register

| Name:    | PIO_PER        |               |                 |              |     |     |     |

|----------|----------------|---------------|-----------------|--------------|-----|-----|-----|

| Address: | 0x400E0E00 (PI | OA), 0x400E10 | 000 (PIOB), 0x4 | 00E1200 (PIO | C)  |     |     |

| Access:  | Write-only     |               |                 |              |     |     |     |

| 31       | 30             | 29            | 28              | 27           | 26  | 25  | 24  |

| P31      | P30            | P29           | P28             | P27          | P26 | P25 | P24 |

| 23       | 22             | 21            | 20              | 19           | 18  | 17  | 16  |

| P23      | P22            | P21           | P20             | P19          | P18 | P17 | P16 |

| 15       | 14             | 13            | 12              | 11           | 10  | 9   | 8   |

| P15      | P14            | P13           | P12             | P11          | P10 | P9  | P8  |

| 7        | 6              | 5             | 4               | 3            | 2   | 1   | 0   |

| P7       | P6             | P5            | P4              | P3           | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in "PIO Write Protect Mode Register" .

## • P0-P31: PIO Enable

0: No effect.

1: Enables the PIO to control the corresponding pin (disables peripheral control of the pin).

## 27.7.20 PIO Multi-driver Status Register

Name: PIO\_MDSR

Address: 0x400E0E58 (PIOA), 0x400E1058 (PIOB), 0x400E1258 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Multi Drive Status.

0: The Multi Drive is disabled on the I/O line. The pin is driven at high and low level.

1: The Multi Drive is enabled on the I/O line. The pin is driven at low level only.

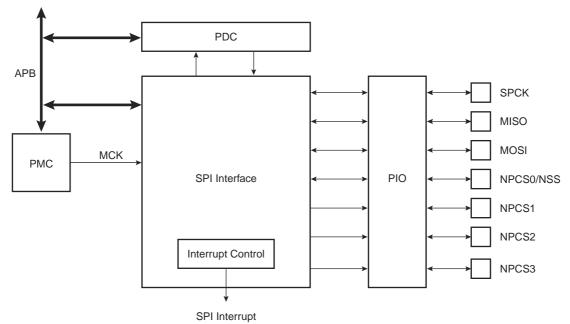

# 28.3 Block Diagram

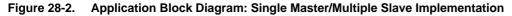

# 28.4 Application Block Diagram

Atmel

| 20.0.9 381 | Chip Select Register |    |     |       |        |       |      |  |  |  |

|------------|----------------------|----|-----|-------|--------|-------|------|--|--|--|

| Name:      | SPI_CSRx[x=03]       |    |     |       |        |       |      |  |  |  |

| Address:   | 0x40008030           |    |     |       |        |       |      |  |  |  |

| Access:    | Read/Write           |    |     |       |        |       |      |  |  |  |

| 31         | 30                   | 29 | 28  | 27    | 26     | 25    | 24   |  |  |  |

|            |                      |    | DLY | ВСТ   |        |       |      |  |  |  |

| 23         | 22                   | 21 | 20  | 19    | 18     | 17    | 16   |  |  |  |

|            |                      |    | DĽ  | YBS   |        |       |      |  |  |  |

| 15         | 14                   | 13 | 12  | 11    | 10     | 9     | 8    |  |  |  |

|            | SCBR                 |    |     |       |        |       |      |  |  |  |

| 7          | 6                    | 5  | 4   | 3     | 2      | 1     | 0    |  |  |  |

|            | BITS                 |    |     | CSAAT | CSNAAT | NCPHA | CPOL |  |  |  |

This register can only be written if the WPEN bit is cleared in "SPI Write Protection Mode Register".

Note: SPI\_CSRx registers must be written even if the user wants to use the defaults. The BITS field will not be updated with the translated value unless the register is written.

## CPOL: Clock Polarity

20.0.0 CDI Chin Salaat Degister

0 = The inactive state value of SPCK is logic level zero.

1 = The inactive state value of SPCK is logic level one.

CPOL is used to determine the inactive state value of the serial clock (SPCK). It is used with NCPHA to produce the required clock/data relationship between master and slave devices.

## • NCPHA: Clock Phase

0 = Data is changed on the leading edge of SPCK and captured on the following edge of SPCK.

1 = Data is captured on the leading edge of SPCK and changed on the following edge of SPCK.

NCPHA determines which edge of SPCK causes data to change and which edge causes data to be captured. NCPHA is used with CPOL to produce the required clock/data relationship between master and slave devices.

## • CSNAAT: Chip Select Not Active After Transfer (Ignored if CSAAT = 1)

0 = The Peripheral Chip Select does not rise between two transfers if the SPI\_TDR is reloaded before the end of the first transfer and if the two transfers occur on the same Chip Select.

1 = The Peripheral Chip Select rises systematically after each transfer performed on the same slave. It remains active after the end of transfer for a minimal duration of:

- $-\frac{DLYBCT}{MCK}$  (if DLYBCT field is different from 0)

- $\frac{DLYBCT + 1}{MCK}$  (if DLYBCT field equals 0)

## CSAAT: Chip Select Active After Transfer

0 = The Peripheral Chip Select Line rises as soon as the last transfer is achieved.

1 = The Peripheral Chip Select does not rise after the last transfer is achieved. It remains active until a new transfer is requested on a different chip select.

### 31.7.7.5 Character Transmission

The characters are sent by writing in the Transmit Holding Register (US\_THR). An additional condition for transmitting a character can be added when the USART is configured in SPI master mode. In the USART\_MR register, the value configured on INACK field can prevent any character transmission (even if US\_THR has been written) while the receiver side is not ready (character not read). When WRDBT equals 0, the character is transmitted whatever the receiver status. If WRDBT is set to 1, the transmitter waits for the receiver holding register to be read before transmitting the character (RXRDY flag cleared), thus preventing any overflow (character loss) on the receiver side.

The transmitter reports two status bits in the Channel Status Register (US\_CSR): TXRDY (Transmitter Ready), which indicates that US\_THR is empty and TXEMPTY, which indicates that all the characters written in US\_THR have been processed. When the current character processing is completed, the last character written in US\_THR is transferred into the Shift Register of the transmitter and US\_THR becomes empty, thus TXRDY rises.

Both TXRDY and TXEMPTY bits are low when the transmitter is disabled. Writing a character in US\_THR while TXRDY is low has no effect and the written character is lost.

If the USART is in SPI Slave Mode and if a character must be sent while the Transmit Holding Register (US\_THR) is empty, the UNRE (Underrun Error) bit is set. The TXD transmission line stays at high level during all this time. The UNRE bit is cleared by writing the Control Register (US\_CR) with the RSTSTA (Reset Status) bit to 1.

In SPI Master Mode, the slave select line (NSS) is asserted at low level 1 Tbit (Time bit) before the transmission of the MSB bit and released at high level 1 Tbit after the transmission of the LSB bit. So, the slave select line (NSS) is always released between each character transmission and a minimum delay of 3 Tbits always inserted. However, in order to address slave devices supporting the CSAAT mode (Chip Select Active After Transfer), the slave select line (NSS) can be forced at low level by writing the Control Register (US\_CR) with the RTSEN bit to 1. The slave select line (NSS) can be released at high level only by writing the Control Register (US\_CR) with the RTSEN bit to 1. The slave select line (NSS) can be released at high level only by writing the Control Register (US\_CR) with the RTSEN bit to 1.

In SPI Slave Mode, the transmitter does not require a falling edge of the slave select line (NSS) to initiate a character transmission but only a low level. However, this low level must be present on the slave select line (NSS) at least 1 Tbit before the first serial clock cycle corresponding to the MSB bit.

### 31.7.7.6 Character Reception

When a character reception is completed, it is transferred to the Receive Holding Register (US\_RHR) and the RXRDY bit in the Status Register (US\_CSR) rises. If a character is completed while RXRDY is set, the OVRE (Overrun Error) bit is set. The last character is transferred into US\_RHR and overwrites the previous one. The OVRE bit is cleared by writing the Control Register (US\_CR) with the RSTSTA (Reset Status) bit to 1.

To ensure correct behavior of the receiver in SPI Slave Mode, the master device sending the frame must ensure a minimum delay of 1 Tbit between each character transmission. The receiver does not require a falling edge of the slave select line (NSS) to initiate a character reception but only a low level. However, this low level must be present on the slave select line (NSS) at least 1 Tbit before the first serial clock cycle corresponding to the MSB bit.

### 31.7.7.7 Receiver Timeout

Because the receiver baudrate clock is active only during data transfers in SPI Mode, a receiver timeout is impossible in this mode, whatever the Time-out value is (field TO) in the Time-out Register (US\_RTOR).

### 31.7.8 Test Modes

The USART can be programmed to operate in three different test modes. The internal loopback capability allows on-board diagnostics. In the loopback mode the USART interface pins are disconnected or not and reconfigured for loopback internally or externally.

## 31.8.2 USART Control Register (SPI\_MODE)

| Name:    | US_CR (SPI_M    | ODE)           |                |       |       |    |        |

|----------|-----------------|----------------|----------------|-------|-------|----|--------|

| Address: | 0x40024000 (0), | , 0x40028000 ( | 1), 0x4002C000 | ) (2) |       |    |        |

| Access:  | Write-only      |                |                |       |       |    |        |

| 31       | 30              | 29             | 28             | 27    | 26    | 25 | 24     |

| -        | -               | -              | -              | -     | -     | -  | -      |

| 23       | 22              | 21             | 20             | 19    | 18    | 17 | 16     |

| _        | -               | -              | -              | RCS   | FCS   | _  | -      |

| 15       | 14              | 13             | 12             | 11    | 10    | 9  | 8      |

| -        | _               | —              | _              | —     | -     | —  | RSTSTA |

| 7        | 6               | 5              | 4              | 3     | 2     | 1  | 0      |

| TXDIS    | TXEN            | RXDIS          | RXEN           | RSTTX | RSTRX | -  | -      |

This configuration is relevant only if USART\_MODE=0xE or 0xF in "USART Mode Register" on page 633.

### • RSTRX: Reset Receiver

0: No effect.

1: Resets the receiver.

### • RSTTX: Reset Transmitter

0: No effect.

1: Resets the transmitter.

### • RXEN: Receiver Enable

0: No effect.

1: Enables the receiver, if RXDIS is 0.

## • RXDIS: Receiver Disable

0: No effect.

1: Disables the receiver.

## • TXEN: Transmitter Enable

0: No effect.

1: Enables the transmitter if TXDIS is 0.

## • TXDIS: Transmitter Disable

0: No effect.

1: Disables the transmitter.

## RSTSTA: Reset Status Bits

0: No effect.

1: Resets the status bits OVRE, UNRE in US\_CSR.

## 33.7.12 PWM Channel Counter Register

Name: PWM\_CCNT[0..3]

## Address: 0x4002020C [0], 0x4002022C [1], 0x4002024C [2], 0x4002026C [3]

Access: Read-only

| 31  | 30  | 29 | 28 | 27 | 26 | 25 | 24 |  |

|-----|-----|----|----|----|----|----|----|--|

|     | CNT |    |    |    |    |    |    |  |

| 23  | 22  | 21 | 20 | 19 | 18 | 17 | 16 |  |

|     | CNT |    |    |    |    |    |    |  |

| 15  | 14  | 13 | 12 | 11 | 10 | 9  | 8  |  |

|     | CNT |    |    |    |    |    |    |  |

| 7   | 6   | 5  | 4  | 3  | 2  | 1  | 0  |  |

| CNT |     |    |    |    |    |    |    |  |

### CNT: Channel Counter Register

Internal counter value. This register is reset when:

- the channel is enabled (writing CHIDx in the PWM\_ENA register).

- the counter reaches CPRD value defined in the PWM\_CPRDx register if the waveform is left aligned.

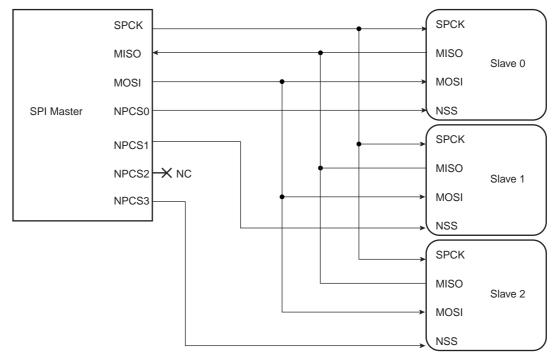

# 34.3 Block Diagram

### Figure 34-1. Analog-to-Digital Converter Block Diagram

# 34.4 Signal Description

## Table 34-1. ADC Pin Description

| Pin Name                  | Description                |

|---------------------------|----------------------------|

| ADVREF                    | External Reference voltage |

| AD0 - AD16 <sup>(1)</sup> | Analog input channels      |

| ADTRG                     | External trigger           |

Note: 1. AD16 is not an actual pin but is internally connected to a temperature sensor.

## 36.4.5 3 to 20 MHz Crystal Oscillator Characteristics

| Symbol                   | Parameter                                  | Conditions                                                             | Min | Тур | Max  | Unit |  |

|--------------------------|--------------------------------------------|------------------------------------------------------------------------|-----|-----|------|------|--|

| f <sub>osc</sub>         | Operating Frequency                        | Normal mode with crystal                                               | 3   | 16  | 20   | MHz  |  |

| V <sub>rip(VDDPLL)</sub> | Supply Ripple Voltage (on VDDPLL)          | RMS value, 10 kHz to 10 MHz                                            |     |     | 30   | mV   |  |

|                          | Duty Cycle                                 |                                                                        | 40  | 50  | 60   | %    |  |

|                          |                                            | 3 MHz, C <sub>SHUNT</sub> = 3 pF                                       |     |     | 14.5 |      |  |

|                          |                                            | 8 MHz, C <sub>SHUNT</sub> = 7 pF                                       |     |     | 4    |      |  |

| t <sub>START</sub>       | Startup Time                               | 16 MHz, $C_{SHUNT} = 7 \text{ pF}$ with $C_m = 8 \text{ fF}$           |     |     | 1.4  | ms   |  |

|                          |                                            | 16 MHz, $C_{SHUNT} = 7 \text{ pF}$ with $C_m = 1.6 \text{ fF}$         |     |     | 2.5  |      |  |

|                          |                                            | 20 MHz, C <sub>SHUNT</sub> = 7 pF                                      |     |     | 1    |      |  |

| I <sub>DDON</sub>        | Current Consumption (on VDDIO)             | 3 MHz                                                                  |     | 230 | 350  | μΑ   |  |

|                          |                                            | 8 MHz                                                                  |     | 300 | 400  |      |  |

|                          |                                            | 16 MHz                                                                 |     | 390 | 470  |      |  |

|                          |                                            | 20 MHz                                                                 |     | 450 | 560  |      |  |

|                          |                                            | 3 MHz                                                                  |     |     | 15   |      |  |

| P <sub>ON</sub>          | Drive Level                                | 8 MHz                                                                  |     |     | 30   | μW   |  |

|                          |                                            | 16 MHz, 20 MHz                                                         |     |     | 50   |      |  |

| R <sub>f</sub>           | Internal Resistor                          | Between XIN and XOUT                                                   |     | 0.5 |      | MΩ   |  |

| C <sub>LEXT</sub>        | Maximum External Capacitor on XIN and XOUT |                                                                        |     |     | 17   | pF   |  |

| C <sub>INTLOAD</sub>     | Internal Load Capacitance                  | Integrated load capacitance ((XIN)<br>(GND) and (XOUT)(GND) in series) | 7.5 | 9   | 10.5 | pF   |  |

| C <sub>LOAD</sub>        | Internal Equivalent Load Capacitance       | Integrated Load Capacitance<br>(XIN and XOUT in series)                | 7.5 | 9   | 10.5 | pF   |  |

| Table 36-23. | 3 to 20 MHz Crystal Oscillator Characteristics |

|--------------|------------------------------------------------|

|--------------|------------------------------------------------|

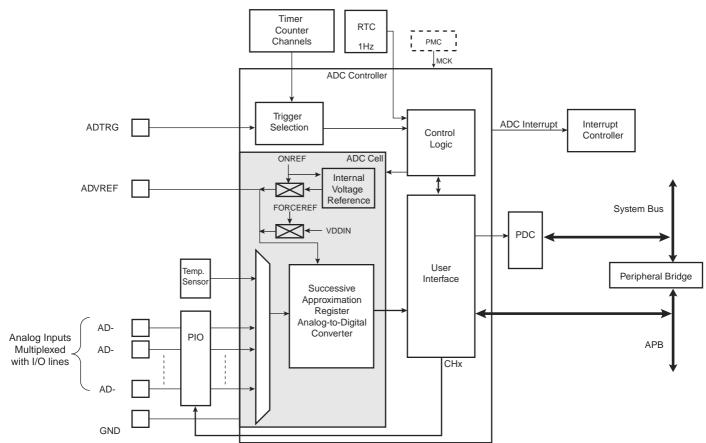

### Figure 36-11. 3 to 20 MHz Crystal Oscillator Schematics

$C_{\text{LEXT}} = 2 \times (C_{\text{crystal}} - C_{\text{L}} - C_{\text{PCB}})$

where:

$C_{\text{PCB}}$  is the capacitance of the printed circuit board (PCB) track layout from the crystal to the SAM4 pin.

### Table 41-1. SAM4N Datasheet Rev. 11158B Revision History (Continued)

| Issue Date  | Comments                                                                                                                                                                                                                                                                                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Section 36. "SAM4N Electrical Characteristics" (cont'd)                                                                                                                                                                                                                                                                          |

|             | Section 36.10.6 "Embedded Flash Characteristics": inserted content about erasing flash content prior to programming an application; corrected instance of "field FWS of the MC_FMR" to "field FWS in the EEFC_FMR"; replaced four "Embedded Flash Wait State" tables with single Table 36-45 "Embedded Flash Wait State at 85°C" |

|             | Table 36-46 "AC Flash Characteristics": added parameter "Erase Pin Assertion Time"; added Program Cycle Time values for Write Page Mode                                                                                                                                                                                          |

| 23-Mar-15   | Section 37. "SAM4N Mechanical Characteristics"                                                                                                                                                                                                                                                                                   |

| 23-11101-15 | Figure 37-2 "100-ball TFBGA Package Drawing": corrected 'A' maximum dimension in inches from 0.0575 to 0.0433                                                                                                                                                                                                                    |

|             | Added Section 38. "Marking"                                                                                                                                                                                                                                                                                                      |

|             | Section 39. "Ordering Information"                                                                                                                                                                                                                                                                                               |

|             | Table 39-1 "Ordering Codes for SAM4N Devices": updated column headers; removed "Package Type" column (this information is provided on the Atmel website)                                                                                                                                                                         |

|             | Added Section 40. "Errata"                                                                                                                                                                                                                                                                                                       |

| Doc. Rev.<br>11158A |             | Change<br>Request<br>Ref. |

|---------------------|-------------|---------------------------|

|                     | First Issue |                           |