Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                    |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40MHz                                                                            |

| Connectivity               | CANbus, SPI, UART/USART                                                          |

| Peripherals                | PWM, WDT                                                                         |

| Number of I/O              | 47                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                     |

| Data Converters            | A/D 14x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | PG-LQFP-64-4                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc164cm16f40fbafxqma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2007-03 Published by Infineon Technologies AG 81726 Munich, Germany © 2007 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# 16-Bit Single-Chip Microcontroller with C166SV2 Core XC166 Family

XC164CM

# **1** Summary of Features

For a quick overview or reference, the XC164CM's properties are listed here in a condensed way.

- High Performance 16-bit CPU with 5-Stage Pipeline

- 25 ns Instruction Cycle Time at 40 MHz CPU Clock (Single-Cycle Execution)

- 1-Cycle Multiplication (16 × 16 bit), Background Division (32 / 16 bit) in 21 Cycles

- 1-Cycle Multiply-and-Accumulate (MAC) Instructions

- Enhanced Boolean Bit Manipulation Facilities

- Zero-Cycle Jump Execution

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Fast Context Switching Support with Two Additional Local Register Banks

- 16 Mbytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area (C166 Family Compatible)

- 16-Priority-Level Interrupt System with up to 63 Sources, Sample-Rate down to 50 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC), 24-Bit Pointers Cover Total Address Space

- Clock Generation via on-chip PLL (factors 1:0.15 ... 1:10), or

- via Prescaler (factors 1:1 ... 60:1)

- On-Chip Memory Modules

- 2 Kbytes On-Chip Dual-Port RAM (DPRAM)

- 0/2/4 Kbytes<sup>1)</sup> On-Chip Data SRAM (DSRAM)

- 2 Kbytes On-Chip Program/Data SRAM (PSRAM)

- 32/64/128<sup>1)</sup> Kbytes On-Chip Program Memory (Flash Memory)

- On-Chip Peripheral Modules

- 14-Channel A/D Converter with Programmable Resolution (10-bit or 8-bit) and Conversion Time (down to 2.55 μs or 2.15 μs)

- 16-Channel General Purpose Capture/Compare Unit (CAPCOM2)

- Capture/Compare Unit for flexible PWM Signal Generation (CAPCOM6)

- Multi-Functional General Purpose Timer Unit with 5 Timers

- Two Synchronous/Asynchronous Serial Channels (USARTs)

- Two High-Speed-Synchronous Serial Channels

- On-Chip TwinCAN Interface (Rev. 2.0B active) with 32 Message Objects (Full CAN/Basic CAN) on Two CAN Nodes, and Gateway Functionality

- On-Chip Real Time Clock, Driven by the Main Oscillator

<sup>1)</sup> Depends on the respective derivative. See Table 1 "XC164CM Derivative Synopsis" on Page 6.

#### **Summary of Features**

#### Table 1 XC164CM Derivative Synopsis

| Derivative <sup>1)</sup>                 | Temp.            | Program             | On-Chip RAM                                          | Interfaces                               |

|------------------------------------------|------------------|---------------------|------------------------------------------------------|------------------------------------------|

|                                          | Range            | Memory              |                                                      | Internaces                               |

| SAK-XC164CM-16F40F<br>SAK-XC164CM-16F20F | -40 to<br>125 °C | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1 |

| SAF-XC164CM-16F40F<br>SAF-XC164CM-16F20F | -40 to<br>85 °C  | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1 |

| SAK-XC164CM-8F40F<br>SAK-XC164CM-8F20F   | -40 to<br>125 °C | 64 Kbytes<br>Flash  | 2 Kbytes DPRAM,<br>2 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1 |

| SAF-XC164CM-8F40F<br>SAF-XC164CM-8F20F   | -40 to<br>85 °C  | 64 Kbytes<br>Flash  | 2 Kbytes DPRAM,<br>2 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1 |

| SAK-XC164CM-4F40F<br>SAK-XC164CM-4F20F   | -40 to<br>125 °C | 32 Kbytes<br>Flash  | 2 Kbytes DPRAM,<br>2 Kbytes PSRAM                    | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1 |

| SAF-XC164CM-4F40F<br>SAF-XC164CM-4F20F   | -40 to<br>85 °C  | 32 Kbytes<br>Flash  | 2 Kbytes DPRAM,<br>2 Kbytes PSRAM                    | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1 |

1) This Data Sheet is valid for:

devices starting with and including design step BA for the -16F derivatives, and for devices starting with and including design step AA for -4F/8F derivatives.

#### **General Device Information**

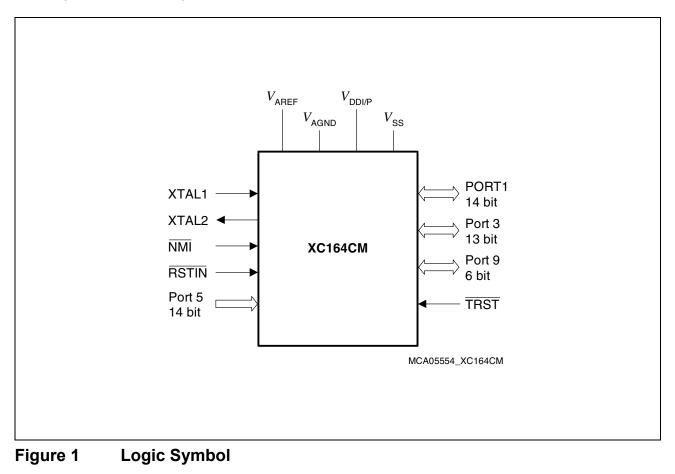

# 2 General Device Information

The XC164CM derivatives are high-performance members of the Infineon XC166 Family of full featured single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 40 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. They also provide clock generation via PLL and various on-chip memory modules such as program Flash, program RAM, and data RAM.

## **General Device Information**

| Table 2     | Pi            | n Defini       | tions and Functions (cont'd)                                                                                                                                                                                                           |

|-------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sym-<br>bol | Pin<br>Num.   | Input<br>Outp. | Function                                                                                                                                                                                                                               |

| PORT1       | 1-6,<br>49-56 | IO             | PORT1 consists of one 8-bit and one 6-bit bidirectional I/O<br>port P1L and P1H. Each pin can be programmed for input<br>(output driver in high-impedance state) or output.<br>The following PORT1 pins also serve for alt. functions: |

| P1L.0       | 49            | I/O            | CC60: [CAPCOM6] Input / Output of Channel 0                                                                                                                                                                                            |

| P1L.1       | 50            | 0              | COUT60: [CAPCOM6] Output of Channel 0                                                                                                                                                                                                  |

| P1L.2       | 51            | I/O            | CC61: [CAPCOM6] Input / Output of Channel 1                                                                                                                                                                                            |

| P1L.3       | 52            | 0              | COUT61: [CAPCOM6] Output of Channel 1                                                                                                                                                                                                  |

| P1L.4       | 53            | I/O            | CC62: [CAPCOM6] Input / Output of Channel 2                                                                                                                                                                                            |

| P1L.5       | 54            | 0              | COUT62: [CAPCOM6] Output of Channel 2                                                                                                                                                                                                  |

| P1L.6       | 55            | 0              | COUT63: Output of 10-bit Compare Channel                                                                                                                                                                                               |

| P1L.7       | 56            | 1              | CTRAP: [CAPCOM6] Trap Input CTRAP is an input pin with                                                                                                                                                                                 |

|             |               |                | an internal pull-up resistor. A low level on this pin switches the CAPCOM6 compare outputs to the logic level defined by software (if enabled).                                                                                        |

|             |               | I/O            | CC22IO: [CAPCOM2] CC22 Capture Inp./Compare Outp.                                                                                                                                                                                      |

| P1H.0       | 1             |                | CC6POS0: [CAPCOM6] Position 0 Input,                                                                                                                                                                                                   |

|             |               |                | EX0IN: [Fast External Interrupt 0] Input (default pin),                                                                                                                                                                                |

|             | ~             | 1/0            | CC23IO: [CAPCOM2] CC23 Capture Inp./Compare Outp.                                                                                                                                                                                      |

| P1H.1       | 2             |                | CC6POS1: [CAPCOM6] Position 1 Input,                                                                                                                                                                                                   |

| P1H.2       | 3             | I<br>I/O<br>I  | EX1IN: [Fast External Interrupt 1] Input (default pin),<br><u>MRST1: [SSC1]</u> Master-Receive/Slave-Transmit In/Out.<br><u>CC6POS2</u> : [CAPCOM6] Position 2 Input,                                                                  |

|             |               | 1              | EX2IN: [Fast External Interrupt 2] Input (default pin),                                                                                                                                                                                |

|             |               | I/O            | MTSR1: [SSC1] Master-Transmit/Slave-Receive Out/Inp.                                                                                                                                                                                   |

| P1H.3       | 3             | 1              | T7IN: [CAPCOM2] Timer T7 Count Input,                                                                                                                                                                                                  |

|             |               | I/O            | SCLK1: [SSC1] Master Clock Output / Slave Clock Input,                                                                                                                                                                                 |

|             |               | 1              | EX3IN: [Fast External Interrupt 3] Input (default pin),                                                                                                                                                                                |

| P1H.4       | 5             | I/O            | CC24IO: [CAPCOM2] CC24 Capture Inp./Compare Outp.,                                                                                                                                                                                     |

|             |               |                | EX4IN: [Fast External Interrupt 4] Input (default pin)                                                                                                                                                                                 |

| P1H.5       | 6             | I/O<br>I       | CC25IO: [CAPCOM2] CC25 Capture Inp./Compare Outp.,<br>EX5IN: [Fast External Interrupt 5] Input (default pin)                                                                                                                           |

|             |               |                | Note: At the end of an external reset P1H.4 and P1H.5 also may input startup configuration values                                                                                                                                      |

### **General Device Information**

| Table 2          | Pin Definitions and Functions (cont'd) |                |                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sym-<br>bol      | Pin<br>Num.                            | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                 |

| XTAL2<br>XTAL1   | 61<br>60                               | 0<br>I         | XTAL2: Output of the oscillator amplifier circuit<br>XTAL1: Input to the oscillator amplifier and input to the<br>internal clock generator<br>To clock the device from an external source, drive XTAL1,<br>while leaving XTAL2 unconnected. Minimum and maximum<br>high/low and rise/fall times specified in the AC Characteristics<br>must be observed. |

|                  |                                        |                | Note: Input pin XTAL1 belongs to the core voltage domain. Therefore, input voltages must be within the range defined for $V_{DDI}$ .                                                                                                                                                                                                                     |

| $V_{AREF}$       | 19                                     | _              | Reference voltage for the A/D converter                                                                                                                                                                                                                                                                                                                  |

| $V_{AGND}$       | 20                                     | -              | Reference ground for the A/D converter                                                                                                                                                                                                                                                                                                                   |

| V <sub>DDI</sub> | 26, 58                                 | _              | Digital Core Supply Voltage (On-Chip Modules):<br>+2.5 V during normal operation and idle mode.<br>Please refer to the <b>Operating Condition Parameters</b>                                                                                                                                                                                             |

| V <sub>DDP</sub> | 8, 27,<br>40, 57                       | _              | Digital Pad Supply Voltage (Pin Output Drivers):<br>+5 V during normal operation and idle mode.<br>Please refer to the <b>Operating Condition Parameters</b>                                                                                                                                                                                             |

| V <sub>SS</sub>  | 7, 25,<br>41, 59                       | -              | <b>Digital Ground</b><br>Connect decoupling capacitors to adjacent $V_{DD}/V_{SS}$ pin pairs<br>as close as possible to the pins.<br>All $V_{SS}$ pins must be connected to the ground-line or ground-<br>plane.                                                                                                                                         |

1) The CAN interface lines are assigned to port P9 under software control.

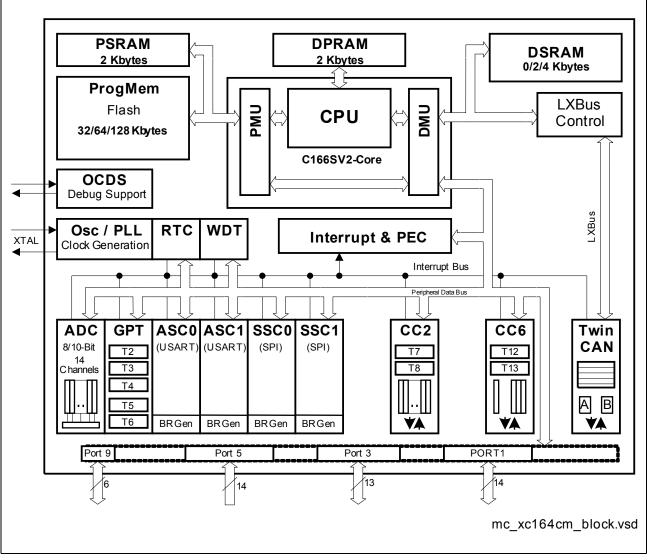

# 3 Functional Description

The architecture of the XC164CM combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a very well-balanced way. In addition, the on-chip memory blocks allow the design of compact systems-on-silicon with maximum performance (computing, control, communication).

The on-chip memory blocks (program code-memory and SRAM, dual-port RAM, data SRAM) and the set of generic peripherals are connected to the CPU via separate buses. Another bus, the LXBus, connects additional on-chip resources (see **Figure 3**).

This bus structure enhances the overall system performance by enabling the concurrent operation of several subsystems of the XC164CM.

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the XC164CM.

Figure 3 Block Diagram

## Table 4 XC164CM Interrupt Nodes

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| EX0IN                                         | CC1_CC8IC           | xx'0060 <sub>H</sub>             | 18 <sub>H</sub> / 24 <sub>D</sub> |

| EX1IN                                         | CC1_CC9IC           | xx'0064 <sub>H</sub>             | 19 <sub>H</sub> / 25 <sub>D</sub> |

| EX2IN                                         | CC1_CC10IC          | xx'0068 <sub>H</sub>             | 1A <sub>H</sub> / 26 <sub>D</sub> |

| EX3IN                                         | CC1_CC11IC          | xx'006C <sub>H</sub>             | 1B <sub>H</sub> / 27 <sub>D</sub> |

| EX4IN                                         | CC1_CC12IC          | xx'0070 <sub>H</sub>             | 1C <sub>H</sub> / 28 <sub>D</sub> |

| EX5IN                                         | CC1_CC13IC          | xx'0074 <sub>H</sub>             | 1D <sub>H</sub> / 29 <sub>D</sub> |

| CAPCOM Register 16                            | CC2_CC16IC          | xx'00C0 <sub>H</sub>             | 30 <sub>H</sub> / 48 <sub>D</sub> |

| CAPCOM Register 17                            | CC2_CC17IC          | xx'00C4 <sub>H</sub>             | 31 <sub>H</sub> / 49 <sub>D</sub> |

| CAPCOM Register 18                            | CC2_CC18IC          | xx'00C8 <sub>H</sub>             | 32 <sub>H</sub> / 50 <sub>D</sub> |

| CAPCOM Register 19                            | CC2_CC19IC          | xx'00CC <sub>H</sub>             | 33 <sub>H</sub> / 51 <sub>D</sub> |

| CAPCOM Register 20                            | CC2_CC20IC          | xx'00D0 <sub>H</sub>             | 34 <sub>H</sub> / 52 <sub>D</sub> |

| CAPCOM Register 21                            | CC2_CC21IC          | xx'00D4 <sub>H</sub>             | 35 <sub>H</sub> / 53 <sub>D</sub> |

| CAPCOM Register 22                            | CC2_CC22IC          | xx'00D8 <sub>H</sub>             | 36 <sub>H</sub> / 54 <sub>D</sub> |

| CAPCOM Register 23                            | CC2_CC23IC          | xx'00DC <sub>H</sub>             | 37 <sub>H</sub> / 55 <sub>D</sub> |

| CAPCOM Register 24                            | CC2_CC24IC          | xx'00E0 <sub>H</sub>             | 38 <sub>H</sub> / 56 <sub>D</sub> |

| CAPCOM Register 25                            | CC2_CC25IC          | xx'00E4 <sub>H</sub>             | 39 <sub>H</sub> / 57 <sub>D</sub> |

| CAPCOM Register 26                            | CC2_CC26IC          | xx'00E8 <sub>H</sub>             | 3A <sub>H</sub> / 58 <sub>D</sub> |

| CAPCOM Register 27                            | CC2_CC27IC          | xx'00EC <sub>H</sub>             | 3B <sub>H</sub> / 59 <sub>D</sub> |

| CAPCOM Register 28                            | CC2_CC28IC          | xx'00F0 <sub>H</sub>             | 3C <sub>H</sub> / 60 <sub>D</sub> |

| CAPCOM Register 29                            | CC2_CC29IC          | xx'0110 <sub>H</sub>             | 44 <sub>H</sub> / 68 <sub>D</sub> |

| CAPCOM Register 30                            | CC2_CC30IC          | xx'0114 <sub>H</sub>             | 45 <sub>H</sub> / 69 <sub>D</sub> |

| CAPCOM Register 31                            | CC2_CC31IC          | xx'0118 <sub>H</sub>             | 46 <sub>H</sub> / 70 <sub>D</sub> |

| CAPCOM Timer 7                                | CC2_T7IC            | xx'00F4 <sub>H</sub>             | 3D <sub>H</sub> / 61 <sub>D</sub> |

| CAPCOM Timer 8                                | CC2_T8IC            | xx'00F8 <sub>H</sub>             | 3E <sub>H</sub> / 62 <sub>D</sub> |

| GPT1 Timer 2                                  | GPT12E_T2IC         | xx'0088 <sub>H</sub>             | 22 <sub>H</sub> / 34 <sub>D</sub> |

| GPT1 Timer 3                                  | GPT12E_T3IC         | xx'008C <sub>H</sub>             | 23 <sub>H</sub> / 35 <sub>D</sub> |

| GPT1 Timer 4                                  | GPT12E_T4IC         | xx'0090 <sub>H</sub>             | 24 <sub>H</sub> / 36 <sub>D</sub> |

| GPT2 Timer 5                                  | GPT12E_T5IC         | xx'0094 <sub>H</sub>             | 25 <sub>H</sub> / 37 <sub>D</sub> |

| GPT2 Timer 6                                  | GPT12E_T6IC         | xx'0098 <sub>H</sub>             | 26 <sub>H</sub> / 38 <sub>D</sub> |

#### Table 4XC164CM Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAN5                                          | CAN_5IC             | xx'0168 <sub>H</sub>             | 5A <sub>H</sub> / 90 <sub>D</sub> |

| CAN6                                          | CAN_6IC             | xx'016C <sub>H</sub>             | 5B <sub>H</sub> / 91 <sub>D</sub> |

| CAN7                                          | CAN_7IC             | xx'0170 <sub>H</sub>             | 5C <sub>H</sub> / 92 <sub>D</sub> |

| RTC                                           | RTC_IC              | xx'0174 <sub>H</sub>             | 5D <sub>H</sub> / 93 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0040 <sub>H</sub>             | 10 <sub>H</sub> / 16 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0044 <sub>H</sub>             | 11 <sub>H</sub> / 17 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0048 <sub>H</sub>             | 12 <sub>H</sub> / 18 <sub>D</sub> |

| Unassigned node                               | -                   | xx'004C <sub>H</sub>             | 13 <sub>H</sub> / 19 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0050 <sub>H</sub>             | 14 <sub>H</sub> / 20 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0054 <sub>H</sub>             | 15 <sub>H</sub> / 21 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0058 <sub>H</sub>             | 16 <sub>H</sub> / 22 <sub>D</sub> |

| Unassigned node                               | -                   | xx'005C <sub>H</sub>             | 17 <sub>H</sub> / 23 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0078 <sub>H</sub>             | 1E <sub>H</sub> / 30 <sub>D</sub> |

| Unassigned node                               | -                   | xx'007C <sub>H</sub>             | 1F <sub>H</sub> / 31 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0080 <sub>H</sub>             | 20 <sub>H</sub> / 32 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0084 <sub>H</sub>             | 21 <sub>H</sub> / 33 <sub>D</sub> |

| Unassigned node                               | -                   | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| Unassigned node                               | -                   | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |

| Unassigned node                               | _                   | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |

1) Register VECSEG defines the segment where the vector table is located to.

Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting, with a distance of 4 (two words) between two vectors.

# 3.4 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system provides a broad range of debug and emulation features built into the XC164CM. The user software running on the XC164CM can thus be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface, consisting of the IEEE-1149-conforming JTAG port and a break interface. The debugger controls the OCDS via a set of dedicated registers accessible via the JTAG interface. Additionally, the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported as well as the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU-halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the JTAG interface.

The debug interface uses a set of 6 interface signals (4 JTAG lines, 2 break lines) to communicate with external circuitry. These interface signals are realized as alternate functions on Port 3 pins.

count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM2 timers, and to cause a reload from the CAPREL register.

The CAPREL register may capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared after the capture procedure. This allows the XC164CM to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

The RTC module can be used for different purposes:

- System clock to determine the current time and date, optionally during idle mode, sleep mode, and power down mode

- Cyclic time based interrupt, to provide a system time tick independent of CPU frequency and other resources, e.g. to wake up regularly from idle mode

- 48-bit timer for long term measurements (maximum timespan is > 100 years)

- Alarm interrupt for wake-up on a defined time

### 3.9 A/D Converter

For analog signal measurement, a 10-bit A/D converter with 14 multiplexed input channels and a sample and hold circuit has been integrated on-chip. It uses the method of successive approximation. The sample time (for loading the capacitors) and the conversion time is programmable (in two modes) and can thus be adjusted to the external circuitry. The A/D converter can also operate in 8-bit conversion mode, where the conversion time is further reduced.

Overrun error detection/protection is provided for the conversion result register (ADDAT): either an interrupt request will be generated when the result of a previous conversion has not been read from the result register at the time the next conversion is complete, or the next conversion is suspended in such a case until the previous result has been read.

For applications which require less analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converter of the XC164CM supports four different conversion modes. In the standard Single Channel conversion mode, the analog level on a specified channel is sampled once and converted to a digital result. In the Single Channel Continuous mode, the analog level on a specified channel is repeatedly sampled and converted without software intervention. In the Auto Scan mode, the analog levels on a prespecified number of channels are sequentially sampled and converted. In the Auto Scan Continuous mode, the prespecified channels are repeatedly sampled and converted. In addition, the conversion of a specific channel can be inserted (injected) into a running sequence without disturbing this sequence. This is called Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the conversion results into a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer.

After each reset and also during normal operation the ADC automatically performs calibration cycles. This automatic self-calibration constantly adjusts the converter to changing operating conditions (e.g. temperature) and compensates process variations.

These calibration cycles are part of the conversion cycle, so they do not affect the normal operation of the A/D converter.

In order to decouple analog inputs from digital noise and to avoid input trigger noise those pins used for analog input can be disconnected from the digital input stages under software control. This can be selected for each pin separately via register P5DIDIS (Port 5 Digital Input Disable).

The Auto-Power-Down feature of the A/D converter minimizes the power consumption when no conversion is in progress.

## 3.16 Parallel Ports

The XC164CM provides up to 47 I/O lines which are organized into three input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of some I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs.

The edge characteristics (shape) and driver characteristics (output current) of the port drivers can be selected via registers POCONx.

The input threshold of some ports is selectable (TTL or CMOS like), where the special CMOS like input threshold reduces noise sensitivity due to the input hysteresis. The input threshold may be selected individually for each byte of the respective ports.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

| Port                           | Control                                        | Alternate Functions                                                                    |

|--------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------|

| PORT1                          | Pad drivers                                    | Capture inputs or compare outputs,<br>Serial interface lines                           |

| Port 3                         | Pad drivers,<br>Open drain,<br>Input threshold | Timer control signals, serial interface lines,<br>System clock output CLKOUT (or FOUT) |

| Port 5                         | -                                              | Analog input channels to the A/D converter,<br>Timer control signals                   |

| Port 9                         | 9 Pad drivers,                                 | Capture inputs or compare outputs                                                      |

| Open drain,<br>Input threshold | CAN interface lines <sup>1)</sup>              |                                                                                        |

Table 7Summary of the XC164CM's Parallel Ports

1) Can be assigned by software.

## 3.17 **Power Management**

The XC164CM provides several means to control the power it consumes either at a given time or averaged over a certain timespan. Three mechanisms can be used (partly in parallel):

• **Power Saving Modes** switch the XC164CM into a special operating mode (control via instructions).

Idle Mode stops the CPU while the peripherals can continue to operate.

Sleep Mode and Power Down Mode stop all clock signals and all operation (RTC may optionally continue running). Sleep Mode can be terminated by external interrupt signals.

• Clock Generation Management controls the distribution and the frequency of internal and external clock signals. While the clock signals for currently inactive parts of logic are disabled automatically, the user can reduce the XC164CM's CPU clock frequency which drastically reduces the consumed power.

External circuitry can be controlled via the programmable frequency output FOUT.

• **Peripheral Management** permits temporary disabling of peripheral modules (control via register SYSCON3). Each peripheral can separately be disabled/enabled.

The on-chip RTC supports intermittent operation of the XC164CM by generating cyclic wake-up signals. This offers full performance to quickly react on action requests while the intermittent sleep phases greatly reduce the average power consumption of the system.

## 3.18 Instruction Set Summary

Table 8 lists the instructions of the XC164CM in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

| Mnemonic                            | Description                                                                                       | Bytes |

|-------------------------------------|---------------------------------------------------------------------------------------------------|-------|

| ADD(B)                              | Add word (byte) operands                                                                          | 2/4   |

| ADDC(B)                             | Add word (byte) operands with Carry                                                               |       |

| SUB(B)                              | Subtract word (byte) operands                                                                     | 2/4   |

| SUBC(B)                             | Subtract word (byte) operands with Carry                                                          | 2/4   |

| MUL(U)                              | (Un)Signed multiply direct GPR by direct GPR (16- $\times$ 16-bit)                                | 2     |

| DIV(U)                              | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |

| DIVL(U)                             | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |

| CPL(B)                              | Complement direct word (byte) GPR                                                                 | 2     |

| NEG(B)                              | Negate direct word (byte) GPR                                                                     | 2     |

| AND(B)                              | Bitwise AND, (word/byte operands)                                                                 | 2/4   |

| OR(B)                               | Bitwise OR, (word/byte operands)                                                                  |       |

| XOR(B)                              | Bitwise exclusive OR, (word/byte operands)                                                        |       |

| BCLR/BSET                           | Clear/Set direct bit                                                                              |       |

| BMOV(N)                             | Move (negated) direct bit to direct bit                                                           |       |

| BAND/BOR/BXOR                       | OR/BXOR AND/OR/XOR direct bit with direct bit                                                     |       |

| BCMP                                | Compare direct bit to direct bit                                                                  | 4     |

| BFLDH/BFLDL                         | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |

| CMP(B) Compare word (byte) operands |                                                                                                   | 2/4   |

| CMPD1/2                             | Compare word data to GPR and decrement GPR by 1/2                                                 |       |

| CMPI1/2                             | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |

| PRIOR                               | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR |       |

| SHL/SHR                             | Shift left/right direct word GPR                                                                  | 2     |

#### Table 8 Instruction Set Summary

| Table 8 Inst | ruction Set Summary (cont'd)                                                             |       |

|--------------|------------------------------------------------------------------------------------------|-------|

| Mnemonic     | Description                                                                              | Bytes |

| ROL/ROR      | Rotate left/right direct word GPR                                                        | 2     |

| ASHR         | Arithmetic (sign bit) shift right direct word GPR                                        | 2     |

| MOV(B)       | Move word (byte) data                                                                    | 2/4   |

| MOVBS/Z      | Move byte operand to word op. with sign/zero extension                                   | 2/4   |

| JMPA/I/R     | Jump absolute/indirect/relative if condition is met                                      | 4     |

| JMPS         | Jump absolute to a code segment                                                          | 4     |

| JB(C)        | Jump relative if direct bit is set (and clear bit)                                       | 4     |

| JNB(S)       | Jump relative if direct bit is not set (and set bit)                                     | 4     |

| CALLA/I/R    | Call absolute/indirect/relative subroutine if condition is met                           | 4     |

| CALLS        | Call absolute subroutine in any code segment                                             | 4     |

| PCALL        | Push direct word register onto system stack and call absolute subroutine                 | 4     |

| TRAP         | Call interrupt service routine via immediate trap number                                 | 2     |

| PUSH/POP     | Push/pop direct word register onto/from system stack                                     | 2     |

| SCXT         | Push direct word register onto system stack and update register with word operand        | 4     |

| RET(P)       | Return from intra-segment subroutine<br>(and pop direct word register from system stack) | 2     |

| RETS         | Return from inter-segment subroutine                                                     | 2     |

| RETI         | Return from interrupt service subroutine                                                 | 2     |

| SBRK         | Software Break                                                                           | 2     |

| SRST         | Software Reset                                                                           | 4     |

| IDLE         | Enter Idle Mode                                                                          | 4     |

| PWRDN        | Enter Power Down Mode (supposes MMI-pin being low)                                       | 4     |

| SRVWDT       | Service Watchdog Timer                                                                   | 4     |

| DISWDT/ENWDT | Disable/Enable Watchdog Timer                                                            | 4     |

| EINIT        | End-of-Initialization Register Lock                                                      | 4     |

| ATOMIC       | Begin ATOMIC sequence                                                                    | 2     |

| EXTR         | Begin EXTended Register sequence                                                         | 2     |

| EXTP(R)      | Begin EXTended Page (and Register) sequence                                              |       |

| EXTS(R)      |                                                                                          |       |

| Table 8Instruction Set Summary (cont'd) |                                     |       |  |

|-----------------------------------------|-------------------------------------|-------|--|

| Mnemonic                                | Description                         | Bytes |  |

| NOP                                     | Null operation                      | 2     |  |

| CoMUL/CoMAC                             | Multiply (and accumulate)           | 4     |  |

| CoADD/CoSUB                             | Add/Subtract                        | 4     |  |

| Co(A)SHR                                | (Arithmetic) Shift right            | 4     |  |

| CoSHL                                   | Shift left                          | 4     |  |

| CoLOAD/STORE                            | Load accumulator/Store MAC register | 4     |  |

| CoCMP                                   | Compare                             | 4     |  |

| CoMAX/MIN                               | Maximum/Minimum                     | 4     |  |

| CoABS/CoRND                             | Absolute value/Round accumulator    | 4     |  |

| CoMOV                                   | Data move                           | 4     |  |

| CoNEG/NOP                               | Negate accumulator/Null operation   | 4     |  |

#### **Electrical Parameters**

Sample time and conversion time of the XC164CM's A/D Converter are programmable. In compatibility mode, the above timing can be calculated using **Table 15**. The limit values for  $f_{BC}$  must not be exceeded when selecting ADCTC.

| ADCON.15 14<br>(ADCTC) | A/D Converter<br>Basic Clock $f_{\rm BC}$ | ADCON.13 12<br>(ADSTC) | Sample Time<br><i>t</i> <sub>S</sub> |

|------------------------|-------------------------------------------|------------------------|--------------------------------------|

| 00                     | <i>f</i> <sub>SYS</sub> / 4               | 00                     | $t_{\rm BC} 	imes 8$                 |

| 01                     | f <sub>SYS</sub> / 2                      | 01                     | $t_{\rm BC} 	imes 16$                |

| 10                     | <i>f</i> <sub>SYS</sub> / 16              | 10                     | $t_{\rm BC} \times 32$               |

| 11                     | f <sub>SYS</sub> / 8                      | 11                     | $t_{\rm BC} 	imes 64$                |

Table 15

A/D Converter Computation Table<sup>1)</sup>

1) These selections are available in compatibility mode. An improved mechanism to control the ADC input clock can be selected.

#### **Converter Timing Example:**

| Assumptions:      | $f_{\rm SYS}$           | = 40 MHz (i.e. <i>t</i> <sub>SYS</sub> = 25 ns), ADCTC = '01', ADSTC = '00'           |

|-------------------|-------------------------|---------------------------------------------------------------------------------------|

| Basic clock       | $f_{\rm BC}$            | = f <sub>SYS</sub> / 2 = 20 MHz, i.e. t <sub>BC</sub> = 50 ns                         |

| Sample time       | t <sub>S</sub>          | = $t_{\rm BC} \times 8$ = 400 ns                                                      |

| Conversion 10-b   | oit:                    |                                                                                       |

| With post-calibr. | t <sub>C10P</sub>       | = $52 \times t_{BC}$ + $t_{S}$ + $6 \times t_{SYS}$ = (2600 + 400 + 150) ns = 3.15 µs |

| Post-calibr. off  | <i>t</i> <sub>C10</sub> | = $40 \times t_{BC}$ + $t_{S}$ + $6 \times t_{SYS}$ = (2000 + 400 + 150) ns = 2.55 µs |

| Conversion 8-bi   | t:                      |                                                                                       |

| With post-calibr. | t <sub>C8P</sub>        | = $44 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (2200 + 400 + 150) ns = 2.75 µs     |

| Post-calibr. off  | t <sub>C8</sub>         | = $32 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (1600 + 400 + 150) ns = 2.15 µs     |

www.infineon.com

B158-H8824-G2-X-7600

Published by Infineon Technologies AG