Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 118                                                                              |

| Program Memory Size        | 448KB (448K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 24x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2385a56f80laakxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |  |  |  |  |

|-----|------------------|--------|------|------------------------------------------------|--|--|--|--|

| 45  | P5.10            | I      | In/A | Bit 10 of Port 5, General Purpose Input        |  |  |  |  |

|     | ADC0_CH10        | I      | In/A | Analog Input Channel 10 for ADC0               |  |  |  |  |

|     | ADC1_CH10        | I      | In/A | Analog Input Channel 10 for ADC1               |  |  |  |  |

|     | BRKIN_A          | I      | In/A | OCDS Break Signal Input                        |  |  |  |  |

|     | U2C1_DX0F        | I      | In/A | USIC2 Channel 1 Shift Data Input               |  |  |  |  |

|     | CCU61_T13<br>HRA | I      | In/A | External Run Control Input for T13 of CCU61    |  |  |  |  |

| 46  | P5.11            | I      | In/A | Bit 11 of Port 5, General Purpose Input        |  |  |  |  |

|     | ADC0_CH11        | I      | In/A | Analog Input Channel 11 for ADC0               |  |  |  |  |

|     | ADC1_CH11        | I      | In/A | Analog Input Channel 11 for ADC1               |  |  |  |  |

| 47  | P5.12            | I      | In/A | Bit 12 of Port 5, General Purpose Input        |  |  |  |  |

|     | ADC0_CH12        | I      | In/A | Analog Input Channel 12 for ADC0               |  |  |  |  |

| 48  | P5.13            | I      | In/A | Bit 13 of Port 5, General Purpose Input        |  |  |  |  |

|     | ADC0_CH13        | I      | In/A | Analog Input Channel 13 for ADC0               |  |  |  |  |

|     | CCU63_T13<br>HRF | I      | In/A | External Run Control Input for T13 of CCU63    |  |  |  |  |

| 49  | P5.14            | I      | In/A | Bit 14 of Port 5, General Purpose Input        |  |  |  |  |

|     | ADC0_CH14        | I      | In/A | Analog Input Channel 14 for ADC0               |  |  |  |  |

| 50  | P5.15            | I      | In/A | Bit 15 of Port 5, General Purpose Input        |  |  |  |  |

|     | ADC0_CH15        | I      | In/A | Analog Input Channel 15 for ADC0               |  |  |  |  |

|     | RxDC2F           | I      | In/A | CAN Node 2 Receive Data Input                  |  |  |  |  |

| 51  | P2.12            | O0 / I | St/B | Bit 12 of Port 2, General Purpose Input/Output |  |  |  |  |

|     | U0C0_SELO<br>4   | O1     | St/B | USIC0 Channel 0 Select/Control 4 Output        |  |  |  |  |

|     | U0C1_SELO<br>3   | O2     | St/B | USIC0 Channel 1 Select/Control 3 Output        |  |  |  |  |

|     | TXDC2            | О3     | St/B | CAN Node 2 Transmit Data Output                |  |  |  |  |

|     | READY            | IH     | St/B | External Bus Interface READY Input             |  |  |  |  |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.      | Туре | Function                                                                                                                           |

|-----|-------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| 52  | P2.11             | 00/1       | St/B | Bit 11 of Port 2, General Purpose Input/Output                                                                                     |

| -   | U0C0_SELO<br>2    | 01         | St/B | USIC0 Channel 0 Select/Control 2 Output                                                                                            |

|     | U0C1_SELO<br>2    | O2         | St/B | USIC0 Channel 1 Select/Control 2 Output                                                                                            |

|     | BHE/WRH           | ОН         | St/B | External Bus Interf. High-Byte Control Output Can operate either as Byte High Enable (BHE) or as Write strobe for High Byte (WRH). |

| 53  | P11.5             | O0 / I     | St/B | Bit 5 of Port 11, General Purpose Input/Output                                                                                     |

|     | CCU61_CC6<br>0    | O1         | St/B | CCU61 Channel 0 Output                                                                                                             |

|     | CCU61_COU<br>T63  | O2         | St/B | CCU61 Channel 3 Output                                                                                                             |

|     | CCU61_CC6<br>0INB | I          | St/B | CCU61 Channel 0 Input                                                                                                              |

| 55  | P2.0              | O0 / I     | St/B | Bit 0 of Port 2, General Purpose Input/Output                                                                                      |

|     | CCU63_CC6         | O2         | St/B | CCU63 Channel 0 Output                                                                                                             |

|     | AD13              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 13                                                                                        |

|     | RxDC0C            | I          | St/B | CAN Node 0 Receive Data Input                                                                                                      |

|     | CCU63_CC6<br>0INB | I          | St/B | CCU63 Channel 0 Input                                                                                                              |

|     | T5INB             | I          | St/B | GPT12E Timer T5 Count/Gate Input                                                                                                   |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.      | Туре | Function                                       |

|-----|-------------------|------------|------|------------------------------------------------|

| 56  | P2.1              | O0 / I     | St/B | Bit 1 of Port 2, General Purpose Input/Output  |

|     | TxDC0             | 01         | St/B | CAN Node 0 Transmit Data Output                |

|     | CCU63_CC6<br>1    | O2         | St/B | CCU63 Channel 1 Output                         |

|     | AD14              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 14    |

|     | CCU63_CC6<br>1INB | I          | St/B | CCU63 Channel 1 Input                          |

|     | T5EUDB            | I          | St/B | GPT12E Timer T5 External Up/Down Control Input |

|     | ESR1_5            | I          | St/B | ESR1 Trigger Input 5                           |

| 57  | P11.4             | O0 / I     | St/B | Bit 4 of Port 11, General Purpose Input/Output |

|     | CCU61_CC6<br>2    | 01         | St/B | CCU61 Channel 2 Output                         |

|     | CCU61_CC6<br>2INB | I          | St/B | CCU61 Channel 2 Input                          |

| 58  | P2.2              | O0 / I     | St/B | Bit 2 of Port 2, General Purpose Input/Output  |

|     | TxDC1             | 01         | St/B | CAN Node 1 Transmit Data Output                |

|     | CCU63_CC6<br>2    | O2         | St/B | CCU63 Channel 2 Output                         |

|     | AD15              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15    |

|     | CCU63_CC6<br>2INB | I          | St/B | CCU63 Channel 2 Input                          |

|     | ESR2_5            | I          | St/B | ESR2 Trigger Input 5                           |

| 59  | P11.3             | O0 / I     | St/B | Bit 3 of Port 11, General Purpose Input/Output |

|     | CCU61_COU<br>T63  | 01         | St/B | CCU61 Channel 3 Output                         |

|     | CCU61_COU<br>T62  | O2         | St/B | CCU61 Channel 2 Output                         |

|     | CCU61_T13<br>HRF  | I          | St/B | External Run Control Input for T13 of CCU61    |

Table 6 Pin Definitions and Functions (cont'd)

| Symbol Ctrl. Type Function |                                                                                                                                             |      |                                                                                        |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|--|--|--|

| Symbol                     | Ctrl.                                                                                                                                       | Type | Function                                                                               |  |  |  |

| P0.3                       | O0 / I                                                                                                                                      | St/B | Bit 3 of Port 0, General Purpose Input/Output                                          |  |  |  |

| U1C0_SELO<br>0             | O1                                                                                                                                          | St/B | USIC1 Channel 0 Select/Control 0 Output                                                |  |  |  |

| U1C1_SELO<br>1             | O2                                                                                                                                          | St/B | USIC1 Channel 1 Select/Control 1 Output                                                |  |  |  |

| CCU61_COU<br>T60           | О3                                                                                                                                          | St/B | CCU61 Channel 0 Output                                                                 |  |  |  |

| A3                         | ОН                                                                                                                                          | St/B | External Bus Interface Address Line 3                                                  |  |  |  |

| U1C0_DX2A                  | I                                                                                                                                           | St/B | USIC1 Channel 0 Shift Control Input                                                    |  |  |  |

| RxDC0B                     | I                                                                                                                                           | St/B | CAN Node 0 Receive Data Input                                                          |  |  |  |

| P3.1                       | O0 / I                                                                                                                                      | St/B | Bit 1 of Port 3, General Purpose Input/Output                                          |  |  |  |

| U2C0_DOUT                  | 01                                                                                                                                          | St/B | USIC2 Channel 0 Shift Data Output                                                      |  |  |  |

| HLDA                       | OH /<br>IH                                                                                                                                  | St/B | External Bus Hold Acknowledge Output/Input Output in master mode, input in slave mode. |  |  |  |

| U2C0_DX0B                  | I                                                                                                                                           | St/B | USIC2 Channel 0 Shift Data Input                                                       |  |  |  |

| P10.2                      | O0 / I                                                                                                                                      | St/B | Bit 2 of Port 10, General Purpose Input/Output                                         |  |  |  |

| U0C0_SCLK<br>OUT           | 01                                                                                                                                          | St/B | USIC0 Channel 0 Shift Clock Output                                                     |  |  |  |

| CCU60_CC6<br>2             | O2                                                                                                                                          | St/B | CCU60 Channel 2 Output                                                                 |  |  |  |

| AD2                        | OH /<br>IH                                                                                                                                  | St/B | External Bus Interface Address/Data Line 2                                             |  |  |  |

| CCU60_CC6<br>2INA          | I                                                                                                                                           | St/B | CCU60 Channel 2 Input                                                                  |  |  |  |

| U0C0_DX1B                  | I                                                                                                                                           | St/B | USIC0 Channel 0 Shift Clock Input                                                      |  |  |  |

|                            | U1C0_SELO 0 U1C1_SELO 1 CCU61_COU T60 A3 U1C0_DX2A RXDC0B P3.1 U2C0_DOUT HLDA  U2C0_DX0B P10.2 U0C0_SCLK OUT CCU60_CC6 2 AD2 CCU60_CC6 2INA | P0.3 | P0.3                                                                                   |  |  |  |

### **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.      | Туре | Function                                       |

|-----|------------------|------------|------|------------------------------------------------|

| 102 | P0.6             | 00 / 1     |      | Bit 6 of Port 0, General Purpose Input/Output  |

|     | U1C1 DOUT        | 01         | St/B | USIC1 Channel 1 Shift Data Output              |

|     | TxDC1            | 02         | St/B | CAN Node 1 Transmit Data Output                |

|     | CCU61_COU<br>T63 | O3         | St/B | CCU61 Channel 3 Output                         |

|     | A6               | ОН         | St/B | External Bus Interface Address Line 6          |

|     | U1C1_DX0A        | I          | St/B | USIC1 Channel 1 Shift Data Input               |

|     | CCU61_CTR<br>APA | I          | St/B | CCU61 Emergency Trap Input                     |

|     | U1C1_DX1B        | I          | St/B | USIC1 Channel 1 Shift Clock Input              |

| 103 | P10.6            | O0 / I     | St/B | Bit 6 of Port 10, General Purpose Input/Output |

|     | U0C0_DOUT        | 01         | St/B | USIC0 Channel 0 Shift Data Output              |

|     | U1C0_SELO<br>0   | О3         | St/B | USIC1 Channel 0 Select/Control 0 Output        |

|     | AD6              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 6     |

|     | U0C0_DX0C        | I          | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U1C0_DX2D        | I          | St/B | USIC1 Channel 0 Shift Control Input            |

|     | CCU60_CTR<br>APA | I          | St/B | CCU60 Emergency Trap Input                     |

| 104 | P3.6             | O0 / I     | St/B | Bit 6 of Port 3, General Purpose Input/Output  |

|     | U2C1_DOUT        | O1         | St/B | USIC2 Channel 1 Shift Data Output              |

|     | U0C0_SELO<br>6   | О3         | St/B | USIC0 Channel 0 Select/Control 6 Output        |

|     | U2C1_DX0A        | I          | St/B | USIC2 Channel 1 Shift Data Input               |

|     | U2C1_DX1B        | I          | St/B | USIC2 Channel 1 Shift Clock Input              |

Data Sheet 36 V2.12, 2014-06

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.                                                                                                                      | Type | Function                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 138 | PORST            | I                                                                                                                          | In/B | Power On Reset Input A low level at this pin resets the XC238xA completely. A spike filter suppresses input pulses <10 ns. Input pulses >100 ns safely pass the filter. The minimum duration for a safe recognition should be 120 ns. An internal pull-up device will hold this pin high when nothing is driving it. |  |  |  |

| 139 | ESR1             | External Service Request 1 After power-up, an internal weak pull-up device holds this pin high when nothing is driving it. |      |                                                                                                                                                                                                                                                                                                                      |  |  |  |

|     | RxDC0E           | I                                                                                                                          | St/B | CAN Node 0 Receive Data Input                                                                                                                                                                                                                                                                                        |  |  |  |

|     | U1C0_DX0F        | I                                                                                                                          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |  |

|     | U1C0_DX2C        | I                                                                                                                          | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                                                  |  |  |  |

|     | U1C1_DX0C        | I                                                                                                                          | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |  |

|     | U1C1_DX2B        | I                                                                                                                          | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                  |  |  |  |

|     | U2C1_DX2C        | I                                                                                                                          | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                  |  |  |  |

| 140 | ESR2             | O0 / I                                                                                                                     | St/B | External Service Request 2 After power-up, an internal weak pull-up device holds this pin high when nothing is driving it.                                                                                                                                                                                           |  |  |  |

|     | RxDC1E           | I                                                                                                                          | St/B | CAN Node 1 Receive Data Input                                                                                                                                                                                                                                                                                        |  |  |  |

|     | CCU60_CTR<br>APC | I                                                                                                                          | St/B | CCU60 Emergency Trap Input                                                                                                                                                                                                                                                                                           |  |  |  |

|     | CCU61_CTR<br>APC | I                                                                                                                          | St/B | CCU61 Emergency Trap Input                                                                                                                                                                                                                                                                                           |  |  |  |

|     | CCU62_CTR<br>APC | I                                                                                                                          | St/B | CCU62 Emergency Trap Input                                                                                                                                                                                                                                                                                           |  |  |  |

|     | CCU63_CTR<br>APC | I                                                                                                                          | St/B | CCU63 Emergency Trap Input                                                                                                                                                                                                                                                                                           |  |  |  |

|     | U1C1_DX0D        | I                                                                                                                          | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |  |

|     | U1C1_DX2C        | I                                                                                                                          | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                  |  |  |  |

|     | U2C1_DX0E        | I                                                                                                                          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |  |

|     | U2C1_DX2B        | I                                                                                                                          | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                  |  |  |  |

### **General Device Information**

## 2.2 Identification Registers

The identification registers describe the current version of the XC238xA and of its modules.

Table 7 XC238xA Identification Registers

| <b>Short Name</b> | Value                  | Address              | Notes                       |

|-------------------|------------------------|----------------------|-----------------------------|

| SCU_IDMANUF       | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |                             |

| SCU_IDCHIP        | 3801 <sub>H</sub>      | 00'F07C <sub>H</sub> |                             |

| SCU_IDMEM         | 30D0 <sub>H</sub>      | 00'F07A <sub>H</sub> |                             |

| SCU_IDPROG        | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |                             |

| JTAG_ID           | 0017'E083 <sub>H</sub> |                      | marking EES-AA, ES-AA or AA |

Data Sheet 49 V2.12, 2014-06

# **Functional Description**

## Table 9 Compare Modes (cont'd)

| Compare Modes           | Function                                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Mode 2                  | Interrupt-only compare mode; Only one compare interrupt per timer period is generated                                     |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated    |

| Double Register<br>Mode | Two registers operate on one pin; Pin toggles on each compare match; Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses; Can be used with any compare mode                                                       |

### **Functional Description**

#### 3.18 Parallel Ports

The XC238xA provides up to 119 I/O lines which are organized into 11 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in **Table 10**.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

Table 10 Summary of the XC238xA's Ports

| Port | Width | I/O | Connected Modules                                                            |  |  |  |

|------|-------|-----|------------------------------------------------------------------------------|--|--|--|

| P0   | 8     | I/O | EBC (A7A0),<br>CCU6, USIC, CAN                                               |  |  |  |

| P1   | 8     | I/O | EBC (A15A8),<br>CCU6, USIC                                                   |  |  |  |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13), CAN, CC2, GPT12E, USIC, DAP/JTAG |  |  |  |

| P3   | 8     | I/O | CAN, USIC                                                                    |  |  |  |

| P4   | 8     | I/O | EBC (CS3CS0),<br>CC2, CAN, GPT12E, USIC                                      |  |  |  |

| P5   | 16    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                   |  |  |  |

| P6   | 4     | I/O | ADC, CAN, GPT12E                                                             |  |  |  |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                  |  |  |  |

| P8   | 7     | I/O | CCU6, DAP/JTAG, USIC                                                         |  |  |  |

| P9   | 8     | I/O | CCU6, DAP/JTAG, CAN                                                          |  |  |  |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0),<br>CCU6, USIC, DAP/JTAG, CAN              |  |  |  |

| P11  | 6     | I/O | CCU6, USIC, CAN                                                              |  |  |  |

| P15  | 8     | I   | Analog Inputs, GPT12E                                                        |  |  |  |

#### **Electrical Parameters**

### 4.1.3 Pad Timing Definition

If not otherwise noted, all timing parameters are tested and are valid for the corresponding output pins operating in strong driver, fast edge mode. See also "Pad Properties" on Page 113.

### 4.1.4 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC238xA and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

#### CC (Controller Characteristics):

The logic of the XC238xA provides signals with the specified characteristics.

### SR (System Requirement):

The external system must provide signals with the specified characteristics to the XC238xA.

#### **Electrical Parameters**

#### 4.2 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XC238xA are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.6.4**.

### **Supply Voltage Restrictions**

The XC238xA can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

During power-on sequences, the supply voltages may only change with a maximum speed of  $dV/dt < 5 \ V/\mu s$ , i.e. the target supply voltage may be reached earliest after approx. 1  $\mu s$ .

Note: To limit the speed of supply voltage changes, the employment of external buffer capacitors at pins  $V_{\rm DDPA}/V_{\rm DDPB}$  is recommended.

#### **Electrical Parameters**

Table 14 DC Characteristics for Upper Voltage Range (cont'd)

| Parameter                        | Symbol     | Values |      | Unit | Note / |                             |

|----------------------------------|------------|--------|------|------|--------|-----------------------------|

|                                  |            | Min.   | Тур. | Max. |        | Test Condition              |

| Output Low Voltage <sup>8)</sup> | $V_{OL}CC$ | -      | _    | 1.0  | V      | $I_{OL} \leq I_{OLmax}$     |

|                                  |            | _      | -    | 0.4  | ٧      | $I_{OL} \le I_{OLnom}^{9)}$ |

- 1) Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

- 2) Not subject to production test verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm CIV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (T<sub>J</sub> = junction temperature [°C]): I<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x TJ->)</sup> [μΑ]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 μA. Leakage derating depending on voltage level (DV = V<sub>DDP</sub> V<sub>PIN</sub> [V]): I<sub>OZ</sub> = I<sub>OZtempmax</sub> (1.6 x DV) (μA]. This voltage derating formula is an approximation which applies for maximum temperature.

- 5) Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device: V<sub>PIN</sub> ≤ V<sub>II max</sub> for a pullup; V<sub>PIN</sub> ≥ V<sub>II+min</sub> for a pulldown.

- 6) These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

- 7) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> ≥ V<sub>IHmin</sub> for a pullup; V<sub>PIN</sub> ≤ V<sub>ILmax</sub> for a pulldown.

- 8) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 9) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{\rm OL}$ -> $V_{\rm SS}$ ,  $V_{\rm OH}$ -> $V_{\rm DDP}$ ). However, only the levels for nominal output currents are verified.

Data Sheet 88 V2.12, 2014-06

#### **Electrical Parameters**

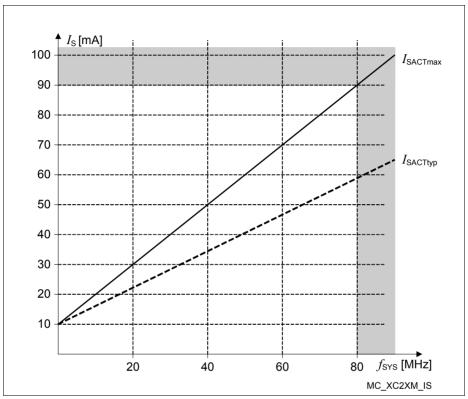

### 4.2.3 Power Consumption

The power consumed by the XC238xA depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current I<sub>S</sub> depends on the device activity

- The leakage current  $I_{LK}$  depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}$$

.

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

#### Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

### Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

Table 16 Switching Power Consumption

| Parameter                                                              | Symbol           |      | Values                                     | 3                    | Unit | Note /         |  |

|------------------------------------------------------------------------|------------------|------|--------------------------------------------|----------------------|------|----------------|--|

|                                                                        |                  | Min. | Тур.                                       | Max.                 |      | Test Condition |  |

| Power supply current (active) with all peripherals active and EVVRs on | $I_{SACT}$       | _    | 10 + $0.6 \text{ x}$ $f_{\text{SYS}}^{1)}$ | 10 + $f_{SYS}^{(1)}$ | mA   | 2)3)           |  |

| Power supply current in stopover mode, EVVRs on                        | $I_{\rm SSO}$ CC | _    | 0.7                                        | 2.0                  | mA   |                |  |

<sup>1)</sup>  $f_{SYS}$  in MHz.

### **Electrical Parameters**

Figure 14 Supply Current in Active Mode as a Function of Frequency

Note: Operating Conditions apply.

#### **Electrical Parameters**

Table 26 is valid under the following conditions:

$V_{\rm DDP} \ge 4.5 \text{ V}; \ V_{\rm DDPtyp} = 5 \text{ V}; \ V_{\rm DDP} \le 5.5 \text{ V}; \ C_{\rm L} \ge 20 \text{ pF}; \ C_{\rm L} \le 100 \text{ pF};$

Table 26 Standard Pad Parameters for Upper Voltage Range

| Parameter                                                    | Symbol               | Values |      |                                  | Unit | Note /                        |

|--------------------------------------------------------------|----------------------|--------|------|----------------------------------|------|-------------------------------|

|                                                              |                      | Min.   | Тур. | Max.                             |      | Test Condition                |

| Maximum output driver current (absolute value) <sup>1)</sup> | I <sub>Omax</sub> CC | -      | _    | 10                               | mA   | Strong driver                 |

|                                                              |                      | _      | _    | 4.0                              | mA   | Medium driver                 |

|                                                              |                      | _      | -    | 0.5                              | mA   | Weak driver                   |

| Nominal output driver current (absolute value)               | I <sub>Onom</sub> CC | -      | -    | 2.5                              | mA   | Strong driver                 |

|                                                              |                      | _      | _    | 1.0                              | mA   | Medium driver                 |

|                                                              |                      | _      | _    | 0.1                              | mA   | Weak driver                   |

| Rise and Fall times (10% - 90%)                              | t <sub>RF</sub> CC   | _      | -    | 4.2 +<br>0.14 x<br>$C_{L}$       | ns   | Strong driver;<br>Sharp edge  |

|                                                              |                      | _      | -    | 11.6 +<br>0.22 x<br>$C_{L}$      | ns   | Strong driver;<br>Medium edge |

|                                                              |                      | _      | -    | 20.6 +<br>0.22 x<br>$C_{\rm L}$  | ns   | Strong driver;<br>Slow edge   |

|                                                              |                      | _      | -    | 23 +<br>0.6 x<br>$C_{L}$         | ns   | Medium driver                 |

|                                                              |                      | -      | -    | 212 +<br>1.9 x<br>C <sub>1</sub> | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

#### **Electrical Parameters**

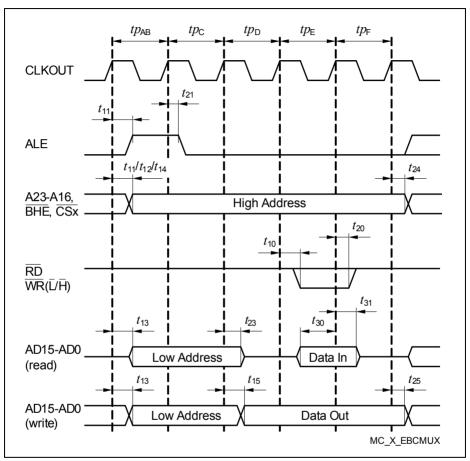

Figure 23 Multiplexed Bus Cycle

#### **Electrical Parameters**

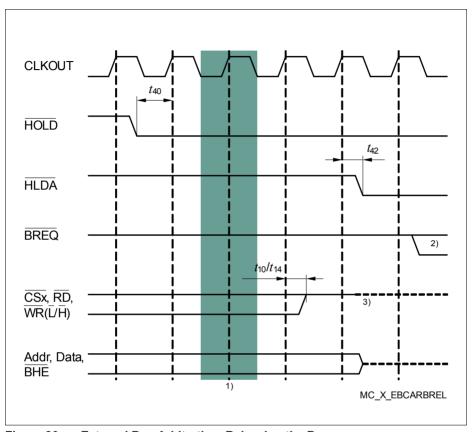

Figure 26 External Bus Arbitration, Releasing the Bus

### **Notes**

- 1. The XC238xA completes the currently running bus cycle before granting bus access.

- 2. This is the first possibility for BREQ to get active.

- 3. The control outputs will be resistive high (pull-up) after being driven inactive (ALE will be low).

#### **Electrical Parameters**

## 4.6.6 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_l = 20 \text{ pF}.$

Table 34 USIC SSC Master Mode Timing for Upper Voltage Range

| •      | • •  | U       | U              |

|--------|------|---------|----------------|

| Values |      |         | Note /         |

| Тур.   | Max. |         | Test Condition |

| _      | _    | ns      |                |

| -      | _    | ns      |                |

| _      | 9    | ns      |                |

| -      | -    | ns      |                |

| _      | _    | ns      |                |

|        | -    | - 9<br> | ns             |

<sup>1)</sup>  $t_{SYS} = 1 / f_{SYS}$

Table 35 USIC SSC Master Mode Timing for Lower Voltage Range

| Parameter                                                         | Symbol            | Values                                     |      |      | Unit | Note /         |

|-------------------------------------------------------------------|-------------------|--------------------------------------------|------|------|------|----------------|

|                                                                   |                   | Min.                                       | Тур. | Max. |      | Test Condition |

| Slave select output SELO active to first SCLKOUT transmit edge    | t <sub>1</sub> CC | <i>t</i> <sub>SYS</sub> - 10 <sup>1)</sup> | _    | _    | ns   |                |

| Slave select output SELO inactive after last SCLKOUT receive edge | t <sub>2</sub> CC | <i>t</i> <sub>SYS</sub> - 9 <sup>1)</sup>  | _    | _    | ns   |                |

| Data output DOUT valid time                                       | t <sub>3</sub> CC | -7                                         | _    | 11   | ns   |                |

#### **Electrical Parameters**

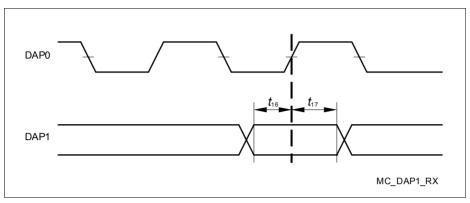

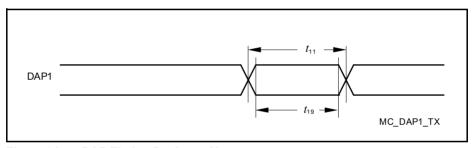

Figure 30 DAP Timing Host to Device

Figure 31 DAP Timing Device to Host

Note: The transmission timing is determined by the receiving debugger by evaluating the sync-request synchronization pattern telegram.

Data Sheet 133 V2.12, 2014-06

www.infineon.com

Published by Infineon Technologies AG