Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                           |

| Core Size                  | 16/32-Bit                                                                         |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI              |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                   |

| Number of I/O              | 118                                                                               |

| Program Memory Size        | 832KB (832K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 50K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                         |

| Data Converters            | A/D 24x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-144-4                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2387a104f80laakxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2014-06 Published by Infineon Technologies AG 81726 Munich, Germany © 2014 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Table | Table 6Pin Definitions and Functions (cont'd) |        |      |                                                   |  |  |  |  |  |

|-------|-----------------------------------------------|--------|------|---------------------------------------------------|--|--|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                          |  |  |  |  |  |

| 68    | P4.2                                          | O0 / I | St/B | Bit 2 of Port 4, General Purpose Input/Output     |  |  |  |  |  |

|       | TxDC2                                         | 02     | St/B | CAN Node 2 Transmit Data Output                   |  |  |  |  |  |

|       | CC2_CC26                                      | O3 / I | St/B | CAPCOM2 CC26IO Capture Inp./ Compare Out.         |  |  |  |  |  |

|       | CS2                                           | OH     | St/B | External Bus Interface Chip Select 2 Output       |  |  |  |  |  |

|       | T2INA                                         | I      | St/B | GPT12E Timer T2 Count/Gate Input                  |  |  |  |  |  |

|       | CCU62_CCP<br>OS1B                             | I      | St/B | CCU62 Position Input 1                            |  |  |  |  |  |

| 69    | P2.6                                          | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output     |  |  |  |  |  |

|       | U0C0_SELO<br>0                                | 01     | St/B | USIC0 Channel 0 Select/Control 0 Output           |  |  |  |  |  |

|       | U0C1_SELO<br>1                                | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output           |  |  |  |  |  |

|       | CC2_CC19                                      | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.         |  |  |  |  |  |

|       | A19                                           | OH     | St/B | External Bus Interface Address Line 19            |  |  |  |  |  |

|       | U0C0_DX2D                                     | I      | St/B | USIC0 Channel 0 Shift Control Input               |  |  |  |  |  |

|       | RxDC0D                                        | I      | St/B | CAN Node 0 Receive Data Input                     |  |  |  |  |  |

|       | ESR2_6                                        | I      | St/B | ESR2 Trigger Input 6                              |  |  |  |  |  |

| 70    | P4.4                                          | 00 / 1 | St/B | Bit 4 of Port 4, General Purpose Input/Output     |  |  |  |  |  |

|       | CC2_CC28                                      | O3 / I | St/B | CAPCOM2 CC28IO Capture Inp./ Compare Out.         |  |  |  |  |  |

|       | CS4                                           | OH     | St/B | External Bus Interface Chip Select 4 Output       |  |  |  |  |  |

|       | CLKIN2                                        | I      | St/B | Clock Signal Input 2                              |  |  |  |  |  |

| 71    | P4.3                                          | 00 / I | St/B | Bit 3 of Port 4, General Purpose Input/Output     |  |  |  |  |  |

|       | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output                 |  |  |  |  |  |

|       | CC2_CC27                                      | O3 / I | St/B | CAPCOM2 CC27IO Capture Inp./ Compare Out.         |  |  |  |  |  |

|       | CS3                                           | OH     | St/B | External Bus Interface Chip Select 3 Output       |  |  |  |  |  |

|       | RxDC2A                                        | I      | St/B | CAN Node 2 Receive Data Input                     |  |  |  |  |  |

|       | T2EUDA                                        | I      | St/B | GPT12E Timer T2 External Up/Down Control<br>Input |  |  |  |  |  |

|       | CCU62_CCP<br>OS2B                             | I      | St/B | CCU62 Position Input 2                            |  |  |  |  |  |

| Table | Table 6         Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |

|-------|--------------------------------------------------------|------------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                       |  |  |  |

| 84    | P10.0                                                  | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C1_DOUT                                              | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |

|       | CCU60_CC6<br>0                                         | O2         | St/B | CCU60 Channel 0 Output                         |  |  |  |

|       | AD0                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |  |  |  |

|       | CCU60_CC6<br>0INA                                      | 1          | St/B | CCU60 Channel 0 Input                          |  |  |  |

|       | ESR1_2                                                 | I          | St/B | ESR1 Trigger Input 2                           |  |  |  |

|       | U0C0_DX0A                                              | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|       | U0C1_DX0A                                              | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |

| 85    | P3.0                                                   | O0 / I     | St/B | Bit 0 of Port 3, General Purpose Input/Output  |  |  |  |

|       | U2C0_DOUT                                              | 01         | St/B | USIC2 Channel 0 Shift Data Output              |  |  |  |

|       | BREQ                                                   | ОН         | St/B | External Bus Request Output                    |  |  |  |

|       | ESR1_1                                                 | I          | St/B | ESR1 Trigger Input 1                           |  |  |  |

|       | U2C0_DX0A                                              | I          | St/B | USIC2 Channel 0 Shift Data Input               |  |  |  |

|       | U2C0_DX1A                                              | Ι          | St/B | USIC2 Channel 0 Shift Clock Input              |  |  |  |

| 86    | P10.1                                                  | O0 / I     | St/B | Bit 1 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C0_DOUT                                              | 01         | St/B | USIC0 Channel 0 Shift Data Output              |  |  |  |

|       | CCU60_CC6<br>1                                         | O2         | St/B | CCU60 Channel 1 Output                         |  |  |  |

|       | AD1                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 1     |  |  |  |

|       | CCU60_CC6<br>1INA                                      | 1          | St/B | CCU60 Channel 1 Input                          |  |  |  |

|       | U0C0_DX1A                                              | I          | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |  |

|       | U0C0_DX0B                                              | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

| Table | Fable 6Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |  |  |

|-------|-----------------------------------------------|--------|------|------------------------------------------------|--|--|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                       |  |  |  |  |  |

| 90    | P0.4                                          | O0 / I | St/B | Bit 4 of Port 0, General Purpose Input/Output  |  |  |  |  |  |

|       | U1C1_SELO<br>0                                | 01     | St/B | USIC1 Channel 1 Select/Control 0 Output        |  |  |  |  |  |

|       | U1C0_SELO<br>1                                | O2     | St/B | USIC1 Channel 0 Select/Control 1 Output        |  |  |  |  |  |

|       | CCU61_COU<br>T61                              | O3     | St/B | CCU61 Channel 1 Output                         |  |  |  |  |  |

|       | A4                                            | ОН     | St/B | External Bus Interface Address Line 4          |  |  |  |  |  |

|       | U1C1_DX2A                                     | I      | St/B | USIC1 Channel 1 Shift Control Input            |  |  |  |  |  |

|       | RxDC1B                                        | I      | St/B | CAN Node 1 Receive Data Input                  |  |  |  |  |  |

|       | ESR2_8                                        | I      | St/B | ESR2 Trigger Input 8                           |  |  |  |  |  |

| 92    | P2.13                                         | O0 / I | St/B | Bit 13 of Port 2, General Purpose Input/Output |  |  |  |  |  |

|       | U2C1_SELO<br>2                                | 01     | St/B | USIC2 Channel 1 Select/Control 2 Output        |  |  |  |  |  |

|       | RxDC2D                                        | I      | St/B | CAN Node 2 Receive Data Input                  |  |  |  |  |  |

| 93    | P3.2                                          | O0 / I | St/B | Bit 2 of Port 3, General Purpose Input/Output  |  |  |  |  |  |

|       | U2C0_SCLK<br>OUT                              | O1     | St/B | USIC2 Channel 0 Shift Clock Output             |  |  |  |  |  |

|       | U2C0_DX1B                                     | I      | St/B | USIC2 Channel 0 Shift Clock Input              |  |  |  |  |  |

|       | HOLD                                          | IH     | St/B | External Bus Master Hold Request Input         |  |  |  |  |  |

| 94    | P2.10                                         | O0 / I | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |  |  |  |  |

|       | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |  |  |

|       | U0C0_SELO<br>3                                | O2     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |  |  |  |

|       | CC2_CC23                                      | O3 / I | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |  |  |  |  |

|       | A23                                           | ОН     | St/B | External Bus Interface Address Line 23         |  |  |  |  |  |

|       | U0C1_DX0E                                     | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |  |  |

|       | CAPINA                                        | I      | St/B | GPT12E Register CAPREL Capture Input           |  |  |  |  |  |

| Table | Table 6Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                       |  |  |  |  |

| 102   | P0.6                                          | O0 / I     | St/B | Bit 6 of Port 0, General Purpose Input/Output  |  |  |  |  |

|       | U1C1_DOUT                                     | 01         | St/B | USIC1 Channel 1 Shift Data Output              |  |  |  |  |

|       | TxDC1                                         | O2         | St/B | CAN Node 1 Transmit Data Output                |  |  |  |  |

|       | CCU61_COU<br>T63                              | O3         | St/B | CCU61 Channel 3 Output                         |  |  |  |  |

|       | A6                                            | OH         | St/B | External Bus Interface Address Line 6          |  |  |  |  |

|       | U1C1_DX0A                                     | I          | St/B | USIC1 Channel 1 Shift Data Input               |  |  |  |  |

|       | CCU61_CTR<br>APA                              | I          | St/B | CCU61 Emergency Trap Input                     |  |  |  |  |

|       | U1C1_DX1B                                     | I          | St/B | USIC1 Channel 1 Shift Clock Input              |  |  |  |  |

| 103   | P10.6                                         | O0 / I     | St/B | Bit 6 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | U0C0_DOUT                                     | 01         | St/B | USIC0 Channel 0 Shift Data Output              |  |  |  |  |

|       | U1C0_SELO<br>0                                | O3         | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |  |  |  |

|       | AD6                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 6     |  |  |  |  |

|       | U0C0_DX0C                                     | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |  |

|       | U1C0_DX2D                                     | I          | St/B | USIC1 Channel 0 Shift Control Input            |  |  |  |  |

|       | CCU60_CTR<br>APA                              | I          | St/B | CCU60 Emergency Trap Input                     |  |  |  |  |

| 104   | P3.6                                          | O0 / I     | St/B | Bit 6 of Port 3, General Purpose Input/Output  |  |  |  |  |

|       | U2C1_DOUT                                     | 01         | St/B | USIC2 Channel 1 Shift Data Output              |  |  |  |  |

|       | U0C0_SELO<br>6                                | O3         | St/B | USIC0 Channel 0 Select/Control 6 Output        |  |  |  |  |

|       | U2C1_DX0A                                     | I          | St/B | USIC2 Channel 1 Shift Data Input               |  |  |  |  |

|       | U2C1_DX1B                                     | I          | St/B | USIC2 Channel 1 Shift Clock Input              |  |  |  |  |

# 3 Functional Description

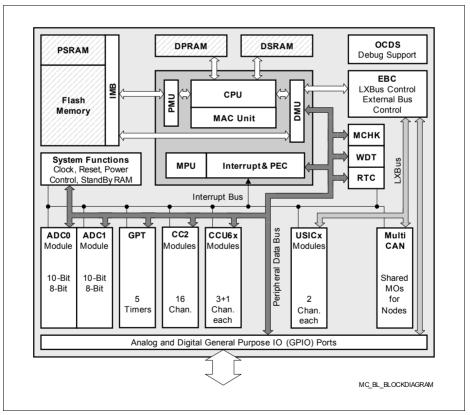

The architecture of the XC238xA combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources (see **Figure 4**). This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC238xA.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC238xA.

Figure 4 Block Diagram

#### **Functional Description**

With this hardware most XC238xA instructions are executed in a single machine cycle of 12.5 ns with an 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC238xA instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

## 3.10 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 and T4 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2 or T4, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be continuously generated without software intervention.

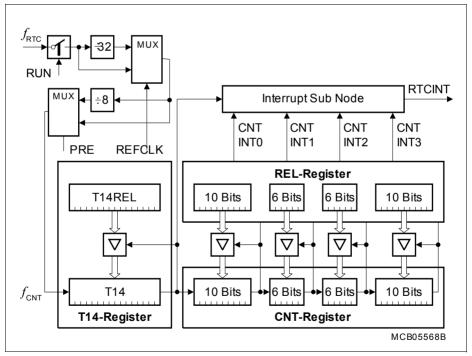

## 3.11 Real Time Clock

The Real Time Clock (RTC) module of the XC238xA can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

### Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

### **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

### 3.19 Instruction Set Summary

Table 11 lists the instructions of the XC238xA.

The addressing modes that can be used with a specific instruction, the function of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the **"Instruction Set Manual"**.

This document also provides a detailed description of each instruction.

| Mnemonic      | Description                                                                                       | Bytes |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------|-------|--|--|--|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |  |  |  |

| ADDC(B)       | Add word (byte) operands with Carry                                                               |       |  |  |  |

| SUB(B)        | Subtract word (byte) operands                                                                     | 2/4   |  |  |  |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |  |  |  |

| MUL(U)        | Un)Signed multiply direct GPR by direct GPR 16- × 16-bit)                                         |       |  |  |  |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |  |  |  |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |  |  |  |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |  |  |  |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |  |  |  |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |  |  |  |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |  |  |  |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |  |  |  |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |  |  |  |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |  |  |  |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |  |  |  |

| BCMP          | Compare direct bit to direct bit                                                                  | 4     |  |  |  |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |  |  |  |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |  |  |  |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |  |  |  |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |  |  |  |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |  |  |  |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |  |  |  |

### Table 11 Instruction Set Summary

| Mnemonic     | Description                                                                              | Bytes |  |  |  |

|--------------|------------------------------------------------------------------------------------------|-------|--|--|--|

| ROL/ROR      | Rotate left/right direct word GPR                                                        | 2     |  |  |  |

| ASHR         | Arithmetic (sign bit) shift right direct word GPR                                        |       |  |  |  |

| MOV(B)       | Nove word (byte) data                                                                    |       |  |  |  |

| MOVBS/Z      | Move byte operand to word op. with sign/zero extension                                   | 2/4   |  |  |  |

| JMPA/I/R     | Jump absolute/indirect/relative if condition is met                                      | 4     |  |  |  |

| JMPS         | Jump absolute to a code segment                                                          | 4     |  |  |  |

| JB(C)        | Jump relative if direct bit is set (and clear bit)                                       | 4     |  |  |  |

| JNB(S)       | Jump relative if direct bit is not set (and set bit)                                     | 4     |  |  |  |

| CALLA/I/R    | Call absolute/indirect/relative subroutine if condition is met                           | 4     |  |  |  |

| CALLS        | Call absolute subroutine in any code segment                                             | 4     |  |  |  |

| PCALL        | Push direct word register onto system stack and call absolute subroutine                 | 4     |  |  |  |

| TRAP         | Call interrupt service routine via immediate trap number                                 | 2     |  |  |  |

| PUSH/POP     | Push/pop direct word register onto/from system stack                                     | 2     |  |  |  |

| SCXT         | Push direct word register onto system stack and update register with word operand        | 4     |  |  |  |

| RET(P)       | Return from intra-segment subroutine<br>(and pop direct word register from system stack) | 2     |  |  |  |

| RETS         | Return from inter-segment subroutine                                                     | 2     |  |  |  |

| RETI         | Return from interrupt service subroutine                                                 | 2     |  |  |  |

| SBRK         | Software Break                                                                           | 2     |  |  |  |

| SRST         | Software Reset                                                                           | 4     |  |  |  |

| IDLE         | Enter Idle Mode                                                                          | 4     |  |  |  |

| PWRDN        | Unused instruction <sup>1)</sup>                                                         | 4     |  |  |  |

| SRVWDT       | Service Watchdog Timer                                                                   | 4     |  |  |  |

| DISWDT/ENWDT | Disable/Enable Watchdog Timer                                                            | 4     |  |  |  |

| EINIT        | End-of-Initialization Register Lock                                                      | 4     |  |  |  |

| ATOMIC       | Begin ATOMIC sequence                                                                    | 2     |  |  |  |

| EXTR         | Begin EXTended Register sequence                                                         | 2     |  |  |  |

| EXTP(R)      | Begin EXTended Page (and Register) sequence                                              | 2/4   |  |  |  |

| EXTS(R)      | Begin EXTended Segment (and Register) sequence                                           | 2/4   |  |  |  |

#### Data Sheet

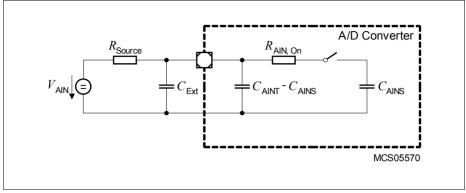

## 4.3 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance. *Note: Operating Conditions apply.*

### Table 18ADC Parameters

| Parameter                                       | Symbol                     |          | Values | S    | Unit     | Note /                                             |

|-------------------------------------------------|----------------------------|----------|--------|------|----------|----------------------------------------------------|

|                                                 |                            | Min. Typ |        | Max. |          | Test Condition                                     |

| Switched capacitance at an analog input         | C <sub>AINSW</sub><br>CC   | -        | 4      | 5    | pF       | not subject to production test <sup>1)</sup>       |

| Total capacitance at an analog input            | C <sub>AINT</sub><br>CC    | _        | 10     | 12   | pF       | not subject to production test <sup>1)</sup>       |

| Switched capacitance at the reference input     | C <sub>AREFSW</sub><br>CC  | _        | 7      | 9    | pF       | not subject to<br>production<br>test <sup>1)</sup> |

| Total capacitance at the reference input        | C <sub>AREFT</sub><br>CC   | _        | 13     | 15   | pF       | not subject to production test <sup>1)</sup>       |

| Differential Non-Linearity<br>Error             | EA <sub>DNL</sub>  <br>CC  | _        | 0.8    | 1.0  | LSB      | not subject to<br>production test                  |

| Gain Error                                      | EA <sub>GAIN</sub>  <br>CC | _        | 0.4    | 0.8  | LSB      | not subject to<br>production test                  |

| Integral Non-Linearity                          | EA <sub>INL</sub>  <br>CC  | _        | 0.8    | 1.2  | LSB      | not subject to<br>production test                  |

| Offset Error                                    | EA <sub>OFF</sub>  <br>CC  | -        | 0.5    | 0.8  | LSB      | not subject to<br>production test                  |

| Analog clock frequency                          | $f_{\rm ADCI}{\rm SR}$     | 0.5      | -      | 20   | MHz      | Upper voltage<br>range                             |

|                                                 |                            | 0.5      | -      | 16.5 | MHz      | Lower voltage range                                |

| Input resistance of the selected analog channel | R <sub>AIN</sub> CC        | -        | -      | 2    | kOh<br>m | not subject to<br>production<br>test <sup>1)</sup> |

| Input resistance of the reference input         | R <sub>AREF</sub><br>CC    | -        | -      | 2    | kOh<br>m | not subject to<br>production<br>test <sup>1)</sup> |

#### **Electrical Parameters**

Figure 16 Equivalent Circuitry for Analog Inputs

### PLL frequency band selection

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| Table 24 System PLL Parameters | Table 24 | System PLL Parameters |

|--------------------------------|----------|-----------------------|

|--------------------------------|----------|-----------------------|

| Parameter            | Symbol           |      | Values | 6    | Unit | Note /                   |

|----------------------|------------------|------|--------|------|------|--------------------------|

|                      |                  | Min. | Тур.   | Max. |      | Test Condition           |

| VCO output frequency | $f_{\rm VCO}$ CC | 50   | -      | 110  | MHz  | VCOSEL = $00_B$          |

| (VCO controlled)     |                  | 100  | -      | 160  | MHz  | VCOSEL = 01 <sub>B</sub> |

| VCO output frequency | $f_{\rm VCO}$ CC | 10   | -      | 40   | MHz  | VCOSEL = 00 <sub>B</sub> |

| (VCO free-running)   |                  | 20   | -      | 80   | MHz  | VCOSEL = 01 <sub>B</sub> |

### 4.6.2.2 Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL =  $00_B$ ), the system clock is derived from the low-frequency wakeup clock source:

$f_{SYS} = f_{WU}$ .

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

### 4.6.2.3 Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

### 4.6.4 Pad Properties

The output pad drivers of the XC238xA can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . The following table lists the pad parameters.

- Note: These parameters are not subject to production test but verified by design and/or characterization.

- Note: Operating Conditions apply.

### 4.6.5.1 Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command ( $\overline{RD}$  or  $\overline{WR}$ ).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.

## 4.6.6 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

*Note:* Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

|                                                                                                                                                   | •                 |                                              |      | •    | <u> </u> |                |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------|------|------|----------|----------------|

| Parameter                                                                                                                                         | Symbol            | Values                                       |      |      | Unit     | Note /         |

|                                                                                                                                                   |                   | Min.                                         | Тур. | Max. |          | Test Condition |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge                                                                              | t <sub>1</sub> CC | <i>t</i> <sub>SYS</sub><br>- 8 <sup>1)</sup> | -    | -    | ns       |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge                                                                           | t <sub>2</sub> CC | <i>t</i> <sub>SYS</sub><br>- 6 <sup>1)</sup> | _    | _    | ns       |                |

| Data output DOUT valid time                                                                                                                       | t <sub>3</sub> CC | -6                                           | -    | 9    | ns       |                |

| Receive data input setup time to SCLKOUT receive edge                                                                                             | t <sub>4</sub> SR | 31                                           | -    | -    | ns       |                |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge                                                                                          | t <sub>5</sub> SR | -4                                           | -    | -    | ns       |                |

| Data output DOUT valid<br>time<br>Receive data input setup<br>time to SCLKOUT receive<br>edge<br>Data input DX0 hold time<br>from SCLKOUT receive | t <sub>4</sub> SR | 31                                           | -    | 9    | ns       |                |

### Table 34 USIC SSC Master Mode Timing for Upper Voltage Range

1)  $t_{SYS} = 1 / f_{SYS}$

### Table 35 USIC SSC Master Mode Timing for Lower Voltage Range

| Parameter                                                               | Symbol            | Values                                        |      |      | Unit | Note /         |

|-------------------------------------------------------------------------|-------------------|-----------------------------------------------|------|------|------|----------------|

|                                                                         |                   | Min.                                          | Тур. | Max. |      | Test Condition |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC | <i>t</i> <sub>SYS</sub><br>- 10 <sup>1)</sup> | -    | -    | ns   |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC | t <sub>SYS</sub><br>- 9 <sup>1)</sup>         | -    | -    | ns   |                |

| Data output DOUT valid<br>time                                          | t <sub>3</sub> CC | -7                                            | _    | 11   | ns   |                |

| Parameter                                         | Symbol                    | Values           |      |      | Unit | Note /                 |

|---------------------------------------------------|---------------------------|------------------|------|------|------|------------------------|

|                                                   |                           | Min.             | Тур. | Max. |      | Test Condition         |

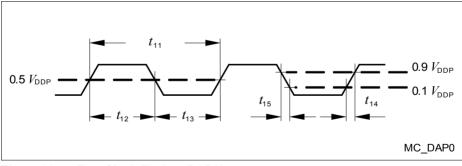

| DAP0 clock period                                 | <i>t</i> <sub>11</sub> SR | 25 <sup>1)</sup> | -    | _    | ns   |                        |

| DAP0 high time                                    | t <sub>12</sub> SR        | 8                | -    | -    | ns   |                        |

| DAP0 low time                                     | t <sub>13</sub> SR        | 8                | -    | _    | ns   |                        |

| DAP0 clock rise time                              | t <sub>14</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP0 clock fall time                              | t <sub>15</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP1 setup to DAP0<br>rising edge                 | <i>t</i> <sub>16</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 hold after DAP0 rising edge                  | <i>t</i> <sub>17</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 valid per DAP0<br>clock period <sup>2)</sup> | <i>t</i> <sub>19</sub> CC | 12               | 17   | -    | ns   | pad_type= stan<br>dard |

### Table 39 DAP Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

2) The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 29 Test Clock Timing (DAP0)

### Debug via JTAG

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_1 = 20 \text{ pF}$ .

| Parameter                                                                | Symbol                    | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|------|------|------|----------------|

|                                                                          |                           | Min.             | Тур. | Max. | 1    | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 50 <sup>1)</sup> | _    | -    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR         | 16               | -    | -    | ns   |                |

| TCK low time                                                             | $t_3$ SR                  | 16               | -    | -    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -                | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -    | -    | ns   |                |

#### Table 40JTAG Interface Timing for Upper Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.