Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

EXFL

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 118                                                                              |

| Program Memory Size        | 448KB (448K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 24x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2387a56f80laakfuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

# 16/32-Bit Single-Chip Microcontroller with 32-Bit Performance

XC238xA (XC2000 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XC238xA are summarized here.

- High-performance CPU with five-stage pipeline and MPU

- 12.5 ns instruction cycle at 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- · Interrupt system with 16 priority levels for up to 96 sources

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 32 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 832 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

- On-Chip Peripheral Modules

- Multi-functional general purpose timer unit with 5 timers

- 16-channel general purpose capture/compare unit (CAPCOM2)

- Up to 4 capture/compare units for flexible PWM signal generation (CCU6x)

#### **Summary of Features**

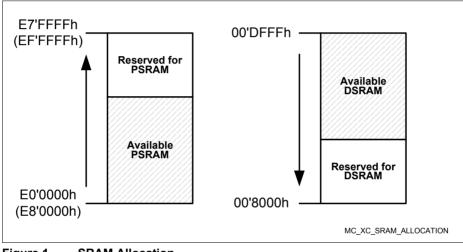

The XC238xA types are offered with several SRAM memory sizes. **Figure 1** shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- · PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

# XC2385A, XC2387A XC2000 Family / Base Line

# **General Device Information**

| Table | Table 6Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                       |  |  |  |  |

| 105   | P10.7                                         | O0 / I     | St/B | Bit 7 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | U0C1_DOUT                                     | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |  |

|       | CCU60_COU<br>T63                              | O2         | St/B | CCU60 Channel 3 Output                         |  |  |  |  |

|       | AD7                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 7     |  |  |  |  |

|       | U0C1_DX0B                                     | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |  |

|       | CCU60_CCP<br>OS0A                             | 1          | St/B | CCU60 Position Input 0                         |  |  |  |  |

|       | T4INB                                         | I          | St/B | GPT12E Timer T4 Count/Gate Input               |  |  |  |  |

| 106   | P0.7                                          | O0 / I     | St/B | Bit 7 of Port 0, General Purpose Input/Output  |  |  |  |  |

|       | U1C1_DOUT                                     | 01         | St/B | USIC1 Channel 1 Shift Data Output              |  |  |  |  |

|       | U1C0_SELO<br>3                                | O2         | St/B | USIC1 Channel 0 Select/Control 3 Output        |  |  |  |  |

|       | A7                                            | ОН         | St/B | External Bus Interface Address Line 7          |  |  |  |  |

|       | U1C1_DX0B                                     | I          | St/B | USIC1 Channel 1 Shift Data Input               |  |  |  |  |

|       | CCU61_CTR<br>APB                              | 1          | St/B | CCU61 Emergency Trap Input                     |  |  |  |  |

| 107   | P3.7                                          | O0 / I     | St/B | Bit 7 of Port 3, General Purpose Input/Output  |  |  |  |  |

|       | U2C1_DOUT                                     | 01         | St/B | USIC2 Channel 1 Shift Data Output              |  |  |  |  |

|       | U2C0_SELO<br>3                                | O2         | St/B | USIC2 Channel 0 Select/Control 3 Output        |  |  |  |  |

|       | U0C0_SELO<br>7                                | O3         | St/B | USIC0 Channel 0 Select/Control 7 Output        |  |  |  |  |

|       | U2C1_DX0B                                     | I          | St/B | USIC2 Channel 1 Shift Data Input               |  |  |  |  |

#### **Functional Description**

# 3.6 Interrupt System

The architecture of the XC238xA supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Where in a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XC238xA has eight PEC channels, each whith fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XC238xA can react quickly to the occurrence of non-deterministic events.

## Interrupt Nodes and Source Selection

The interrupt system provides 96 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

## External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

## **Trap Processing**

The XC238xA provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

#### **Functional Description**

to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Depending on the package option up to 3 External Service Request (ESR) pins are provided. The ESR unit processes their input values and allows to implement user controlled trap functions (System Requests SR0 and SR1). In this way reset, wakeup and power control can be efficiently realized.

Software interrupts are supported by the 'TRAP' instruction in combination with an individual trap (interrupt) number. Alternatively to emulate an interrupt by software a program can trigger interrupt requests by writing the Interrupt Request (IR) bit of an interrupt control register.

# 3.7 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XC238xA provides a broad range of debug and emulation features. User software running on the XC238xA can be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface. This either consists of the 2-pin Device Access Port (DAP) or of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (DAP or JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the debug interface, or via the external bus interface for increased performance.

Tracing of program execution is supported by the XC2000 Family emulation device.

The DAP interface uses two interface signals, the JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

#### **Functional Description**

# 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.42 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

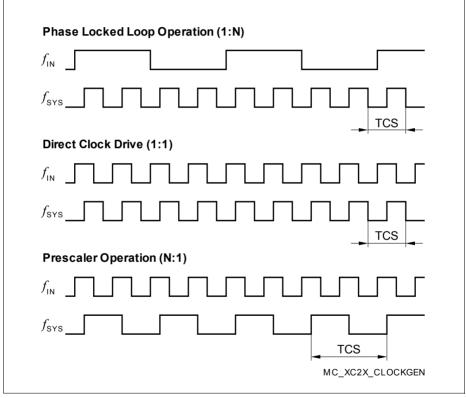

## 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC238xA from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- · On-chip clock source for operation without crystal/resonator

- · Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

# XC2385A, XC2387A XC2000 Family / Base Line

## **Functional Description**

| Table IT instruction Set Summary (cont d) |                                     |       |  |  |  |  |

|-------------------------------------------|-------------------------------------|-------|--|--|--|--|

| Mnemonic                                  | Description                         | Bytes |  |  |  |  |

| NOP                                       | Null operation                      | 2     |  |  |  |  |

| CoMUL/CoMAC                               | Multiply (and accumulate)           | 4     |  |  |  |  |

| CoADD/CoSUB                               | Add/Subtract                        | 4     |  |  |  |  |

| Co(A)SHR                                  | (Arithmetic) Shift right            | 4     |  |  |  |  |

| CoSHL                                     | Shift left                          | 4     |  |  |  |  |

| CoLOAD/STORE                              | Load accumulator/Store MAC register | 4     |  |  |  |  |

| CoCMP                                     | Compare                             | 4     |  |  |  |  |

| CoMAX/MIN                                 | Maximum/Minimum                     | 4     |  |  |  |  |

| CoABS/CoRND                               | Absolute value/Round accumulator    | 4     |  |  |  |  |

| CoMOV                                     | Data move                           | 4     |  |  |  |  |

| CoNEG/NOP                                 | Negate accumulator/Null operation   | 4     |  |  |  |  |

# Table 11 Instruction Set Summary (cont'd)

The Enter Power Down Mode instruction is not used in the XC238xA, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

# 4 Electrical Parameters

The operating range for the XC238xA is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

## 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

# 4.1.1 Absolut Maximum Rating Conditions

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability.

During absolute maximum rating overload conditions ( $V_{\rm IN} > V_{\rm DDP}$  or  $V_{\rm IN} < V_{\rm SS}$ ) the voltage on  $V_{\rm DDP}$  pins with respect to ground ( $V_{\rm SS}$ ) must not exceed the values defined by the absolute maximum ratings.

| Parameter                                                       | Symbol                       | Values |      |                           | Unit | Note /                             |

|-----------------------------------------------------------------|------------------------------|--------|------|---------------------------|------|------------------------------------|

|                                                                 |                              | Min.   | Тур. | Max.                      |      | Test Condition                     |

| Output current on a pin when high value is driven               | $I_{\rm OH}{\rm SR}$         | -30    | -    | -                         | mA   |                                    |

| Output current on a pin when low value is driven                | $I_{\rm OL}{\rm SR}$         | -      | -    | 30                        | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$         | -10    | _    | 10                        | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{\rm OV} $<br>SR  | -      | -    | 100                       | mA   | 1)                                 |

| Junction Temperature                                            | $T_{\rm J}{\rm SR}$          | -40    | _    | 150                       | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$          | -65    | _    | 150                       | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDPA}, V_{\rm DDPB}$ | -0.5   | -    | 6.0                       | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}$ SR              | -0.5   | -    | V <sub>DDP</sub><br>+ 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

## Table 12 Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

# 4.2 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XC238xA are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.6.4**.

## Supply Voltage Restrictions

The XC238xA can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

During power-on sequences, the supply voltages may only change with a maximum speed of dV/dt < 5 V/ $\mu$ s, i.e. the target supply voltage may be reached earliest after approx. 1  $\mu$ s.

Note: To limit the speed of supply voltage changes, the employment of external buffer capacitors at pins  $V_{DDPA}/V_{DDPB}$  is recommended.

Sample time and conversion time of the XC238xA's A/D converters are programmable. The timing above can be calculated using Table 19.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

| GLOBCTR.5-0<br>(DIVA) | A/D Converter<br>Analog Clock $f_{ADCI}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup><br>t <sub>s</sub> |

|-----------------------|------------------------------------------|---------------------|---------------------------------------------|

| 000000 <sub>B</sub>   | f <sub>SYS</sub>                         | 00 <sub>H</sub>     | $t_{ADCI} \times 2$                         |

| 000001 <sub>B</sub>   | f <sub>SYS</sub> / 2                     | 01 <sub>H</sub>     | $t_{ADCI} \times 3$                         |

| 000010 <sub>B</sub>   | f <sub>SYS</sub> / 3                     | 02 <sub>H</sub>     | $t_{ADCI} \times 4$                         |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                 | :                   | $t_{ADCI} \times (STC+2)$                   |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                    | FE <sub>H</sub>     | $t_{ADCI} \times 256$                       |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                    | FF <sub>H</sub>     | $t_{\rm ADCI} 	imes 257$                    |

Table 19

A/D Converter Computation Table

1) The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

## **Converter Timing Example A:**

| Assumptions:   | $f_{\rm SYS}$           | = 80 MHz (i.e. $t_{SYS}$ = 12.5 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub>                  |

|----------------|-------------------------|------------------------------------------------------------------------------------------------------|

| Analog clock   | $f_{\rm ADCI}$          | $= f_{SYS} / 4 = 20 \text{ MHz}$ , i.e. $t_{ADCI} = 50 \text{ ns}$                                   |

| Sample time    | t <sub>S</sub>          | $= t_{ADCI} \times 2 = 100 \text{ ns}$                                                               |

| Conversion 10- | bit:                    |                                                                                                      |

|                | <i>t</i> <sub>C10</sub> | = $13 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $13 \times 50$ ns + $2 \times 12.5$ ns = 0.675 $\mu$ s |

| Conversion 8-b | oit:                    |                                                                                                      |

|                | t <sub>C8</sub>         | = $11 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $11 \times 50$ ns + $2 \times 12.5$ ns = 0.575 $\mu$ s |

#### **Converter Timing Example B:**

| Assumptions:   | $f_{\rm SYS}$           | = 40 MHz (i.e. $t_{SYS}$ = 25 ns), DIVA = 02 <sub>H</sub> , STC = 03 <sub>H</sub>            |

|----------------|-------------------------|----------------------------------------------------------------------------------------------|

| Analog clock   | $f_{\rm ADCI}$          | $= f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e. $t_{ADCI} = 75 \text{ ns}$                         |

| Sample time    | t <sub>S</sub>          | $= t_{ADCI} \times 5 = 375 \text{ ns}$                                                       |

| Conversion 10  | -bit:                   |                                                                                              |

|                | <i>t</i> <sub>C10</sub> | = $16 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 16 × 75 ns + 2 × 25 ns = 1.25 µs                    |

| Conversion 8-b | oit:                    |                                                                                              |

|                | t <sub>C8</sub>         | = $14 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $14 \times 75$ ns + $2 \times 25$ ns = 1.10 µs |

|                |                         |                                                                                              |

# 4.6.2 Definition of Internal Timing

The internal operation of the XC238xA is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XC238xA.

Figure 19 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 19** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

The timing in the AC Characteristics refers to TCSs. Timing must be calculated using the minimum TCS possible under the given circumstances.

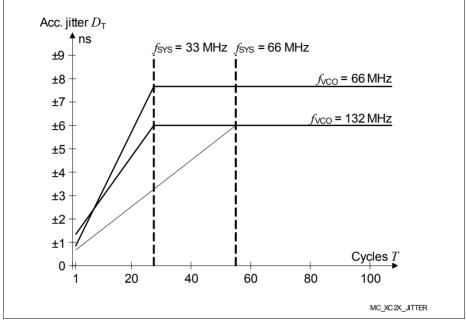

The actual minimum value for TCS depends on the jitter of the PLL. Because the PLL is constantly adjusting its output frequency to correspond to the input frequency (from crystal or oscillator), the accumulated jitter is limited. This means that the relative deviation for periods of more than one TCS is lower than for a single TCS (see formulas and **Figure 20**).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler K2 to generate the system clock signal  $f_{SYS}$ . The number of VCO cycles is K2 × **T**, where **T** is the number of consecutive  $f_{SYS}$  cycles (TCS).

The maximum accumulated jitter (long-term jitter) D<sub>Tmax</sub> is defined by:

$D_{\text{Tmax}}$  [ns] = ±(220 / (K2 ×  $f_{\text{SYS}}$ ) + 4.3)

This maximum value is applicable, if either the number of clock cycles T > ( $f_{SYS}$  / 1.2) or the prescaler value K2 > 17.

In all other cases for a timeframe of  $\mathbf{T} \times TCS$  the accumulated jitter  $D_T$  is determined by:

$D_{T}$  [ns] =  $D_{Tmax} \times [(1 - 0.058 \times K2) \times (T - 1) / (0.83 \times f_{SYS} - 1) + 0.058 \times K2]$

$f_{SYS}$  in [MHz] in all formulas.

Example, for a period of 3 TCSs @ 33 MHz and K2 = 4:

$D_{max} = \pm (220 / (4 \times 33) + 4.3) = 5.97$  ns (Not applicable directly in this case!)

$\mathsf{D_3} = 5.97 \times [(1 - 0.058 \times 4) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 4]$

= 5.97 × [0.768 × 2 / 26.39 + 0.232]

Example, for a period of 3 TCSs @ 33 MHz and K2 = 2:

$D_{max} = \pm (220 / (2 \times 33) + 4.3) = 7.63$  ns (Not applicable directly in this case!)

$D_3 = 7.63 \times [(1 - 0.058 \times 2) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 2]$ = 7.63 \times [0.884 \times 2 / 26 30 + 0.116]

$$= 7.63 \times [0.884 \times 2/26.39 + 0.116]$$

# XC2385A, XC2387A XC2000 Family / Base Line

#### **Electrical Parameters**

Figure 20 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_L$  = 20 pF.

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{DDPB}$  pin 100 and  $V_{SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

Table 26 is valid under the following conditions:

$V_{\text{DDP}} \ge 4.5 \text{ V}; V_{\text{DDPtyp}} = 5 \text{ V}; V_{\text{DDP}} \le 5.5 \text{ V}; C_{\text{L}} \ge 20 \text{ pF}; C_{\text{L}} \le 100 \text{ pF};$

## Table 26 Standard Pad Parameters for Upper Voltage Range

| Parameter                              | Symbol             |      | Values | 5                                         | Unit | Note /                        |

|----------------------------------------|--------------------|------|--------|-------------------------------------------|------|-------------------------------|

|                                        |                    | Min. | Тур.   | Max.                                      |      | Test Condition                |

| Maximum output driver                  | I <sub>Omax</sub>  | -    | -      | 10                                        | mA   | Strong driver                 |

| current (absolute value) <sup>1)</sup> | CC                 | -    | -      | 4.0                                       | mA   | Medium driver                 |

|                                        |                    | -    | -      | 0.5                                       | mA   | Weak driver                   |

| Nominal output driver                  | I <sub>Onom</sub>  | -    | -      | 2.5                                       | mA   | Strong driver                 |

| current (absolute value)               | CC                 | -    | -      | 1.0                                       | mA   | Medium driver                 |

|                                        |                    | -    | -      | 0.1                                       | mA   | Weak driver                   |

| Rise and Fall times (10% -<br>90%)     | t <sub>RF</sub> CC | _    | -      | 4.2 +<br>0.14 x<br><i>C</i> <sub>L</sub>  | ns   | Strong driver;<br>Sharp edge  |

|                                        |                    | _    | -      | 11.6 +<br>0.22 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Medium edge |

|                                        |                    | _    | -      | 20.6 +<br>0.22 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Slow edge   |

|                                        |                    | _    | -      | 23 +<br>0.6 x<br>C <sub>L</sub>           | ns   | Medium driver                 |

|                                        |                    | _    | -      | 212 +<br>1.9 x<br><i>C</i> L              | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

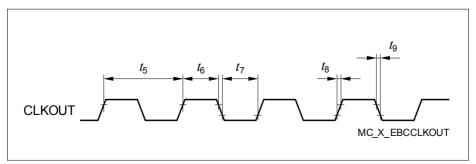

# 4.6.5 External Bus Timing

The following parameters specify the behavior of the XC238xA bus interface.

- Note: These parameters are not subject to production test but verified by design and/or characterization.

- Note: Operating Conditions apply.

## **Bus Interface Performance Limits**

The output frequency at the bus interface pins is limited by the performance of the output drivers. The fast clock driver (used for CLKOUT) can drive 80-MHz signals, the standard drivers can drive 40-MHz signals

Therefore, the speed of the EBC must be limited, either by limiting the system frequency to  $f_{SYS} \le 80$  MHz or by adding waitstates so that signal transitions have a minimum distance of 12.5 ns.

For a description of the bus protocol and the programming of its variable timing parameters, please refer to the User's Manual.

| Parameter                       | Symbol            |      | Values      |      | Unit | Note /         |

|---------------------------------|-------------------|------|-------------|------|------|----------------|

|                                 |                   | Min. | Тур.        | Max. |      | Test Condition |

| CLKOUT Cycle Time <sup>1)</sup> | t <sub>5</sub> CC | -    | $1/f_{SYS}$ | -    | ns   |                |

| CLKOUT high time                | t <sub>6</sub> CC | 2    | -           | -    |      |                |

| CLKOUT low time                 | t <sub>7</sub> CC | 2    | -           | -    |      |                |

| CLKOUT rise time                | t <sub>8</sub> CC | -    | -           | 3    | ns   |                |

| CLKOUT fall time                | t <sub>9</sub> CC | -    | -           | 3    |      |                |

## Table 28 EBC Parameters

The CLKOUT cycle time is influenced by PLL jitter. For longer periods the relative deviation decreases (see PLL deviation formula).

# 4.6.7 Debug Interface Timing

The debugger can communicate with the XC238xA either via the 2-pin DAP interface or via the standard JTAG interface.

## Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_L$ = 20 pF.

| Parameter                                         | Symbol                    |                  | Values | S    | Unit | Note /                 |

|---------------------------------------------------|---------------------------|------------------|--------|------|------|------------------------|

|                                                   |                           | Min.             | Тур.   | Max. |      | Test Condition         |

| DAP0 clock period                                 | t <sub>11</sub> SR        | 25 <sup>1)</sup> | -      | -    | ns   |                        |

| DAP0 high time                                    | t <sub>12</sub> SR        | 8                | -      | -    | ns   |                        |

| DAP0 low time                                     | t <sub>13</sub> SR        | 8                | -      | -    | ns   |                        |

| DAP0 clock rise time                              | t <sub>14</sub> SR        | -                | -      | 4    | ns   |                        |

| DAP0 clock fall time                              | t <sub>15</sub> SR        | -                | -      | 4    | ns   |                        |

| DAP1 setup to DAP0<br>rising edge                 | <i>t</i> <sub>16</sub> SR | 6                | -      | -    | ns   | pad_type= stan<br>dard |

| DAP1 hold after DAP0 rising edge                  | <i>t</i> <sub>17</sub> SR | 6                | -      | -    | ns   | pad_type= stan<br>dard |

| DAP1 valid per DAP0<br>clock period <sup>2)</sup> | <i>t</i> <sub>19</sub> CC | 17               | 20     | -    | ns   | pad_type= stan<br>dard |

Table 38

DAP Interface Timing for Upper Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

2) The Host has to find a suitable sampling point by analyzing the sync telegram response.

| Parameter                                                                | Symbol                    |                  | Values | 5    | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|--------|------|------|----------------|

|                                                                          |                           | Min.             | Тур.   | Max. |      | Test Condition |

| TCK clock period                                                         | $t_1$ SR                  | 50 <sup>1)</sup> | -      | -    | ns   | 2)             |

| TCK high time                                                            | $t_2$ SR                  | 16               | -      | _    | ns   |                |

| TCK low time                                                             | $t_3$ SR                  | 16               | -      | _    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -                | -      | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -      | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -      | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -      | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                | 32     | 36   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 32     | 36   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 32     | 36   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -      | -    | ns   |                |

## Table 41 JTAG Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.

## Package and Reliability

# Package Outlines

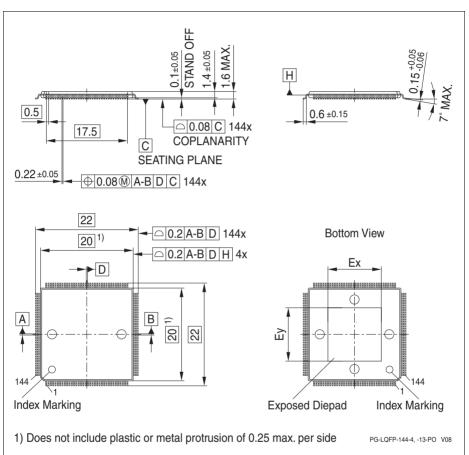

# Figure 34 PG-LQFP-144-13/-23 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages

## Package and Reliability

# 5.3 Quality Declarations

The operation lifetime of the XC238xA depends on the applied temperature profile in the application. For a typical example, please refer to **Table 44**; for other profiles, please contact your Infineon counterpart to calculate the specific lifetime within your application.

## Table 43Quality Parameters

| Parameter                                                    | Symbol             | Values |      |       | Unit | Note /                       |

|--------------------------------------------------------------|--------------------|--------|------|-------|------|------------------------------|

|                                                              |                    | Min.   | Тур. | Max.  |      | Test Condition               |

| Operation lifetime                                           | t <sub>OP</sub> CC | -      | -    | 20    | а    | See Table 44<br>and Table 45 |

| ESD susceptibility<br>according to Human Body<br>Model (HBM) | $V_{\rm HBM}$ SR   | -      | -    | 2 000 | V    | EIA/JESD22-<br>A114-B        |

| Moisture sensitivity level                                   | MSL CC             | -      | -    | 3     | -    | JEDEC<br>J-STD-020C          |

## Table 44 Typical Usage Temperature Profile

| Operating Time (Sum = 20 years) | Operating Temperat.                       | Notes            |

|---------------------------------|-------------------------------------------|------------------|

| 1 200 h                         | <i>T</i> <sub>J</sub> = 150°C             | Normal operation |

| 3 600 h                         | <i>T</i> <sub>J</sub> = 125°C             | Normal operation |

| 7 200 h                         | <i>T</i> <sub>J</sub> = 110°C             | Normal operation |

| 12 000 h                        | <i>T</i> <sub>J</sub> = 100°C             | Normal operation |

| 7 × 21 600 h                    | <i>T</i> <sub>J</sub> = 010°C,,<br>6070°C | Power reduction  |

#### Table 45 Long Time Storage Temperature Profile

| Operating Time (Sum = 20 years) | Operating Temperat.                | Notes            |

|---------------------------------|------------------------------------|------------------|

| 2 000 h                         | <i>T</i> <sub>J</sub> = 150°C      | Normal operation |

| 16 000 h                        | <i>T</i> <sub>J</sub> = 125°C      | Normal operation |

| 6 000 h                         | <i>T</i> <sub>J</sub> = 110°C      | Normal operation |

| 151 200 h                       | $T_{\rm J} \le 150^{\circ}{\rm C}$ | No operation     |

www.infineon.com

Published by Infineon Technologies AG